Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SCI                                                  |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 98                                                                              |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417145fw50v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 8.5  | DTC Operation Flowchart                                            | 126 |

|-------------|--------------------------------------------------------------------|-----|

| Figure 8.6  | Memory Mapping in Normal Mode                                      | 127 |

| Figure 8.7  | Memory Mapping in Repeat Mode                                      | 128 |

| Figure 8.8  | Memory Mapping in Block Transfer Mode                              | 130 |

| Figure 8.9  | Chain Transfer                                                     | 131 |

| Figure 8.10 | DTC Operation Timing Example (Normal Mode)                         | 132 |

| Section 9   | Bus State Controller (BSC)                                         |     |

| Figure 9.1  | BSC Block Diagram                                                  | 138 |

| Figure 9.2  | Address Format                                                     | 141 |

| Figure 9.3  | Basic Timing of External Space Access                              | 154 |

| Figure 9.4  | Wait State Timing of External Space Access (Software Wait Only)    | 155 |

| Figure 9.5  | Wait State Timing of External Space Access                         |     |

|             | (Two Software Wait States + $\overline{WAIT}$ Signal Wait State)   | 156 |

| Figure 9.6  | CS Assert Period Extension Function                                | 157 |

| Figure 9.7  | Example of Idle Cycle Insertion                                    | 159 |

| Figure 9.8  | Example of Idle Cycle Insertion at Same Space Consecutive Access   | 160 |

| Figure 9.9  | Bus Mastership Release Procedure                                   | 162 |

| Figure 9.10 | Example of 8-bit Data Bus Width ROM Connection                     | 163 |

| Figure 9.11 | Example of 16-bit Data Bus Width ROM Connection                    | 163 |

| Figure 9.12 | Example of 32-bit Data Bus Width ROM Connection (only for SH7145)  | 164 |

|             | Example of 8-bit Data Bus Width SRAM Connection                    |     |

| Figure 9.14 | Example of 16-bit Data Bus Width SRAM Connection                   | 165 |

| Figure 9.15 | Example of 32-bit Data Bus Width SRAM Connection (only for SH7145) | 165 |

| Figure 9.16 | One Bus Cycle                                                      | 166 |

| Section 10  | Direct Memory Access Controller (DMAC)                             |     |

| Figure 10.1 | DMAC Block Diagram                                                 | 168 |

| Figure 10.2 | DMAC Transfer Flowchart                                            | 181 |

| Figure 10.3 | (1) Round Robin Mode                                               | 185 |

| Figure 10.3 | (2) Example of Changes in Priority in Round Robin Mode             | 186 |

| Figure 10.4 | Data Flow in Single Address Mode                                   | 188 |

|             | Example of DMA Transfer Timing in Single Address Mode              |     |

| Figure 10.6 | Direct Address Operation during Dual Address Mode                  | 190 |

| Figure 10.7 | Example of Direct Address Transfer Timing in Dual Address Mode     | 191 |

| -           | Dual Address Mode and Indirect Address Operation                   |     |

| •           | (When External Memory Space Is 16 Bits)                            | 192 |

| Figure 10.9 | Dual Address Mode and Indirect Address Transfer Timing Example     |     |

| -           | (External Memory Space to External Memory Space, 16-Bit Width)     | 193 |

| Figure 10.1 | 0 Dual Address Mode and Indirect Address Transfer Timing Example   |     |

| -           | (On-chip Memory Space to On-chip Memory Space)                     | 194 |

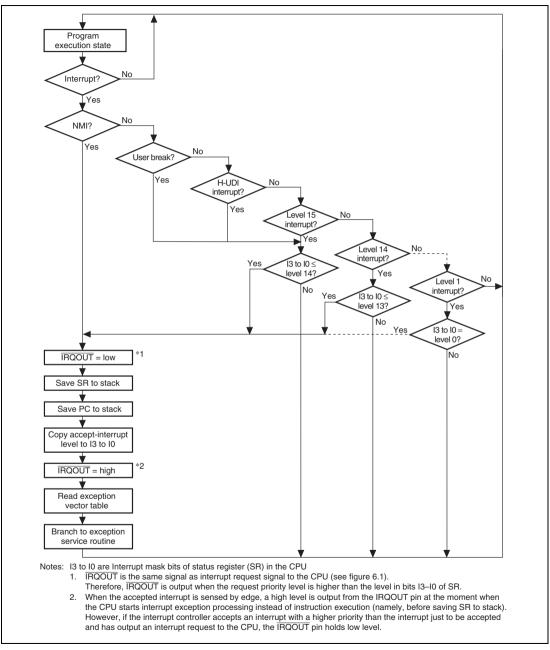

the IRQ status register (ISR). Interrupts held pending due to edge detection are cleared by a power-on reset or a manual reset.

### Figure 6.3 Interrupt Sequence Flowchart

Rev.4.00 Mar. 27, 2008 Page 94 of 882 REJ09B0108-0400

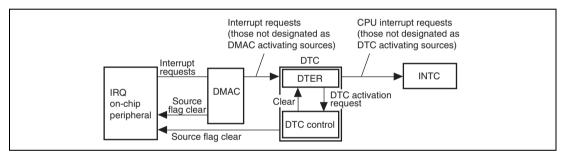

## 8.3 Operation

### 8.3.1 Activation Sources

The DTC operates when activated by an interrupt or by a write to DTCSR by software. An interrupt request can be directed to the CPU or DTC, as designated by the corresponding DTER bit. At the end of a data transfer (or the last consecutive transfer in the case of chain transfer), the activation source interrupt flag or corresponding DTER bit is cleared. The activation source flag, in the case of RXI\_2, for example, is the RDRF flag of SCI2.

When a DTC is activated by an interrupt, existing CPU mask level and interrupt controller priorities have no effect. If there is more than one activation source at the same time, the DTC operates in accordance with the default priorities.

Figure 8.2 shows a block diagram of activation source control. For details see section 6, Interrupt Controller (INTC).

Figure 8.2 Activating Source Control Block Diagram

### 8.3.2 Location of Register Information and DTC Vector Table

Figure 8.3 shows the allocation of register information in memory space. The register information start addresses are designated by DTBR for the upper 16 bits, and the DTC vector table for the lower 16 bits.

The allocation in order from the register information start address in normal mode is DTMR, DTCRA, 4 bytes empty (no effect on DTC operation), DTSAR, then DTDAR. In repeat mode it is DTMR, DTCRA, DTIAR, DTSAR, and DTDAR. In block transfer mode, it is DTMR, DTCRA, 2 bytes empty (no effect on DTC operation), DTCRB, DTSAR, then DTDAR.

Fundamentally, certain RAM areas are designated for addresses storing register information.

### Table 9.2Address Map

### • On-chip ROM enabled mode

| Address                  | Space                     | Memory                    | Size       | Bus Width      |

|--------------------------|---------------------------|---------------------------|------------|----------------|

| H'00000000 to H'0003FFFF | On-chip ROM               | On-chip ROM               | 256 kbytes | 32 bits        |

| H'00040000 to H'001FFFFF | Reserved                  | Reserved                  |            |                |

| H'00200000 to H'003FFFFF | CS0 space                 | External space            | 2 Mbytes   | 8/16/32 bits*1 |

| H'00400000 to H'007FFFFF | CS1 space                 | External space            | 4 Mbytes   | 8/16/32 bits*1 |

| H'00800000 to H'00BFFFFF | CS2 space                 | External space            | 4 Mbytes   | 8/16/32 bits*1 |

| H'00C00000 to H'00FFFFFF | CS3 space                 | External space            | 4 Mbytes   | 8/16/32 bits*1 |

| H'01000000 to H'011FFFFF | Reserved                  | Reserved                  |            |                |

| H'01200000 to H'013FFFFF | CS4 space*3               | External space            | 2 Mbytes   | 8/16/32 bits*1 |

| H'01400000 to H'017FFFFF | CS5 space*3               | External space            | 4 Mbytes   | 8/16/32 bits*1 |

| H'01800000 to H'01BFFFFF | CS6 space*3               | External space            | 4 Mbytes   | 8/16/32 bits*1 |

| H'01C00000 to H'01FFFFFF | CS7 space*3               | External space            | 4 Mbytes   | 8/16/32 bits*1 |

| H'02000000 to H'FFFF7FFF | Reserved                  | Reserved                  |            |                |

| H'FFFF8000 to H'FFFFBFFF | On-chip peripheral module | On-chip peripheral module | 16 kbytes  | 8/16 bits      |

| H'FFFFC000 to H'FFFFDFFF | Reserved                  | Reserved                  |            |                |

| H'FFFFE000 to H'FFFFFFF  | On-chip RAM               | On-chip RAM               | 8 kbytes   | 32 bits        |

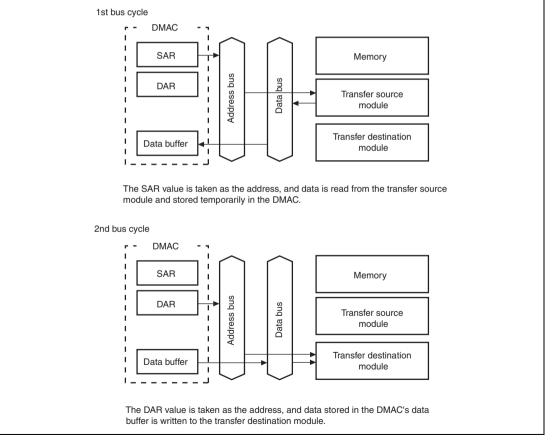

#### **Dual Address Mode:**

Dual address mode is used for access of both the transfer source and destination by address. Transfer source and destination can be accessed either internally or externally. Dual address mode is subdivided into two other modes: direct address transfer mode and indirect address transfer mode.

• Direct Address Transfer Mode

Data is read from the transfer source during the data read cycle, and written to the transfer destination during the write cycle, so transfer is conducted in two bus cycles. At this time, the transfer data is temporarily stored in the DMAC. With the kind of external memory transfer shown in figure 10.6, data is read from one of the memories by the DMAC during a read cycle, then written to the other external memory during the subsequent write cycle. Figure 10.7 shows the timing for this operation.

Figure 10.6 Direct Address Operation during Dual Address Mode

Rev.4.00 Mar. 27, 2008 Page 190 of 882 REJ09B0108-0400

### 11.3.5 Timer Status Register (TSR)

The TSR registers are 8-bit readable/writable registers that indicate the status of each channel. The MTU has five TSR registers, one for each channel.

| Bit | Bit Name | Initial Value | R/W    | Description                                                                                                                                                                                                                             |

|-----|----------|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TCFD     | 1             | R      | Count Direction Flag                                                                                                                                                                                                                    |

|     |          |               |        | Status flag that shows the direction in which TCNT counts in channels 1, 2, 3, and 4.                                                                                                                                                   |

|     |          |               |        | In channel 0, bit 7 is reserved. It is always read as 1 and the write value should always be 1.                                                                                                                                         |

|     |          |               |        | 0: TCNT counts down<br>1: TCNT counts up                                                                                                                                                                                                |

| 6   | —        | 1             | R      | Reserved                                                                                                                                                                                                                                |

|     |          |               |        | This bit is always read as 1. The write value should always be 1.                                                                                                                                                                       |

| 5   | TCFU     | 0             | R/(W)* | Underflow Flag                                                                                                                                                                                                                          |

|     |          |               |        | Status flag that indicates that TCNT underflow has<br>occurred when channels 1 and 2 are set to phase counting<br>mode. Only 0 can be written, for flag clearing.                                                                       |

|     |          |               |        | In channels 0, 3, and 4, bit 5 is reserved. It is always read as 0 and the write value should always be 0.                                                                                                                              |

|     |          |               |        | [Setting condition]                                                                                                                                                                                                                     |

|     |          |               |        | <ul> <li>When the TCNT value underflows (changes from<br/>H'0000 to H'FFFF)</li> </ul>                                                                                                                                                  |

|     |          |               |        | [Clearing condition]                                                                                                                                                                                                                    |

|     |          |               |        | • When 0 is written to TCFU after reading TCFU = 1                                                                                                                                                                                      |

| 4   | TCFV     | 0             | R/(W)* | Overflow Flag                                                                                                                                                                                                                           |

|     |          |               |        | Status flag that indicates that TCNT overflow has occurred. Only 0 can be written, for flag clearing.                                                                                                                                   |

|     |          |               |        | [Setting condition]                                                                                                                                                                                                                     |

|     |          |               |        | <ul> <li>When the TCNT value overflows (changes from<br/>H'FFFF to H'0000)</li> <li>In channel 4, when the TCNT_4 value underflows<br/>(changes from H'0001 to H'0000) in complementary<br/>PWM mode, this flag is also set.</li> </ul> |

|     |          |               |        | [Clearing condition]                                                                                                                                                                                                                    |

|     |          |               |        | <ul> <li>When 0 is written to TCFV after reading TCFV = 1<br/>In cannel 4, when DTC is activated by TCIV interrupt<br/>and the DISEL bit of DTMR in DTC is 0, this flag is<br/>also cleared.</li> </ul>                                 |

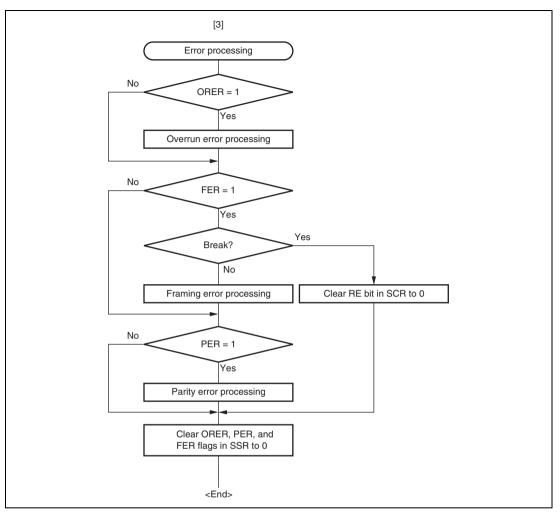

Figure 13.9 Sample Serial Reception Data Flowchart (2)

| Channel | Name  | Interrupt Source    | Interrupt Flag | DMAC or DTC<br>Activation |

|---------|-------|---------------------|----------------|---------------------------|

| 0       | ERI_0 | Receive error       | ORER, FER, PER | Not possible              |

|         | RXI_0 | Receive data full   | RDRF           | Possible                  |

|         | TXI_0 | Transmit data empty | TDRE           | Possible                  |

|         | TEI_0 | Transmission end    | TEND           | Not possible              |

| 1       | ERI_1 | Receive error       | ORER, FER, PER | Not possible              |

|         | RXI_1 | Receive data full   | RDRF           | Possible                  |

|         | TXI_1 | Transmit data empty | TDRE           | Possible                  |

|         | TEI_1 | Transmission end    | TEND           | Not possible              |

| 2       | ERI_2 | Receive error       | ORER, FER, PER | Not possible              |

|         | RXI_2 | Receive data full   | RDRF           | Possible                  |

|         | TXI_2 | Transmit data empty | TDRE           | Possible                  |

|         | TEI_2 | Transmission end    | TEND           | Not possible              |

| 3       | ERI_3 | Receive error       | ORER, FER, PER | Not possible              |

|         | RXI_3 | Receive data full   | RDRF           | Possible                  |

|         | TXI_3 | Transmit data empty | TDRE           | Possible                  |

|         | TEI_3 | Transmission end    | TEND           | Not possible              |

### Table 13.12 Interrupt Sources in Serial Communication Interface Mode

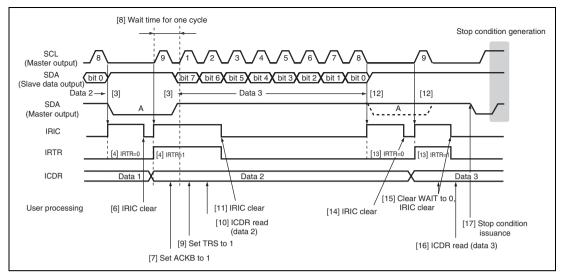

The following description gives the procedures for and operations of receiving data in one byte units by fixing SCL low for every data reception using the HNDS bit function.

- Clear the TRS bit in ICCR to 0 to change from the transmit mode to the receive mode. Clear the ACKB bit in ICSR to 0 (setting of the acknowledge data). Set the HNDS bit in SCRX to 1. Clear the IRIC flag to 0 to confirm that reception has been completed. When the first frame is the final receive data, perform end processing in step 6 and subsequent steps.

- 2. When ICDR is read (a dummy read operation), the receiving of data starts; the receive clock is output in synchronization with the internal clock, and the first datum is then received. (Data of the SDA pin is stored in ICDRS in synchronization with the rising edge of receive clock.)

- 3. The master device sets SDA to low on the 9th cycle of the receive clock and returns the acknowledge bit. The receive data is transferred from ICDRS to ICDRR at the rising edge of the 9th cycle of the receive clock, and the ICDRF, IRIC, and IRTR flags are set to 1. When the IEIC bit in ICCR has been set to 1, an interrupt request is generated for the CPU. The master devise fixes SCL low between at the falling edge of 9th cycle of the receive clock and read of ICDR data.

- 4. To identify the next interrupt, the IRIC flag is cleared to 0. When the next frame is the final receive data, perform end processing in step 6 and subsequent steps.

- 5. Read the receive data of ICDR. This clears the ICDRF flag to 0, and the master devise outputs the receive clock continuously for the reception of the next data.

Data can be received by repeating the steps 3 to 5.

- 6. Set the ACKB bit to 1 (setting of acknowledge data for the final reception).

- 7. Read ICDR receive data. This clears the ICDRF flag to 0. The master device outputs the receive clock to receive data.

- 8. When one frame of data has been received, the ICDRF, IRIC, and IRTR flags are set to 1 at the rising edge of the 9th cycle of receive clock.

- 9. Clear the IRIC flag to 0.

- 10. Read ICDR receives data after setting the TRS bit to 1. This clears the ICDRF flag to 0.

- Write 0 to BBSY and SCP in ICCR to generate the stop condition.

This changes SDA from low to high when SCL is high, and generates the stop condition.

Figure 14.16 An Example of the Stop Condition Issuance Timing in Master Receive Mode (MLS = ACKB = 0, WAIT = 1)

### 14.4.5 Operations in Slave Reception

In the slave receive mode of the  $I^2C$  bus format, the master device transmits the transmit clock and data, and the slave device returns acknowledgements of reception. The slave device compares the address of the slave address and the slave address of the first frame issued after the start condition issuance by the master device. If the addresses match, the slave device operates as a slave device specified by the master device.

#### **Reception with HNDS Function (HNDS = 1):**

Figure 14.17 is a flowchart that gives an example of operations in slave receive mode (HNDS = 1).

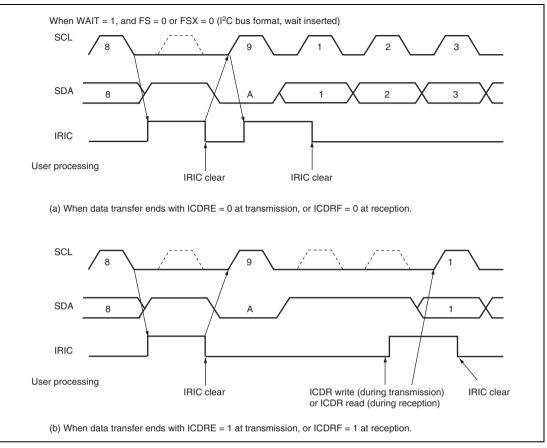

Figure 14.26 IRIC Flag Set Timing and the Control of SCL (2)

- 14. Points for cautions when reading ICDR in transmit mode and writing to ICDR in receive mode When ICDR is read in transmit mode (TRS = 1) or ICDR is written to in receive mode (TRS = 0), the SCL pin may not be held low in some cases after transmit/receive operation has been completed, thus inconveniently allowing clock pulses to be output on the SCL bus line before ICDR is accessed correctly. To access ICDR correctly, read the ICDR after setting to receive mode or write to the ICDR after setting to transmit mode.

- 15. Points for cautions on ACKE and TRS bits in slave mode

In the  $I^2C$  bus interface, if 1 is received as the acknowledge bit value (ACKB = 1) in transmit mode (TRS = 1) and then the address is received in slave mode without performing appropriate processing, interrupt handling may start at the rising edge of the 9th cycle of the clock even when the address does not match.

Similarly, in slave mode, if the start condition or address is transmitted from the master device in transmit mode (TRS = 1), the IRIC flag may be set as a result of the ICDRE flag set or receiving 1 as the acknowledge bit value (ACKB = 1), thus causing an interrupt source to occur even when the address does not match.

To use the  $I^2C$  bus interface module in slave mode, be sure to follow the procedures below.

- When 1 is received as the acknowledge bit value for the final transmit data at the end of a series of transmit operations, clear the ACKE bit in ICCR once to initialize the ACKB bit to 0.

- Set to receive mode (TRS = 0) before the next start condition is input in slave mode. Complete transmit operation by the procedure shown in figure 14.23, in order to switch from slave transmit mode to slave receive mode.

#### 14.5.1 Module Stop Mode Setting

IIC is enabled or disabled using the module stop control register. IIC is disabled with the initial value. Cancelling module stop mode allows the register to be accessed. For details, see section 24, Power-Down Modes.

|                   | Pin Name         |                                        |                               |                                        |  |  |  |  |  |  |

|-------------------|------------------|----------------------------------------|-------------------------------|----------------------------------------|--|--|--|--|--|--|

| Pin No.<br>SH7144 | On-Chip ROM      | I Enabled (MCU Mode 2)                 | Single Chip Mode (MCU Mode 3) |                                        |  |  |  |  |  |  |

|                   | Initial Function | PFC Selected Function<br>Possibilities | Initial Function              | PFC Selected Function<br>Possibilities |  |  |  |  |  |  |

| 99                | PF7/AN7          | PF7/AN7                                | PF7/AN7                       | PF7/AN7                                |  |  |  |  |  |  |

| 102               | PE5              | PE5/TIOC1B/TXD3                        | PE5                           | PE5/TIOC1B/TXD3                        |  |  |  |  |  |  |

| 104               | PE6              | PE6/TIOC2A/SCK3                        | PE6                           | PE6/TIOC2A/SCK3                        |  |  |  |  |  |  |

| 105               | PE7              | PE7/TIOC2B/RXD2                        | PE7                           | PE7/TIOC2B/RXD2                        |  |  |  |  |  |  |

| 106               | PE8              | PE8/TIOC3A/ SCK2                       | PE8                           | PE8/TIOC3A/SCK2                        |  |  |  |  |  |  |

| 107               | PE9              | PE9/TIOC3B/ SCK3                       | PE9                           | PE9/TIOC3B/SCK3                        |  |  |  |  |  |  |

| 108               | PE10             | PE10/TIOC3C/TXD2                       | PE10                          | PE10/TIOC3C/TXD2                       |  |  |  |  |  |  |

| 110               | PE11             | PE11/TIOC3D/RXD3                       | PE11                          | PE11/TIOC3D/RXD3                       |  |  |  |  |  |  |

| 111               | PE12             | PE12/TIOC4A/TXD3                       | PE12                          | PE12/TIOC4A/TXD3                       |  |  |  |  |  |  |

| 112               | PE13             | PE13/TIOC4B/MRES                       | PE13                          | PE13/TIOC4B/MRES                       |  |  |  |  |  |  |

| Notoe: 1          | E-7TAT version   | only                                   |                               |                                        |  |  |  |  |  |  |

Notes: 1. F-ZTAT version only

2. Fixed to TMS, TRST, TDI, TDO, and TCK when using the E10A (in DBGMD = high).

3. Masked ROM version and ROM less version only

### 19.6.1 Boot Mode

Table 19.4 shows the boot mode operations between reset end and branching to the programming control program.

- 1. When boot mode is used, the flash memory programming control program must be prepared in the host beforehand. Prepare a programming control program in accordance with the description in section 19.8, Flash Memory Programming/Erasing.

- 2. The SCI1 should be set to asynchronous mode, and the transfer format as follows: 8-bit data, 1 stop bit, and no parity.

- 3. When the boot program is initiated, the chip measures the low-level period of asynchronous SCI communication data (H'00) transmitted continuously from the host. The chip then calculates the bit rate of transmission from the host, and adjusts the SCI1 bit rate to match that of the host. The reset should end with the RxD pin high. The RxD and TxD pins should be pulled up on the board if necessary.

- 4. After matching the bit rates, the chip transmits one H'00 byte to the host to indicate the completion of bit rate adjustment. The host should confirm that this adjustment end indication (H'00) has been received normally, and transmit one H'55 byte to the chip. If reception could not be performed normally, initiate boot mode again by a reset. Depending on the host's transfer bit rate and system clock frequency of this LSI, there will be a discrepancy between the bit rates of the host and the chip. To operate the SCI properly, set the host's transfer bit rate and system clock frequency of this LSI within the ranges listed in table 19.5.

- 5. In boot mode, a part of the on-chip RAM area is used by the boot program. The area H'FFFFE800 to H'FFFFFFF is the area to which the programming control program is transferred from the host. The boot program area cannot be used until the execution state in boot mode switches to the programming control program.

- 6. Before branching to the programming control program, the chip terminates transfer operations by SCI1 (by clearing the RE and TE bits in SCR to 0), however the adjusted bit rate value remains set in BRR. Therefore, the programming control program can still use it for transfer of write data or verify data with the host. The TxD pin is high. The contents of the CPU general registers are undefined immediately after branching to the programming control program. These registers must be initialized at the beginning of the programming control program, as the stack pointer (SP), in particular, is used implicitly in subroutine calls, etc.

- 7. Boot mode can be cleared by a reset. End the reset after driving the reset pin low, waiting at least 25 states, and then setting the mode (MD) pins. Boot mode is also cleared when a WDT overflow occurs.

- 8. Do not change the MD pin input levels in boot mode.

- 9. All interrupts are disabled during programming or erasing of the flash memory.

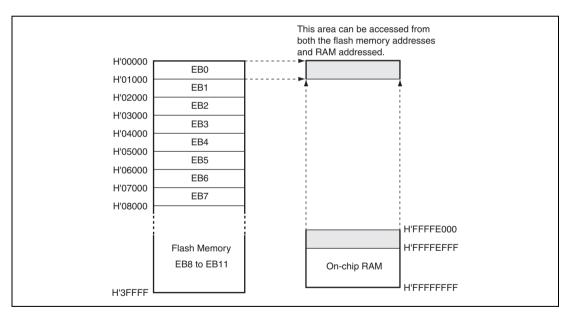

Figure 19.8 shows a sample procedure for flash memory block area overlapping.

- 1. The RAM area to be overlapped is fixed at a 4-kbyte area in the range H'FFFFE000 to H'FFFFEFFF.

- 2. The flash memory area to be overlapped is selected by RAMER from a 4-kbyte area of the EB0 to EB7 blocks.

- 3. The overlapped RAM area can be accessed from both the flash memory addresses and RAM addresses.

- 4. When the RAMS bit in RAMER is set to 1, program/erase protection is enabled for all flash memory blocks (emulation protection). In this state, setting the P or E bit in FLMCR1 to 1 does not cause a transition to program mode or erase mode.

- 5. A RAM area cannot be erased by execution of software in accordance with the erase algorithm.

- 6. Block area EB0 contains the vector table. When performing RAM emulation, the vector table is needed in the overlapped RAM.

Figure 19.8 Example of RAM Overlap Operation (RAM[2:0] = B'000)

### 25. List of Registers

| Register<br>abbreviation | Bit7 | Bit6 | Bit5   | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Module                   |

|--------------------------|------|------|--------|------|------|------|------|------|--------------------------|

| _                        | _    |      | _      | _    | _    | _    | _    | _    | _                        |

| BCR1                     | _    | _    | MTURWE |      | _    | _    | _    | _    | BSC                      |

|                          | A3LG | A2LG | A1LG   | A0LG | A3SZ | A2SZ | A1SZ | A0SZ |                          |

| BCR2                     | IW31 | IW30 | IW21   | IW20 | IW11 | IW10 | IW01 | IW00 |                          |

|                          | CW3  | CW2  | CW1    | CW0  | SW3  | SW2  | SW1  | SW0  |                          |

| WCR1                     | W33  | W32  | W31    | W30  | W23  | W22  | W21  | W20  |                          |

|                          | W13  | W12  | W11    | W10  | W03  | W02  | W01  | W00  |                          |

| WCR2                     | _    | _    | _      | _    | _    | _    | _    | _    |                          |

|                          | _    | _    | _      | _    | DSW3 | DSW2 | DSW1 | DSW0 |                          |

| _                        | _    | _    | _      | _    | _    | _    | _    | _    | _                        |

| RAMER                    | _    | _    | _      | _    | _    | _    | _    | _    | FLASH                    |

|                          | _    | _    | _      | _    | RAMS | RAM2 | RAM1 | RAM0 | (Only in F-ZTAT version) |

|                          | _    | _    | _      | _    | _    | _    | _    | _    | _                        |

| DMAOR                    | _    | _    | _      | _    | _    | _    | PR1  | PR0  | DMAC                     |

|                          | _    | _    | _      | _    | _    | AE   | NMIF | DME  | for all channels         |

| SAR_0                    |      |      |        |      |      |      |      |      | DMAC                     |

|                          |      |      |        |      |      |      |      |      | (Channel 0)              |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

| DAR_0                    |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

| DMATCR_0                 | _    | _    | _      | _    | _    | _    | _    | _    |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

| CHCR_0                   | _    | _    | _      | _    | _    | _    | _    | _    |                          |

|                          | _    | _    | _      | _    | _    | RL   | AM   | AL   |                          |

|                          | DM1  | DM0  | SM1    | SM0  | RS3  | RS2  | RS1  | RS0  |                          |

|                          | —    | DS   | ТМ     | TS1  | TS0  | IE   | TE   | DE   |                          |

### A. Pin States

| Pin Fi        | unction              |                          |         |           |         |        | Pin State                 |       |              |                                           |

|---------------|----------------------|--------------------------|---------|-----------|---------|--------|---------------------------|-------|--------------|-------------------------------------------|

|               |                      |                          |         | Reset Sta | ate     |        | Power-<br>Sta             |       |              |                                           |

|               |                      |                          | Po      | ower-On   |         |        |                           |       | -            |                                           |

|               |                      | Expansion<br>without ROM |         | Expansion | Single- | -      | Software                  |       | Bus Master-  | Software<br>Standby in Bus<br>Master-ship |

| Туре          | Pin Name             | 8 bits                   | 16 bits | with ROM  | chip    | Manual | Standby                   | Sleep | ship Release | Release                                   |

| A/D converter | AN0 to AN7           | Z                        | Z       | Z         | Z       | I      | Z                         | I     | I            | Z                                         |

|               | ADTRG                | Z                        | Z       | Z         | Z       | I      | Z                         | I     | I            | Z                                         |

| l²C           | SCL0                 | Z                        | Z       | Z         | Z       | I/O    | Z                         | I/O   | I/O          | Z                                         |

|               | SDA0                 | Z                        | Z       | Z         | Z       | I/O    | Z                         | I/O   | I/O          | Z                                         |

| I/O port      | PA0 to PA15          | Z                        | Z       | Z         | Z       | I/O    | <b>K</b> * <sup>1</sup>   | I/O   | I/O          | K* <sup>1</sup>                           |

|               | PB0 to PB9           | _                        |         |           |         |        |                           |       |              |                                           |

|               | PC0 to PC15          | _                        |         |           |         |        |                           |       |              |                                           |

|               | PD0 to PD15          | -                        |         |           |         |        |                           |       |              |                                           |

|               | PE0 to PE8,<br>PE10  | -                        |         |           |         |        |                           |       |              |                                           |

|               | PE9,<br>PE11 to PE15 | Z                        | Z       | Z         | Z       | I/O    | Z<br>(MZIZE in<br>PPCR=0) | I/O   | I/O          | Z<br>(MZIZE in<br>PPCR=0)                 |

|               |                      |                          |         |           |         |        | <b>K</b> * <sup>1</sup>   |       |              | K* <sup>1</sup>                           |

|               |                      |                          |         |           |         |        | (MZIZE in PPCR=1)         |       |              | (MZIZE in PPCR=1)                         |

|               | PF0 to PF7           | Z                        | Z       | Z         | Z       | I      | Z                         | I     | 1            | Z                                         |

[Legend]

I: Input

O: Output

H: High-level output

L: Low-level output

Z: High-impedance

K: Input pins become high-impedance, and output pins retain their state.

### Table A.2Pin States (SH7145)

| Pin F        | unction          | Pin State       |                 |                 |                 |        |                                                                                    |       |              |                                                                                    |  |  |

|--------------|------------------|-----------------|-----------------|-----------------|-----------------|--------|------------------------------------------------------------------------------------|-------|--------------|------------------------------------------------------------------------------------|--|--|

|              |                  |                 |                 | Reset Sta       | ate             |        | Power-<br>Sta                                                                      |       |              | Software<br>Standby in<br>Bus Master-                                              |  |  |

|              |                  |                 | Р               | ower-On         |                 |        |                                                                                    |       | Bus Master-  |                                                                                    |  |  |

|              |                  | Expar<br>withou | nsion<br>ut ROM | Expansion       | Single-         | _      | Software                                                                           |       |              |                                                                                    |  |  |

| Туре         | Pin Name         | 8 bits          | 16 bits         | with ROM        | chip            | Manual | Standby                                                                            | Sleep | ship Release | ship Release                                                                       |  |  |

| Clock        | СК               | 0               | 0               | 0               | Z               | 0      | H* <sup>1</sup>                                                                    | 0     | 0            | 0                                                                                  |  |  |

|              | XTAL             | 0               | 0               | 0               | 0               | 0      | L                                                                                  | 0     | 0            | L                                                                                  |  |  |

|              | EXTAL            | I               | I               | I               | I               | I      | I                                                                                  | I     | I            | I                                                                                  |  |  |

|              | PLLCAP           | I               | I               | I               | I               | I      | I                                                                                  | I     | I            | I                                                                                  |  |  |

| System       | RES              | 1               | I               | I               | I               | I      | I                                                                                  | I     | I            | I                                                                                  |  |  |

| control      | MRES             | Z               | Z               | Z               | Z               | I      | Z                                                                                  | I     | I            | Z                                                                                  |  |  |

|              | WDTOVF           | 0* <sup>2</sup> | O* <sup>2</sup> | O* <sup>2</sup> | O* <sup>2</sup> | 0      | 0                                                                                  | 0     | 0            | 0                                                                                  |  |  |

|              | BREQ             | Z               | Z               | Z               | Z               | I      | Z                                                                                  | I     | I            | I                                                                                  |  |  |

|              | BACK             | Z               | Z               | Z               | Z               | 0      | Z                                                                                  | 0     | L            | L                                                                                  |  |  |

| Operation    | MD0 to MD3       | I               | I               | I               | I               | I      | I                                                                                  | I     | I            | I                                                                                  |  |  |

| mode control | DBGMD            | 1               | I               | 1               | I               | I      | I                                                                                  | I     | I            | 1                                                                                  |  |  |

|              | FWP              | 1               | I               | 1               | I               | I      | I                                                                                  | I     | I            | 1                                                                                  |  |  |

| Interrupt    | NMI              | 1               | I               | I               | I               | I      | I                                                                                  | I     | I            | I                                                                                  |  |  |

|              | IRQ0 to IRQ3     | Z               | Z               | Z               | Z               | I      | Z* <sup>3</sup>                                                                    | 1     | I            | Z* <sup>3</sup>                                                                    |  |  |

|              | IRQ4 to IRQ7     | Z               | Z               | Z               | Z               | I      | Z* <sup>4</sup>                                                                    | I     | I            | Z* <sup>4</sup>                                                                    |  |  |

|              | IRQOUT<br>(PD30) | Z               | Z               | Z               | Z               | 0      | H* <sup>1</sup>                                                                    | 0     | 0            | H* <sup>1</sup>                                                                    |  |  |

|              | IRQOUT<br>(PE15) | Z               | Z               | Z               | Z               | 0      | Z* <sup>6</sup><br>(MZIZE in<br>PPCR=0)<br>H* <sup>1</sup><br>(MZIZE in<br>PPCR=1) | 0     | 0            | Z* <sup>6</sup><br>(MZIZE in<br>PPCR=0)<br>H* <sup>1</sup><br>(MZIZE in<br>PPCR=1) |  |  |

| Address bus  | A0 to A17        | 0               | 0               | Z               | Z               | 0      | Z                                                                                  | 0     | Z            | Z                                                                                  |  |  |

|              | A18 to A21       | z               | Z               | Z               | z               | 0      | Z                                                                                  | 0     | Z            | Z                                                                                  |  |  |

| Data bus     | D0 to D31        | Z               | Z               | Z               | Z               | I/O    | Z                                                                                  | I/O   | Z            | Z                                                                                  |  |  |

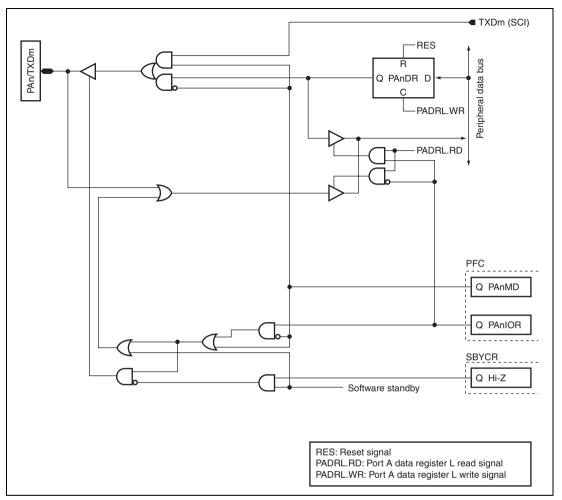

## Figure D.2 PAn/TXDm

|          | Symb          | ol in Figure D.2 | 2                 | Available Products                            |                   |                                               |  |  |  |  |

|----------|---------------|------------------|-------------------|-----------------------------------------------|-------------------|-----------------------------------------------|--|--|--|--|

|          |               |                  |                   | SH7144                                        |                   | SH7145                                        |  |  |  |  |

| Pins     | Pins PAn TXDm |                  | F-ZTAT<br>version | Masked ROM<br>version/<br>ROM less<br>version | F-ZTAT<br>version | Masked ROM<br>version/<br>ROM less<br>version |  |  |  |  |

| PA1/TXD0 | PA1           | TXD0 (SCI)       |                   | $\checkmark$                                  |                   | $\checkmark$                                  |  |  |  |  |

| PA4/TXD1 | PA4           | TXD1 (SCI)       |                   |                                               |                   | $\checkmark$                                  |  |  |  |  |

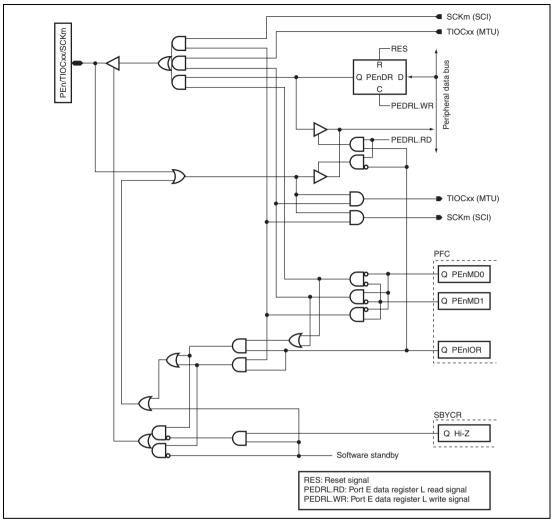

|                     | Syı | mbol in Fig     | gure D.36     | Available Products |              |                   |                                               |  |

|---------------------|-----|-----------------|---------------|--------------------|--------------|-------------------|-----------------------------------------------|--|

|                     |     |                 |               |                    | SH7144       | SH7145            |                                               |  |

| Pins                | PEn | TIOCxx          | SCKm          | F-ZTAT<br>version  |              | F-ZTAT<br>version | Masked ROM<br>version/<br>ROM less<br>version |  |

| PE9/TIOC3B/<br>SCK3 | PE9 | TIOC3B<br>(MTU) | SCK3<br>(SCI) | $\checkmark$       | $\checkmark$ | _                 |                                               |  |

| PE8/TIOC3A/<br>SCK2 | PE8 | TIOC3A<br>(MTU) | SCK2<br>(SCI) |                    | $\checkmark$ |                   |                                               |  |

Rev.4.00 Mar. 27, 2008 Page 848 of 882 REJ09B0108-0400