#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SCI                                                  |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 74                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 112-BQFP                                                                        |

| Supplier Device Package    | 112-QFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f7144fw50v |

|                            |                                                                                 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 10.11 DMA Transfer Example in Cyc      | cle-Steal Mode1                        | 195 |

|-----------------------------------------------|----------------------------------------|-----|

| Figure 10.12 DMA Transfer Example in Bur      | rst Mode 1                             | 195 |

| Figure 10.13 Bus Handling when Multiple C     | Channels Are Operating 1               | 197 |

| Figure 10.14 Cycle Steal, Dual Address and    | Level Detection (Fastest Operation)2   | 200 |

| Figure 10.15 Cycle Steal, Dual Address and    | Level Detection (Normal Operation)2    | 200 |

| Figure 10.16 Cycle Steal, Single Address and  | d Level Detection (Fastest Operation)2 | 200 |

| Figure 10.17 Cycle Steal, Single Address and  | d Level Detection (Normal Operation)2  | 200 |

| Figure 10.18 Burst Mode, Dual Address and     | Level Detection (Fastest Operation)2   | 201 |

| Figure 10.19 Burst Mode, Dual Address and     | Level Detection (Normal Operation)2    | 201 |

| Figure 10.20 Burst Mode, Single Address an    | d Level Detection (Fastest Operation)2 | 201 |

| Figure 10.21 Burst Mode, Single Address an    | d Level Detection (Normal Operation)2  | 202 |

| Figure 10.22 Burst Mode, Dual Address and     | Edge Detection                         | 202 |

| Figure 10.23 Burst Mode, Single Address an    | d Edge Detection2                      | 202 |

|                                               | on2                                    |     |

| Figure 10.25 Source Address Reload Function   | on Timing Chart2                       | 203 |

| Section 11 Multi-Function Timer Pulse Un      | nit (MTU)                              |     |

| Figure 11.1 Block Diagram of MTU              |                                        | 216 |

| Figure 11.2 Complementary PWM Mode Ou         | 11 utput Level Example2                | 254 |

| Figure 11.3 Example of Counter Operation S    | Setting Procedure2                     | 259 |

| Figure 11.4 Free-Running Counter Operation    | n2                                     | 260 |

| Figure 11.5 Periodic Counter Operation        |                                        | 261 |

| Figure 11.6 Example of Setting Procedure for  | or Waveform Output by Compare Match2   | 261 |

| Figure 11.7 Example of 0 Output/1 Output C    | Dperation2                             | 262 |

| Figure 11.8 Example of Toggle Output Oper     | ation2                                 | 262 |

| Figure 11.9 Example of Input Capture Opera    | ation Setting Procedure2               | 263 |

| Figure 11.10 Example of Input Capture Open    | ration2                                | 264 |

|                                               | ation Setting Procedure2               |     |

| Figure 11.12 Example of Synchronous Operation | ation2                                 | 266 |

| Figure 11.13 Compare Match Buffer Operation   | ion2                                   | 267 |

| Figure 11.14 Input Capture Buffer Operation   | 12                                     | 267 |

| Figure 11.15 Example of Buffer Operation S    | etting Procedure2                      | 267 |

| Figure 11.16 Example of Buffer Operation (    | 1)2                                    | 268 |

| Figure 11.17 Example of Buffer Operation (2   | 2)2                                    | 269 |

| Figure 11.18 Cascaded Operation Setting Pro   | ocedure2                               | 270 |

| Figure 11.19 Example of Cascaded Operatio     | n2                                     | 270 |

| Figure 11.20 Example of PWM Mode Settin       | g Procedure2                           | 273 |

| Figure 11.21 Example of PWM Mode Opera        | tion (1)2                              | 273 |

| Figure 11.22 Example of PWM Mode Opera        | tion (2)2                              | 274 |

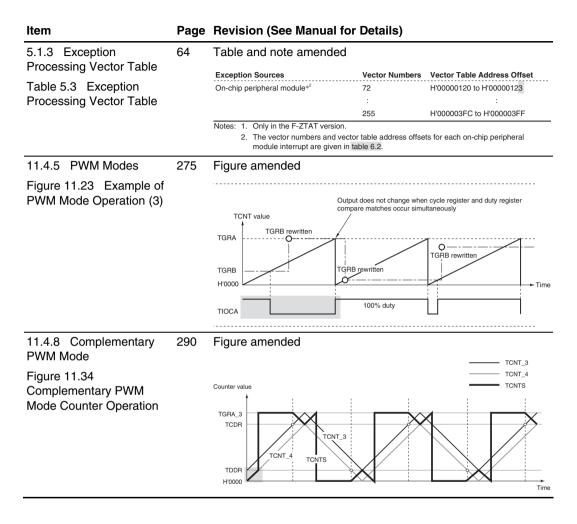

|                                               | tion (3)2                              |     |

| Figure 11.24 Example of Phase Counting Me     | ode Setting Procedure2                 | 276 |

| Figure 11.91   | Error Occurrence in PWM Mode 1, Recovery in Normal Mode             | 345 |

|----------------|---------------------------------------------------------------------|-----|

| -              | Error Occurrence in PWM Mode 1, Recovery in PWM Mode 1              |     |

| •              | Error Occurrence in PWM Mode 1, Recovery in PWM Mode 2              |     |

| •              | Error Occurrence in PWM Mode 1, Recovery in Phase Counting Mode     |     |

| -              | Error Occurrence in PWM Mode 1, Recovery in Complementary PWM       |     |

| U              | Mode                                                                | 349 |

| Figure 11.96   | Error Occurrence in PWM Mode 1, Recovery in Reset-Synchronous PWM   |     |

| U              | Mode                                                                | 350 |

| Figure 11.97   | Error Occurrence in PWM Mode 2, Recovery in Normal Mode             | 351 |

| Figure 11.98   | Error Occurrence in PWM Mode 2, Recovery in PWM Mode 1              | 352 |

| Figure 11.99   | Error Occurrence in PWM Mode 2, Recovery in PWM Mode 2              | 353 |

| -              | Error Occurrence in PWM Mode 2, Recovery in Phase Counting Mode     |     |

| •              | Error Occurrence in Phase Counting Mode, Recovery in Normal Mode    |     |

| •              | Error Occurrence in Phase Counting Mode, Recovery in PWM Mode 1     |     |

| -              | Error Occurrence in Phase Counting Mode, Recovery in PWM Mode 2     |     |

| -              | Error Occurrence in Phase Counting Mode, Recovery in Phase Counting |     |

| 0              | Mode                                                                | 358 |

| Figure 11.105  | Error Occurrence in Complementary PWM Mode, Recovery in Normal      |     |

| 8              | Mode                                                                | 359 |

| Figure 11.106  | Error Occurrence in Complementary PWM Mode, Recovery in PWM         |     |

| 8              | Mode 1                                                              |     |

| Figure 11.107  |                                                                     |     |

| 1.9010 11110,  | Complementary PWM Mode                                              |     |

| Figure 11.108  | Error Occurrence in Complementary PWM Mode, Recovery in             |     |

| 1.80.0         | Complementary PWM Mode                                              |     |

| Figure 11.109  | Error Occurrence in Complementary PWM Mode, Recovery in             |     |

|                | Reset-Synchronous PWM Mode                                          | 363 |

| Figure 11.110  | Error Occurrence in Reset-Synchronous PWM Mode, Recovery in Normal  |     |

| 8              | Mode                                                                | 364 |

| Figure 11.111  | Error Occurrence in Reset-Synchronous PWM Mode, Recovery in PWM     |     |

| U              | Mode 1                                                              | 365 |

| Figure 11.112  | Error Occurrence in Reset-Synchronous PWM Mode, Recovery in         |     |

|                | Complementary PWM Mode                                              | 366 |

| Figure 11.113  | Error Occurrence in Reset-Synchronous PWM Mode, Recovery in         |     |

| 1.80.0 111110  | Reset-Synchronous PWM Mode                                          | 367 |

| Figure 11 114  | POE Block Diagram                                                   |     |

|                | Low-Level Detection Operation                                       |     |

|                | Output-Level Detection Operation                                    |     |

|                | Falling Edge Detection Operation                                    |     |

| 1.5010 11.111/ | running Eage Dettetion operation                                    |     |

# Section 11 Multi-Function Timer Pulse Unit (MTU)

This LSI has an on-chip multi-function timer pulse unit (MTU) that comprises five 16-bit timer channels.

The block diagram is shown in figure 11.1.

### 11.1 Features

- Maximum 16-pulse input/output

- Selection of 8 counter input clocks for each channel

- The following operations can be set for each channel:

- Waveform output at compare match

- Input capture function

- Counter clear operation

- Multiple timer counters (TCNT) can be written to simultaneously

- Simultaneous clearing by compare match and input capture is possible

- Register simultaneous input/output is possible by synchronous counter operation

- A maximum 12-phase PWM output is possible in combination with synchronous operation

- Buffer operation settable for channels 0, 3, and 4

- Phase counting mode settable independently for each of channels 1 and 2

- Cascade connection operation

- Fast access via internal 16-bit bus

- 23 interrupt sources

- Automatic transfer of register data

- A/D converter conversion start trigger can be generated

- Module standby mode can be settable

- A total of six-phase waveform output, which includes complementary PWM output, and positive and negative phases of reset PWM output by interlocking operation of channels 3 and 4, is possible.

- AC synchronous motor (brushless DC motor) drive mode using complementary PWM output and reset PWM output is settable by interlocking operation of channels 0, 3, and 4, and the selection of two types of waveform outputs (chopping and level) is possible.

#### Table 11.12 TIOR\_1 (Channel 1)

|               |               |               |               |                       | Description                                                       |

|---------------|---------------|---------------|---------------|-----------------------|-------------------------------------------------------------------|

| Bit 7<br>IOB3 | Bit 6<br>IOB2 | Bit 5<br>IOB1 | Bit 4<br>IOB0 | TGRB_1<br>Function    | TIOC1B Pin Function                                               |

| 0             | 0             | 0             | 0             | Output                | Output retained*                                                  |

|               |               |               | 1             | compare<br>register   | Initial output is 0                                               |

|               |               |               |               | register              | 0 output at compare match                                         |

|               |               | 1             | 0             | —                     | Initial output is 0                                               |

|               |               |               |               |                       | 1 output at compare match                                         |

|               |               |               | 1             | _                     | Initial output is 0                                               |

|               |               |               |               |                       | Toggle output at compare match                                    |

|               | 1             | 0             | 0             |                       | Output retained                                                   |

|               |               |               | 1             | _                     | Initial output is 1                                               |

|               |               |               |               |                       | 0 output at compare match                                         |

|               |               | 1             | 0             |                       | Initial output is 1                                               |

|               |               |               |               |                       | 1 output at compare match                                         |

|               |               |               | 1             |                       | Initial output is 1                                               |

|               |               |               |               |                       | Toggle output at compare match                                    |

| 1             | 0             | 0             | 0             | Input                 | Input capture at rising edge                                      |

|               |               |               | 1             | capture<br>_ register | Input capture at falling edge                                     |

|               |               | 1             | Х             |                       | Input capture at both edges                                       |

|               | 1             | Х             | Х             | _                     | Input capture at generation of TGRC_0 compare match/input capture |

[Legend]

X: Don't care

Note: \* After power-on reset, 0 is output until TIOR is set.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                 |  |

|-----|----------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------|--|

| 2   | TGIEC    | 0             | R/W | TGR Interrupt Enable C                                                                                                      |  |

|     |          |               |     | Enables or disables interrupt requests (TGIC) by the TGFC bit when the TGFC bit in TSR is set to 1 in channels 0, 3, and 4. |  |

|     |          |               |     | In channels 1 and 2, bit 2 is reserved. It is always read as 0 and the write value should always be 0.                      |  |

|     |          |               |     | 0: Interrupt requests (TGIC) by TGFC bit disabled                                                                           |  |

|     |          |               |     | 1: Interrupt requests (TGIC) by TGFC bit enabled                                                                            |  |

| 1   | TGIEB    | 0             | R/W | TGR Interrupt Enable B                                                                                                      |  |

|     |          |               |     | Enables or disables interrupt requests (TGIB) by the TGFB bit when the TGFB bit in TSR is set to 1.                         |  |

|     |          |               |     | 0: Interrupt requests (TGIB) by TGFB bit disabled                                                                           |  |

|     |          |               |     | 1: Interrupt requests (TGIB) by TGFB bit enabled                                                                            |  |

| 0   | TGIEA    | 0             | R/W | TGR Interrupt Enable A                                                                                                      |  |

|     |          |               |     | Enables or disables interrupt requests (TGIA) by the TGFA bit when the TGFA bit in TSR is set to 1.                         |  |

|     |          |               |     | 0: Interrupt requests (TGIA) by TGFA bit disabled                                                                           |  |

|     |          |               |     | 1: Interrupt requests (TGIA) by TGFA bit enabled                                                                            |  |

### 11.3.11 Timer Output Control Register (TOCR)

TOCR is an 8-bit readable/writable register that enables/disables PWM synchronized toggle output in complementary PWM mode/reset synchronized PWM mode, and controls output level inversion of PWM output.

| Bit    | Bit Name | Initial value | R/W | Description                                                                                                             |  |

|--------|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------|--|

| 7      | _        | 0             | R   | Reserved                                                                                                                |  |

|        |          |               |     | This bit is always read as 0. The write value should always be 0.                                                       |  |

| 6      | PSYE     | 0             | R/W | PWM Synchronous Output Enable                                                                                           |  |

|        |          |               |     | This bit selects the enable/disable of toggle output synchronized with the PWM period.                                  |  |

|        |          |               |     | 0: Toggle output is disabled                                                                                            |  |

|        |          |               |     | 1: Toggle output is enabled                                                                                             |  |

| 5 to 2 | ! —      | All 0         | R   | Reserved                                                                                                                |  |

|        |          |               |     | These bits are always read as 0. The write value should always be 0.                                                    |  |

| 1      | OLSN     | 0             | R/W | Output Level Select N                                                                                                   |  |

|        |          |               |     | This bit selects the reverse phase output level in reset-synchronized PWM mode/complementary PWM mode. See table 11.26  |  |

| 0      | OLSP     | 0             | R/W | Output Level Select P                                                                                                   |  |

|        |          |               |     | This bit selects the positive phase output level in reset-synchronized PWM mode/complementary PWM mode. See table 11.27 |  |

#### Table 11.26 Output Level Select Function

| Bit 1 | Function       |              |            |                      |  |  |  |

|-------|----------------|--------------|------------|----------------------|--|--|--|

|       |                |              | (          | Compare Match Output |  |  |  |

| OLSN  | Initial Output | Active Level | Up Count   | Down Count           |  |  |  |

| 0     | High level     | Low level    | High level | Low level            |  |  |  |

| 1     | Low level      | High level   | Low level  | High level           |  |  |  |

Note: The reverse phase waveform initial output value changes to active level after elapse of the dead time after count start.

| Bit 0 | Function             |              |            |            |  |  |  |

|-------|----------------------|--------------|------------|------------|--|--|--|

|       | Compare Match Output |              |            |            |  |  |  |

| OLSP  | Initial Output       | Active Level | Up Count   | Down Count |  |  |  |

| 0     | High level           | Low level    | Low level  | High level |  |  |  |

| 1     | Low level            | High level   | High level | Low level  |  |  |  |

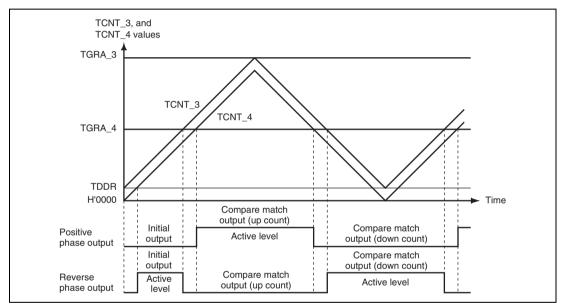

Figure 11.2 shows an example of complementary PWM mode output (1 phase) when OLSN = 1, OLSP = 1.

Figure 11.2 Complementary PWM Mode Output Level Example

### 11.4 Operation

### 11.4.1 Basic Functions

Each channel has a TCNT and TGR register. TCNT performs up-counting, and is also capable of free-running operation, synchronous counting, and external event counting.

Each TGR can be used as an input capture register or output compare register.

Always select MTU external pins set function using the pin function controller (PFC).

#### **Counter Operation:**

When one of bits CST0 to CST4 is set to 1 in TSTR, the TCNT counter for the corresponding channel begins counting. TCNT can operate as a free-running counter, periodic counter, for example.

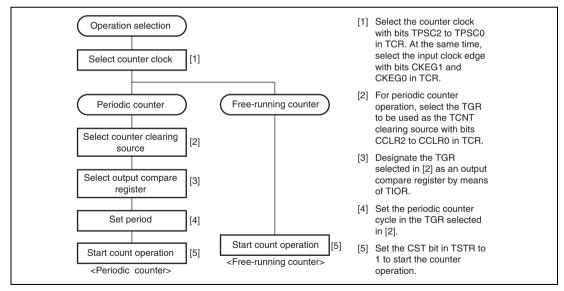

1. Example of Count Operation Setting Procedure

Figure 11.3 shows an example of the count operation setting procedure.

Figure 11.3 Example of Counter Operation Setting Procedure

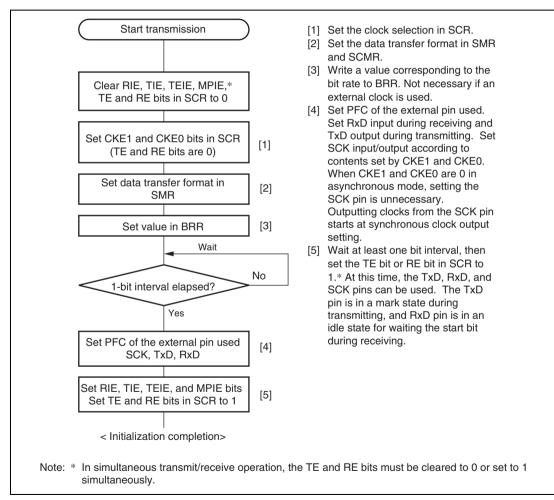

### 13.4.4 SCI Initialization (Asynchronous Mode)

Before transmitting and receiving data, you should first clear the TE and RE bits in SCR to 0, then initialize the SCI as described below. When the operating mode, transfer format, etc., is changed, the TE and RE bits must be cleared to 0 before making the change using the following procedure. When the TE bit is cleared to 0, the TDRE flag is set to 1. Note that clearing the RE bit to 0 does not initialize the contents of the RDRF, PER, FER, and ORER flags, or the contents of RDR. When the external clock is used in asynchronous mode, the clock must be supplied even during initialization.

### Figure 13.5 Sample SCI Initialization Flowchart

### 13.5 Multiprocessor Communication Function

Use of the multiprocessor communication function enables data transfer to be performed among a number of processors sharing communication lines by means of asynchronous serial communication using the multiprocessor format, in which a multiprocessor bit is added to the transfer data. When multiprocessor communication is carried out, each receiving station is addressed by a unique ID code. The serial communication cycle consists of two component cycles: an ID transmission cycle which specifies the receiving station, and a data transmission cycle. The multiprocessor bit is used to differentiate between the ID transmission cycle and the data transmission cycle. If the multiprocessor bit is 1, the cycle is an ID transmission cycle, and if the multiprocessor bit is 0, the cycle is a data transmission cycle. Figure 13.10 shows an example of inter-processor communication using the multiprocessor format. The transmitting station first sends the ID code of the receiving station with which it wants to perform serial communication as data with a 1 multiprocessor bit added. It then sends transmit data as data with a 0 multiprocessor bit added. The receiving station skips data until data with a 1 multiprocessor bit is sent. When data with a 1 multiprocessor bit is received, the receiving station compares that data with its own ID. The station whose ID matches then receives the data sent next. Stations whose ID does not match continue to skip data until data with a 1 multiprocessor bit is again received.

The SCI uses the MPIE bit in SCR to implement this function. When the MPIE bit is set to 1, transfer of receive data from RSR to RDR, error flag detection, and setting the SSR status flags, RDRF, FER, and OER to 1 are inhibited until data with a 1 multiprocessor bit is received. On reception of receive character with a 1 multiprocessor bit, the MPBR bit in SSR is set to 1 and the MPIE bit is automatically cleared, thus normal reception is resumed. If the RIE bit in SCR is set to 1 at this time, an RXI interrupt is generated.

When the multiprocessor format is selected, the parity bit setting is invalid. All other bit settings are the same as those in normal asynchronous mode. The clock used for multiprocessor communication is the same as that in normal asynchronous mode.

When the TE bit is cleared to 0, the transmission section is initialized regardless of the present transmission status.

### 13.9.5 Receive Error Flags and Transmit Operations (Clocked Synchronous Mode Only)

Transmission cannot be started when a receive error flag (ORER, PER, or FER) is set to 1, even if the TDRE flag is cleared to 0. Be sure to clear the receive error flags to 0 before starting transmission. Note also that receive error flags cannot be cleared to 0 even if the RE bit is cleared to 0.

### 13.9.6 Notes on DMAC and DTC Use

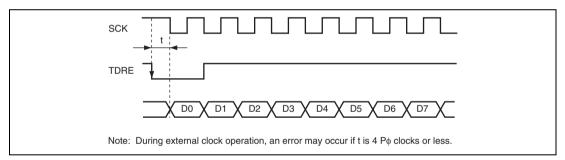

- When using an external clock source for the serial clock, update TDR with the DMAC or the DTC, and then after the elapse of five peripheral clocks (Pφ) or more, input a transmit clock. If a transmit clock is input in the first four Pφ clocks after TDR is written, an error may occur (figure 13.30).

- 2. Before reading the receive data register (RDR) with the DMAC or the DTC, select the receivedata-full (RXI) interrupt of the SCI as a start-up source.

### 13.9.7 Notes on Clocked Synchronous External Clock Mode

- 1. Set TE = RE = 1 only when external clock SCK is 1.

- 2. Do not set TE = RE = 1 until at least four P $\phi$  clocks after external clock SCK has changed from 0 to 1.

- 3. When receiving, RDRF is 1 when RE is cleared to 0 after 2.5 to 3.5 Pφ clocks from the rising edge of the RxD D7 bit SCK input, but copying to RDR is not possible.

| Register | Bit | Bit Name | Initial<br>Value | R/W | Description                                      |

|----------|-----|----------|------------------|-----|--------------------------------------------------|

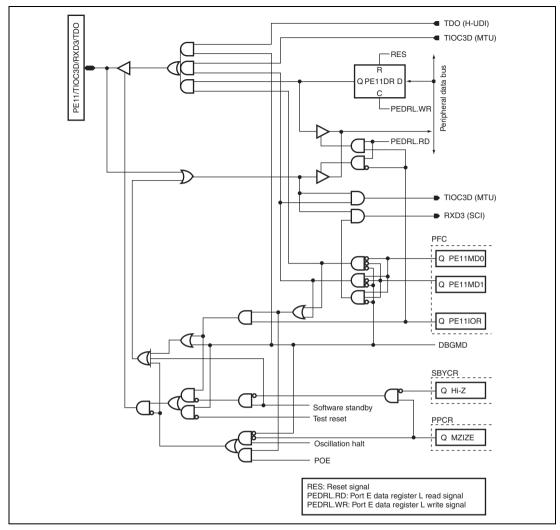

| PECRL1   | 7   | PE11MD1  | 0                | R/W | PE11 Mode                                        |

| PECRL1   | 6   | PE11MD0  | 0                | R/W | Select the function of the PE11/TIOC3D/RXD3 pin. |

|          |     |          |                  |     | 00: PE11 I/O (port)                              |

|          |     |          |                  |     | 01: TIOC3D I/O (MTU)                             |

|          |     |          |                  |     | 10: Setting prohibited                           |

|          |     |          |                  |     | 11: RXD3 input (SCI)                             |

| PECRL1   | 5   | PE10MD1  | 0                | R/W | PE10 Mode                                        |

| PECRL1   | 4   | PE10MD0  | 0                | R/W | Select the function of the PE10/TIOC3C/TXD2 pin. |

|          |     |          |                  |     | 00: PE10 I/O (port)                              |

|          |     |          |                  |     | 01: TIOC3C I/O (MTU)                             |

|          |     |          |                  |     | 10: TXD2 output (SCI)                            |

|          |     |          |                  |     | 11: Setting prohibited                           |

| PECRL1   | 3   | PE9MD1   | 0                | R/W | PE9 Mode                                         |

| PECRL1   | 2   | PE9MD0   | 0                | R/W | Select the function of the PE9/TIOC3B/SCK3 pin.  |

|          |     |          |                  |     | 00: PE9 I/O (port)                               |

|          |     |          |                  |     | 01: TIOC3B I/O (MTU)                             |

|          |     |          |                  |     | 10: Setting prohibited                           |

|          |     |          |                  |     | 11: SCK3 I/O (SCI)                               |

| PECRL1   | 1   | PE8MD1   | 0                | R/W | PE8 Mode                                         |

| PECRL1   | 0   | PE8MD0   | 0                | R/W | Select the function of the PE8/TIOC3A/SCK2 pin.  |

|          |     |          |                  |     | 00: PE8 I/O (port)                               |

|          |     |          |                  |     | 01: TIOC3A I/O (MTU)                             |

|          |     |          |                  |     | 10: SCK2 I/O (SCI)                               |

|          |     |          |                  |     | 11: Setting prohibited                           |

| PECRL2   | 15  | PE7MD1   | 0                | R/W | PE7 Mode                                         |

| PECRL2   | 14  | PE7MD0   | 0                | R/W | Select the function of the PE7/TIOC2B/RXD2 pin.  |

|          |     |          |                  |     | 00: PE7 I/O (port)                               |

|          |     |          |                  |     | 01: TIOC2B I/O (MTU)                             |

|          |     |          |                  |     | 10: RXD2 input (SCI)                             |

|          |     |          |                  |     | 11: Setting prohibited                           |

| Bit | Bit Name | Initial Value | R/W | Description     |

|-----|----------|---------------|-----|-----------------|

| 7   | PF7DR    | 0/1*          | R   | See table 18.6* |

| 6   | PF6DR    | 0/1*          | R   | _               |

| 5   | PF5DR    | 0/1*          | R   | _               |

| 4   | PF4DR    | 0/1*          | R   | _               |

| 3   | PF3DR    | 0/1*          | R   | _               |

| 2   | PF2DR    | 0/1*          | R   | _               |

| 1   | PF1DR    | 0/1*          | R   | _               |

| 0   | PF0DR    | 0/1*          | R   | _               |

Notes: \* Initial values are dependent on the state of the pins.

### Table 18.6 Port F Data Register (PFDR) Read/Write Operations

• Bits 7 to 0

| Pin Function             | Read      | Write                            |

|--------------------------|-----------|----------------------------------|

| General input            | Pin state | Ignored (no effect on pin state) |

| ANn input (analog input) | 1         | Ignored (no effect on pin state) |

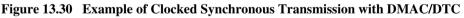

Figure 19.12 Power On/Off Timing (User Program Mode)

### 24.4 Usage Notes

#### 24.4.1 I/O Port Status

When a transition is made to software standby mode while the port high-impedance bit (HIZ) in SBYCR is 0, I/O port states are retained. Therefore, there is no reduction in current consumption for the output current when a high-level signal is output.

#### 24.4.2 Current Consumption during Oscillation Stabilization Wait Period

Current consumption increases during the oscillation stabilization wait period.

#### 24.4.3 On-Chip Peripheral Module Interrupt

Relevant interrupt operations cannot be performed in module standby mode. Consequently, if the CPU enters module standby mode while an interrupt has been requested, it will not be possible to clear the CPU interrupt source or the DMAC/DTC activation source.

Interrupts should therefore be disabled before entering module standby mode.

### 24.4.4 Writing to MSTCR1 and MSTCR2

MSTCR1 and MSTCR2 should only be written to by the CPU.

### 24.4.5 DMAC, DTC, or AUD Operation in Sleep Mode

In sleep mode, data should not be accessed by the DMAC, DTC, or AUD.

| Register<br>abbreviation | Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  | Module          |

|--------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|

| TCR_3                    | CCLR2 | CCLR1 | CCLR0 | CKEG1 | CKEG0 | TPSC2 | TPSC1 | TPSC0 | MTU             |

| TCR_4                    | CCLR2 | CCLR1 | CCLR0 | CKEG1 | CKEG0 | TPSC2 | TPSC1 | TPSC0 | (Channels 3, 4) |

| TMDR_3                   | _     | _     | BFB   | BFA   | MD3   | MD2   | MD1   | MD0   |                 |

| TMDR_4                   | _     | _     | BFB   | BFA   | MD3   | MD2   | MD1   | MD0   |                 |

| TIORH_3                  | IOB3  | IOB2  | IOB1  | IOB0  | IOA3  | IOA2  | IOA1  | IOA0  |                 |

| TIORL_3                  | IOD3  | IOD2  | IOD1  | IOD0  | IOC3  | IOC2  | IOC1  | IOC0  |                 |

| TIORH_4                  | IOB3  | IOB2  | IOB1  | IOB0  | IOA3  | IOA2  | IOA1  | IOA0  |                 |

| TIORL_4                  | IOD3  | IOD2  | IOD1  | IOD0  | IOC3  | IOC2  | IOC1  | IOC0  |                 |

| TIER_3                   | TTGE  | _     | _     | TCIEV | TGIED | TGIEC | TGIEB | TGIEA |                 |

| TIER_4                   | TTGE  | _     | _     | TCIEV | TGIED | TGIEC | TGIEB | TGIEA |                 |

| TOER                     | _     | _     | OE4D  | OE4C  | OE3D  | OE4B  | OE4A  | OE3B  |                 |

| TOCR                     | _     | PSYE  | _     | _     | _     | _     | OLSN  | OLSP  |                 |

| TGCR                     | _     | BDC   | Ν     | Р     | FB    | WF    | VF    | UF    |                 |

| TCNT_3                   |       |       |       |       |       |       |       |       |                 |

| TCNT_4                   |       |       |       |       |       |       |       |       |                 |

| TCDR                     |       |       |       |       |       |       |       |       | _               |

| TDDR                     |       |       |       |       |       |       |       |       |                 |

| TGRA_3                   |       |       |       |       |       |       |       |       |                 |

| TGRB_3                   |       |       |       |       |       |       |       |       |                 |

| TGRA_4                   |       |       |       |       |       |       |       |       | _               |

| TGRB_4                   |       |       |       |       |       |       |       |       | _               |

| TCNTS                    |       |       |       |       |       |       |       |       | _               |

| TCBR                     |       |       |       |       |       |       |       |       |                 |

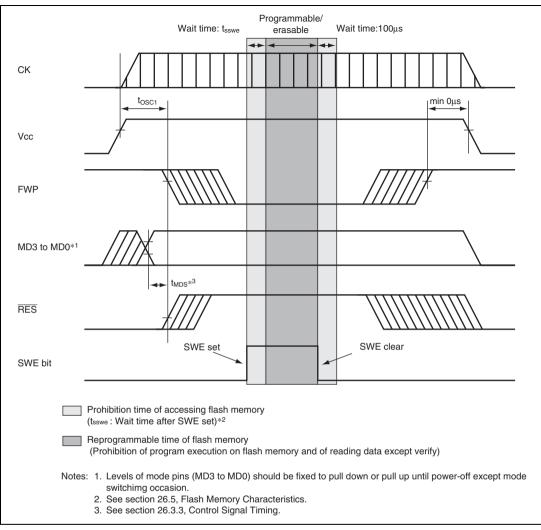

|                   | Symb            | ol in Fig      | ure D.16          | Available Products                            |                   |                                               |   |  |  |

|-------------------|-----------------|----------------|-------------------|-----------------------------------------------|-------------------|-----------------------------------------------|---|--|--|

|                   |                 |                |                   | S                                             | SH7144            | SH7145                                        |   |  |  |

| Pins              | s PBn IRQm POEm |                | F-ZTAT<br>version | Masked ROM<br>version/<br>ROM less<br>version | F-ZTAT<br>version | Masked ROM<br>version/<br>ROM less<br>version |   |  |  |

| PB4/IRQ2/<br>POE2 | PB4             | IRQ2<br>(INTC) | POE2<br>(POE)     | $\checkmark$                                  | _                 | $\checkmark$                                  | _ |  |  |

| PB5/IRQ3/<br>POE3 | PB5             | IRQ3<br>(INTC) | POE3<br>(POE)     |                                               |                   |                                               | _ |  |  |

Rev.4.00 Mar. 27, 2008 Page 828 of 882 REJ09B0108-0400

|                          | Symbol in Figure D.55 |                 |               |                | Available Products |                                               |                   |                                               |  |

|--------------------------|-----------------------|-----------------|---------------|----------------|--------------------|-----------------------------------------------|-------------------|-----------------------------------------------|--|

|                          |                       |                 |               |                | :                  | SH7144                                        | SH7145            |                                               |  |

| Pins                     | PE11                  | TIOC3D          | RXD3          | TDO            | F-ZTAT<br>version  | Masked ROM<br>version/<br>ROM less<br>version | F-ZTAT<br>version | Masked ROM<br>version/<br>ROM less<br>version |  |

| PE11/TIOC3D/<br>RXD3/TDO | PE11                  | TIOC3D<br>(MTU) | RXD3<br>(SCI) | TDO<br>(H-UDI) | _                  | —                                             |                   | _                                             |  |

# Main Revisions for this Edition