Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SCI                                                  |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 98                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f7145fw50v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 11.25 | Example of Phase Counting Mode 1 Operation                            | 277 |

|--------------|-----------------------------------------------------------------------|-----|

| -            | Example of Phase Counting Mode 2 Operation                            |     |

| -            | Example of Phase Counting Mode 3 Operation                            |     |

| Figure 11.28 |                                                                       |     |

| -            | Phase Counting Mode Application Example                               |     |

|              | Procedure for Selecting Reset-Synchronized PWM Mode                   |     |

|              | Reset-Synchronized PWM Mode Operation Example                         |     |

| C            | (When TOCR's OLSN = 1 and OLSP = 1)                                   | 284 |

| Figure 11.32 | Block Diagram of Channels 3 and 4 in Complementary PWM Mode           |     |

| -            | Example of Complementary PWM Mode Setting Procedure                   |     |

| -            | Complementary PWM Mode Counter Operation                              |     |

| Figure 11.35 | Example of Complementary PWM Mode Operation                           | 292 |

| Figure 11.36 | Example of PWM Cycle Updating                                         | 294 |

|              | Example of Data Update in Complementary PWM Mode                      |     |

| Figure 11.38 | Example of Initial Output in Complementary PWM Mode (1)               |     |

| Figure 11.39 | Example of Initial Output in Complementary PWM Mode (2)               | 298 |

| Figure 11.40 | Example of Complementary PWM Mode Waveform Output (1)                 |     |

| Figure 11.41 | Example of Complementary PWM Mode Waveform Output (2)                 | 300 |

| Figure 11.42 | Example of Complementary PWM Mode Waveform Output (3)                 | 301 |

| Figure 11.43 | Example of Complementary PWM Mode 0% and 100% Waveform Output         |     |

|              | (1)                                                                   | 301 |

| Figure 11.44 | Example of Complementary PWM Mode 0% and 100% Waveform Output         |     |

|              | (2)                                                                   | 302 |

| Figure 11.45 | Example of Complementary PWM Mode 0% and 100% Waveform Output         |     |

|              | (3)                                                                   | 302 |

| Figure 11.46 | Example of Complementary PWM Mode 0% and 100% Waveform Output         |     |

|              | (4)                                                                   | 303 |

| Figure 11.47 | Example of Complementary PWM Mode 0% and 100% Waveform Output         |     |

|              | (5)                                                                   | 303 |

| Figure 11.48 | Example of Toggle Output Waveform Synchronized with PWM Output        | 304 |

| Figure 11.49 | Counter Clearing Synchronized with Another Channel                    | 305 |

| Figure 11.50 | Example of Output Phase Switching by External Input (1)               | 306 |

| Figure 11.51 | Example of Output Phase Switching by External Input (2)               | 307 |

| Figure 11.52 | Example of Output Phase Switching by Means of UF, VF, WF Bit Settings |     |

|              | (1)                                                                   | 307 |

| Figure 11.53 | Example of Output Phase Switching by Means of UF, VF, WF Bit Settings |     |

|              | (2)                                                                   | 308 |

| -            | Count Timing in Internal Clock Operation                              |     |

| -            | Count Timing in External Clock Operation                              |     |

| Figure 11.56 | Count Timing in External Clock Operation (Phase Counting Mode)        | 313 |

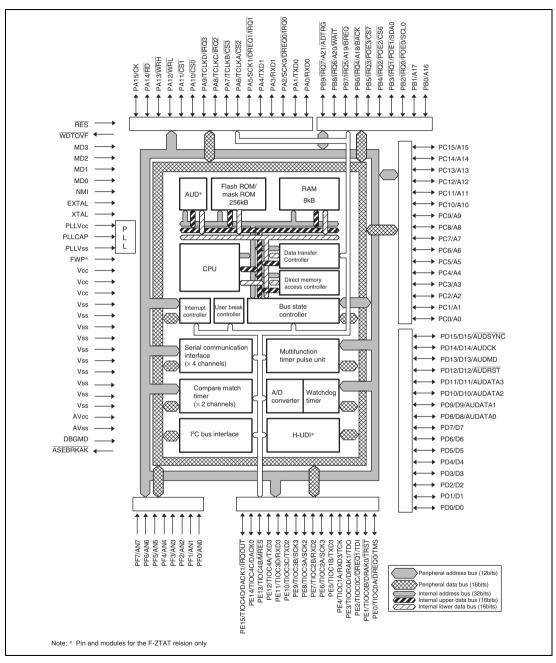

# 1.2 Internal Block Diagram

Figure 1.1 Internal Block Diagram of SH7144

Rev.4.00 Mar. 27, 2008 Page 4 of 882 REJ09B0108-0400

| Instruct | ion            | Instruction Code | Operation                                                              | Execution<br>States | T<br>Bit |

|----------|----------------|------------------|------------------------------------------------------------------------|---------------------|----------|

| MOV.B    | @(R0,Rm),Rn    | 0000nnnnmmm1100  | $(R0 + Rm) \rightarrow Sign$ extension $\rightarrow Rn$                | 1                   | —        |

| MOV.W    | @(R0,Rm),Rn    | 0000nnnnmmm1101  | $(R0 + Rm) \rightarrow Sign$<br>extension $\rightarrow Rn$             | 1                   | —        |

| MOV.L    | @(R0,Rm),Rn    | 0000nnnnmmm1110  | $(R0 + Rm) \rightarrow Rn$                                             | 1                   |          |

| MOV.B    | R0,@(disp,GBR) | 11000000ddddddd  | $R0 \rightarrow (disp + GBR)$                                          | 1                   | _        |

| MOV.W    | R0,@(disp,GBR) | 11000001ddddddd  | $R0 \rightarrow (disp \times 2 + GBR)$                                 | 1                   | _        |

| MOV.L    | R0,@(disp,GBR) | 11000010ddddddd  | $R0 \rightarrow (disp \times 4 + GBR)$                                 | 1                   |          |

| MOV.B    | @(disp,GBR),R0 | 11000100ddddddd  | (disp + GBR) $\rightarrow$ Sign extension $\rightarrow$ R0             | 1                   | —        |

| MOV.W    | @(disp,GBR),R0 | 11000101ddddddd  | $(disp \times 2 + GBR) \rightarrow Sign$<br>extension $\rightarrow R0$ | 1                   | —        |

| MOV.L    | @(disp,GBR),R0 | 11000110ddddddd  | $(disp\times 4+GBR)\toR0$                                              | 1                   | _        |

| MOVA     | @(disp,PC),R0  | 11000111ddddddd  | $\text{disp} \times 4 + \text{PC} \rightarrow \text{R0}$               | 1                   | _        |

| MOVT     | Rn             | 0000nnnn00101001 | $T \rightarrow Rn$                                                     | 1                   | _        |

| SWAP.B   | Rm,Rn          | 0110nnnnmmm1000  | $Rm \rightarrow Swap bottom two bytes \rightarrow Rn$                  | 1                   | —        |

| SWAP.W   | Rm,Rn          | 0110nnnnmmm1001  | $Rm \rightarrow Swap two$ consecutive words $\rightarrow Rn$           | 1                   | —        |

| XTRCT    | Rm,Rn          | 0010nnnnmmm1101  | Rm: Middle 32 bits of Rn $\rightarrow$ Rn                              | 1                   | —        |

The clock mode is selected by the input of MD2 and MD3 pins.

|                | Pin Setting |     | Clock Ratio (when input clock is 1) |                          |                             |  |

|----------------|-------------|-----|-------------------------------------|--------------------------|-----------------------------|--|

| Clock Mode No. | MD3         | MD2 | System clock (φ)                    | Peripheral<br>clock (Pø) | System clock<br>output (CK) |  |

| 0              | 0           | 0   | ×1                                  | ×1                       | ×1                          |  |

| 1              | 0           | 1   | ×2                                  | ×2                       | ×2                          |  |

| 2              | 1           | 0   | ×4                                  | ×4*                      | ×4                          |  |

| 3              | 1           | 1   | ×4                                  | ×2                       | ×4                          |  |

|                |             |     |                                     |                          |                             |  |

#### Table 3.2 Clock Mode Setting

Note: \* The maximum clock input frequency is 10MHz because the p∳ is specified as 40MHz or less.

## 6.4 Interrupt Sources

There are five types of interrupt sources: NMI, user breaks, H-UDI, IRQ, and on-chip peripheral modules. Each interrupt has a priority expressed as a priority level (0 to 16, with 0 the lowest and 16 the highest). Giving an interrupt a priority level of 0 masks it.

#### 6.4.1 External Interrupts

**NMI Interrupts:** The NMI interrupt has priority 16 and is always accepted. Input at the NMI pin is detected by edge. Use the NMI edge select bit (NMIE) in the interrupt control register 1 (ICR1) to select either the rising or falling edge. NMI interrupt exception processing sets the interrupt mask level bits (I3 to I0) in the status register (SR) to level 15.

**IRQ Interrupts:** IRQ interrupts are requested by input from pins  $\overline{IRQ0}$  to  $\overline{IRQ7}$ . Set the IRQ sense select bits (IRQ0S to IRQ7S) of the interrupt control register 1 (ICR1) and IRQ edge select bit (IRQ0ES[1:0] to IRQ7ES[1:0]) of the interrupt control register 2 (ICR2) to select low level detection, falling edge detection, or rising edge detection for each pin. The priority level can be set from 0 to 15 for each pin using the interrupt priority registers A and B (IPRA and IPRB).

When IRQ interrupts are set to low level detection, an interrupt request signal is sent to the INTC during the period the  $\overline{IRQ}$  pin is low level. Interrupt request signals are not sent to the INTC when the  $\overline{IRQ}$  pin becomes high level. Interrupt request levels can be confirmed by reading the IRQ flags (IRQ0F to IRQ7F) of the IRQ status register (ISR).

When IRQ interrupts are set to falling edge detection, interrupt request signals are sent to the INTC upon detecting a change on the  $\overline{IRQ}$  pin from high to low level. The results of detection for IRQ interrupt request are maintained until the interrupt request is accepted. It is possible to confirm that IRQ interrupt requests have been detected by reading the IRQ flags (IRQ0F to IRQ7F) of the IRQ status register (ISR), and by writing a 0 after reading a 1, IRQ interrupt request detection results can be cleared

In IRQ interrupt exception processing, the interrupt mask bits (I3 to I0) of the status register (SR) are set to the priority level value of the accepted IRQ interrupt. Figure 6.2 shows the block diagram of this IRQ7 to IRQ0 interrupts.

#### 11.3.12 Timer Gate Control Register (TGCR)

TGCR is an 8-bit readable/writable register that controls the waveform output necessary for brushless DC motor control in reset-synchronized PWM mode/complementary PWM mode. These register settings are ineffective for anything other than complementary PWM mode/reset-synchronized PWM mode.

| Bit | Bit Name | Initial value | R/W | Description                                                                                                                                                                |

|-----|----------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | —        | 1             | R   | Reserved                                                                                                                                                                   |

|     |          |               |     | This bit is always read as 1. The write value should always be 1.                                                                                                          |

| 6   | BDC      | 0             | R/W | Brushless DC Motor                                                                                                                                                         |

|     |          |               |     | This bit selects whether to make the functions of this register (TGCR) effective or ineffective.                                                                           |

|     |          |               |     | 0: Ordinary output                                                                                                                                                         |

|     |          |               |     | 1: Functions of this register are made effective                                                                                                                           |

| 5   | Ν        | 0             | R/W | Reverse Phase Output (N) Control                                                                                                                                           |

|     |          |               |     | This bit selects whether the level output or the reset-<br>synchronized PWM/complementary PWM output<br>while the reverse pins (TIOC3D, TIOC4C, and<br>TIOC4D) are output. |

|     |          |               |     | 0: Level output                                                                                                                                                            |

|     |          |               |     | <ol> <li>Reset synchronized PWM/complementary PWM<br/>output</li> </ol>                                                                                                    |

| 4   | Р        | 0             | R/W | Positive Phase Output (P) Control                                                                                                                                          |

|     |          |               |     | This bit selects whether the level output or the reset-<br>synchronized PWM/complementary PWM output<br>while the positive pin (TIOC3B, TIOC4A, and<br>TIOC4B) are output. |

|     |          |               |     | 0: Level output                                                                                                                                                            |

|     |          |               |     | 1: Reset synchronized PWM/complementary PWM<br>output                                                                                                                      |

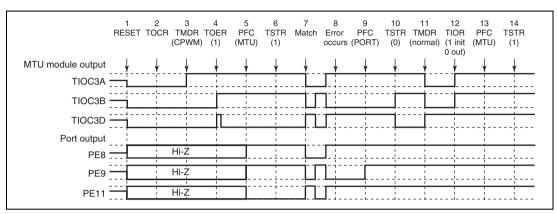

**Operation when Error Occurs during Reset-Synchronous PWM Mode Operation, and Operation is Restarted in Normal Mode:** Figure 11.110 shows an explanatory diagram of the case where an error occurs in reset-synchronous PWM mode and operation is restarted in normal mode after re-setting.

Figure 11.110 Error Occurrence in Reset-Synchronous PWM Mode, Recovery in Normal Mode

- 1. After a reset, MTU output is low and ports are in the high-impedance state.

- 2. Select the reset-synchronous PWM output level and cyclic output enabling/disabling with TOCR.

- 3. Set reset-synchronous PWM.

- 4. Enable channel 3 and 4 output with TOER.

- 5. Set MTU output with the PFC.

- 6. The count operation is started by TSTR.

- 7. The reset-synchronous PWM waveform is output on compare-match occurrence.

- 8. An error occurs.

- 9. Set port output with the PFC and output the inverse of the active level.

- 10. The count operation is stopped by TSTR. (MTU output becomes the reset-synchronous PWM output initial value.)

- 11. Set normal mode. (MTU positive phase output is low, and negative phase output is high.)

- 12. Initialize the pins with TIOR.

- 13. Set MTU output with the PFC.

- 14. Operation is restarted by TSTR.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | TE       | 0             | R/W | Transmit Enable                                                                                                                                                                                                                                                                                                                                                          |

|     |          |               |     | When this bit is set to 1, transmission is enabled.                                                                                                                                                                                                                                                                                                                      |

|     |          |               |     | In this state, serial transmission is started when transmit data is written to TDR and the TDRE flag in SSR is cleared to 0.                                                                                                                                                                                                                                             |

|     |          |               |     | SMR setting must be made to decide the transfer<br>format before setting the TE bit to 1. When this bit is<br>cleared to 0, transmit operation is disabled, and the<br>TDRE flag in SSR is fixed to 1.                                                                                                                                                                   |

| 4   | RE       | 0             | R/W | Receive Enable                                                                                                                                                                                                                                                                                                                                                           |

|     |          |               |     | When this bit is set to 1, reception is enabled.                                                                                                                                                                                                                                                                                                                         |

|     |          |               |     | Serial reception is started in this state when a start<br>bit is detected in asynchronous mode or synchronous<br>clock input is detected in clocked synchronous mode.                                                                                                                                                                                                    |

|     |          |               |     | SMR setting must be made to decide the receive format before setting the RE bit to 1.                                                                                                                                                                                                                                                                                    |

|     |          |               |     | Clearing the RE bit to 0 disables reception and does<br>not affect the RDRF, FER, PER, and ORER flags,<br>which retain their states.                                                                                                                                                                                                                                     |

| 3   | MPIE     | 0             | R/W | Multiprocessor Interrupt Enable (enabled only when the MP bit in SMR is 1 in asynchronous mode)                                                                                                                                                                                                                                                                          |

|     |          |               |     | When this bit is set to 1, receive data in which the multiprocessor bit is 0 is skipped, and setting of the RDRF, FER, and ORER status flags in SSR is prohibited. On receiving data in which the multiprocessor bit is 1, this bit is automatically cleared and normal reception is resumed. For details, refer to section 13.5, Multiprocessor Communication Function. |

|     |          |               |     | When receive data including MPB = 0 is received,<br>receive data transfer from RSR to RDR, receive error<br>detection, and setting of the RDRF, FER, and ORER<br>flags in SSR, are not performed.                                                                                                                                                                        |

|     |          |               |     | When receive data including MPB = 1 is received,<br>the MPB bit in SSR is set to 1, the MPIE bit is<br>cleared to 0 automatically, and generation of RXI and<br>ERI interrupts (when the TIE and RIE bits in SCR are<br>set to 1) and FER and ORER flag setting are<br>enabled.                                                                                          |

#### 13.3.8 Serial Direction Control Register (SDCR)

SDCR selects LSB-first or MSB-first transfer and sets the smart card interface. With an 8-bit data length, LSB-first/MSB-first selection is available regardless of the communication mode. With a 7-bit data length, LSB-first transfer must be selected. The description in this section assumes LSB-first transfer.

| s be 1. Operation<br>written.<br>nversion direction.                                  |

|---------------------------------------------------------------------------------------|

| written.                                                                              |

| version direction.                                                                    |

| version direction.                                                                    |

|                                                                                       |

|                                                                                       |

|                                                                                       |

| hen the transfer data<br>a, LSB-first is fixed.                                       |

|                                                                                       |

| a logic level. The SINV<br>evel of the parity bit. To<br>$0/\overline{E}$ bit in SMR. |

| card interface mode. In<br>or clocked synchronous                                     |

| ted as they are. Receive<br>DR                                                        |

| before being<br>is stored in inverted form                                            |

|                                                                                       |

| nd cannot be modified.                                                                |

| Select                                                                                |

| e SCI operate in smart                                                                |

| de or clocked                                                                         |

| )                                                                                     |

|                                                                                       |

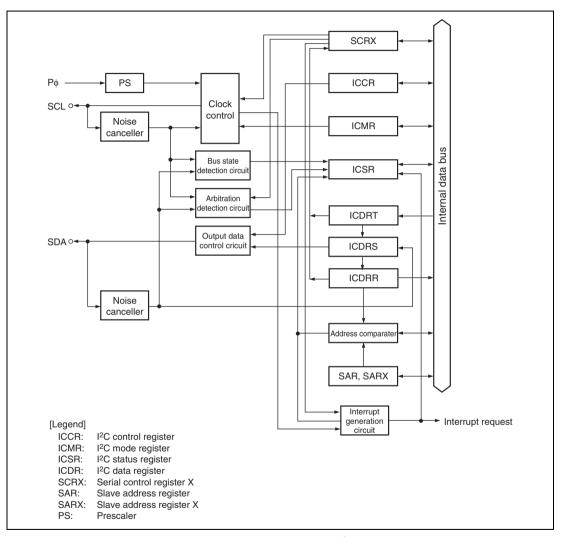

Figure 14.1 is a block diagram of the  $I^2C$  bus interface. Figure 14.2 shows an example of the connection of  $I^2C$  bus interfaces. Since the I/O pins are driven only by the NMOS transistor, they operate in the same way as pins driven by an open-drain NMOS transistor. The voltage that can be applied to the I/O pins depends on the supply voltage of the LSI.

Figure 14.1 A Block Diagram of the I<sup>2</sup>C Bus Interface

#### 14.3.7 Serial Control Register X (SCRX)

SCRX enables or disables  $I^2C$  bus interface interrupts and confirms the state of reception and transmission.

| Bit  | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                            |

|------|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6 | _        | All 0         | R   | Reserved                                                                                                                                                                                                               |

|      |          |               |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                   |

| 5    | IICX     | 0             | R/W | I <sup>2</sup> C Transfer Rate Select                                                                                                                                                                                  |

|      |          |               |     | Along with bits CKS2 to CKS0 in the I <sup>2</sup> C bus mode register (ICMR), this bit selects the transfer rate in the master mode. For details on setting the transfer rate, see table 14.3.                        |

| 4    | IICE     | 0             | R/W | I <sup>2</sup> C master Enable                                                                                                                                                                                         |

|      |          |               |     | This bit controls access by the CPU to the I <sup>2</sup> C bus<br>interface registers (ICCR, ICSR, ICDR/SARX, and<br>ICMR/SAR) of the I <sup>2</sup> C bus interface.                                                 |

|      |          |               |     | 0: Disables CPU access to the registers of the I <sup>2</sup> C bus interface.                                                                                                                                         |

|      |          |               |     | <ol> <li>Enables CPU access to the registers of the I<sup>2</sup>C bus<br/>interface.</li> </ol>                                                                                                                       |

| 3    | HNDS     | 0             | R/W | Hand-Shake Receive Select                                                                                                                                                                                              |

|      |          |               |     | This bit enables/disables continuous reception in receive mode.                                                                                                                                                        |

|      |          |               |     | When the HNDS bit is cleared to 0, receive operation<br>is performed continuously after data has been received<br>successfully while ICDRF flag is 0.                                                                  |

|      |          |               |     | When the HNDS bit is set to 1, SCL is fixed to the low level thus disabling the next data to be transferred. The bus line is released and next frame receive operation is enabled by reading the receive data in ICDR. |

| 2    | _        | 0             | R   | Reserved                                                                                                                                                                                                               |

|      |          |               |     | This bit is always read as 0. The write value should always be 0.                                                                                                                                                      |

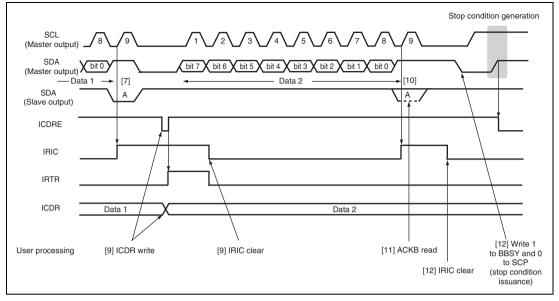

Figure 14.9 An Example of the Stop Condition Issuance Timing in Master Transmit Mode (MLS = WAIT = 0)

- 14. Confirm that the ICDRF flag is set to 1, and then read ICDR.

- 15. Clear the IRIC flag to 0.

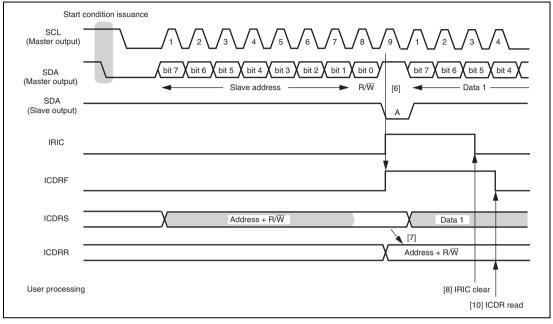

Figure 14.21 An Example of the Timing of Operations in Slave Receive Mode 1 (MLS = ACKB = 0, HNDS = 0)

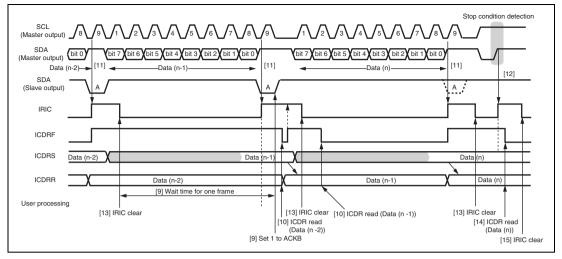

Figure 14.22 An Example of the Timing of Operations in Slave Receive Mode 2 (MLS = ACKB = 0, HNDS = 0)

#### 15.3.3 A/D Control Register\_0, 1 (ADCR\_0, ADCR\_1)

ADCR for each module controls A/D conversion started by an external trigger signal and selects the operating clock.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TRGE     | 0             | R/W | Trigger Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |               |     | Enables or disables triggering of A/D conversion by ADTRG or an MTU trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |               |     | 0: A/D conversion triggering is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |               |     | 1: A/D conversion triggering is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6   | CKS1     | 0             | R/W | Clock Select 1, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | CKS0     | 0             | R/W | Select the A/D conversion time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |          |               |     | 00: Pþ/32<br>01: Pþ/16<br>10: Pþ/8<br>11: Pþ/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |               |     | When changing the operating mode, first clear the ADST bit in the A/D control registers (ADCR) to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |               |     | $CKS[1,0]$ = b'11 can be set while $P\varphi \leq 25~MHz.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | ADST     | 0             | R/W | A/D Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |          |               |     | Starts or stops A/D conversion. When this bit is set to<br>1, A/D conversion is started. When this bit is cleared<br>to 0, A/D conversion is stopped and the A/D<br>converter enters the idle state. In single or single-<br>cycle scan mode, this bit is automatically cleared to 0<br>when A/D conversion ends on the selected single<br>channel. In continuous scan mode, A/D conversion is<br>continuously performed for the selected channels in<br>sequence until this bit is cleared by a software, reset,<br>or in software standby mode, or module standby<br>mode. |

| 3   | ADCS     | 0             | R/W | A/D Continuous Scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |          |               |     | Selects either single-cycle scan or continuous scan in scan mode. This bit is valid only when scan mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |               |     | 0: Single-cycle scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |               |     | 1: Continuous scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |               |     | When changing the operating mode, first clear the ADST bit in the A/D control registers (ADCR) to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Register | Bit | Bit Name | Initial<br>Value        | R/W | Description                                                        |  |

|----------|-----|----------|-------------------------|-----|--------------------------------------------------------------------|--|

| PACRL1   | 6   | PA11MD   | <b>0</b> * <sup>3</sup> | R/W | PA11 Mode                                                          |  |

|          |     |          |                         |     | Selects the function of the PA11/ $\overline{\text{CS1}}$ pin.     |  |

|          |     |          |                         |     | 0: PA11 I/O (port)                                                 |  |

|          |     |          |                         |     | 1: CS1 output (BSC)                                                |  |

| PACRL1   | 4   | PA10MD   | <b>0</b> * <sup>3</sup> | R/W | PA10 Mode                                                          |  |

|          |     |          |                         |     | Selects the function of the PA10/ $\overline{\text{CS0}}$ pin.     |  |

|          |     |          |                         |     | 0: PA10 I/O (port)                                                 |  |

|          |     |          |                         |     | 1: CS0 output (BSC)                                                |  |

| PACRL1   | 3   | PA9MD1   | 0                       | R/W | PA9 Mode                                                           |  |

| PACRL1   | 2   | PA9MD0   | 0                       | R/W | Select the function of the PA9/TCLKD/IRQ3 pin.                     |  |

|          |     |          |                         |     | 00: PA9 I/O (port)                                                 |  |

|          |     |          |                         |     | 01: TCLKD input (MTU)                                              |  |

|          |     |          |                         |     | 10: IRQ3 input (INTC)                                              |  |

|          |     |          |                         |     | 11: Setting prohibited                                             |  |

| PACRL1   | 1   | PA8MD1   | 0                       | R/W | PA8 Mode                                                           |  |

| PACRL1   | 0   | PA8MD0   | 0                       | R/W | Select the function of the PA8/TCLKC/IRQ2 pin.                     |  |

|          |     |          |                         |     | 00: PA8 I/O (port)                                                 |  |

|          |     |          |                         |     | 01: TCLKC input (MTU)                                              |  |

|          |     |          |                         |     | 10: IRQ2 input (INTC)                                              |  |

|          |     |          |                         |     | 11: Setting prohibited                                             |  |

| PACRL2   | 15  | PA7MD1   | 0                       | R/W | PA7 Mode                                                           |  |

| PACRL2   | 14  | PA7MD0   | 0                       | R/W | Select the function of the PA7/TCLKB/ $\overline{\text{CS3}}$ pin. |  |

|          |     |          |                         |     | 00: PA7 I/O (port)                                                 |  |

|          |     |          |                         |     | 01: TCLKB input (MTU)                                              |  |

|          |     |          |                         |     | 10: CS3 output (BSC)                                               |  |

|          |     |          |                         |     | 11: Setting prohibited                                             |  |

| PACRL2   | 13  | PA6MD1   | 0                       | R/W | PA6 Mode                                                           |  |

| PACRL2   | 12  | PA6MD0   | 0                       | R/W | Select the function of the PA6/TCLKA/ $\overline{\text{CS2}}$ pin. |  |

|          |     |          |                         |     | 00: PA6 I/O (port)                                                 |  |

|          |     |          |                         |     | 01: TCLKA input (MTU)                                              |  |

|          |     |          |                         |     | 10: CS2 output (BSC)                                               |  |

|          |     |          |                         |     | 11: Setting prohibited                                             |  |

## **19.4** Input/Output Pins

The flash memory is controlled by means of the pins shown in table 19.2.

Table 19.2Pin Configuration

| Pin Name                 | I/O    | Function                                         |

|--------------------------|--------|--------------------------------------------------|

| RES                      | Input  | Reset                                            |

| FWP* <sup>1</sup>        | Input  | Flash programming/erasing protection by hardware |

| MD1                      | Input  | Sets this LSI's operating mode                   |

| MD0                      | Input  | Sets this LSI's operating mode                   |

| TxD1 (PA4)* <sup>2</sup> | Output | Serial transmit data output                      |

| RxD1 (PA3)* <sup>2</sup> | Input  | Serial receive data input                        |

Notes: 1. Protection cannot be made to flash memory programming/erasing regardless of the setting of the FWP pin when using E10A (when DBGMD is high)

2. In boot mode, SCI pins are fixed, and PA3 and PA4 pins are used as SCI pins.

#### 23.4.3 Operation

Operation starts in RAM monitor mode when  $\overline{\text{AUDRST}}$  is asserted, AUDMD is driven high, then  $\overline{\text{AUDRST}}$  is negated.

Figure 23.5 shows an example of a read operation, and figure 23.6 an example of a write operation.

When AUDSYNC is asserted, input from the AUDATA pins begins. When a command, address, or data (writing only) is input in the format shown in figure 23.4, execution of read/write access to the specified address is started. During internal execution, the AUD returns Not Ready (0000). When execution is completed, the Ready flag (0001) is returned (figures 23.5 and 23.6). Table 23.2 shows the Ready flag format.

In a read, data of the specified size is output when  $\overline{\text{AUDSYNC}}$  is negated following detection of this flag (figure 23.5).

If a command other than the above is input in DIR, the AUD treats this as a command error, disables processing, and sets bit 1 in the Ready flag to 1. If a read/write operation initiated by the command specified in DIR causes a bus error, the AUD disables processing and sets bit 2 in the Ready flag to 1 (figure 23.7).

Bus error conditions are shown below.

- 1. Word access to address 4n+1 or 4n+3

- 2. Longword access to address 4n+1, 4n+2, or 4n+3

- 3. Longword access to on-chip I/O 8-bit area

- 4. Access to external area in single-chip mode

#### Table 23.2Ready Flag Format

| Bit 3      | Bit 2            | Bit 1            | Bit 0        |

|------------|------------------|------------------|--------------|

| Fixed at 0 | 0: Normal status | 0: Normal status | 0: Not ready |

|            | 1: Bus error     | 1: Command error | 1: Ready     |

#### 25. List of Registers

| Register<br>abbreviation | Bit7 | Bit6 | Bit5   | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | Module                   |

|--------------------------|------|------|--------|------|------|------|------|------|--------------------------|

| _                        | _    |      | _      | _    | _    | _    | _    | _    | _                        |

| BCR1                     | _    | _    | MTURWE |      | _    | _    | _    | _    | BSC                      |

|                          | A3LG | A2LG | A1LG   | A0LG | A3SZ | A2SZ | A1SZ | A0SZ |                          |

| BCR2                     | IW31 | IW30 | IW21   | IW20 | IW11 | IW10 | IW01 | IW00 |                          |

|                          | CW3  | CW2  | CW1    | CW0  | SW3  | SW2  | SW1  | SW0  |                          |

| WCR1                     | W33  | W32  | W31    | W30  | W23  | W22  | W21  | W20  |                          |

|                          | W13  | W12  | W11    | W10  | W03  | W02  | W01  | W00  |                          |

| WCR2                     | _    | _    | _      | _    | _    | _    | _    | _    |                          |

|                          | _    | _    | _      | _    | DSW3 | DSW2 | DSW1 | DSW0 |                          |

| _                        | _    | _    | _      | _    | _    | _    | _    | _    | _                        |

| RAMER                    | _    | _    | _      | _    | _    | _    | _    | _    | FLASH                    |

|                          | _    | _    | _      | _    | RAMS | RAM2 | RAM1 | RAM0 | (Only in F-ZTAT version) |

|                          | _    | _    | _      | _    | _    | _    | _    | _    | _                        |

| DMAOR                    | _    | _    | _      | _    | _    | _    | PR1  | PR0  | DMAC                     |

|                          | _    | _    | _      | _    | _    | AE   | NMIF | DME  | for all channels         |

| SAR_0                    |      |      |        |      |      |      |      |      | DMAC                     |

|                          |      |      |        |      |      |      |      |      | (Channel 0)              |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

| DAR_0                    |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

| DMATCR_0                 | _    | _    | _      | _    | _    | _    | _    | _    |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

|                          |      |      |        |      |      |      |      |      |                          |

| CHCR_0                   | _    | _    | _      | _    | _    | _    | _    | _    |                          |

|                          | _    | _    | _      | _    | _    | RL   | AM   | AL   |                          |

|                          | DM1  | DM0  | SM1    | SM0  | RS3  | RS2  | RS1  | RS0  |                          |

|                          | —    | DS   | ТМ     | TS1  | TS0  | IE   | TE   | DE   |                          |

# SH7144 Group, SH7145 Group Hardware Manual

Renesas Electronics Corporation 1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan

REJ09B0108-0400