Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | DMA, PDR, POR, PVD, PWM, Temp Sensor, WDT                               |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 10K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f102c8t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction   |                                                        |

|---|-------|-----------|--------------------------------------------------------|

| 2 | Desc  | ription . |                                                        |

|   | 2.1   | Device    | overview                                               |

|   | 2.2   | Full con  | npatibility throughout the family                      |

|   | 2.3   |           | ew                                                     |

|   |       |           | ······································                 |

| 3 | Pinou | ut and p  | in description                                         |

| 4 | Memo  | ory map   | pping                                                  |

| 5 | Elect | rical cha | aracteristics                                          |

|   | 5.1   | Parame    | eter conditions                                        |

|   |       | 5.1.1     | Minimum and maximum values                             |

|   |       | 5.1.2     | Typical values                                         |

|   |       | 5.1.3     | Typical curves                                         |

|   |       | 5.1.4     | Loading capacitor                                      |

|   |       | 5.1.5     | Pin input voltage                                      |

|   |       | 5.1.6     | Power supply scheme                                    |

|   |       | 5.1.7     | Current consumption measurement                        |

|   | 5.2   | Absolut   | e maximum ratings 26                                   |

|   | 5.3   | Operati   | ng conditions                                          |

|   |       | 5.3.1     | General operating conditions                           |

|   |       | 5.3.2     | Operating conditions at power-up / power-down          |

|   |       | 5.3.3     | Embedded reset and power control block characteristics |

|   |       | 5.3.4     | Embedded reference voltage                             |

|   |       | 5.3.5     | Supply current characteristics                         |

|   |       | 5.3.6     | External clock source characteristics                  |

|   |       | 5.3.7     | Internal clock source characteristics                  |

|   |       | 5.3.8     | PLL characteristics                                    |

|   |       | 5.3.9     | Memory characteristics                                 |

|   |       | 5.3.10    | EMC characteristics                                    |

|   |       | 5.3.11    | Absolute maximum ratings (electrical sensitivity)      |

|   |       | 5.3.12    | I/O current injection characteristics                  |

DocID15056 Rev 6

| Table 45. | ADC characteristics                                     | 1 |

|-----------|---------------------------------------------------------|---|

| Table 46. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 12 MHz      | 5 |

| Table 47. | ADC accuracy - limited test conditions                  | 5 |

| Table 48. | ADC accuracy                                            | 5 |

| Table 49. | TS characteristics                                      | 7 |

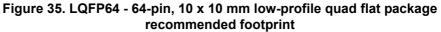

| Table 50. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat       |   |

|           | package mechanical data 68                              | 3 |

| Table 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |   |

|           | mechanical data                                         | 2 |

| Table 52. | Package thermal characteristics                         | 1 |

| Table 53. | Ordering information scheme                             | 3 |

| Table 54. | Document revision history                               | 7 |

# 2 Description

The STM32F102xx medium-density USB access line incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a 48 MHz frequency, high-speed embedded memories (Flash memory of 64 or 128 Kbytes and SRAM of 10 or 16 Kbytes), and an extensive range of enhanced peripherals and I/Os connected to two APB buses. All devices offer standard communication interfaces (two I<sup>2</sup>Cs, two SPIs, one USB and three USARTs), one 12-bit ADC and three general-purpose 16-bit timers.

The STM32F102xx family operates in the -40 to +85 °C temperature range, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F102xx medium-density USB access line is delivered in the LQFP48 7  $\times$  7 mm and LQFP64 10  $\times$  10 mm packages.

The STM32F102xx medium-density USB access line microcontrollers are suitable for a wide range of applications.

- Application control and user interface

- Medical and handheld equipment

- PC peripherals, gaming and GPS platforms

- Industrial applications: PLC, inverters, printers, and scanners

- Alarm systems, Video intercom, and HVAC

Figure 1 shows the general block diagram of the device family.

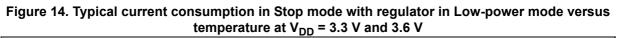

#### Low-power modes

The STM32F102xx medium-density USB access line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output or the RTC alarm.

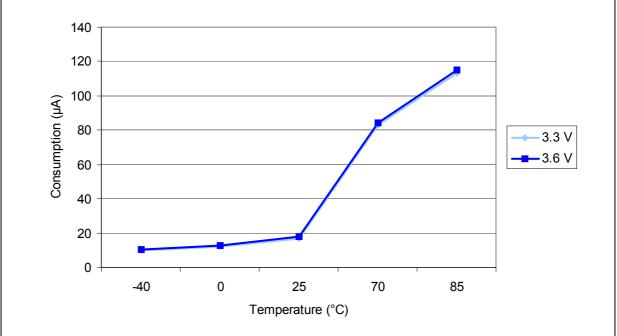

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.8 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, SRAM and registers content are lost except for registers in the Backup domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), a IWDG reset, a rising edge on the WKUP pin, or an RTC alarm occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop or Standby mode.

#### DMA

The flexible 7-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, general purpose timers TIMx and ADC.

#### RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are ten 16-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present.

The real-time clock provides a set of continuously running counters which can be used with suitable software to provide a clock calendar function, and provides an alarm interrupt and a periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low power RC oscillator or the high-speed external clock divided by 128. The internal low power RC has a typical frequency of 40 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural crystal deviation. The RTC features a 32-bit programmable counter for long term measurement using the Compare

| Pi     | ns     |                                |                     | 2)                         |                                                  | Alternate functio                                             | ns <sup>(3) (4)</sup> |

|--------|--------|--------------------------------|---------------------|----------------------------|--------------------------------------------------|---------------------------------------------------------------|-----------------------|

| LQFP48 | LQFP64 | Pin name                       | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                       | Remap                 |

| 1      | 1      | V <sub>BAT</sub>               | S                   | -                          | V <sub>BAT</sub>                                 | -                                                             | -                     |

| 2      | 2      | PC13-TAMPER-RTC <sup>(5)</sup> | I/O                 | -                          | PC13 <sup>(6)</sup>                              | TAMPER-RTC                                                    | -                     |

| 3      | 3      | PC14-OSC32_IN <sup>(5)</sup>   | I/O                 | -                          | PC14 <sup>(6)</sup>                              | OSC32_IN                                                      | -                     |

| 4      | 4      | PC15-OSC32_OUT <sup>(5)</sup>  | I/O                 | -                          | PC15 <sup>(6)</sup>                              | OSC32_OUT                                                     | -                     |

| 5      | 5      | OSC_IN                         | I/O                 | FT                         | OSC_IN                                           | -                                                             | PD0 <sup>(7)</sup>    |

| 6      | 6      | OSC_OUT                        | I/O                 | FT                         | OSC_OUT                                          | -                                                             | PD1 <sup>(7)</sup>    |

| 7      | 7      | NRST                           | I/O                 | -                          | NRST                                             | -                                                             | -                     |

| -      | 8      | PC0                            | I/O                 | -                          | PC0                                              | ADC_IN10                                                      | -                     |

| -      | 9      | PC1                            | I/O                 | -                          | PC1                                              | ADC_IN11                                                      | -                     |

| -      | 10     | PC2                            | I/O                 | -                          | PC2                                              | ADC_IN12                                                      | -                     |

| -      | 11     | PC3                            | I/O                 | -                          | PC3                                              | ADC_IN13                                                      | -                     |

| 8      | 12     | V <sub>SSA</sub>               | S                   | -                          | V <sub>SSA</sub>                                 | -                                                             | -                     |

| 9      | 13     | V <sub>DDA</sub>               | S                   | -                          | V <sub>DDA</sub>                                 | -                                                             | -                     |

| 10     | 14     | PA0-WKUP                       | I/O                 | -                          | PA0                                              | WKUP/USART2_CTS/<br>ADC_IN0/<br>TIM2_CH1_ETR <sup>(8)</sup>   | -                     |

| 11     | 15     | PA1                            | I/O                 | -                          | PA1                                              | USART2_RTS/<br>ADC_IN1/TIM2_CH2 <sup>(8)</sup>                | -                     |

| 12     | 16     | PA2                            | I/O                 | -                          | PA2                                              | USART2_TX/<br>ADC_IN2/TIM2_CH3 <sup>(8)</sup>                 | -                     |

| 13     | 17     | PA3                            | I/O                 | -                          | PA3                                              | USART2_RX/<br>ADC_IN3/TIM2_CH4 <sup>(8)</sup>                 | -                     |

| -      | 18     | V <sub>SS_4</sub>              | S                   | -                          | V <sub>SS_4</sub>                                | -                                                             | -                     |

| -      | 19     | V <sub>DD_4</sub>              | S                   | -                          | $V_{DD_4}$                                       | -                                                             | -                     |

| 14     | 20     | PA4                            | I/O                 | -                          | PA4                                              | SPI1_NSS <sup>(8)</sup> /ADC_IN4<br>USART2_CK/                | -                     |

| 15     | 21     | PA5                            | I/O                 | -                          | PA5                                              | SPI1_SCK <sup>(8)</sup> /ADC_IN5                              | -                     |

| 16     | 22     | PA6                            | I/O                 | -                          | PA6                                              | SPI1_MISO <sup>(8)</sup> /ADC_IN6/<br>TIM3_CH1 <sup>(8)</sup> | -                     |

| 17     | 23     | PA7                            | I/O                 | -                          | PA7                                              | SPI1_MOSI <sup>(8)</sup> /ADC_IN7/<br>TIM3_CH2 <sup>(8)</sup> | -                     |

| -      | 24     | PC4                            | I/O                 | -                          | PC4                                              | ADC_IN14                                                      | -                     |

| -      | 25     | PC5                            | I/O                 | -                          | PC5                                              | ADC_IN15                                                      | -                     |

| 18     | 26     | PB0                            | I/O                 | -                          | PB0                                              | ADC_IN8/TIM3_CH3 <sup>(8)</sup>                               | -                     |

| 19     | 27     | PB1                            | I/O                 | -                          | PB1                                              | ADC_IN9/TIM3_CH4 <sup>(8)</sup>                               | -                     |

Table 4. Medium-density STM32F102xx pin definitions

| Pi     | ns     |                   |                     | (2)                        |                                                  | Alternate function                 | ons <sup>(3) (4)</sup>                 |

|--------|--------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------|----------------------------------------|

| LQFP48 | LQFP64 | Pin name          | Type <sup>(1)</sup> | I / O level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                            | Remap                                  |

| 39     | 55     | PB3               | I/O                 | FT                         | JTDO                                             | -                                  | TIM2_CH2/PB3/<br>TRACESWO/<br>SPI1_SCK |

| 40     | 56     | PB4               | I/O                 | FT                         | JNTRST                                           | -                                  | TIM3_CH1 / PB4<br>SPI1_MISO            |

| 41     | 57     | PB5               | I/O                 | -                          | PB5                                              | I2C1_SMBA                          | TIM3_CH2 /<br>SPI1_MOSI                |

| 42     | 58     | PB6               | I/O                 | FT                         | PB6                                              | I2C1_SCL <sup>(8)</sup> / TIM4_CH1 | USART1_TX                              |

| 43     | 59     | PB7               | I/O                 | FT                         | PB7                                              | I2C1_SDA <sup>(8)</sup> / TIM4_CH2 | USART1_RX                              |

| 44     | 60     | BOOT0             | I                   | -                          | BOOT0                                            | -                                  | -                                      |

| 45     | 61     | PB8               | I/O                 | FT                         | PB8                                              | TIM4_CH3                           | I2C1_SCL                               |

| 46     | 62     | PB9               | I/O                 | FT                         | PB9                                              | TIM4_CH4                           | I2C1_SDA                               |

| 47     | 63     | V <sub>SS_3</sub> | S                   | -                          | V <sub>SS_3</sub>                                | -                                  | -                                      |

| 48     | 64     | V <sub>DD_3</sub> | S                   | -                          | V <sub>DD_3</sub>                                | -                                  | -                                      |

| Table 4. Medium-density | v STM32F102xx | pin definitions | (continued) |

|-------------------------|---------------|-----------------|-------------|

|                         |               |                 |             |

1. I = input, O = output, S = supply.

2. FT= 5 V tolerant.

3. Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripherals that is included. For example, if a device has only one SPI, two USARTs and two timers, they will be called SPI1, USART1 & USART2 and TIM2 & TIM 3, respectively. Refer to *Table 2 on page 9Table 3 on page 12*.

4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F102xx reference manual, available from the STMicroelectronics website: www.st.com.

- 7. The pins number 5 and 6 in the LQFP48 package are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual. The use of PD0 and PD1 in output mode is limited as they can only be used at 50 MHz in output mode.

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual,

available from the STMicroelectronics website: www.st.com.

Figure 15. Typical current consumption in Standby mode versus temperature at V<sub>DD</sub> = 3.3 V and 3.6 V

### Typical current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals are disabled except if it is explicitly mentioned

- The Flash access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz)

- Prefetch is on (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK/4</sub>, f<sub>PCLK2</sub> = f<sub>HCLK/2</sub>, f<sub>ADCCLK</sub> = f<sub>PCLK2</sub>/4

The parameters given in *Table 16* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

|                 |                      |                           |                                                              | Typ <sup>(1)</sup> | Typ <sup>(1)</sup>          |      |

|-----------------|----------------------|---------------------------|--------------------------------------------------------------|--------------------|-----------------------------|------|

| Symbol          | Parameter            | Conditions                | ns f <sub>HCLK</sub> All periphera<br>enabled <sup>(2)</sup> |                    | All peripherals<br>disabled | Unit |

|                 |                      |                           | 48 MHz                                                       | 24.2               | 18.6                        |      |

|                 |                      |                           | 36 MHz                                                       | 19                 | 14.8                        |      |

|                 |                      |                           | 24 MHz                                                       | 12.9               | 10.1                        |      |

|                 |                      |                           | 16 MHz                                                       | 9.3                | 7.4                         |      |

|                 |                      | External                  | 8 MHz                                                        | 5.5                | 4.6                         |      |

|                 |                      | clock <sup>(3)</sup>      | 4 MHz                                                        | 3.3                | 2.8                         |      |

|                 |                      |                           | 2 MHz                                                        | 2.2                | 1.9                         |      |

|                 |                      |                           | 1 MHz                                                        | 1.6                | 1.45                        |      |

|                 |                      |                           | 500 kHz                                                      | 1.3                | 1.25                        |      |

|                 | Supply<br>current in |                           | 125 kHz                                                      | 1.08               | 1.06                        | mA   |

| I <sub>DD</sub> | Run mode             |                           | 48 MHz                                                       | 23.5               | 17.9                        | ШA   |

|                 |                      |                           | 36 MHz                                                       | 18.3               | 14.1                        |      |

|                 |                      | Running on                | 24 MHz                                                       | 12.2               | 9.5                         |      |

|                 |                      | high speed<br>internal RC | 16 MHz                                                       | 8.5                | 6.8                         |      |

|                 |                      | (HSI), AHB                | 8 MHz                                                        | 4.9                | 4                           |      |

|                 |                      | prescaler<br>used to      | 4 MHz                                                        | 2.7                | 2.2                         |      |

|                 |                      | reduce the                | 2 MHz                                                        | 1.6                | 1.4                         |      |

|                 |                      | frequency                 | 1 MHz                                                        | 1.02               | 0.9                         |      |

|                 |                      |                           | 500 kHz                                                      | 0.73               | 0.67                        |      |

|                 |                      |                           | 125 kHz                                                      | 0.5                | 0.48                        |      |

# Table 16. Typical current consumption in Run mode, code with data processing<br/>running from Flash

1. Typical values are measures at  $T_A = 25$  °C,  $V_{DD} = 3.3$  V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                 |                                    |                                 |                   | Typ <sup>(1)</sup>                        | Typ <sup>(1)</sup>          |      |

|-----------------|------------------------------------|---------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                          | Conditions                      | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                    |                                 | 48 MHz            | 9.9                                       | 3.9                         |      |

|                 |                                    |                                 | 36 MHz            | 7.6                                       | 3.1                         |      |

|                 |                                    |                                 | 24 MHz            | 5.3                                       | 2.3                         |      |

|                 |                                    |                                 | 16 MHz            | 3.8                                       | 1.8                         |      |

|                 |                                    | External clock <sup>(3)</sup>   | 8 MHz             | 2.1                                       | 1.2                         |      |

|                 |                                    |                                 | 4 MHz             | 1.6                                       | 1.1                         |      |

|                 | Supply<br>current in<br>Sleep mode |                                 | 2 MHz             | 1.3                                       | 1                           |      |

|                 |                                    |                                 | 1 MHz             | 1.11                                      | 0.98                        | l    |

|                 |                                    |                                 | 500 kHz           | 1.04                                      | 0.96                        |      |

| 1               |                                    |                                 | 125 kHz           | 0.98                                      | 0.95                        | mA   |

| I <sub>DD</sub> |                                    | Running on High                 | 48 MHz            | 9.3                                       | 3.3                         |      |

|                 |                                    |                                 | 36 MHz            | 7                                         | 2.5                         |      |

|                 |                                    |                                 | 24 MHz            | 4.8                                       | 1.8                         |      |

|                 |                                    |                                 | 16 MHz            | 3.2                                       | 1.2                         |      |

|                 |                                    | Speed Internal<br>RC (HSI), AHB | 8 MHz             | 1.6                                       | 0.6                         |      |

|                 |                                    | prescaler used to reduce the    | 4 MHz             | 1                                         | 0.5                         |      |

|                 |                                    | frequency                       | 2 MHz             | 0.72                                      | 0.47                        |      |

|                 |                                    |                                 | 1 MHz             | 0.56                                      | 0.44                        |      |

|                 |                                    |                                 | 500 kHz           | 0.49                                      | 0.42                        |      |

|                 |                                    |                                 | 125 kHz           | 0.43                                      | 0.41                        |      |

| Table 17. Typical current consumption in Sleep mode, code running from Flash or |

|---------------------------------------------------------------------------------|

| RAM                                                                             |

1. Typical values are measures at  $T_A = 25 \text{ °C}$ ,  $V_{DD} = 3.3 \text{ V}$ .

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

- 2. The BusMatrix is automatically active when at least one master is ON.

- 3. Specific conditions for ADC:  $f_{HCLK}$  = 48 MHz,  $f_{APB1} = f_{HCLK}/2$ ,  $f_{APB2} = f_{HCLK}$ ,  $f_{ADCCLK} = f_{APB2}/4$ .

- 4. When ADON bit in the ADC\_CR2 register is set to 1, there is an additional current consumption equal to 0, 65 mA. When we enable the ADC, there is an additional current consumption of 0,05 mA.

# 5.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

The characteristics given in *Table 19* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 8*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                       | User external clock source frequency <sup>(1)</sup> |                                  | 1                  | 8   | 25                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                  | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  |                                  | V <sub>SS</sub>    | -   | 0.3V <sub>DD</sub> | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              | -                                | 5                  | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -                  | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             |                                  | -                  | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          |                                  | 45                 | -   | 55                 | %    |

| ١L                                         | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                    | -   | ±1                 | μA   |

Table 19. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

## Low-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 8*.

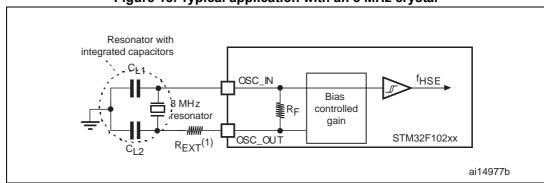

Figure 18. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                               | Conditions                                                |                         |   | Тур  | Max | Unit |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------|---|------|-----|------|

| R <sub>F</sub>                      | Feedback resistor                                                                                       | -                                                         |                         | - | 5    | -   | MΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance<br>versus equivalent serial<br>resistance of the crystal (R <sub>S</sub> ) | R <sub>S</sub> = 30 k                                     | -                       | - | 15   | pF  |      |

| I <sub>2</sub>                      | LSE driving current                                                                                     | V <sub>DD</sub> = 3.3<br>V <sub>IN</sub> = V <sub>S</sub> | -                       | - | 1.4  | μA  |      |

| g <sub>m</sub>                      | Oscillator transconductance                                                                             | -                                                         |                         | 5 | -    | -   | µA/V |

|                                     |                                                                                                         |                                                           | T <sub>A</sub> = 50 °C  | - | 1.5  | -   |      |

|                                     |                                                                                                         |                                                           | T <sub>A</sub> = 25 °C  | - | 2.5  | -   |      |

|                                     |                                                                                                         |                                                           | T <sub>A</sub> = 10 °C  | - | 4.0  | -   |      |

| + (2)                               |                                                                                                         | V is stabilized                                           | T <sub>A</sub> = 0 °C   | - | 6.0  | -   |      |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | Startup time                                                                                            | V <sub>DD</sub> is stabilized                             | T <sub>A</sub> = -10 °C | - | 10.0 | -   | S    |

|                                     |                                                                                                         |                                                           | T <sub>A</sub> = -20 °C | - | 17.0 | -   |      |

|                                     |                                                                                                         |                                                           | T <sub>A</sub> = -30 °C | - | 32.0 | -   |      |

|                                     |                                                                                                         |                                                           | T <sub>A</sub> = -40 °C | - | 60.0 | -   |      |

Table 22. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz)

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled by software to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and can vary significantly with the crystal manufacturer, PCB layout and humidity.

- 2. Refer to application note AN2868 "STM32F10xxx internal RC oscillator (HSI) calibration" available from the ST website www.st.com.

- 3. Guaranteed by design, not tested in production.

- 4. Based on characterization, not tested in production.

- 5. The actual frequency of HSI oscillator may be impacted by a reflow, but does not drift out of the specified range.

### Low-speed internal (LSI) RC oscillator

| Symbol                              | Parameter                        | Min <sup>(2)</sup> | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|--------------------|------|-----|------|

| f <sub>LSI</sub>                    | Frequency                        | 30                 | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -                  | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -                  | 0.65 | 1.2 | μA   |

| Table 24. LSI | oscillator | characteristics | (1) |

|---------------|------------|-----------------|-----|

|---------------|------------|-----------------|-----|

- 1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 85 °C unless otherwise specified.

- 2. Based on characterization, not tested in production.

- 3. Guaranteed by design, not tested in production.

#### Wakeup time from low-power mode

The wakeup times given in *Table 25* is measured on a wakeup phase with a 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Table 25. Low | -nower mode | wakeun | timinas |

|---------------|-------------|--------|---------|

|               | -power mode | waneup | unningə |

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

|                                     | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| twustdby <sup>(1)</sup>             | Wakeup from Standby mode                            | 50  | μs   |

1. The wakeup times are measured from the wakeup event to the point at which the user application code reads the first instruction.

## 5.3.8 PLL characteristics

The parameters given in *Table 26* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                                                     | Parameter                                                           | Conditions                                                                            | Min                                                     | Тур                                       | Мах                                              | Unit |                                                  |  |

|------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|--------------------------------------------------|------|--------------------------------------------------|--|

|                                                            |                                                                     |                                                                                       |                                                         | Standard IO<br>input low level<br>voltage | _                                                | -    | 0.28*(V <sub>DD</sub> -2 V)+0.8 V <sup>(1)</sup> |  |

| V <sub>IL</sub>                                            | Low level input voltage                                             | IO FT <sup>(3)</sup> input<br>low level voltage                                       | -                                                       | -                                         | 0.32*(V <sub>DD</sub> -2V)+0.75 V <sup>(1)</sup> |      |                                                  |  |

|                                                            |                                                                     | All I/Os except<br>BOOT0                                                              | -                                                       | -                                         | 0.35V <sub>DD</sub> <sup>(2)</sup>               |      |                                                  |  |

|                                                            |                                                                     | Standard IO<br>input high level<br>voltage                                            | 0.41*(V <sub>DD</sub> -2 V)+1.3 V <sup>(1)</sup>        | -                                         | -                                                | V    |                                                  |  |

| V <sub>IH</sub>                                            | High level input<br>voltage                                         | IO FT <sup>(3)</sup> input<br>high level<br>voltage                                   | 0.42*(V <sub>DD</sub> -2 V)+1 V <sup>(1)</sup>          | -                                         | -                                                |      |                                                  |  |

|                                                            |                                                                     | All I/Os except<br>BOOT0                                                              | 0.65V <sub>DD</sub> <sup>(2)</sup>                      | -                                         | -                                                |      |                                                  |  |

| V <sub>hys</sub>                                           | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(4)</sup> | -                                                                                     | 200                                                     | -                                         | -                                                | mV   |                                                  |  |

| IO FT Schmitt trigger<br>voltage hysteresis <sup>(4)</sup> |                                                                     | ,c                                                                                    | IO FT Schmitt trigger voltage hysteresis <sup>(4)</sup> | -                                         | 5% V <sub>DD</sub> <sup>(5)</sup>                | -    | -                                                |  |

|                                                            | Input leakage current                                               | $\begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ \text{Standard I/Os} \end{array}$ | -                                                       | -                                         | ±1                                               |      |                                                  |  |

| l <sub>lkg</sub>                                           | (6)                                                                 | V <sub>IN</sub> = 5 V<br>I/O FT                                                       | -                                                       | -                                         | 3                                                | μA   |                                                  |  |

| R <sub>PU</sub>                                            | Weak pull-up<br>equivalent resistor <sup>(7)</sup>                  | $V_{IN} = V_{SS}$                                                                     | 30                                                      | 40                                        | 50                                               | kΩ   |                                                  |  |

| R <sub>PD</sub>                                            | Weak pull-down<br>equivalent resistor <sup>(7)</sup>                | $V_{IN} = V_{DD}$                                                                     | 30                                                      | 40                                        | 50                                               | K22  |                                                  |  |

| C <sub>IO</sub>                                            | I/O pin capacitance                                                 | -                                                                                     | -                                                       | 5                                         | -                                                | pF   |                                                  |  |

Table 34. I/O static characteristics

1. Data based on design simulation.

2. Tested in production.

3. FT = Five-volt tolerant, In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

4. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

5. With a minimum of 100 mV.

6. Leakage could be higher than max, if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimum (~10% order).

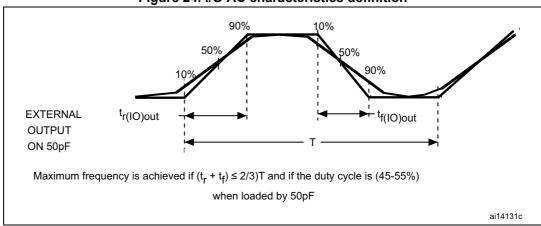

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 24* and *Table 36*, respectively.

Unless otherwise specified, the parameters given in *Table 36* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| MODEx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                                               | Conditions                                             | Мах                | Unit |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                                        | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V                 | 2                  | MHz  |

| 10                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                                      |                                                        |                    | ns   |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                                      | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 125 <sup>(3)</sup> | 115  |

|                                            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(2)</sup>                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 3.6 V               | 10                 | MHz  |

| 01                                         | t <sub>f(IO)out</sub>   | Output high to low level fall time                                                      | C <sub>I</sub> = 50 pF, V <sub>DD</sub> = 2 V to 3.6 V | 25 <sup>(3)</sup>  | 20   |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                                      | CL- 50 μr, V <sub>DD</sub> - 2 V to 3.6 V              | 25 <sup>(3)</sup>  | ns   |

|                                            |                         |                                                                                         | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 50                 | MHz  |

|                                            | F <sub>max(IO)out</sub> | Maximum Frequency <sup>(2)</sup>                                                        | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               |                    | MHz  |

|                                            |                         |                                                                                         | $C_{L}$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V               | 20                 | MHz  |

|                                            |                         |                                                                                         | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   |      |

| 11                                         | t <sub>f(IO)out</sub>   | f(IO)out Output high to low level fall $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to}$ | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 8 <sup>(3)</sup>   | 1    |

|                                            |                         |                                                                                         | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  | ns   |

|                                            |                         |                                                                                         | $C_L$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 5 <sup>(3)</sup>   | 115  |

|                                            | t <sub>r(IO)out</sub>   | Output low to high level rise time                                                      | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | 8 <sup>(3)</sup>   |      |

|                                            |                         |                                                                                         | $C_L$ = 50 pF, $V_{DD}$ = 2 V to 2.7 V                 | 12 <sup>(3)</sup>  |      |

| -                                          | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the EXTI<br>controller                   | -                                                      | 10                 | ns   |

Table 36. I/O AC characteristics<sup>(1)</sup>

The I/O speed is configured using the MODEx[1:0] bits. Refer to the STM32F10xxx reference manual for a description of GPIO Port configuration register.

2. The maximum frequency is defined in *Figure 24*.

3. Guaranteed by design, not tested in production.

#### Figure 24. I/O AC characteristics definition

# 5.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see *Table 34*).

Unless otherwise specified, the parameters given in *Table 37* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 8*.

| Symbol                               | Parameter                                       | Conditions        | Min  | Тур | Max                  | Unit |

|--------------------------------------|-------------------------------------------------|-------------------|------|-----|----------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | -                 | -0.5 | -   | 0.8                  | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | -                 | 2    | -   | V <sub>DD</sub> +0.5 | v    |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      | -                 | -    | 200 | -                    | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 30   | 40  | 50                   | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       | -                 | -    | -   | 100                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | -                 | 300  | -   | -                    | ns   |

Table 37. NRST pin characteristics

1. Guaranteed by design, not tested in production.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

|                                            | _                                                              | Standard m | ode I <sup>2</sup> C <sup>(1)(2)</sup> | Fast mode | e I <sup>2</sup> C <sup>(1)(2)</sup> |      |

|--------------------------------------------|----------------------------------------------------------------|------------|----------------------------------------|-----------|--------------------------------------|------|

| Symbol                                     | Parameter                                                      | Min        | Мах                                    | Min       | Max                                  | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                             | 4.7        | -                                      | 1.3       | -                                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                            | 4.0        | -                                      | 0.6       | -                                    | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                 | 250        | -                                      | 100       | -                                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                             | -          | 3450 <sup>(3)</sup>                    | -         | 900 <sup>(3)</sup>                   |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                          | -          | 1000                                   | -         | 300                                  | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                          | -          | 300                                    | -         | 300                                  |      |

| t <sub>h(STA)</sub>                        | Start condition hold time                                      | 4.0        | -                                      | 0.6       | -                                    |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                            | 4.7        | -                                      | 0.6       | -                                    | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                      | 4.0        | -                                      | 0.6       | -                                    | μs   |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                        | 4.7        | -                                      | 1.3       | -                                    | μs   |

| t <sub>SP</sub>                            | Pulse width of spikes that are suppressed by the analog filter | 0          | 50 <sup>(4)</sup>                      | 0         | 50 <sup>(4)</sup>                    | ns   |

| Cb                                         | Capacitive load for each bus line                              | -          | 400                                    | -         | 400                                  | pF   |

Table 39. I<sup>2</sup>C characteristics

1. Values guaranteed by design, not tested in production.

$f_{PCLK1}$  must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I2C fast mode clock. 2.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of the SCL signal.

4. The analog filter minimum filtered spikes is above  $t_{SP(max)}$  to ensure that spikes width up to  $t_{SP(max)}$  are filtered.

| Currente a l |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol       | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| С            | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D            | -     | 12.000      | -     | -      | 0.4724                | -      |

| D1           | -     | 10.000      | -     | -      | 0.3937                | -      |

| D3           | -     | 7.500       | -     | -      | 0.2953                | -      |

| E            | -     | 12.000      | -     | -      | 0.4724                | -      |

| E1           | -     | 10.000      | -     | -      | 0.3937                | -      |

| E3           | -     | 7.500       | -     | -      | 0.2953                | -      |

| е            | -     | 0.500       | -     | -      | 0.0197                | -      |

| К            | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| L            | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1           | -     | 1.000       | -     | -      | 0.0394                | -      |

| CCC          | -     | -           | 0.080 | -      | -                     | 0.0031 |

Table 50. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

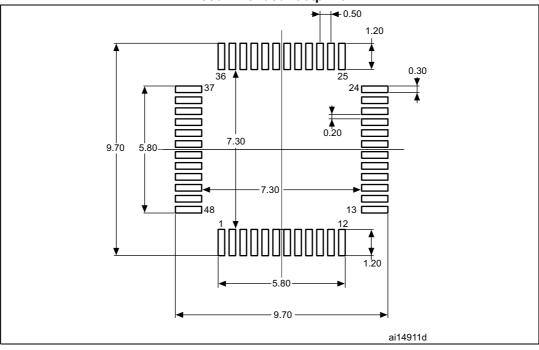

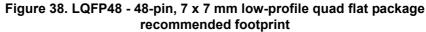

# 6.2 LQFP48 package information

SEATING PLANE С A A ŨŦŨŦŨŦŨŦĬĦŮ<del>Ÿ</del>ŨŦŨŦŨŦŨŦŎŹ ¥ 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 <u>ÅAAAAA AAAAAAA</u> 24 37 Œ b **CHE** <u>ш</u> ш Ē ----------£ 48 13 PIN 1 IDENTIFICATION 1 12 e 5B\_ME\_V2

Figure 37. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

1. Dimensions are expressed in millimeters.

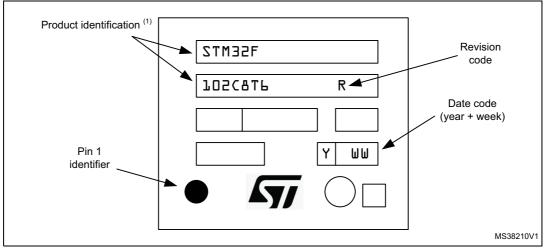

#### **Device marking for LQFP48**

Figure 39 gives an example of topside marking orientation versus pin 1 identifier location.

Samples marked "ES" are to be considered as "Engineering Samples": i.e. they are intended to be sent to customer for electrical compatibility evaluation and may be used to start customer qualification where specifically authorized by ST in writing. In no event ST will be liable for any customer usage in production. Only if ST has authorized in writing the customer qualification Engineering Samples can be used for reliability qualification trials.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID15056 Rev 6