Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | 8051                                                                     |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 4KB (4K x 8)                                                             |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 20-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p87lpc764bdh-512 |

|                            |                                                                          |

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

### **ORDERING INFORMATION**

| Type number     | Package |                                                                        |                               |                        |          |

|-----------------|---------|------------------------------------------------------------------------|-------------------------------|------------------------|----------|

|                 | Name    | Description                                                            | Frequency                     | Temperature Range (°C) | Version  |

| P87LPC764BD/01  | SO20    | plastic small outline package; 20 leads; body width 7.5 mm             | 20 MHz (5 V),<br>10 MHz (3 V) | 0 to +70               | SOT163-1 |

| P87LPC764BD     | SO20    | plastic small outline package; 20 leads; body width 7.5 mm             | 20 MHz (5 V),<br>10 MHz (3 V) | 0 to +70               | SOT163-1 |

| P87LPC764BDH/01 | TSSOP20 | plastic thin shrink small outline package; 20 leads; body width 4.4 mm | 20 MHz (5 V)<br>10 MHz (3 V)  | 0 to +70               | SOT360-1 |

| P87LPC764BDH    | TSSOP20 | plastic thin shrink small outline package; 20 leads; body width 4.4 mm | 20 MHz (5 V)<br>10 MHz (3 V)  | 0 to +70               | SOT360-1 |

| P87LPC764BN     | DIP20   | plastic dual in-line package; 20 leads (300 mil)                       | 20 MHz (5 V),<br>10 MHz (3 V) | 0 to +70               | SOT146-1 |

| P87LPC764FN     | DIP20   | plastic dual in-line package; 20 leads (300 mil)                       | 20 MHz (5 V),<br>10 MHz (3 V) | -40 to +85             | SOT146-1 |

| P87LPC764FD     | SO20    | plastic small outline package; 20 leads; body width 7.5 mm             | 20 MHz (5 V),<br>10 MHz (3 V) | -40 to +85             | SOT163-1 |

| P87LPC764FDH    | TSSOP20 | plastic thin shrink small outline package; 20 leads; body width 4.4 mm | 20 MHz (5 V),<br>10 MHz (3 V) | -40 to +85             | SOT360-1 |

| P87LPC764HDH    | TSSOP20 | plastic thin shrink small outline package; 20 leads; body width 4.4 mm | 16 MHz (5 V)                  | -40 to +125            | SOT360-1 |

### DEVICE COMPARISON TABLE<sup>1</sup>

| Part type                    | Internal RC oscillator |

|------------------------------|------------------------|

| P87LPC764BD/01, BDH/01       | ±2.5% to 5%            |

| P87LPC764BDH, HDH            | ±10%                   |

| P87LPC764BD, BN, FN, FD, FDH | ±25%                   |

### NOTE:

### PIN CONFIGURATION, 20-PIN DIP, SO, AND TSSOP PACKAGES

| CMP2/P0.0 1       | 20 P0.1/CIN2B      |

|-------------------|--------------------|

| P1.7 2            | 19 P0.2/CIN2A      |

| P1.6 3            | 18 P0.3/CIN1B      |

| RST/P1.5 4        | 17 P0.4/CIN1A      |

| V <sub>SS</sub> 5 | 16 P0.5/CMPREF     |

| X1/P2.1 6         | 15 V <sub>DD</sub> |

| X2/CLKOUT/P2.0 7  | 14 P0.6/CMP1       |

| INT1/P1.4 8       | 13 P0.7/T1         |

| SDA/INT0/P1.3 9   | 12 P1.0/TxD        |

| SCL/T0/P1.2 10    | 11 P1.1/RxD        |

| ,                 |                    |

|                   | SU01149            |

<sup>1.</sup> Please see AC and DC characteristics for more details.

Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

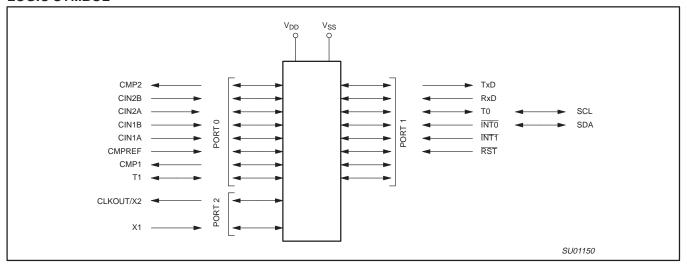

### **LOGIC SYMBOL**

P87LPC764

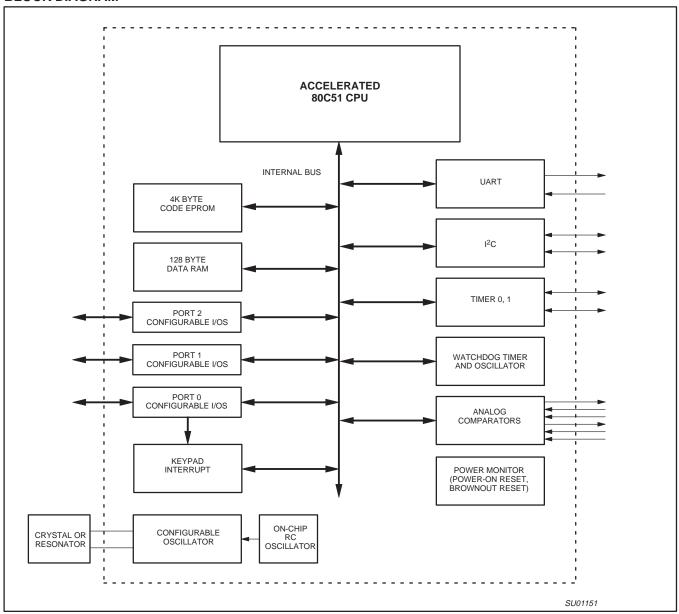

### **BLOCK DIAGRAM**

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

### **PIN DESCRIPTIONS**

| MNEMONIC        | PIN NO.             | TYPE       |                                                                                   | NAME AND FUNCTION                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|-----------------|---------------------|------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| P0.0–P0.7       | 1, 13, 14,<br>16–20 | I/O        | the quasi-bid<br>by the PRHI<br>depends upo                                       | lirectional mo<br>bit in the UCI<br>on the port co                       | /O port with a user-configurable output type. Port 0 latches are configured in de and have either ones or zeros written to them during reset, as determined FG1 configuration byte. The operation of port 0 pins as inputs and outputs infiguration selected. Each port pin is configured independently. Refer to the uration and the DC Electrical Characteristics for details.                                                |  |  |  |  |  |  |

|                 |                     |            | The Keyboar                                                                       | d Interrupt fe                                                           | eature operates with port 0 pins.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                 |                     |            | Port 0 also p                                                                     | rovides vario                                                            | us special functions as described below.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                 | 1                   | 0          | P0.0                                                                              | CMP2                                                                     | Comparator 2 output.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                 | 20                  | I          | P0.1                                                                              | CIN2B                                                                    | Comparator 2 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                 | 19                  | - 1        | P0.2                                                                              | CIN2A                                                                    | Comparator 2 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                 | 18                  | I          | P0.3                                                                              | CIN1B                                                                    | Comparator 1 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                 | 17                  | I          | P0.4                                                                              | CIN1A                                                                    | Comparator 1 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                 | 16                  | 1          | P0.5                                                                              | CMPREF                                                                   | Comparator reference (negative) input.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                 | 14                  | 0          | P0.6                                                                              | CMP1                                                                     | Comparator 1 output.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                 | 13                  | I/O        | P0.7                                                                              | T1                                                                       | Timer/counter 1 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| P1.0-P1.7       | 2–4, 8–12           | I/O        | below. Port 1<br>written to the<br>operation of<br>selected. Ea-<br>port configur | latches are am during resthe configura chief the configura ation and the | /O port with a user-configurable output type, except for three pins as noted configured in the quasi-bidirectional mode and have either ones or zeros et, as determined by the PRHI bit in the UCFG1 configuration byte. The ble port 1 pins as inputs and outputs depends upon the port configuration figurable port pins are programmed independently. Refer to the section on I/O DC Electrical Characteristics for details. |  |  |  |  |  |  |

|                 |                     |            | Port 1 also p                                                                     | ort 1 also provides various special functions as described below.        |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                 | 12                  | 0          | P1.0                                                                              | TxD                                                                      | Transmitter output for the serial port.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                 | 11                  | I          | P1.1                                                                              | RxD                                                                      | Receiver input for the serial port.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                 | 10                  | I/O<br>I/O | P1.2                                                                              | T0<br>SCL                                                                | Timer/counter 0 external count input or overflow output. I <sup>2</sup> C serial clock input/output. When configured as an output, P1.2 is open drain, in order to conform to I <sup>2</sup> C specifications.                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                 | 9                   | I<br>I/O   | P1.3                                                                              | INTO<br>SDA                                                              | External interrupt 0 input. I <sup>2</sup> C serial data input/output. When configured as an output, P1.3 is open drain, in order to conform to I <sup>2</sup> C specifications.                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                 | 8                   | I          | P1.4                                                                              | INT1                                                                     | External interrupt 1 input.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                 | 4                   | I          | P1.5                                                                              | RST                                                                      | External Reset input (if selected via EPROM configuration). A low on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor begins execution at address 0. When used as a port pin, P1.5 is a Schmitt trigger input only.                                                                                                                                    |  |  |  |  |  |  |

| P2.0-P2.1       | 6, 7                | I/O        | quasi-bidired<br>the PRHI bit<br>depends upo<br>section on I/0                    | tional mode a<br>in the UCFG<br>on the port co<br>O port configu         | O port with a user-configurable output type. Port 2 latches are configured in the and have either ones or zeros written to them during reset, as determined by 1 configuration byte. The operation of port 2 pins as inputs and outputs infiguration selected. Each port pin is configured independently. Refer to the uration and the DC Electrical Characteristics for details.                                               |  |  |  |  |  |  |

|                 | _                   |            |                                                                                   |                                                                          | us special functions as described below.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                 | 7                   | 0          | P2.0                                                                              | X2                                                                       | Output from the oscillator amplifier (when a crystal oscillator option is selected via the EPROM configuration).                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                 |                     |            |                                                                                   | CLKOUT                                                                   | CPU clock divided by 6 clock output when enabled via SFR bit and in conjunction with internal RC oscillator or external clock input.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                 | 6                   | I          | P2.1                                                                              | X1                                                                       | Input to the oscillator circuit and internal clock generator circuits (when selected via the EPROM configuration).                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| V <sub>SS</sub> | 5                   | I          | Ground: 0V                                                                        | reference.                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| V <sub>DD</sub> | 15                  | I          | Power Supp<br>Power Down                                                          |                                                                          | e power supply voltage for normal operation as well as Idle and                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

### **SPECIAL FUNCTION REGISTERS**

| Name                | Description                                                         | SFR<br>Address |          |          |             |          |             |             | LSB      | Reset<br>Value |                  |

|---------------------|---------------------------------------------------------------------|----------------|----------|----------|-------------|----------|-------------|-------------|----------|----------------|------------------|

|                     |                                                                     |                | E7       | E6       | E5          | E4       | E3          | E2          | E1       | E0             |                  |

| ACC*                | Accumulator                                                         | E0h            |          |          |             |          |             |             |          |                | 00h              |

| AUXR1#              | Auxiliary Function Register                                         | A2h            | KBF      | BOD      | BOI         | LPEP     | SRST        | 0           | -        | DPS            | 02h <sup>1</sup> |

|                     |                                                                     |                | F7       | F6       | F5          | F4       | F3          | F2          | F1       | F0             | 1                |

| B*                  | B register                                                          | F0h            |          |          |             |          |             |             |          |                | 00h              |

| CMP1#               | Comparator 1 control register                                       | ACh            | -        | -        | CE1         | CP1      | CN1         | OE1         | CO1      | CMF1           | 00h <sup>1</sup> |

| CMP2#               | Comparator 2 control register                                       | ADh            | _        | -        | CE2         | CP2      | CN2         | OE2         | CO2      | CMF2           | 00h <sup>1</sup> |

| DIVM#               | CPU clock divide-by-M control                                       | 95h            |          |          |             |          |             |             |          |                | 00h              |

| DPTR:<br>DPH<br>DPL | Data pointer (2 bytes) Data pointer high byte Data pointer low byte | 83h<br>82h     |          |          |             |          |             |             |          |                | 00h<br>00h       |

|                     |                                                                     |                | CF       | CE       | CD          | CC       | СВ          | CA          | C9       | C8             | ]                |

| I2CFG#*             | I <sup>2</sup> C configuration register                             | C8h/RD         | SLAVEN   | MASTRQ   | 0           | TIRUN    | _           | _           | CT1      | CT0            | 00h <sup>1</sup> |

|                     |                                                                     | C8h/WR         | SLAVEN   | MASTRQ   | CLRTI       | TIRUN    | _           | _           | CT1      | CT0            |                  |

|                     |                                                                     |                | DF       | DE       | DD          | DC       | DB          | DA          | D9       | D8             |                  |

| I2CON#*             | I <sup>2</sup> C control register                                   | D8h/RD         | RDAT     | ATN      | DRDY        | ARL      | STR         | STP         | MASTER   | _              | 80h <sup>1</sup> |

|                     |                                                                     | D8h/WR         | CXA      | IDLE     | CDR         | CARL     | CSTR        | CSTP        | XSTR     | XSTP           | 1                |

| I2DAT#              | I <sup>2</sup> C data register                                      | D9h/RD         | RDAT     | 0        | 0           | 0        | 0           | 0           | 0        | 0              | 80h              |

|                     |                                                                     | D9h/WR         | XDAT     | х        | х           | х        | х           | х           | Х        | х              | 1                |

|                     |                                                                     |                | AF       | AE       | AD          | AC       | AB          | AA          | A9       | A8             | 1                |

| IEN0*               | Interrupt enable 0                                                  | A8h            | EA       | EWD      | EBO         | ES       | ET1         | EX1         | ET0      | EX0            | 00h              |

|                     |                                                                     |                | EF       | EE       | ED          | EC       | EB          | EA          | E9       | E8             | 1                |

| IEN1#*              | Interrupt enable 1                                                  | E8h            | ETI      | _        | EC1         | _        | _           | EC2         | EKB      | El2            | 00h <sup>1</sup> |

|                     |                                                                     |                | BF       | BE       | BD          | ВС       | BB          | ВА          | В9       | B8             | 1                |

| IP0*                | Interrupt priority 0                                                | B8h            | _        | PWD      | PBO         | PS       | PT1         | PX1         | PT0      | PX0            | 00h <sup>1</sup> |

| IP0H#               | Interrupt priority 0 high byte                                      | B7h            | -        | PWDH     | PBOH        | PSH      | PT1H        | PX1H        | PT0H     | PX0H           | 00h <sup>1</sup> |

|                     |                                                                     |                | FF       | FE       | FD          | FC       | FB          | FA          | F9       | F8             | 1                |

| IP1*                | Interrupt priority 1                                                | F8h            | PTI      | <u> </u> | PC1         | _        | _           | PC2         | PKB      | PI2            | 00h <sup>1</sup> |

| IP1H#               | Interrupt priority 1 high byte                                      | F7h            | PTIH     | _        | PC1H        | _        | _           | PC2H        | PKBH     | PI2H           | 00h <sup>1</sup> |

| KBI#                | Keyboard Interrupt                                                  | 86h            | 87       | 86       | 85          | 84       | 83          | 82          | 81       | 80             | 00h              |

| P0*                 | Port 0                                                              | 80h            | T1       | CMP1     | CMPREF      | CIN1A    | CIN1B       | CIN2A       | CIN2B    | CMP2           | Note 2           |

|                     |                                                                     |                | 97       | 96       | 95          | 94       | 93          | 92          | 91       | 90             |                  |

| P1*                 | Port 1                                                              | 90h            | (P1.7)   | (P1.6)   | RST         | INT1     | ĪNT0        | T0          | RxD      | TxD            | Note 2           |

|                     |                                                                     |                | A7       | A6       | A5          | A4       | A3          | A2          | A1       | A0             |                  |

| P2*                 | Port 2                                                              | A0h            | _        | _        |             |          | T -         |             | X1       | X2             | Note 2           |

| P0M1#               | Port 0 output mode 1                                                | 84h            | (P0M1.7) | (P0M1.6) | (P0M1.5)    | (P0M1.4) | (P0M1.3)    | (P0M1.2)    | (P0M1.1) | (P0M1.0)       | 00h              |

| P0M2#               | Port 0 output mode 2                                                | 85h            | (P0M2.7) | (P0M2.6) | (P0M2.5)    | (P0M2.4) | (P0M2.3)    | (P0M2.2)    | (P0M2.1) | (P0M2.0)       | 00H              |

| P1M1#               | Port 1 output mode 1                                                | 91h            | (P1M1.7) | (P1M1.6) | (1 OIVIZ.5) | (P1M1.4) | (1 01412.0) | (1 GIVIZ.Z) | (P1M1.1) | (P1M1.0)       | 00h <sup>1</sup> |

| P1M2#               | Port 1 output mode 2                                                | 92h            | (P1M1.7) | (P1M1.6) | _           | (P1M2.4) | _           | _           | (P1M2.1) | (P1M2.0)       | 00h <sup>1</sup> |

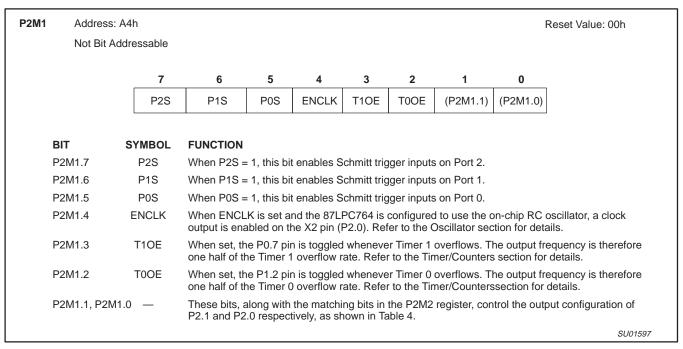

| P2M1#               | Port 2 output mode 1                                                | 9211<br>A4h    | P2S      | P1S      | POS         | ENCLK    | T10E        | TOOE        | (P2M1.1) | (P2M1.0)       | 00h              |

| P2M1#<br>P2M2#      | Port 2 output mode 1                                                | A4fi<br>A5h    | P23<br>_ | FIS      | F U S       | LINCLK   | _ TIOE      | - TOOE      | , ,      | (P2M1.0)       | 00h <sup>1</sup> |

|                     | ·                                                                   |                |          | CMODO    |             |          |             |             | (P2M2.1) | <u> </u>       | -                |

| PCON                | Power control register                                              | 87h            | SMOD1    | SMOD0    | BOF         | POF      | GF1         | GF0         | PD       | IDL            | Note 3           |

## Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

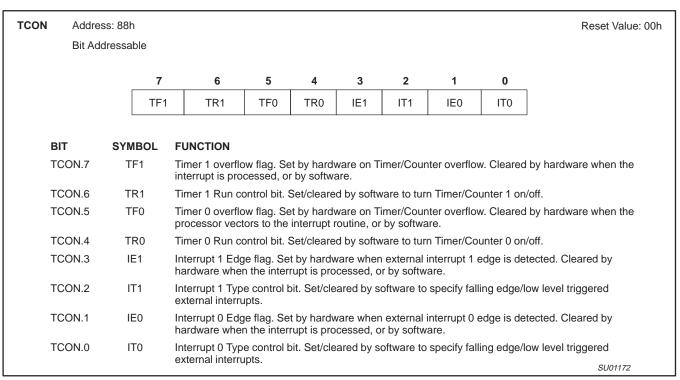

#### **External Interrupt Inputs**

The P87LPC764 has two individual interrupt inputs as well as the Keyboard Interrupt function. The latter is described separately elsewhere in this section. The two interrupt inputs are identical to those present on the standard 80C51 microcontroller.

The external sources can be programmed to be level-activated or transition-activated by setting or clearing bit IT1 or IT0 in Register TCON. If ITn = 0, external interrupt n is triggered by a detected low at the  $\overline{\text{INTn}}$  pin. If ITn = 1, external interrupt n is edge triggered. In this mode if successive samples of the  $\overline{\text{INTn}}$  pin show a high in one cycle and a low in the next cycle, interrupt request flag IEn in TCON is set, causing an interrupt request.

Since the external interrupt pins are sampled once each machine cycle, an input high or low should hold for at least 6 CPU Clocks to ensure proper sampling. If the external interrupt is

transition-activated, the external source has to hold the request pin high for at least one machine cycle, and then hold it low for at least one machine cycle. This is to ensure that the transition is seen and that interrupt request flag IEn is set. IEn is automatically cleared by the CPU when the service routine is called.

If the external interrupt is level-activated, the external source must hold the request active until the requested interrupt is actually generated. If the external interrupt is still asserted when the interrupt service routine is completed another interrupt will be generated. It is not necessary to clear the interrupt flag IEn when the interrupt is level sensitive, it simply tracks the input pin level.

If an external interrupt is enabled when the P87LPC764 is put into Power Down or Idle mode, the interrupt will cause the processor to wake up and resume operation. Refer to the section on Power Reduction Modes for details.

Figure 9. Interrupt Sources, Interrupt Enables, and Power Down Wakeup Sources

## Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

#### I/O Ports

The P87LPC764 has 3 I/O ports, port 0, port 1, and port 2. The exact number of I/O pins available depend upon the oscillator and reset options chosen. At least 15 pins of the P87LPC764 may be used as I/Os when a two-pin external oscillator and an external reset circuit are used. Up to 18 pins may be available if fully on-chip oscillator and reset configurations are chosen.

All but three I/O port pins on the P87LPC764 may be software configured to one of four types on a bit-by-bit basis, as shown in Table 4. These are: quasi-bidirectional (standard 80C51 port outputs), push-pull, open drain, and input only. Two configuration registers for each port choose the output type for each port pin.

Table 4. Port Output Configuration Settings

| PxM1.y | PxM2.y     | Port Output Mode            |  |  |

|--------|------------|-----------------------------|--|--|

| 0      | 0          | Quasi-bidirectional         |  |  |

| 0      | 0 1 Push-P |                             |  |  |

| 1      | 0          | Input Only (High Impedance) |  |  |

| 1      | 1          | Open Drain                  |  |  |

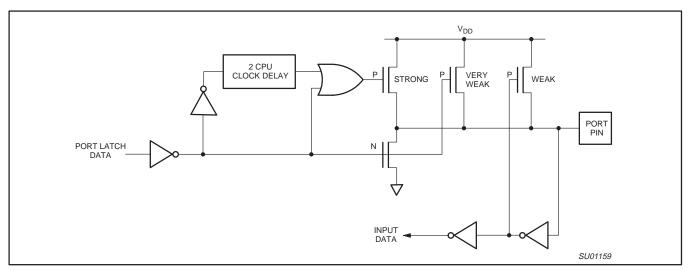

### **Quasi-Bidirectional Output Configuration**

The default port output configuration for standard P87LPC764 I/O ports is the quasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an

input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes.

One of these pull-ups, called the "very weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The very weak pull-up sources a very small current that will pull the pin high if it is left floating.

A second pull-up, called the "weak" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the weak pull-up turns off, and only the very weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the weak pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The quasi-bidirectional port configuration is shown in Figure 10.

Figure 10. Quasi-Bidirectional Output

## Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

Figure 13. Port 2 Mode Register 1 (P2M1)

### **Keyboard Interrupt (KBI)**

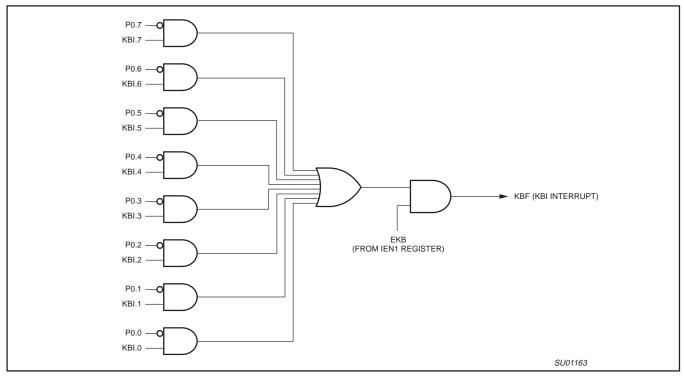

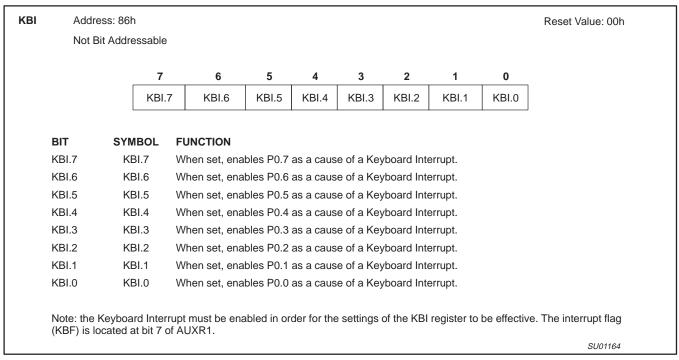

The Keyboard Interrupt function is intended primarily to allow a single interrupt to be generated when any key is pressed on a keyboard or keypad connected to specific pins of the P87LPC764, as shown in Figure 14. This interrupt may be used to wake up the CPU from Idle or Power Down modes. This feature is particularly useful in handheld, battery powered systems that need to carefully manage power consumption yet also need to be convenient to use.

The P87LPC764 allows any or all pins of port 0 to be enabled to cause this interrupt. Port pins are enabled by the setting of bits in

the KBI register, as shown in Figure 15. The Keyboard Interrupt Flag (KBF) in the AUXR1 register is set when any enabled pin is pulled low while the KBI interrupt function is active. An interrupt will generated if it has been enabled. Note that the KBF bit must be cleared by software.

Due to human time scales and the mechanical delay associated with keyswitch closures, the KBI feature will typically allow the interrupt service routine to poll port 0 in order to determine which key was pressed, even if the processor has to wake up from Power Down mode. Refer to the section on Power Reduction Modes for details.

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

Figure 14. Keyboard Interrupt

Figure 15. Keyboard Interrupt Register (KBI)

## Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

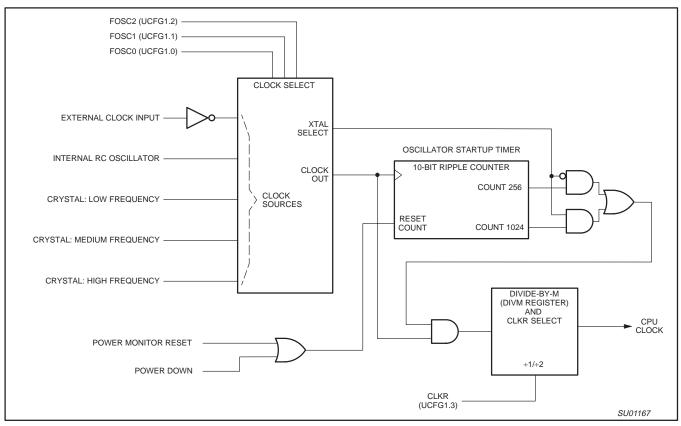

Figure 18. Block Diagram of Oscillator Control

#### **CPU Clock Modification: CLKR and DIVM**

For backward compatibility, the CLKR configuration bit allows setting the P87LPC764 instruction and peripheral timing to match standard 80C51 timing by dividing the CPU clock by two. Default timing for the P87LPC764 is 6 CPU clocks per machine cycle while standard 80C51 timing is 12 clocks per machine cycle. This division also applies to peripheral timing, allowing 80C51 code that is oscillator frequency and/or timer rate dependent. The CLKR bit is located in the EPROM configuration register UCFG1, described under EPROM Characteristics

In addition to this, the CPU clock may be divided down from the oscillator rate by a programmable divider, under program control. This function is controlled by the DIVM register. If the DIVM register is set to zero (the default value), the CPU will be clocked by either the unmodified oscillator rate, or that rate divided by two, as determined by the previously described CLKR function.

When the DIVM register is set to some value N (between 1 and 255), the CPU clock is divided by 2 \* (N + 1). Clock division values from 4 through 512 are thus possible. This feature makes it possible to temporarily run the CPU at a lower rate, reducing power consumption, in a manner similar to Idle mode. By dividing the clock, the CPU can retain the ability to respond to events other than those that can cause interrupts (i.e. events that allow exiting the Idle mode) by executing its normal program at a lower rate. This can allow bypassing the oscillator startup time in cases where Power Down mode would otherwise be used. The value of DIVM may be changed by the program at any time without interrupting code execution.

### **Power Monitoring Functions**

The P87LPC764 incorporates power monitoring functions designed to prevent incorrect operation during initial power up and power loss or reduction during operation. This is accomplished with two hardware functions: Power-On Detect and Brownout Detect.

#### **Brownout Detection**

The Brownout Detect function allows preventing the processor from failing in an unpredictable manner if the power supply voltage drops below a certain level. The default operation is for a brownout detection to cause a processor reset, however it may alternatively be configured to generate an interrupt by setting the BOI bit in the AUXR1 register (AUXR1.5).

The P87LPC764 allows selection of two Brownout levels: 2.5~V or 3.8~V. When  $V_{DD}$  drops below the selected voltage, the brownout detector triggers and remains active until  $V_{DD}$  is returns to a level above the Brownout Detect voltage. When Brownout Detect causes a processor reset, that reset remains active as long as  $V_{DD}$  remains below the Brownout Detect voltage. When Brownout Detect generates an interrupt, that interrupt occurs once as  $V_{DD}$  crosses from above to below the Brownout Detect voltage. For the interrupt to be processed, the interrupt system and the BOI interrupt must both be enabled (via the EA and EBO bits in IEN0).

When Brownout Detect is activated, the BOF flag in the PCON register is set so that the cause of processor reset may be determined by software. This flag will remain set until cleared by software.

## Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

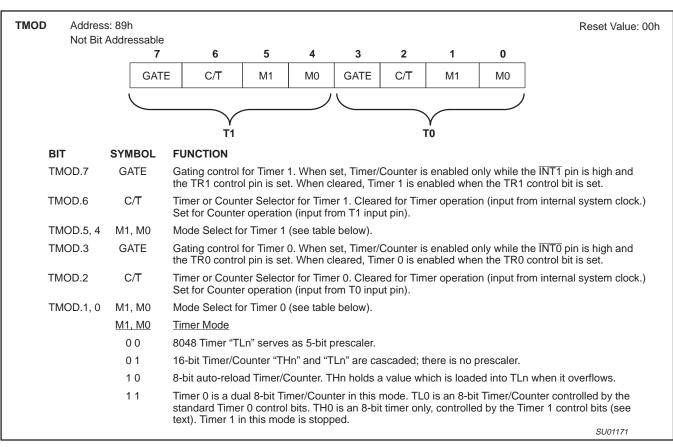

#### Timer/Counters

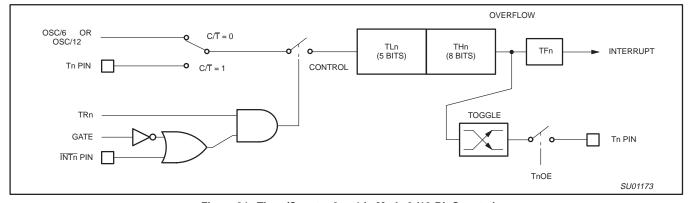

The P87LPC764 has two general purpose counter/timers which are upward compatible with the standard 80C51 Timer 0 and Timer 1. Both can be configured to operate either as timers or event counters (see Figure 22). An option to automatically toggle the T0 and/or T1 pins upon timer overflow has been added.

In the "Timer" function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of 6 CPU clock periods, the count rate is 1/6 of the CPU clock frequency. Refer to the section Enhanced CPU for a description of the CPU clock.

In the "Counter" function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once during every

machine cycle. When the samples of the pin state show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (12 CPU clocks) to recognize a 1-to-0 transition, the maximum count rate is 1/6 of the CPU clock frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.

The "Timer" or "Counter" function is selected by control bits  $C/\overline{T}$  in the Special Function Register TMOD. In addition to the "Timer" or "Counter" selection, Timer 0 and Timer 1 have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters. Mode 3 is different. The four operating modes are described in the following text.

Figure 22. Timer/Counter Mode Control Register (TMOD)

## Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

#### Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. Figure 24 shows Mode 0 operation.

In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFn. The count input is enabled to the Timer when TRn = 1 and either GATE = 0 or  $\overline{\text{INTn}}$  = 1. (Setting GATE = 1 allows the Timer to be controlled by external input  $\overline{\text{INTn}}$ , to facilitate pulse width

measurements). TRn is a control bit in the Special Function Register TCON (Figure 23). The GATE bit is in the TMOD register.

The 13-bit register consists of all 8 bits of THn and the lower 5 bits of TLn. The upper 3 bits of TLn are indeterminate and should be ignored. Setting the run flag (TRn) does not clear the registers.

Mode 0 operation is the same for Timer 0 and Timer 1. See Figure 24. There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

Figure 23. Timer/Counter Control Register (TCON)

Figure 24. Timer/Counter 0 or 1 in Mode 0 (13-Bit Counter)

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

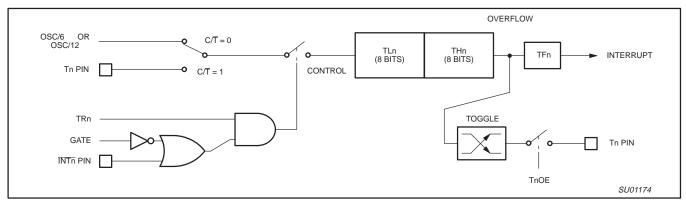

#### Mode 1

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register (THn and TLn) are used. See Figure 25

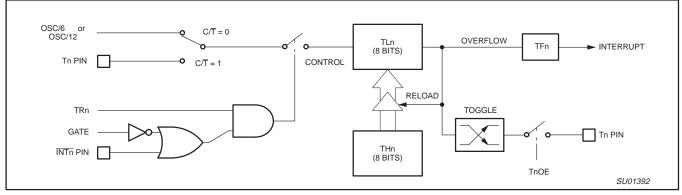

#### Mode 2

Mode 2 configures the Timer register as an 8-bit Counter (TL1) with automatic reload, as shown in Figure 26. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of THn, which must be preset by software. The reload leaves THn unchanged. Mode 2 operation is the same for Timer 0 and Timer 1.

#### Mode 3

When Timer 1 is in Mode 3 it is stopped. The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate 8-bit counters. The logic for Mode 3 on Timer 0 is shown in Figure 27. TL0 uses the Timer 0 control bits: C/T, GATE, TR0 and pin INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the "Timer 1" interrupt.

Mode 3 is provided for applications that require an extra 8-bit timer. With Timer 0 in Mode 3, an P87LPC764 can look like it has three Timer/Counters. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it into and out of its own Mode 3. It can still be used by the serial port as a baud rate generator, or in any application not requiring an interrupt.

Figure 25. Timer/Counter 0 or 1 in Mode 1 (16-Bit Counter)

Figure 26. Timer/Counter 0 or 1 in Mode 2 (8-Bit Auto-Reload)

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

#### Serial Port Control Register (SCON)

The serial port control and status register is the Special Function Register SCON, shown in Figure 28. This register contains not only the mode selection bits, but also the 9th data bit for transmit and receive (TB8 and RB8), and the serial port interrupt bits (TI and RI).

The Framing Error bit (FE) allows detection of missing stop bits in the received data stream. The FE bit shares the bit position SCON.7

with the SM0 bit. Which bit appears in SCON at any particular time is determined by the SM0D0 bit in the PCON register. If SM0D0 = 0, SCON.7 is the SM0 bit. If SM0D0 = 1, SCON.7 is the FE bit. Once set, the FE bit remains set until it is cleared by software. This allows detection of framing errors for a group of characters without the need for monitoring it for every character individually.

| <b>N</b> Addre | ess: 98h   |                              |              |              |             |            |              |               | Reset Value: 00h                                              |

|----------------|------------|------------------------------|--------------|--------------|-------------|------------|--------------|---------------|---------------------------------------------------------------|

| Bit Ac         | ddressable |                              |              |              |             |            |              |               |                                                               |

|                | 7          | 6                            | 5            | 4            | 3           | 2          | 1            | 0             |                                                               |

|                | SM0/       | FE SM1                       | SM2          | REN          | TB8         | RB8        | TI           | RI            |                                                               |

| BIT            | SYMBOL     | FUNCTION                     |              |              |             |            |              |               |                                                               |

| SCON.7         | FE         | Framing Error.               | ware. The    |              |             |            |              |               | t is detected. Must be is bit to be accessible.               |

| SCON.7         | SM0        | With SM1, defito be accessib |              |              |             | SMOD0 b    | oit in the P | CON regis     | ster must be 0 for this bit                                   |

| SCON. 6        | SM1        | With SM0, def                | nes the s    | erial port n | node (see   | table belo | w).          |               |                                                               |

|                | SM0, SM1   | <b>UART Mode</b>             |              | Baud         | Rate        |            |              |               |                                                               |

|                | 0 0        | 0: shift register            |              | CPU          | clock/6     |            |              |               |                                                               |

|                | 0 1        | 1: 8-bit UART                |              | Varial       | ole (see te | ext)       |              |               |                                                               |

|                | 10         | 2: 9-bit UART                |              | CPU          | clock/32    | or CPU clo | ck/16        |               |                                                               |

|                | 11         | 3: 9-bit UART                |              | Varial       | ole (see te | ext)       |              |               |                                                               |

| SCON.5         | SM2        |                              | ill not be a | activated if | the recei   | ved 9th da | ta bit (RB8  | 3) is 0. In N | ode 2 or 3, if SM2 is set Mode 1, if SM2=1 then RI ould be 0. |

| SCON.4         | REN        | Enables serial               | reception    | . Set by so  | ftware to   | enable red | eption. Cl   | ear by sof    | tware to disable reception                                    |

| SCON.3         | TB8        | The 9th data b               | it that will | be transm    | itted in M  | odes 2 and | d 3. Set or  | clear by s    | oftware as desired.                                           |

| SCON.2         | RB8        | In Modes 2 an was received.  |              |              |             | s received | . In Mode    | 1, it SM2=    | 0, RB8 is the stop bit that                                   |

| SCON.1         | TI         |                              |              |              |             |            |              |               | de 0, or at the beginning ed by software.                     |

| SCON.0         | RI         |                              |              |              |             |            |              |               | de 0, or halfway through 12). Must be cleared by              |

Figure 28. Serial Port Control Register (SCON)

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

Table 10. Baud Rates, Timer Values, and CPU Clock Frequencies for SMOD1 = 1

| Timer Count |          |          |           | Baud Rate |           |           |           |

|-------------|----------|----------|-----------|-----------|-----------|-----------|-----------|

| Timer Count | 2400     | 4800     | 9600      | 19.2k     | 38.4k     | 57.6k     | 115.2k    |

| -1          | 0.2304   | 0.4608   | 0.9216    | * 1.8432  | * 3.6864  | 5.5296    | * 11.0592 |

| -2          | 0.4608   | 0.9216   | * 1.8432  | * 3.6864  | * 7.3728  | * 11.0592 | -         |

| -3          | 0.6912   | 1.3824   | 2.7648    | 5.5296    | * 11.0592 | 16.5888   | -         |

| -4          | 0.9216   | * 1.8432 | * 3.6864  | * 7.3728  | * 14.7456 | _         | -         |

| -5          | 1.1520   | 2.3040   | 4.6080    | 9.2160    | * 18.4320 | _         | -         |

| -6          | 1.3824   | 2.7648   | 5.5296    | * 11.0592 | _         | _         | -         |

| -7          | 1.6128   | 3.2256   | 6.4512    | 12.9024   | -         | -         | -         |

| -8          | * 1.8432 | * 3.6864 | * 7.3728  | * 14.7456 | -         | -         | -         |

| -9          | 2.0736   | 4.1472   | 8.2944    | 16.5888   | -         | _         | -         |

| -10         | 2.3040   | 4.6080   | 9.2160    | * 18.4320 | _         | _         | -         |

| -11         | 2.5344   | 5.0688   | 10.1376   | _         | _         | _         | -         |

| -12         | 2.7648   | 5.5296   | * 11.0592 | -         | _         | _         | -         |

| -13         | 2.9952   | 5.9904   | 11.9808   | -         | -         | -         | -         |

| -14         | 3.2256   | 6.4512   | 12.9024   | -         | -         | -         | -         |

| -15         | 3.4560   | 6.9120   | 13.8240   | -         | -         | _         | -         |

| -16         | * 3.6864 | * 7.3728 | * 14.7456 | _         | _         | _         | -         |

| -17         | 3.9168   | 7.8336   | 15.6672   | _         | _         | _         | -         |

| -18         | 4.1472   | 8.2944   | 16.5888   | -         | _         | _         | -         |

| -19         | 4.3776   | 8.7552   | 17.5104   | -         | -         | -         | -         |

| -20         | 4.6080   | 9.2160   | * 18.4320 | -         | -         | _         | -         |

| -21         | 4.8384   | 9.6768   | 19.3536   | -         | -         |           | -         |

### NOTES TO TABLES 9 AND 10:

- 1. Tables 6 and 7 apply to UART modes 1 and 3 (variable rate modes), and show CPU clock rates in MHz for standard baud rates from 2400 to 115.2k baud.

- 2. Table 6 shows timer settings and CPU clock rates with the SMOD1 bit in the PCON register = 0 (the default after reset), while Table 7 reflects the SMOD1 bit = 1.

- 3. The tables show all potential CPU clock frequencies up to 20 MHz that may be used for baud rates from 9600 baud to 115.2k baud. Other CPU clock frequencies that would give only lower baud rates are not shown.

- 4. Table entries marked with an asterisk (\*) indicate standard crystal and ceramic resonator frequencies that may be obtained from many sources without special ordering.

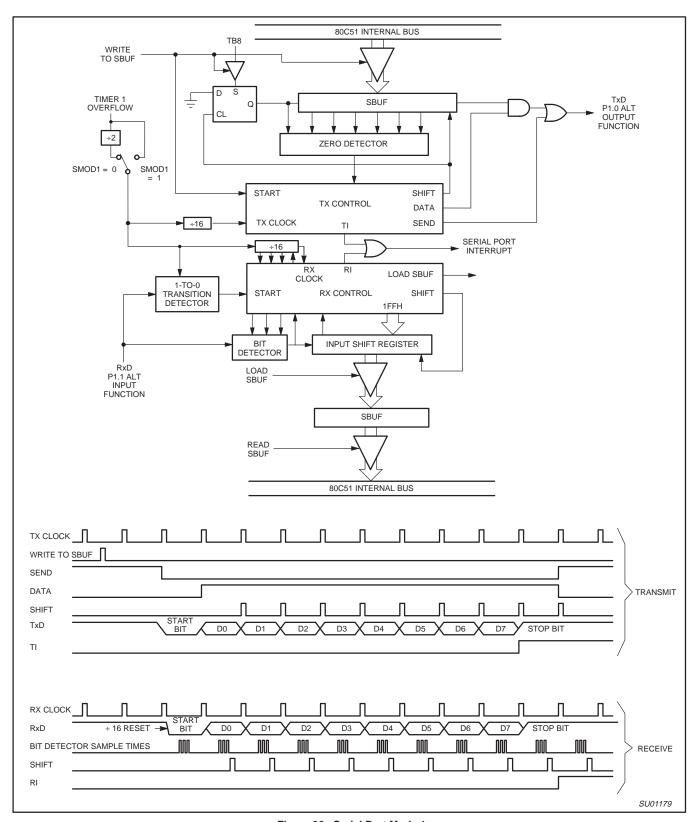

Figure 30. Serial Port Mode 1

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

#### More About UART Modes 2 and 3

Eleven bits are transmitted (through TxD), or received (through RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit (TB8) can be assigned the value of 0 or 1. On receive, the 9the data bit goes into RB8 in SCON. The baud rate is programmable to either 1/16 or 1/32 of the CPU clock frequency in Mode 2. Mode 3 may have a variable baud rate generated from Timer 1.

Figures 31 and 32 show a functional diagram of the serial port in Modes 2 and 3. The receive portion is exactly the same as in Mode 1. The transmit portion differs from Mode 1 only in the 9th bit of the transmit shift register.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads TB8 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.)

The transmission begins with activation of SEND, which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that. The first shift clocks a 1 (the stop bit) into the 9th bit position of the shift register. Thereafter, only zeros are clocked in. Thus, as data bits shift out to the right, zeros are clocked in from the left. When TB8 is at the output position of the shift register, then the stop bit is just to the left of TB8, and all positions to the left of that contain zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 11th divide-by-16 rollover after "write to SBUF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written to the input shift register.

At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of R–D. The value accepted is the value that was seen in at least 2 of the 3 samples. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. If the start bit

proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the leftmost position in the shift register (which in Modes 2 and 3 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI.

The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated. 1. RI = 0, and 2. Either SM2 = 0, or the received 9th data bit = 1.

If either of these conditions is not met, the received frame is irretrievably lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the first 8 data bits go into SBUF. One bit time later, whether the above conditions were met or not, the unit goes back to looking for a 1-to-0 transition at the RxD input.

#### **Multiprocessor Communications**

UART modes 2 and 3 have a special provision for multiprocessor communications. In these modes, 9 data bits are received or transmitted. When data is received, the 9th bit is stored in RB8. The UART can be programmed such that when the stop bit is received, the serial port interrupt will be activated only if RB8 = 1. This feature is enabled by setting bit SM2 in SCON. One way to use this feature in multiprocessor systems is as follows:

When the master processor wants to transmit a block of data to one of several slaves, it first sends out an address byte which identifies the target slave. An address byte differs from a data byte in that the 9th bit is 1 in an address byte and 0 in a data byte. With SM2 = 1, no slave will be interrupted by a data byte. An address byte, however, will interrupt all slaves, so that each slave can examine the received byte and see if it is being addressed. The addressed slave will clear its SM2 bit and prepare to receive the data bytes that follow. The slaves that weren't being addressed leave their SM2 bits set and go on about their business, ignoring the subsequent data bytes.

SM2 has no effect in Mode 0, and in Mode 1 can be used to check the validity of the stop bit, although this is better done with the Framing Error flag. In a Mode 1 reception, if SM2 = 1, the receive interrupt will not be activated unless a valid stop bit is received.

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

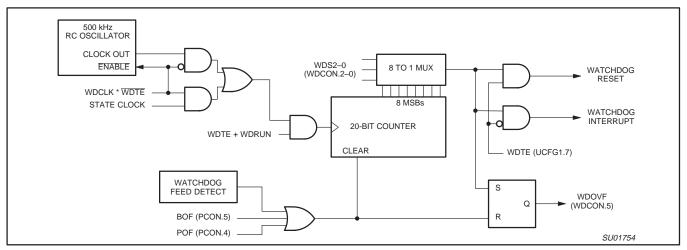

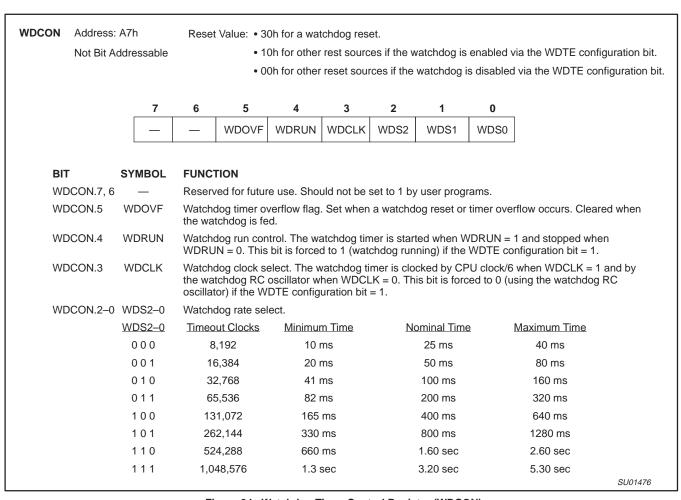

Figure 33. Block Diagram of the Watchdog Timer

Figure 34. Watchdog Timer Control Register (WDCON)

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

### DC ELECTRICAL CHARACTERISTICS (FOR P87LPC764BD, BN, BDH, FN, FD, FDH, BD/01, BDH/01)

$V_{DD} = 2.7 \text{ V to } 6.0 \text{ V}$  unless otherwise specified;  $T_{amb} = 0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  or  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise specified.

| SYMBOL                             | PARAMETER                                                    | TEST CONDITIONS                                     |                          | UNIT                |                          |        |

|------------------------------------|--------------------------------------------------------------|-----------------------------------------------------|--------------------------|---------------------|--------------------------|--------|

| STWIDUL                            | PARAMETER                                                    | TEST CONDITIONS                                     | MIN                      | TYP <sup>1</sup>    | MAX                      | UNII   |

| 1                                  | Power supply current, operating                              | 5.0 V, 20 MHz <sup>11</sup>                         |                          | 15                  | 25                       | mA     |

| I <sub>DD</sub>                    | Power supply current, operating                              | 3.0 V, 10 MHz <sup>11</sup>                         |                          | 4                   | 7                        | mA     |

|                                    | Dower supply surrent Idle mode                               | 5.0 V, 20 MHz <sup>11</sup>                         |                          | 6                   | 10                       | mA     |

| I <sub>ID</sub>                    | Power supply current, Idle mode                              | 3.0 V, 10 MHz <sup>11</sup>                         |                          | 2                   | 4                        | mA     |

| I                                  | Power supply current, Power Down mode                        | 5.0 V <sup>11</sup>                                 |                          | 1                   | 10                       | μΑ     |

| I <sub>PD</sub>                    | Fower supply current, Fower Down mode                        | 3.0 V <sup>11</sup>                                 |                          | 1                   | 5                        | μΑ     |

| $V_{RAM}$                          | RAM keep-alive voltage                                       |                                                     | 1.5                      |                     |                          | V      |

|                                    | Input low voltage (TTL input)                                | 4.0 V < V <sub>DD</sub> < 6.0 V                     | -0.5                     |                     | 0.2 V <sub>DD</sub> -0.1 | V      |

| $V_{IL}$                           | Imput low voltage (11 L imput)                               | 2.7 V < V <sub>DD</sub> < 4.0 V                     | -0.5                     |                     | 0.7                      | V      |

| V <sub>IL1</sub>                   | Negative going threshold (Schmitt input)                     |                                                     | -0.5                     |                     | 0.3 V <sub>DD</sub>      | V      |

| V <sub>IH</sub>                    | Input high voltage (TTL input)                               |                                                     | 0.2 V <sub>DD</sub> +0.9 |                     | V <sub>DD</sub> +0.5     | V      |

| V <sub>IH1</sub>                   | Positive going threshold (Schmitt input)                     |                                                     | 0.7 V <sub>DD</sub>      |                     | V <sub>DD</sub> +0.5     | V      |

| HYS                                | Hysteresis voltage                                           |                                                     |                          | 0.2 V <sub>DD</sub> |                          | V      |

| V <sub>OL</sub>                    | Output low voltage all ports <sup>5, 9</sup>                 | $I_{OL} = 3.2 \text{ mA}, V_{DD} = 2.7 \text{ V}$   |                          |                     | 0.4                      | V      |

| V <sub>OL1</sub>                   | Output low voltage all ports <sup>5, 9</sup>                 | $I_{OL} = 20 \text{ mA}, V_{DD} = 2.7 \text{ V}$    |                          |                     | 1.0                      | V      |

| \ /                                | Output high valtage all parts 3                              | $I_{OH} = -20 \mu A, V_{DD} = 2.7 V$                | V <sub>DD</sub> -0.7     |                     |                          | V      |

| V <sub>OH</sub>                    | Output high voltage, all ports <sup>3</sup>                  | $I_{OH} = -30 \mu A, V_{DD} = 4.5 V$                | V <sub>DD</sub> -0.7     |                     |                          | V      |

| V <sub>OH1</sub>                   | Output high voltage, all ports <sup>4</sup>                  | $I_{OH} = -1.0 \text{ mA}, V_{DD} = 2.7 \text{ V}$  | V <sub>DD</sub> -0.7     |                     |                          | V      |

| C <sub>IO</sub>                    | Input/Output pin capacitance <sup>10</sup>                   |                                                     |                          |                     | 15                       | pF     |

| I <sub>IL</sub>                    | Logical 0 input current, all ports <sup>8</sup>              | V <sub>IN</sub> = 0.4 V                             |                          |                     | -50                      | μΑ     |

| ILI                                | Input leakage current, all ports <sup>7</sup>                | $V_{IN} = V_{IL}$ or $V_{IH}$                       |                          |                     | ±2                       | μΑ     |

|                                    |                                                              | $V_{IN} = 1.5 \text{ V at } V_{DD} = 3.0 \text{ V}$ | -30                      |                     | -250                     | μΑ     |

| l⊤∟                                | Logical 1 to 0 transition current, all ports <sup>3, 6</sup> | $V_{IN} = 2.0 \text{ V at } V_{DD} = 5.5 \text{ V}$ | -150                     |                     | -650                     | μΑ     |

| R <sub>RST</sub>                   | Internal reset pull-up resistor <sup>14</sup>                |                                                     | 40                       |                     | 225                      | kΩ     |

| V <sub>BOLOW</sub>                 | Brownout trip voltage with BOV = 1 <sup>12</sup>             |                                                     | 2.35                     |                     | 2.69                     | V      |

| V <sub>BOHI</sub>                  | Brownout trip voltage with BOV = 0                           |                                                     | 3.45                     |                     | 3.99                     | V      |

| V <sub>REF</sub>                   | Reference voltage                                            |                                                     | 1.11                     | 1.26                | 1.41                     | V      |

| t <sub>C</sub> (V <sub>REF</sub> ) | Temperature coefficient                                      |                                                     |                          | tbd                 |                          | ppm/°( |

| SS                                 | Supply sensitivity                                           |                                                     |                          | tbd                 |                          | %/V    |

#### NOTES:

- 1. Typical ratings are not guaranteed. The values listed are at room temperature, 5 V.

- 2. See other Figures for details.

Active mode:  $I_{CC(MAX)} = tbd$

- Idle mode: I<sub>CC(MAX)</sub> = tbd

3. Ports in quasi-bidirectional mode with weak pull-up (applies to all port pins with pull-ups). Does not apply to open drain pins.

- 4. Ports in PUSH-PULL mode. Does not apply to open drain pins.

- In all output modes except high impedance mode.

- Port pins source a transition current when used in quasi-bidirectional mode and externally driven from 1 to 0. This current is highest when V<sub>IN</sub> is approximately 2 V.

- 7. Measured with port in high impedance mode. Parameter is guaranteed but not tested at cold temperature.

- 8. Measured with port in quasi-bidirectional mode.

- 9. Under steady state (non-transient) conditions, IOI must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 20 mA Maximum total I<sub>OL</sub> for all outputs: 80 mA Maximum total I<sub>OH</sub> for all outputs: 5 mA

Maximum total  $I_{OH}$  for all outputs: 5 mA If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 10. Pin capacitance is characterized but not tested.

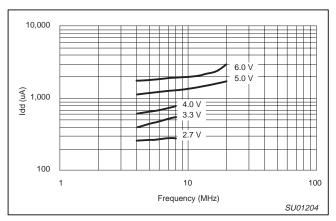

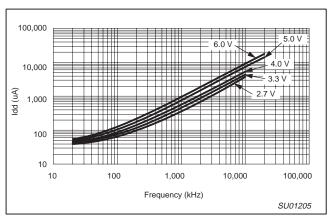

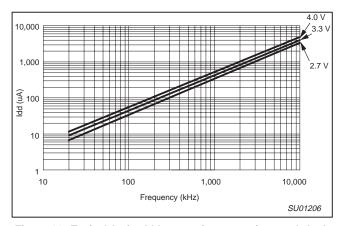

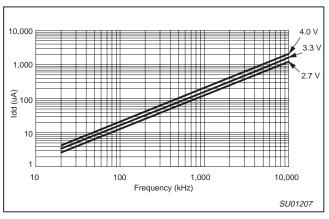

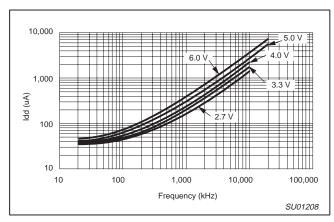

- 11. The I<sub>DD</sub>, I<sub>ID</sub>, and I<sub>PD</sub> specifications are measured using an external clock with the following functions disabled: comparators, brownout detect, and watchdog timer. For V<sub>DD</sub> = 3 V, LPEP = 1. Refer to the appropriate figures on the following pages for additional current drawn by each of these functions and detailed graphs for other frequency and voltage combinations.

- 12. Devices initially operating at V<sub>DD</sub> = 2.7V or above and at f<sub>OSC</sub> = 10 MHz or less are guaranteed to continue to execute instructions correctly at the brownout trip point. Initial power-on operation below V<sub>DD</sub> = 2.7 V is not guaranteed.

- 13. Devices initially operating at V<sub>DD</sub> = 4.0 V or above and at f<sub>OSC</sub> = 20 MHz or less are guaranteed to continue to execute instructions correctly at the brownout trip point. Initial power-on operation below V<sub>DD</sub> = 4.0 V and F<sub>OSC</sub> > 10 MHz is not guaranteed.

- 14. This internal resistor is disconnected if P1.5 is used as a general purpose input pin instead of the reset pin.

# Low power, low price, low pin count (20 pin) microcontroller with 4 kbyte OTP

P87LPC764

Figure 42. Typical Idd versus frequency (high frequency oscillator, 25°C)

Figure 43. Typical Active Idd versus frequency (external clock, 25°C, LPEP=0)

Figure 44. Typical Active Idd versus frequency (external clock, 25°C, LPEP=1)

Figure 45. Typical Idle Idd versus frequency (external clock, 25°C, LPEP=1)

Figure 46. Typical Idle Idd versus frequency (external clock, 25°C, LPEP=0)