Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | SCI                                                                         |

| Peripherals                | PWM, WDT                                                                    |

| Number of I/O              | 30                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 4x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

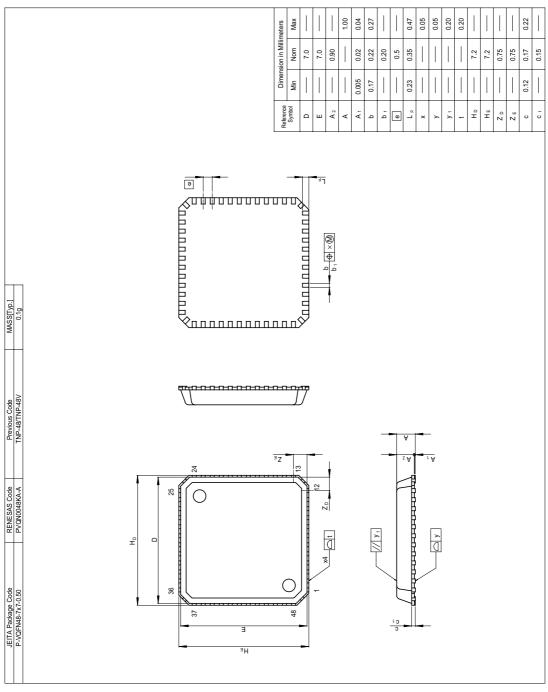

| Package / Case             | 48-VFQFN                                                                    |

| Supplier Device Package    | 48-VQFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36012ftv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

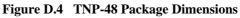

## 2.6 Basic Bus Cycle

CPU operation is synchronized by a system clock ( $\phi$ ) or a subclock ( $\phi_{sub}$ ). The period from a rising edge of  $\phi$  or  $\phi_{sub}$  to the next rising edge is called one state. A bus cycle consists of two states or three states. The cycle differs depending on whether access is to on-chip memory or to on-chip peripheral modules.

#### 2.6.1 Access to On-Chip Memory (RAM, ROM)

Access to on-chip memory takes place in two states. The data bus width is 16 bits, allowing access in byte or word size. Figure 2.9 shows the on-chip memory access cycle.

Figure 2.9 On-Chip Memory Access Cycle

## **3.2 Register Descriptions**

Interrupts are controlled by the following registers.

- Interrupt edge select register 1 (IEGR1)

- Interrupt edge select register 2 (IEGR2)

- Interrupt enable register 1 (IENR1)

- Interrupt flag register 1 (IRR1)

- Wakeup interrupt flag register (IWPR)

#### 3.2.1 Interrupt Edge Select Register 1 (IEGR1)

IEGR1 selects the direction of an edge that generates interrupt requests of pins and  $\overline{IRQ3}$  and  $\overline{IRQ0}.$

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                   |

|--------|----------|------------------|-----|-----------------------------------------------|

| 7      | _        | 0                | -   | Reserved                                      |

|        |          |                  |     | This bit is always read as 0.                 |

| 6 to 4 | _        | All 1            |     | Reserved                                      |

|        |          |                  |     | These bits are always read as 1.              |

| 3      | IEG3     | 0                | R/W | IRQ3 Edge Select                              |

|        |          |                  |     | 0: Falling edge of IRQ3 pin input is detected |

|        |          |                  |     | 1: Rising edge of IRQ3 pin input is detected  |

| 2, 1   | _        | All 0            |     | Reserved                                      |

|        |          |                  |     | These bits are always read as 0.              |

| 0      | IEG0     | 0                | R/W | IRQ0 Edge Select                              |

|        |          |                  |     | 0: Falling edge of IRQ0 pin input is detected |

|        |          |                  |     | 1: Rising edge of IRQ0 pin input is detected  |

## 3.4 Interrupt Exception Handling

#### 3.4.1 External Interrupts

There are external interrupts, NMI, IRQ3, IRQ0, and WKP.

#### (1) NMI

NMI interrupt is requested by input falling edge to pin  $\overline{\text{NMI}}$ .

NMI is the highest interrupt, and can always be accepted without depending on the I bit value in CCR.

#### (2) IRQ3 to IRQ0 Interrupts

IRQ3 to IRQ0 interrupts are requested by input signals to pins  $\overline{\text{IRQ3}}$  to  $\overline{\text{IRQ0}}$ . These four interrupts are given different vector addresses, and are detected individually by either rising edge sensing or falling edge sensing, depending on the settings of bits IEG3 to IEG0 in IEGR1.

When pins  $\overline{IRQ3}$  to  $\overline{IRQ0}$  are designated for interrupt input in PMR1 and the designated signal edge is input, the corresponding bit in IRR1 is set to 1, requesting the CPU of an interrupt. When IRQ3 to IRQ0 interrupt is accepted, the I bit is set to 1 in CCR. These interrupts can be masked by setting bits IEN3 to IEN0 in IENR1.

#### (3) WKP5 to WKP0 Interrupts

WKP5 to WKP0 interrupts are requested by input signals to pins  $\overline{WKP5}$  to  $\overline{WKP0}$ . These six interrupts have the same vector addresses, and are detected individually by either rising edge sensing or falling edge sensing, depending on the settings of bits WPEG5 to WPEG0 in IEGR2.

When pins  $\overline{WKP5}$  to  $\overline{WKP0}$  are designated for interrupt input in PMR5 and the designated signal edge is input, the corresponding bit in IWPR is set to 1, requesting the CPU of an interrupt. These interrupts can be masked by setting bit IENWP in IENR1.

## 7.3 On-Board Programming Modes

There is a mode for programming/erasing of the flash memory; boot mode, which enables onboard programming/erasing. On-board programming/erasing can also be performed in user program mode. At reset-start in reset mode, this LSI changes to a mode depending on the TEST pin settings,  $\overline{\text{NMI}}$  pin settings, and input level of each port, as shown in table 7.1. The input level of each pin must be defined four states before the reset ends.

When changing to boot mode, the boot program built into this LSI is initiated. The boot program transfers the programming control program from the externally-connected host to on-chip RAM via SCI3. After erasing the entire flash memory, the programming control program is executed. This can be used for programming initial values in the on-board state or for a forcible return when programming/erasing can no longer be done in user program mode. In user program mode, individual blocks can be erased and programmed by branching to the user program/erase control program prepared by the user.

| TEST | NMI | E10T_0 | PB0 | PB1 | PB2 | LSI State after Reset End |

|------|-----|--------|-----|-----|-----|---------------------------|

| 0    | 1   | Х      | Х   | Х   | Х   | User Mode                 |

| 0    | 0   | 1      | Х   | Х   | Х   | Boot Mode                 |

Legend: X: Don't care.

#### 7.3.1 Boot Mode

Table 7.2 shows the boot mode operations between reset end and branching to the programming control program.

- 1. When boot mode is used, the flash memory programming control program must be prepared in the host beforehand. Prepare a programming control program in accordance with the description in section 7.4, Flash Memory Programming/Erasing.

- 2. SCI3 should be set to asynchronous mode, and the transfer format as follows: 8-bit data, 1 stop bit, and no parity.

- 3. When the boot program is initiated, the chip measures the low-level period of asynchronous SCI communication data (H'00) transmitted continuously from the host. The chip then calculates the bit rate of transmission from the host, and adjusts the SCI3 bit rate to match that of the host. The reset should end with the RxD pin high. The RxD and TxD pins should be pulled up on the board if necessary. After the reset is complete, it takes approximately 100 states before the chip is ready to measure the low-level period.

## RENESAS

| Program Data | Verify Data | Reprogram Data | Comments                |

|--------------|-------------|----------------|-------------------------|

| 0            | 0           | 1              | Programming completed   |

| 0            | 1           | 0              | Reprogram bit           |

| 1            | 0           | 1              | _                       |

| 1            | 1           | 1              | Remains in erased state |

#### Table 7.4 Reprogram Data Computation Table

#### Table 7.5 Additional-Program Data Computation Table

| Reprogram Data | Verify Data | Additional-Program<br>Data | Comments                  |

|----------------|-------------|----------------------------|---------------------------|

| 0              | 0           | 0                          | Additional-program bit    |

| 0              | 1           | 1                          | No additional programming |

| 1              | 0           | 1                          | No additional programming |

| 1              | 1           | 1                          | No additional programming |

#### Table 7.6Programming Time

| n<br>(Number of Writes) | Programming<br>Time | In Additional<br>Programming | Comments |

|-------------------------|---------------------|------------------------------|----------|

| 1 to 6                  | 30                  | 10                           |          |

| 7 to 1,000              | 200                 | —                            |          |

|                         |                     |                              |          |

Note: Time shown in  $\mu$ s.

#### 7.4.2 Erase/Erase-Verify

When erasing flash memory, the erase/erase-verify flowchart shown in figure 7.4 should be followed.

- 1. Prewriting (setting erase block data to all 0s) is not necessary.

- 2. Erasing is performed in block units. Make only a single-bit specification in the erase block register (EBR1). To erase multiple blocks, each block must be erased in turn.

- 3. The time during which the E bit is set to 1 is the flash memory erase time.

- 4. The watchdog timer (WDT) is set to prevent overerasing due to program runaway, etc. An overflow cycle of approximately 19.8 ms is allowed.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                  |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------|

| 1   | OS1      | 0                | R/W | Output Select 1 and 0                                                                        |

| 0   | OS0      | 0                | R/W | These bits select an output method for the TMOV pin by the compare match of TCORA and TCNTV. |

|     |          |                  |     | 00: No change                                                                                |

|     |          |                  |     | 01: 0 output                                                                                 |

|     |          |                  |     | 10: 1 output                                                                                 |

|     |          |                  |     | 11: Output toggles                                                                           |

OS3 and OS2 select the output level for compare match B. OS1 and OS0 select the output level for compare match A. The two output levels can be controlled independently. After a reset, the timer output is 0 until the first compare match.

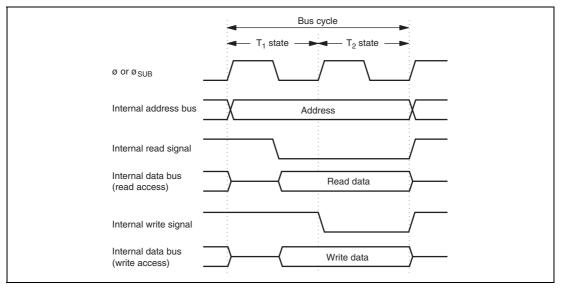

Figure 10.12 Contention between TCORA Write and Compare Match

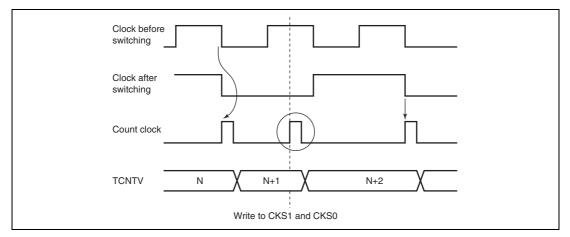

Figure 10.13 Internal Clock Switching and TCNTV Operation

#### 12.2.3 Timer Mode Register WD (TMWD)

TMWD selects the input clock.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                               |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------------|

| 7 to 4 | _        | All 1            |     | Reserved                                                                                  |

|        |          |                  |     | These bits are always read as 1.                                                          |

| 3      | CKS3     | 1                | R/W | Clock Select 3 to 0                                                                       |

| 2      | CKS2     | 1                | R/W | Select the clock to be input to TCWD.                                                     |

| 1      | CKS1     | 1                | R/W | 1000: Internal clock: counts on $\phi/64$                                                 |

| 0      | CKS0     | 1                | R/W | 1001: Internal clock: counts on $\phi/128$                                                |

|        |          |                  |     | 1010: Internal clock: counts on $\phi/256$                                                |

|        |          |                  |     | 1011: Internal clock: counts on $\phi/512$                                                |

|        |          |                  |     | 1100: Internal clock: counts on $\phi/1024$                                               |

|        |          |                  |     | 1101: Internal clock: counts on $\phi/2048$                                               |

|        |          |                  |     | 1110: Internal clock: counts on $\phi/4096$                                               |

|        |          |                  |     | 1111: Internal clock: counts on $\phi$ 8192                                               |

|        |          |                  |     | 0XXX: Internal oscillator                                                                 |

|        |          |                  |     | For the internal oscillator overflow periods, see section 18, Electrical Characteristics. |

Legend X: Don't care.

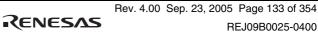

#### 13.8.4 Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

In asynchronous mode, the SCI3 operates on a basic clock with a frequency of 16 times the transfer rate. In reception, the SCI3 samples the falling edge of the start bit using the basic clock, and performs internal synchronization. Receive data is latched internally at the rising edge of the 8th pulse of the basic clock as shown in figure 13.19. Thus, the reception margin in asynchronous mode is given by formula (1) below.

$$M = \left\{ (0.5 - \frac{1}{2N}) - \frac{D - 0.5}{N} - (L - 0.5) F \right\} \times 100(\%)$$

... Formula (1)

[Legend\

N: Ratio of bit rate to clock (N = 16)

D: Clock duty (D = 0.5 to 1.0)

L: Frame length (L = 9 to 12)

F: Absolute value of clock rate deviation

Assuming values of F (absolute value of clock rate deviation) = 0 and D (clock duty) = 0.5 in formula (1), the reception margin can be given by the formula.

$M = \{0.5 - 1/(2 \times 16)\} \times 100 \ [\%] = 46.875\%$

However, this is only the computed value, and a margin of 20% to 30% should be allowed for in system design.

Figure 13.19 Receive Data Sampling Timing in Asynchronous Mode

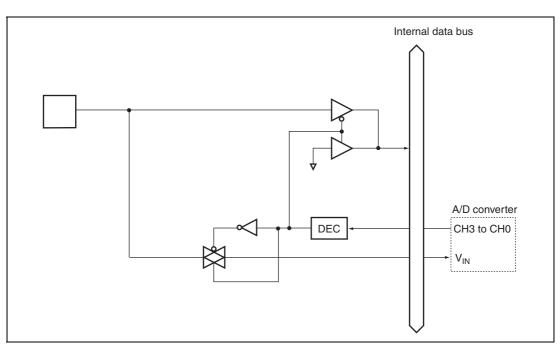

## 14.2 Input/Output Pins

Table 14.1 summarizes the input pins used by the A/D converter.

#### Table 14.1 Pin Configuration

| Pin Name                       | Symbol    | I/O   | Function                                               |

|--------------------------------|-----------|-------|--------------------------------------------------------|

| Analog power supply pin        | $AV_{cc}$ | Input | Analog block power supply pin                          |

| Analog input pin 0             | AN0       | Input | Analog input pins                                      |

| Analog input pin 1             | AN1       | Input |                                                        |

| Analog input pin 2             | AN2       | Input |                                                        |

| Analog input pin 3             | AN3       | Input |                                                        |

| A/D external trigger input pin | ADTRG     | Input | External trigger input pin for starting A/D conversion |

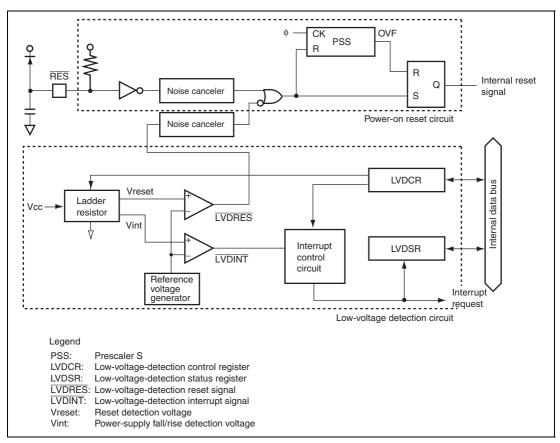

## Section 15 Power-On Reset and Low-Voltage Detection Circuits (Optional)

This LSI can include a power-on reset circuit and low-voltage detection circuit as optional circuits.

The low-voltage detection circuit consists of two circuits: LVDI (interrupt by low voltage detect) and LVDR (reset by low voltage detect) circuits.

This circuit is used to prevent abnormal operation (runaway execution) from occurring due to the power supply voltage fall and to recreate the state before the power supply voltage fall when the power supply voltage rises again.

Even if the power supply voltage falls, the unstable state when the power supply voltage falls below the guaranteed operating voltage can be removed by entering standby mode when exceeding the guaranteed operating voltage and during normal operation. Thus, system stability can be improved. If the power supply voltage falls more, the reset state is automatically entered. If the power supply voltage rises again, the reset state is held for a specified period, then active mode is automatically entered.

Figure 15.1 is a block diagram of the power-on reset circuit and the low-voltage detection circuit.

## 15.1 Features

• Power-on reset circuit

Uses an external capacitor to generate an internal reset signal when power is first supplied.

• Low-voltage detection circuit

LVDR: Monitors the power-supply voltage, and generates an internal reset signal when the voltage falls below a specified value.

LVDI: Monitors the power-supply voltage, and generates an interrupt when the voltage falls below or rises above respective specified values.

Two pairs of detection levels for reset generation voltage are available: when only the LVDR circuit is used, or when the LVDI and LVDR circuits are both used.

```

LVI0000A_000020030300

```

Figure 15.1 Block Diagram of Power-On Reset Circuit and Low-Voltage Detection Circuit

### **15.2 Register Descriptions**

The low-voltage detection circuit has the following registers.

- Low-voltage-detection control register (LVDCR)

- Low-voltage-detection status register (LVDSR)

#### 15.3.2 Low-Voltage Detection Circuit

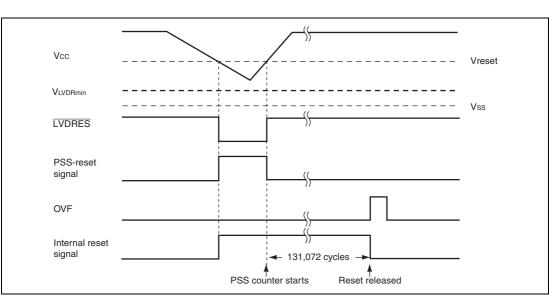

## (1) LVDR (Reset by Low Voltage Detect) Circuit

Figure 15.3 shows the timing of the LVDR function. The LVDR enters the module-standby state after a power-on reset is canceled. To operate the LVDR, set the LVDE bit in LVDCR to 1, wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc., then set the LVDRE bit in LVDCR to 1. After that, the output settings of ports must be made. To cancel the low-voltage detection circuit, first the LVDRE bit should be cleared to 0 and then the LVDE bit should be cleared to 0. The LVDE and LVDRE bits must not be cleared to 0 simultaneously because incorrect operation may occur.

When the power-supply voltage falls below the Vreset voltage (typ. = 2.3 V or 3.6 V), the LVDR clears the  $\overline{LVDRES}$  signal to 0, and resets the prescaler S. The low-voltage detection reset state remains in place until a power-on reset is generated. When the power-supply voltage rises above the Vreset voltage again, the prescaler S starts counting. It counts 131,072 clock ( $\phi$ ) cycles, and then releases the internal reset signal. In this case, the LVDE, LVDSEL, and LVDRE bits in LVDCR are not initialized.

Note that if the power supply voltage (Vcc) falls below  $V_{LVDRmin} = 1.0$  V and then rises from that point, the low-voltage detection reset may not occur.

If the power supply voltage (Vcc) falls below Vpor = 100 mV, a power-on reset occurs.

Figure 15.3 Operational Timing of LVDR Circuit

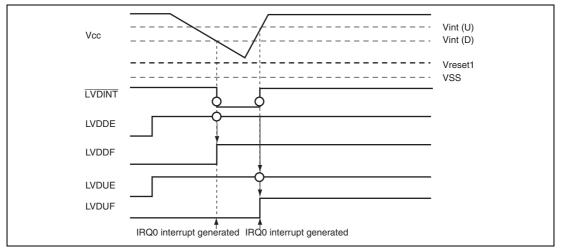

#### (2) LVDI (Interrupt by Low Voltage Detect) Circuit

Figure 15.4 shows the timing of LVDI functions. The LVDI enters the module-standby state after a power-on reset is canceled. To operate the LVDI, set the LVDE bit in LVDCR to 1, wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc., then set the LVDDE and LVDUE bits in LVDCR to 1. After that, the output settings of ports must be made. To cancel the low-voltage detection circuit, first the LVDDE and LVDUE bits should all be cleared to 0 and then the LVDDE bit should be cleared to 0. The LVDE bit must not be cleared to 0 at the same timing as the LVDDE and LVDUE bits because incorrect operation may occur.

When the power-supply voltage falls below Vint (D) (typ. = 3.7 V) voltage, the LVDI clears the  $\overline{\text{LVDINT}}$  signal to 0 and the LVDDF bit in LVDSR is set to 1. If the LVDDE bit is 1 at this time, an IRQ0 interrupt request is simultaneously generated. In this case, the necessary data must be saved in the external EEPROM, etc, and a transition must be made to standby mode or subsleep mode. Until this processing is completed, the power supply voltage must be higher than the lower limit of the guaranteed operating voltage.

When the power-supply voltage does not fall below Vreset1 (typ. = 2.3 V) voltage but rises above Vint (U) (typ. = 4.0 V) voltage, the LVDI sets the  $\overline{LVDINT}$  signal to 1. If the LVDUE bit is 1 at this time, the LVDUF bit in LVDSR is set to 1 and an IRQ0 interrupt request is simultaneously generated.

If the power supply voltage (Vcc) falls below Vreset1 (typ. = 2.3 V) voltage, the LVDR function is performed.

Figure 15.4 Operational Timing of LVDI Circuit

## 17.3 Register States in Each Operating Mode

| Register<br>Name | Reset       | Active | Sleep | Subsleep    | Standby     | Module          |

|------------------|-------------|--------|-------|-------------|-------------|-----------------|

| SMR_3            | Initialized | _      | _     | Initialized | Initialized | SCI3_3          |

| BRR_3            | Initialized | _      | —     | Initialized | Initialized | _               |

| SCR3_3           | Initialized | —      | —     | Initialized | Initialized | _               |

| TDR_3            | Initialized | _      |       | Initialized | Initialized | -               |

| SSR_3            | Initialized | _      | _     | Initialized | Initialized | _               |

| RDR_3            | Initialized | _      | _     | Initialized | Initialized | _               |

| SMCR             | Initialized | _      | _     | Initialized | Initialized | _               |

| LVDCR            | Initialized | _      | _     | _           | _           | LVDC (optional) |

| LVDSR            | Initialized | _      | _     | _           | _           | _               |

| SMR_2            | Initialized | _      | —     | Initialized | Initialized | SCI3_2          |

| BRR_2            | Initialized | _      | _     | Initialized | Initialized | _               |

| SCR3_2           | Initialized | _      | _     | Initialized | Initialized | _               |

| TDR_2            | Initialized | _      | _     | Initialized | Initialized | _               |

| SSR_2            | Initialized | _      | —     | Initialized | Initialized | _               |

| RDR_2            | Initialized | _      | —     | Initialized | Initialized | _               |

| TMRW             | Initialized | _      | _     | _           | _           | Timer W         |

| TCRW             | Initialized | _      | _     | _           | _           | _               |

| TIERW            | Initialized | _      | _     | _           | _           | _               |

| TSRW             | Initialized | _      | _     | _           | _           | -               |

| TIOR0            | Initialized | _      |       | _           | —           | -               |

| TIOR1            | Initialized | _      |       | _           | —           | -               |

| TCNT             | Initialized | _      | —     | _           | _           | _               |

| GRA              | Initialized | _      |       | _           | —           | -               |

| GRB              | Initialized | _      |       | _           | —           | -               |

| GRC              | Initialized | _      | —     | _           | _           | _               |

| GRD              | Initialized | _      | —     | _           | _           | _               |

| FLMCR1           | Initialized | —      | —     | Initialized | Initialized | ROM             |

| FLMCR2           | Initialized | _      | _     | —           | _           | _               |

| EBR1             | Initialized | —      | —     | Initialized | Initialized | _               |

| FENR             | Initialized |        |       |             |             | _               |

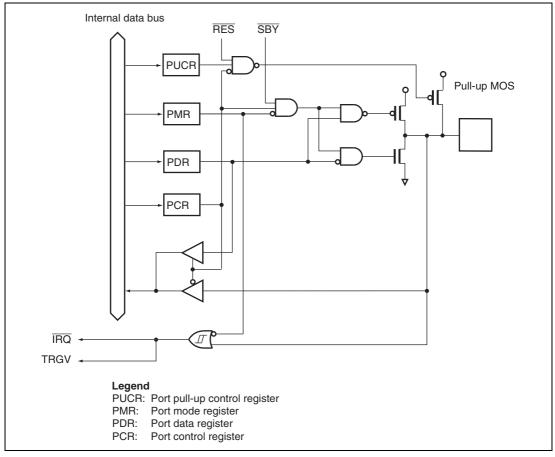

## Appendix B I/O Port Block Diagrams

## B.1 I/O Port Block Diagrams

$\overline{\text{RES}}$  goes low in a reset, and  $\overline{\text{SBY}}$  goes low in a reset and in standby mode.

Figure B.1 Port 1 Block Diagram (P17)

Figure B.23 Port B Block Diagram (PB3 to PB0)

## **B.2** Port States in Each Operating State

| Port                      | Reset          | Active            | Sleep             | Subsleep | Standby         |

|---------------------------|----------------|-------------------|-------------------|----------|-----------------|

| P17 to P14,<br>P12 to P10 | High impedance | Functioning       | Retained          | Retained | High impedance* |

| P22 to P20                | High impedance | Functioning       | Retained          | Retained | High impedance  |

| P57 to P50                | High impedance | Functioning       | Retained          | Retained | High impedance* |

| P76 to P70                | High impedance | Functioning       | Retained          | Retained | High impedance  |

| P84 to P80                | High impedance | Functioning       | Retained          | Retained | High impedance  |

| PB3 to PB0                | High impedance | High<br>impedance | High<br>impedance | Retained | High impedance  |

Note: \* High level output when the pull-up MOS is in on state.

| Product Type |                         |                               | Product Code  | Model Marking      | Package Code     |

|--------------|-------------------------|-------------------------------|---------------|--------------------|------------------|

| H8/36024     | Flash memory<br>version | Standard<br>product           | HD64F36024FP  | HD64F36024FP       | LQFP-64 (FP-64E) |

|              |                         |                               | HD64F36024FX  | HD64F36024FX       | LQFP-48 (FP-48F) |

|              |                         |                               | HD64F36024FY  | HD64F36024FY       | LQFP-48 (FP-48B) |

|              |                         |                               | HD64F36024FT  | HD64F36024FT       | QFN-48(TNP-48)   |

|              |                         | Product<br>with POR<br>& LVDC | HD64F36024GFP | HD64F36024GFP      | LQFP-64 (FP-64E) |

|              |                         |                               | HD64F36024GFX | HD64F36024GFX      | LQFP-48 (FP-48F) |

|              |                         |                               | HD64F36024GFY | HD64F36024GFY      | LQFP-48 (FP-48B) |

|              |                         |                               | HD64F36024GFT | HD64F36024GFT      | QFN-48(TNP-48)   |

|              | Masked ROM<br>version   | Standard<br>product           | HD64336024FP  | HD64336024(***)FP  | LQFP-64 (FP-64E) |

|              |                         |                               | HD64336024FX  | HD64336024(***)FX  | LQFP-48 (FP-48F) |

|              |                         |                               | HD64336024FY  | HD64336024(***)FY  | LQFP-48 (FP-48B) |

|              |                         |                               | HD64336024FT  | HD64336024(***)FT  | QFN-48(TNP-48)   |

|              |                         | Product<br>with POR<br>& LVDC | HD64336024GFP | HD64336024G(***)FP | LQFP-64 (FP-64E) |

|              |                         |                               | HD64336024GFX | HD64336024G(***)FX | LQFP-48 (FP-48F) |

|              |                         |                               | HD64336024GFY | HD64336024G(***)FY | LQFP-48 (FP-48B) |

|              |                         |                               | HD64336024GFT | HD64336024G(***)FT | QFN-48(TNP-48)   |

| H8/36023     | Masked ROM<br>version   | Standard<br>product           | HD64336023FP  | HD64336023(***)FP  | LQFP-64 (FP-64E) |

|              |                         |                               | HD64336023FX  | HD64336023(***)FX  | LQFP-48 (FP-48F) |

|              |                         |                               | HD64336023FY  | HD64336023(***)FY  | LQFP-48 (FP-48B) |

|              |                         |                               | HD64336023FT  | HD64336023(***)FT  | QFN-48(TNP-48)   |

|              |                         | Product<br>with POR<br>& LVDC | HD64336023GFP | HD64336023G(***)FP | LQFP-64 (FP-64E) |

|              |                         |                               | HD64336023GFX | HD64336023G(***)FX | LQFP-48 (FP-48F) |

|              |                         |                               | HD64336023GFY | HD64336023G(***)FY | LQFP-48 (FP-48B) |

|              |                         |                               | HD64336023GFT | HD64336023G(***)FT | QFN-48(TNP-48)   |

# Appendix C Product Code Lineup