Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LFQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36012gfpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Figures

| Section 1   | Overview                                                                 |    |

|-------------|--------------------------------------------------------------------------|----|

| Figure 1.1  | Internal Block Diagram                                                   |    |

| Figure 1.2  | Pin Arrangement (FP-64E)                                                 | 4  |

| Figure 1.3  | Pin Arrangement (FP-48F, FP-48B, TNP-48)                                 | 5  |

| Section 2   | CPU                                                                      |    |

| Figure 2.1  | Memory Map (1)                                                           | 10 |

| Figure 2.1  | Memory Map (2)                                                           | 11 |

| Figure 2.2  | CPU Registers                                                            | 12 |

| Figure 2.3  | Usage of General Registers                                               | 13 |

| Figure 2.4  | Relationship between Stack Pointer and Stack Area                        | 14 |

| Figure 2.5  | General Register Data Formats (1)                                        | 16 |

| Figure 2.5  | General Register Data Formats (2)                                        | 17 |

| Figure 2.6  | Memory Data Formats                                                      |    |

| Figure 2.7  | Instruction Formats                                                      |    |

| Figure 2.8  | Branch Address Specification in Memory Indirect Mode                     |    |

| Figure 2.9  | On-Chip Memory Access Cycle                                              |    |

|             | On-Chip Peripheral Module Access Cycle (3-State Access)                  |    |

| Figure 2.11 | CPU Operation States                                                     |    |

| Figure 2.12 | State Transitions                                                        |    |

| Figure 2.13 | Example of Timer Configuration with Two Registers Allocated to Same      |    |

| -           | Address                                                                  | 39 |

| Section 3   | Exception Handling                                                       |    |

| Figure 3.1  | Reset Sequence                                                           | 54 |

| Figure 3.2  | Stack Status after Exception Handling                                    |    |

| Figure 3.3  | Interrupt Sequence                                                       | 57 |

| Figure 3.4  | Port Mode Register Setting and Interrupt Request Flag Clearing Procedure | 58 |

| Section 4   | Address Break                                                            |    |

| Figure 4.1  | Block Diagram of Address Break                                           | 59 |

| Figure 4.2  | Address Break Interrupt Operation Example (1)                            | 63 |

| Figure 4.2  | Address Break Interrupt Operation Example (2)                            | 63 |

| Section 5   | Clock Pulse Generators                                                   |    |

| Figure 5.1  | Block Diagram of Clock Pulse Generators                                  | 65 |

| Figure 5.2  | Block Diagram of System Clock Generator                                  | 65 |

| Figure 5.3  | Typical Connection to Crystal Resonator                                  | 66 |

| Figure 5.4  | Equivalent Circuit of Crystal Resonator                                  |    |

# RENESAS

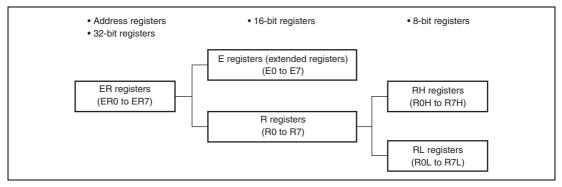

# 2.2.1 General Registers

The H8/300H CPU has eight 32-bit general registers. These general registers are all functionally identical and can be used as both address registers and data registers. When a general register is used as a data register, it can be accessed as a 32-bit, 16-bit, or 8-bit register. Figure 2.3 illustrates the usage of the general registers. When the general registers are used as 32-bit registers or address registers, they are designated by the letters ER (ER0 to ER7).

The ER registers divide into 16-bit general registers designated by the letters E (E0 to E7) and R (R0 to R7). These registers are functionally equivalent, providing a maximum of sixteen 16-bit registers. The E registers (E0 to E7) are also referred to as extended registers.

The R registers divide into 8-bit registers designated by the letters RH (R0H to R7H) and RL (R0L to R7L). These registers are functionally equivalent, providing a maximum of sixteen 8-bit registers.

The usage of each register can be selected independently.

Figure 2.3 Usage of General Registers

General register ER7 has the function of stack pointer (SP) in addition to its general-register function, and is used implicitly in exception handling and subroutine calls. Figure 2.4 shows the stack.

# 2.4 Instruction Set

## 2.4.1 Table of Instructions Classified by Function

The H8/300H CPU has 62 instructions. Tables 2.2 to 2.9 summarize the instructions in each functional category. The notation used in tables 2.2 to 2.9 is defined below.

| Symbol        | Description                                            |

|---------------|--------------------------------------------------------|

| Rd            | General register (destination)*                        |

| Rs            | General register (source)*                             |

| Rn            | General register*                                      |

| ERn           | General register (32-bit register or address register) |

| (EAd)         | Destination operand                                    |

| (EAs)         | Source operand                                         |

| CCR           | Condition-code register                                |

| Ν             | N (negative) flag in CCR                               |

| Z             | Z (zero) flag in CCR                                   |

| V             | V (overflow) flag in CCR                               |

| С             | C (carry) flag in CCR                                  |

| PC            | Program counter                                        |

| SP            | Stack pointer                                          |

| #IMM          | Immediate data                                         |

| disp          | Displacement                                           |

| +             | Addition                                               |

| _             | Subtraction                                            |

| ×             | Multiplication                                         |

| ÷             | Division                                               |

| ^             | Logical AND                                            |

| $\vee$        | Logical OR                                             |

| $\oplus$      | Logical XOR                                            |

| $\rightarrow$ | Move                                                   |

| <b>٦</b>      | NOT (logical complement)                               |

Table 2.1

Operation Notation

# 3.2.4 Interrupt Flag Register 1 (IRR1)

IRR1 is a status flag register for direct transition interrupts, and  $\overline{IRQ3}$  and  $\overline{IRQ0}$  interrupt requests.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                              |

|------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------|

| 7    | IRRDT    | 0                | R/W | Direct Transfer Interrupt Request Flag                                                                   |

|      |          |                  |     | [Setting condition]                                                                                      |

|      |          |                  |     | When a direct transfer is made by executing a SLEEP instruction while DTON in SYSCR2 is set to 1.        |

|      |          |                  |     | [Clearing condition]                                                                                     |

|      |          |                  |     | When IRRDT is cleared by writing 0                                                                       |

| 6    | _        | 0                |     | Reserved                                                                                                 |

|      |          |                  |     | This bit is always read as 0.                                                                            |

| 5, 4 | _        | All 1            |     | Reserved                                                                                                 |

|      |          |                  |     | These bits are always read as 1.                                                                         |

| 3    | IRRI3    | 0                | R/W | IRQ3 Interrupt Request Flag                                                                              |

|      |          |                  |     | [Setting condition]                                                                                      |

|      |          |                  |     | When IRQ3 pin is designated for interrupt input and the designated signal edge is detected.              |

|      |          |                  |     | [Clearing condition]                                                                                     |

|      |          |                  |     | When IRRI3 is cleared by writing 0                                                                       |

| 2, 1 |          | All 0            |     | Reserved                                                                                                 |

|      |          |                  |     | These bits are always read as 0.                                                                         |

| 0    | IRRI0    | 0                | R/W | IRQ0 Interrupt Request Flag                                                                              |

|      |          |                  |     | [Setting condition]                                                                                      |

|      |          |                  |     | When $\overline{IRQ0}$ pin is designated for interrupt input and the designated signal edge is detected. |

|      |          |                  |     | [Clearing condition]                                                                                     |

|      |          |                  |     | When IRRI0 is cleared by writing 0                                                                       |

# 6.1.2 System Control Register 2 (SYSCR2)

SYSCR2 controls the power-down modes, as well as SYSCR1.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                                |

|------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| 7    | SMSEL    | 0                | R/W | Sleep Mode Selection                                                                                                       |

|      |          |                  |     | This bit selects the mode to transit after the execution of a SLEEP instruction, as well as bit SSBY of SYSCR1.            |

|      |          |                  |     | For details, see table 6.2.                                                                                                |

| 6    | _        | 0                |     | Reserved                                                                                                                   |

|      |          |                  |     | This bit is always read as 0.                                                                                              |

| 5    | DTON     | 0                | R/W | Direct Transfer on Flag                                                                                                    |

|      |          |                  |     | This bit selects the mode to transit after the execution of a SLEEP instruction, as well as bit SSBY of SYSCR1.            |

|      |          |                  |     | For details, see table 6.2.                                                                                                |

| 4    | MA2      | 0                | R/W | Active Mode Clock Select 2 to 0                                                                                            |

| 3    | MA1      | 0                | R/W | These bits select the operating clock frequency in active                                                                  |

| 2    | MAO      | 0                | R/W | and sleep modes. The operating clock frequency<br>changes to the set frequency after the SLEEP instruction<br>is executed. |

|      |          |                  |     | OXX: $\phi_{ m osc}$                                                                                                       |

|      |          |                  |     | 100: φ <sub>osc</sub> /8                                                                                                   |

|      |          |                  |     | 101: φ <sub>osc</sub> /16                                                                                                  |

|      |          |                  |     | 110:                                                                                                                       |

|      |          |                  |     | 111:                                                                                                                       |

| 1, 0 | _        | All 0            |     | Reserved                                                                                                                   |

| _    |          |                  |     | These bits are always read as 0.                                                                                           |

Legend: X : Don't care.

The FLMCR1, FLMCR2, and EBR1 settings are retained, however program mode or erase mode is aborted at the point at which the error occurred. Program mode or erase mode cannot be reentered by re-setting the P or E bit. However, PV and EV bit setting is enabled, and a transition can be made to verify mode. Error protection can be cleared only by a reset.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                         |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------|

| 0   | WKP0     | 0                | R/W | P50/WKP0 Pin Function Switch                                                        |

|     |          |                  |     | Selects whether pin P50/ $\overline{WKP0}$ is used as P50 or as $\overline{WKP0}$ . |

|     |          |                  |     | 0: General I/O port                                                                 |

|     |          |                  |     | 1: WKP0 input pin                                                                   |

# 9.3.2 Port Control Register 5 (PCR5)

PCR5 selects inputs/outputs in bit units for pins to be used as general I/O ports of port 5.

|   |       |   | R/W | Description                                                                                                       |

|---|-------|---|-----|-------------------------------------------------------------------------------------------------------------------|

| 7 | PCR57 | 0 | W   | When each of the port 5 pins P57 to P50 functions as an                                                           |

| 6 | PCR56 | 0 | W   | general I/O port, setting a PCR5 bit to 1 makes the corresponding pin an output port, while clearing the bit to 0 |

| 5 | PCR55 | 0 | W   | makes the pin an input port.                                                                                      |

| 4 | PCR54 | 0 | W   |                                                                                                                   |

| 3 | PCR53 | 0 | W   |                                                                                                                   |

| 2 | PCR52 | 0 | W   |                                                                                                                   |

| 1 | PCR51 | 0 | W   |                                                                                                                   |

| 0 | PCR50 | 0 | W   |                                                                                                                   |

# 9.3.3 Port Data Register 5 (PDR5)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                      |  |  |  |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------|--|--|--|

| 7   | P57      | 0                | R/W | Stores output data for port 5 pins.                                              |  |  |  |

| 6   | P56      | 0                | R/W | If PDR5 is read while PCR5 bits are set to 1, the value                          |  |  |  |

| 5   | P55      | 0                | R/W | stored in PDR5 are read. If PDR5 is read while PCR5 bits                         |  |  |  |

| 4   | P54      | 0                | R/W | are cleared to 0, the pin states are read regardless of th value stored in PDR5. |  |  |  |

| 3   | P53      | 0                | R/W |                                                                                  |  |  |  |

| 2   | P52      | 0                | R/W |                                                                                  |  |  |  |

| 1   | P51      | 0                | R/W |                                                                                  |  |  |  |

| 0   | P50      | 0                | R/W |                                                                                  |  |  |  |

PDR5 is a general I/O port data register of port 5.

# 9.3.4 Port Pull-Up Control Register 5 (PUCR5)

PUCR5 controls the pull-up MOS in bit units of the pins set as the input ports.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                           |

|------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 7, 6 | —        | All 0            | _   | Reserved                                                                                                              |

|      |          |                  |     | These bits are always read as 0.                                                                                      |

| 5    | PUCR55   | 0                | R/W | Only bits for which PCR5 is cleared are valid. The pull-up                                                            |

| 4    | PUCR54   | 0                | R/W | MOS of the corresponding pins enter the on-state when<br>these bits are set to 1, while they enter the off-state when |

| 3    | PUCR53   | 0                | R/W | these bits are cleared to 0.                                                                                          |

| 2    | PUCR52   | 0                | R/W |                                                                                                                       |

| 1    | PUCR51   | 0                | R/W |                                                                                                                       |

| 0    | PUCR50   | 0                | R/W |                                                                                                                       |

# Section 10 Timer V

Timer V is an 8-bit timer based on an 8-bit counter. Timer V counts external events. Comparematch signals with two registers can also be used to reset the counter, request an interrupt, or output a pulse signal with an arbitrary duty cycle. Counting can be initiated by a trigger input at the TRGV pin, enabling pulse output control to be synchronized to the trigger, with an arbitrary delay from the trigger input. Figure 10.1 shows a block diagram of timer V.

# 10.1 Features

- Choice of seven clock signals is available.

Choice of six internal clock sources (φ/128, φ/64, φ/32, φ/16, φ/8, φ/4) or an external clock.

- Counter can be cleared by compare match A or B, or by an external reset signal. If the count stop function is selected, the counter can be halted when cleared.

- Timer output is controlled by two independent compare match signals, enabling pulse output with an arbitrary duty cycle, PWM output, and other applications.

- Three interrupt sources: compare match A, compare match B, timer overflow

- Counting can be initiated by trigger input at the TRGV pin. The rising edge, falling edge, or both edges of the TRGV input can be selected.

# 10.3.4 Timer Control/Status Register V (TCSRV)

TCSRV indicates the status flag and controls outputs by using a compare match.

|     |          | Initial |     |                                                                                              |

|-----|----------|---------|-----|----------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                  |

| 7   | CMFB     | 0       | R/W | Compare Match Flag B                                                                         |

|     |          |         |     | Setting condition:                                                                           |

|     |          |         |     | When the TCNTV value matches the TCORB value                                                 |

|     |          |         |     | Clearing condition:                                                                          |

|     |          |         |     | After reading CMFB = 1, cleared by writing 0 to CMFB                                         |

| 6   | CMFA     | 0       | R/W | Compare Match Flag A                                                                         |

|     |          |         |     | Setting condition:                                                                           |

|     |          |         |     | When the TCNTV value matches the TCORA value                                                 |

|     |          |         |     | Clearing condition:                                                                          |

|     |          |         |     | After reading CMFA = 1, cleared by writing 0 to CMFA                                         |

| 5   | OVF      | 0       | R/W | Timer Overflow Flag                                                                          |

|     |          |         |     | Setting condition:                                                                           |

|     |          |         |     | When TCNTV overflows from H'FF to H'00                                                       |

|     |          |         |     | Clearing condition:                                                                          |

|     |          |         |     | After reading OVF = 1, cleared by writing 0 to OVF                                           |

| 4   |          | 1       |     | Reserved                                                                                     |

|     |          |         |     | This bit is always read as 1.                                                                |

| 3   | OS3      | 0       | R/W | Output Select 3 and 2                                                                        |

| 2   | OS2      | 0       | R/W | These bits select an output method for the TMOV pin by the compare match of TCORB and TCNTV. |

|     |          |         |     | 00: No change                                                                                |

|     |          |         |     | 01: 0 output                                                                                 |

|     |          |         |     | 10: 1 output                                                                                 |

|     |          |         |     | 11: Output toggles                                                                           |

# 10.4 Operation

## 10.4.1 Timer V Operation

- According to table 10.2, six internal/external clock signals output by prescaler S can be selected as the timer V operating clock signals. When the operating clock signal is selected, TCNTV starts counting-up. Figure 10.2 shows the count timing with an internal clock signal selected, and figure 10.3 shows the count timing with both edges of an external clock signal selected.

- 2. When TCNTV overflows (changes from H'FF to H'00), the overflow flag (OVF) in TCRV0 will be set. The timing at this time is shown in figure 10.4. An interrupt request is sent to the CPU when OVIE in TCRV0 is 1.

- 3. TCNTV is constantly compared with TCORA and TCORB. Compare match flag A or B (CMFA or CMFB) is set to 1 when TCNTV matches TCORA or TCORB, respectively. The compare-match signal is generated in the last state in which the values match. Figure 10.5 shows the timing. An interrupt request is generated for the CPU when CMIEA or CMIEB in TCRV0 is 1.

- 4. When a compare match A or B is generated, the TMOV responds with the output value selected by bits OS3 to OS0 in TCSRV. Figure 10.6 shows the timing when the output is toggled by compare match A.

- 5. When CCLR1 or CCLR0 in TCRV0 is 01 or 10, TCNTV can be cleared by the corresponding compare match. Figure 10.7 shows the timing.

- 6. When CCLR1 or CCLR0 in TCRV0 is 11, TCNTV can be cleared by the rising edge of the input of TMRIV pin. A TMRIV input pulse-width of at least 1.5 system clocks is necessary. Figure 10.8 shows the timing.

- 7. When a counter-clearing source is generated with TRGE in TCRV1 set to 1, the counting-up is halted as soon as TCNTV is cleared. TCNTV resumes counting-up when the edge selected by TVEG1 or TVEG0 in TCRV1 is input from the TGRV pin.

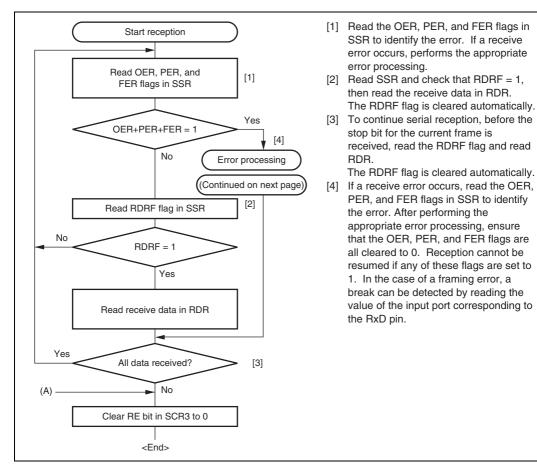

Figure 13.8 Sample Serial Reception Data Flowchart (Asynchronous Mode)(1)

# 13.5 Operation in Clocked Synchronous Mode

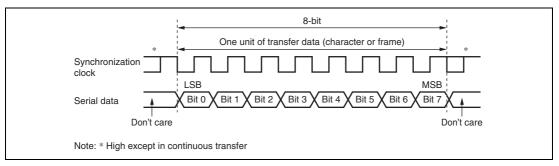

Figure 13.9 shows the general format for clocked synchronous communication. In clocked synchronous mode, data is transmitted or received synchronous with clock pulses. A single character in the transmit data consists of the 8-bit data starting from the LSB. In clocked synchronous serial communication, data on the transmission line is output from one falling edge of the synchronization clock to the next. In clocked synchronous mode, the SCI3 receives data in synchronous with the rising edge of the synchronization clock. After 8-bit data is output, the transmission line holds the MSB state. In clocked synchronous mode, no parity or multiprocessor bit is added. Inside the SCI3, the transmitter and receiver are independent units, enabling full-duplex communication through the use of a common clock. Both the transmitter and the receiver also have a double-buffered structure, so data can be read or written during transmission or reception, enabling continuous data transfer.

Figure 13.9 Data Format in Clocked Synchronous Communication

# 13.5.1 Clock

Either an internal clock generated by the on-chip baud rate generator or an external synchronization clock input at the SCK3 pin can be selected, according to the setting of the COM bit in SMR and CKE0 and CKE1 bits in SCR3. When the SCI3 is operated on an internal clock, the synchronization clock is output from the SCK3 pin. Eight synchronization clock pulses are output in the transfer of one character, and when no transfer is performed the clock is fixed high.

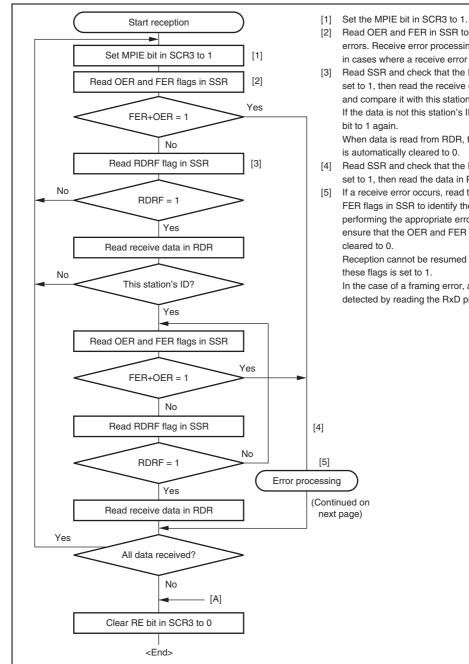

[2] Read OER and FER in SSR to check for errors. Receive error processing is performed in cases where a receive error occurs.

[3] Read SSR and check that the RDRF flag is set to 1, then read the receive data in RDR and compare it with this station's ID. If the data is not this station's ID, set the MPIE

When data is read from RDR, the RDRF flag is automatically cleared to 0.

[4] Read SSR and check that the RDRF flag is set to 1, then read the data in RDR.

[5] If a receive error occurs, read the OER and FER flags in SSR to identify the error. After performing the appropriate error processing, ensure that the OER and FER flags are all

Reception cannot be resumed if either of

In the case of a framing error, a break can be detected by reading the RxD pin value.

## Figure 13.17 Sample Multiprocessor Serial Reception Flowchart (1)

RENESAS

# 14.4.3 Input Sampling and A/D Conversion Time

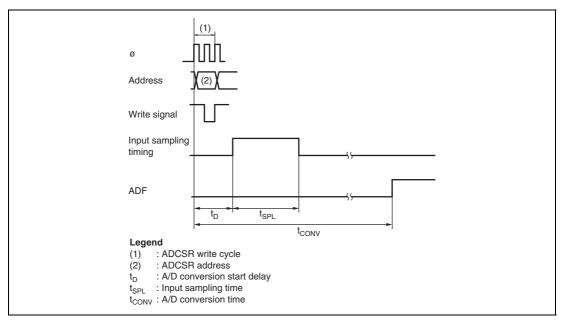

The A/D converter has a built-in sample-and-hold circuit. The A/D converter samples the analog input when the A/D conversion start delay time  $(t_D)$  has passed after the ADST bit is set to 1, then starts conversion. Figure 14.2 shows the A/D conversion timing. Table 14.3 shows the A/D conversion time.

As indicated in figure 14.2, the A/D conversion time includes  $t_D$  and the input sampling time. The length of  $t_D$  varies depending on the timing of the write access to ADCSR. The total conversion time therefore varies within the ranges indicated in table 14.3.

In scan mode, the values given in table 14.3 apply to the first conversion time. In the second and subsequent conversions, the conversion time is 128 states (fixed) when CKS = 0 and 66 states (fixed) when CKS = 1.

Figure 14.2 A/D Conversion Timing

RENESAS

| Register Name                     | Abbre-<br>viation | Bit No | Address | Module<br>Name | Data Bus<br>Width | Access<br>State |

|-----------------------------------|-------------------|--------|---------|----------------|-------------------|-----------------|

| Interrupt edge select register 2  | IEGR2             | 8      | H'FFF3  | Interrupts     | 8                 | 2               |

| Interrupt enable register 1       | IENR1             | 8      | H'FFF4  | Interrupts     | 8                 | 2               |

| Interrupt flag register 1         | IRR1              | 8      | H'FFF6  | Interrupts     | 8                 | 2               |

| Wake-up interrupt flag register   | IWPR              | 8      | H'FFF8  | Interrupts     | 8                 | 2               |

| Module standby control register 1 | MSTCR1            | 8      | H'FFF9  | Power-<br>down | 8                 | 2               |

| Module standby control register 2 | MSTCR2            | 8      | H'FFFA  | Power-<br>down | 8                 | 2               |

Notes: 1. LVDC: Low-voltage detection circuits (optional)

2. Only word access can be used.

3. WDT: Watchdog timer

|          |                    |              |    | Addressing Mode and<br>Instruction Length (bytes) |     |           |             |     |          |     |  |                                                     |   |     |       |      |     |    | No.<br>Stat | . of<br>es <sup>*1</sup> |

|----------|--------------------|--------------|----|---------------------------------------------------|-----|-----------|-------------|-----|----------|-----|--|-----------------------------------------------------|---|-----|-------|------|-----|----|-------------|--------------------------|

| Mnemonic |                    | Operand Size | ×  |                                                   | ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @aa |  | Operation                                           |   | Con | ditio | n Co | ode |    | Normal      | Advanced                 |

|          | ŏ                  | XX#          | Rn | 0                                                 | 0   | Ö         | 0           | 0   | 0        | Ι   |  | I                                                   | н | N   | z     | v    | с   | ž  | Ad          |                          |

| BLD      | BLD #xx:3, @ERd    | В            |    |                                                   | 4   |           |             |     |          |     |  | (#xx:3 of @ERd) $\rightarrow$ C                     | - | -   | —     | —    | -   | \$ | e           | 6                        |

|          | BLD #xx:3, @aa:8   | В            |    |                                                   |     |           |             | 4   |          |     |  | (#xx:3 of @aa:8) $\rightarrow$ C                    | - | —   | —     | —    | —   | \$ | 6           | 6                        |

| BILD     | BILD #xx:3, Rd     | В            |    | 2                                                 |     |           |             |     |          |     |  | $\neg$ (#xx:3 of Rd8) $\rightarrow$ C               | - | —   | —     | —    | —   | \$ | 2           | 2                        |

|          | BILD #xx:3, @ERd   | В            |    |                                                   | 4   |           |             |     |          |     |  | $\neg \text{ (#xx:3 of @ERd)} \rightarrow \text{C}$ | - | —   | —     | —    | —   | \$ | 6           | 6                        |

|          | BILD #xx:3, @aa:8  | В            |    |                                                   |     |           |             | 4   |          |     |  | $\neg$ (#xx:3 of @aa:8) $\rightarrow$ C             | - | —   | —     | —    | —   |    | 6           | 6                        |

| BST      | BST #xx:3, Rd      | В            |    | 2                                                 |     |           |             |     |          |     |  | $C \rightarrow (\#xx:3 \text{ of } Rd8)$            | - | -   | —     | —    | -   | -  | 2           | 2                        |

|          | BST #xx:3, @ERd    | В            |    |                                                   | 4   |           |             |     |          |     |  | $C \rightarrow (\#xx:3 \text{ of } @ERd24)$         | - | -   | —     | —    | -   | -  | 6           | 3                        |

| BIST     | BST #xx:3, @aa:8   | В            |    |                                                   |     |           |             | 4   |          |     |  | $C \rightarrow (\#xx:3 \text{ of } @aa:8)$          | - | -   | —     | —    | -   | -  | 8           | 3                        |

|          | BIST #xx:3, Rd     | В            |    | 2                                                 |     |           |             |     |          |     |  | $\neg C \rightarrow (\#xx:3 \text{ of Rd8})$        | - | -   | —     | —    | —   | —  | 2           | 2                        |

|          | BIST #xx:3, @ERd   | В            |    |                                                   | 4   |           |             |     |          |     |  | $\neg C \rightarrow (\#xx:3 \text{ of } @ERd24)$    | - | -   | —     | —    | —   | —  | 8           | 3                        |

|          | BIST #xx:3, @aa:8  | В            |    |                                                   |     |           |             | 4   |          |     |  | $\neg C \rightarrow (\#xx:3 \text{ of } @aa:8)$     | - | -   | —     | —    | —   | —  | 8           | 3                        |

| BAND     | BAND #xx:3, Rd     | В            |    | 2                                                 |     |           |             |     |          |     |  | $C \land (\#xx:3 \text{ of } Rd8) \rightarrow C$    | - | —   | —     | —    | —   | \$ | 2           | 2                        |

|          | BAND #xx:3, @ERd   | В            |    |                                                   | 4   |           |             |     |          |     |  | $C \land (\#xx:3 \text{ of } @ERd24) \rightarrow C$ | - | -   | —     | —    | —   | \$ | e           | 6                        |

| BIAND    | BAND #xx:3, @aa:8  | В            |    |                                                   |     |           |             | 4   |          |     |  | $C \land (\#xx:3 \text{ of } @aa:8) \rightarrow C$  | - | -   | —     | —    | —   | \$ | e           | 6                        |

|          | BIAND #xx:3, Rd    | В            |    | 2                                                 |     |           |             |     |          |     |  | $C_{\wedge} \neg$ (#xx:3 of Rd8) $\rightarrow C$    | - | —   | —     | —    | —   | \$ | 2           | 2                        |

|          | BIAND #xx:3, @ERd  | В            |    |                                                   | 4   |           |             |     |          |     |  | $C \land \neg$ (#xx:3 of @ERd24) $\rightarrow C$    | — | —   | —     | —    | —   | \$ | e           | 6                        |

|          | BIAND #xx:3, @aa:8 | в            |    |                                                   |     |           |             | 4   |          |     |  | $C \land \neg$ (#xx:3 of @aa:8) $\rightarrow C$     | - | _   | —     | —    | —   | \$ | 6           | 6                        |

| BOR      | BOR #xx:3, Rd      | в            |    | 2                                                 |     |           |             |     |          |     |  | C/(#xx:3 of Rd8) $\rightarrow$ C                    | - | _   | —     | —    | —   | \$ | 2           | 2                        |

|          | BOR #xx:3, @ERd    | В            |    |                                                   | 4   |           |             |     |          |     |  | C/(#xx:3 of @ERd24) $\rightarrow$ C                 | - | -   | —     | —    | -   | \$ | e           | 6                        |

|          | BOR #xx:3, @aa:8   | В            |    |                                                   |     |           |             | 4   |          |     |  | C/(#xx:3 of @aa:8) $\rightarrow$ C                  | - | -   | —     | —    | -   | \$ | e           | 6                        |

| BIOR     | BIOR #xx:3, Rd     | В            |    | 2                                                 |     |           |             |     |          |     |  | C⁄ ¬ (#xx:3 of Rd8) → C                             | - | -   | —     | —    | —   | \$ | 2           | 2                        |

|          | BIOR #xx:3, @ERd   | В            |    |                                                   | 4   |           |             |     |          |     |  | C⁄ ¬ (#xx:3 of @ERd24) → C                          | - | -   | —     | —    | —   | \$ | 6           | 6                        |

|          | BIOR #xx:3, @aa:8  | в            |    |                                                   |     |           |             | 4   |          |     |  | C⁄ ¬ (#xx:3 of @aa:8) → C                           | - | —   | —     | _    | —   | \$ | e           | 6                        |

| BXOR     | BXOR #xx:3, Rd     | В            |    | 2                                                 |     |           |             |     |          |     |  | C⊕(#xx:3 of Rd8) $\rightarrow$ C                    | - | -   | -     | _    | -   | \$ | 2           | 2                        |

|          | BXOR #xx:3, @ERd   | В            |    |                                                   | 4   |           |             |     |          |     |  | C⊕(#xx:3 of @ERd24) → C                             | - | -   | -     | _    | -   | \$ | e           | 6                        |

|          | BXOR #xx:3, @aa:8  | в            |    |                                                   |     |           |             | 4   |          |     |  | C⊕(#xx:3 of @aa:8) → C                              | - | -   | -     | _    | -   | \$ | e           | 6                        |

| BIXOR    | BIXOR #xx:3, Rd    | В            |    | 2                                                 |     |           |             |     |          |     |  | C⊕ ¬ (#xx:3 of Rd8) $\rightarrow$ C                 | - | -   | -     | _    | -   | \$ | 2           | 2                        |

|          | BIXOR #xx:3, @ERd  | В            |    |                                                   | 4   |           |             |     |          |     |  | C⊕ ¬ (#xx:3 of @ERd24) → C                          | - | -   | -     | _    | -   | \$ | E           | 6                        |

|          | BIXOR #xx:3, @aa:8 | в            |    |                                                   |     |           |             | 4   |          |     |  | C⊕ ¬ (#xx:3 of @aa:8) → C                           | - | -   | —     | _    | -   | \$ | 6           | 6                        |

# Appendix B I/O Port Block Diagrams

# B.1 I/O Port Block Diagrams

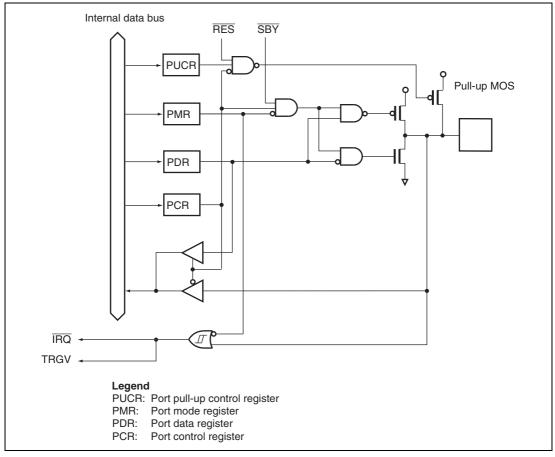

$\overline{\text{RES}}$  goes low in a reset, and  $\overline{\text{SBY}}$  goes low in a reset and in standby mode.

Figure B.1 Port 1 Block Diagram (P17)

### RenesasTechnologyCorp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United Kingdom Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

### Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. Unit2607 Ruijing Building, No.205 Maaming Road (S), Shanghai 200020, China Tel: <86- (21) 6472-1001, Fax: <86- (21) 6415-2952

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001 Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> 2-796-3115, Fax: <82> 2-796-2145

Renesas Technology Malaysia Sdn. Bhd. Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com