#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-VFQFN                                                                     |

| Supplier Device Package    | 48-VQFN (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36012gftv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 18.5 | Output Load Condition                             |     |

|------|---------------------------------------------------|-----|

| Арре | endix A Instruction Set                           |     |

| A.1  | Instruction List                                  |     |

| A.2  | Operation Code Map                                |     |

| A.3  | Number of Execution States                        | 303 |

| A.4  | Combinations of Instructions and Addressing Modes |     |

| App  | endix B I/O Port Block Diagrams                   |     |

| B.1  | I/O Port Block Diagrams                           |     |

|      | Port States in Each Operating State               |     |

| Appo | endix C Product Code Lineup                       |     |

| Appo | endix D Package Dimensions                        |     |

| Mair | n Revisions and Additions in this Edition         |     |

| Inde | х                                                 |     |

- General I/O ports

- I/O pins: 30 I/O pins, including 5 large current ports (I<sub>oL</sub> = 20 mA, @V<sub>oL</sub> = 1.5 V)

- Input-only pins: 4 input pins (also used for analog input)

- Supports various power-down modes

Note: F-ZTAT<sup>™</sup> is a trademark of Renesas Technology Corp.

• Compact package

| Package | Code   | Body Size           | Pin Pitch |

|---------|--------|---------------------|-----------|

| LQFP-64 | FP-64E | 10.0	imes10.0 mm    | 0.5 mm    |

| LQFP-48 | FP-48F | 10.0 	imes 10.0  mm | 0.65 mm   |

| LQFP-48 | FP-48B | 7.0 	imes 7.0 mm    | 0.5 mm    |

| QFN-48  | TNP-48 | 7.0 	imes 7.0  mm   | 0.5 mm    |

| Instruction | Size*        | Function                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DIVXS       | B/W          | $\begin{array}{l} \text{Rd} \div \text{Rs} \rightarrow \text{Rd} \\ \text{Performs signed division on data in two general registers: either 16 bits} \\ \div 8 \text{ bits} \rightarrow 8 \text{-bit quotient and 8-bit remainder or 32 bits} \div 16 \text{ bits} \rightarrow 16 \text{-bit} \\ \text{quotient and 16-bit remainder.} \end{array}$ |  |  |  |

| СМР         | B/W/L        | Rd – Rs, Rd – #IMM<br>Compares data in a general register with data in another general<br>register or with immediate data, and sets CCR bits according to the<br>result.                                                                                                                                                                            |  |  |  |

| NEG         | B/W/L        | 0 – Rd $\rightarrow$ Rd<br>Takes the two's complement (arithmetic complement) of data in a<br>general register.                                                                                                                                                                                                                                     |  |  |  |

| EXTU        | W/L          | Rd (zero extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size, or the lower 16<br>bits of a 32-bit register to longword size, by padding with zeros on the<br>left.                                                                                                                                            |  |  |  |

| EXTS        | W/L          | Rd (sign extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size, or the lower 16<br>bits of a 32-bit register to longword size, by extending the sign bit.                                                                                                                                                       |  |  |  |

| Note: * Re  | efers to the | operand size.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| B: Byt      | e            |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| W: W        | ord          |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

#### **Arithmetic Operations Instructions (2)** Table 2.3

W: Word

L: Longword

#### **Logic Operations Instructions** Table 2.4

| Instruction | Size* | Function                                                                                                                                                                              |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND         | B/W/L | $Rd \wedge Rs \rightarrow Rd$ , $Rd \wedge #IMM \rightarrow Rd$<br>Performs a logical AND operation on a general register and another<br>general register or immediate data.          |

| OR          | B/W/L | $Rd \lor Rs \rightarrow Rd$ , $Rd \lor \#IMM \rightarrow Rd$<br>Performs a logical OR operation on a general register and another<br>general register or immediate data.              |

| XOR         | B/W/L | $Rd \oplus Rs \rightarrow Rd$ , $Rd \oplus #IMM \rightarrow Rd$<br>Performs a logical exclusive OR operation on a general register and<br>another general register or immediate data. |

| NOT         | B/W/L | $\neg$ (Rd) $\rightarrow$ (Rd)<br>Takes the one's complement of general register contents.                                                                                            |

# 3.2.2 Interrupt Edge Select Register 2 (IEGR2)

IEGR2 selects the direction of an edge that generates interrupt requests of the pins  $\overline{\text{ADTRG}}$  and  $\overline{\text{WKP5}}$  to  $\overline{\text{WKP0}}$ .

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                       |

|------|----------|------------------|-----|-----------------------------------------------------------------------------------|

| 7, 6 | _        | All 1            |     | Reserved                                                                          |

|      |          |                  |     | These bits are always read as 1.                                                  |

| 5    | WPEG5    | 0                | R/W | WKP5 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP5}$ ( $\overline{ADTRG}$ ) pin input is detected |

|      |          |                  |     | 1: Rising edge of $\overline{WKP5}$ ( $\overline{ADTRG}$ ) pin input is detected  |

| 4    | WPEG4    | 0                | R/W | WKP4 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP4}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of $\overline{WKP4}$ pin input is detected                         |

| 3    | WPEG3    | 0                | R/W | WKP3 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP3}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP3 pin input is detected                                      |

| 2    | WPEG2    | 0                | R/W | WKP2 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP2}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP2 pin input is detected                                      |

| 1    | WPEG1    | 0                | R/W | WKP1Edge Select                                                                   |

|      |          |                  |     | 0: Falling edge of $\overline{WKP1}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of $\overline{WKP1}$ pin input is detected                         |

| 0    | WPEG0    | 0                | R/W | WKP0 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP0}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP0 pin input is detected                                      |

# Section 8 RAM

This LSI has 2 kbytes of on-chip high-speed static RAM. The RAM is connected to the CPU by a 16-bit data bus, enabling two-state access by the CPU to both byte data and word data.

| Product Classification |                      | RAM Size  | RAM Address       |

|------------------------|----------------------|-----------|-------------------|

| Flash memory version   | H8/36024F, H8/36014F | 2 kbytes  | H'F780 to H'FF7F* |

|                        | H8/36022F, H8/36012F | 2 kbytes  | H'F780 to H'FF7F* |

| Masked ROM version     | H8/36024, H8/36014   | 1 kbyte   | H'FB80 to H'FF7F  |

|                        | H8/36023, H8/36013   | 1 kbyte   | H'FB80 to H'FF7F  |

|                        | H8/36022, H8/36012   | 512 bytes | H'FD80 to H'FF7F  |

|                        | H8/36011             | 512 bytes | H'FD80 to H'FF7F  |

|                        | H8/36010             | 512 bytes | H'FD80 to H'FF7F  |

Note: \* When the E7 or E8 is used, area H'F780 to H'FB7F must not be accessed.

### 9.3.3 Port Data Register 5 (PDR5)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                       |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------|

| 7   | P57      | 0                | R/W | Stores output data for port 5 pins.                                               |

| 6   | P56      | 0                | R/W | If PDR5 is read while PCR5 bits are set to 1, the value                           |

| 5   | P55      | 0                | R/W | stored in PDR5 are read. If PDR5 is read while PCR5 bits                          |

| 4   | P54      | 0                | R/W | are cleared to 0, the pin states are read regardless of the value stored in PDR5. |

| 3   | P53      | 0                | R/W |                                                                                   |

| 2   | P52      | 0                | R/W |                                                                                   |

| 1   | P51      | 0                | R/W |                                                                                   |

| 0   | P50      | 0                | R/W |                                                                                   |

PDR5 is a general I/O port data register of port 5.

# 9.3.4 Port Pull-Up Control Register 5 (PUCR5)

PUCR5 controls the pull-up MOS in bit units of the pins set as the input ports.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                           |

|------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 7, 6 | —        | All 0            | _   | Reserved                                                                                                              |

|      |          |                  |     | These bits are always read as 0.                                                                                      |

| 5    | PUCR55   | 0                | R/W | Only bits for which PCR5 is cleared are valid. The pull-up                                                            |

| 4    | PUCR54   | 0                | R/W | MOS of the corresponding pins enter the on-state when<br>these bits are set to 1, while they enter the off-state when |

| 3    | PUCR53   | 0                | R/W | these bits are cleared to 0.                                                                                          |

| 2    | PUCR52   | 0                | R/W |                                                                                                                       |

| 1    | PUCR51   | 0                | R/W |                                                                                                                       |

| 0    | PUCR50   | 0                | R/W |                                                                                                                       |

#### 9.3.5 Pin Functions

The correspondence between the register specification and the port functions is shown below.

• P57/TXD\_3\* pin

| Register      | SMCR* | PCR5  |                   |

|---------------|-------|-------|-------------------|

| Bit Name      | TXD_3 | PCR57 | Pin Function      |

| Setting Value | 0     | 0     | P57 input pin     |

|               |       | 1     | P57 output pin    |

|               | 1     | Х     | TXD_3 output pin* |

Legend X: Don't care.

Note: \* Not available in the H8/36014.

• P56/RXD\_3\* pin

#### Register SCR3\_3\* PCR5

| Bit Name      | RE | PCR56 | Pin Function     |

|---------------|----|-------|------------------|

| Setting Value | 0  | 0     | P56 input pin    |

|               |    | 1     | P56 output pin   |

|               | 1  | Х     | RXD_3 input pin* |

Legend X: Don't care.

Note: \* Not available in the H8/36014.

#### • P55/WKP5/ADTRG pin

| Register      | PMR5 | PCR5  |                      |

|---------------|------|-------|----------------------|

| Bit Name      | WKP5 | PCR55 | Pin Function         |

| Setting Value | 0    | 0     | P55 input pin        |

|               |      | 1     | P55 output pin       |

|               | 1    | Х     | WKP5/ADTRG input pin |

Legend X: Don't care.

# 9.4.3 Pin Functions

The correspondence between the register specification and the port functions is shown below.

• P76/TMOV pin

| Register      | TCSRV                             | PCR7  |                 |

|---------------|-----------------------------------|-------|-----------------|

| Bit Name      | OS3 to OS0                        | PCR76 | Pin Function    |

| Setting Value | 0000                              | 0     | P76 input pin   |

|               |                                   | 1     | P76 output pin  |

|               | Other than<br>the above<br>values | Х     | TMOV output pin |

Legend X: Don't care.

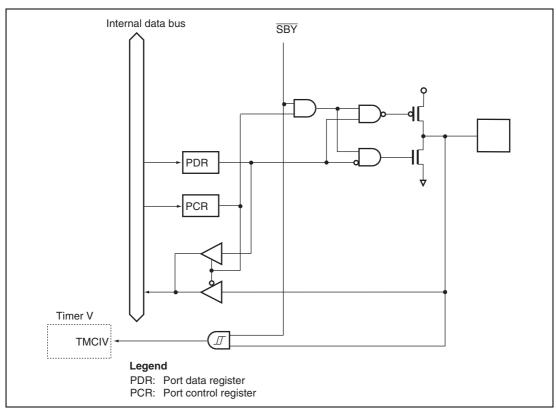

### • P75/TMCIV pin

| Register        | PCR7  |                            |

|-----------------|-------|----------------------------|

| Bit Name        | PCR75 | Pin Function               |

| Setting Value 0 |       | P75 input/TMCIV input pin  |

|                 | 1     | P75 output/TMCIV input pin |

#### • P74/TMRIV pin

| Register      | PCR7  |                            |

|---------------|-------|----------------------------|

| Bit Name      | PCR74 | Pin Function               |

| Setting Value | 0     | P74 input/TMRIV input pin  |

|               | 1     | P74 output/TMRIV input pin |

#### • P73 pin

| Register        | PCR7  |                |

|-----------------|-------|----------------|

| Bit Name        | PCR73 | Pin Function   |

| Setting Value 0 |       | P73 input pin  |

|                 | 1     | P73 output pin |

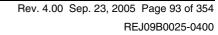

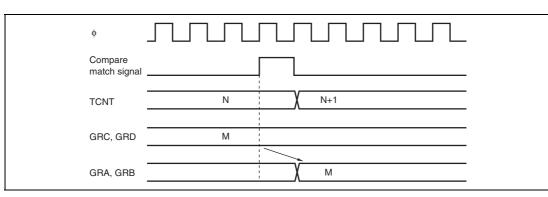

# 11.5.5 Buffer Operation Timing

Figures 11.19 and 11.20 show the buffer operation timing.

#### 11.5.6 Timing of IMFA to IMFD Flag Setting at Compare Match

If a general register (GRA, GRB, GRC, or GRD) is used as an output compare register, the corresponding IMFA, IMFB, IMFC, or IMFD flag is set to 1 when TCNT matches the general register.

The compare match signal is generated in the last state in which the values match (when TCNT is updated from the matching count to the next count). Therefore, when TCNT matches a general register, the compare match signal is generated only after the next TCNT clock pulse is input.

RENESAS

### 13.3.9 SCI3\_3 Module Control Register (SMCR)

SMCR controls the SCI3\_3 and module standby function.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                  |

|--------|----------|------------------|-----|----------------------------------------------------------------------------------------------|

| 7 to 4 |          | All 1            | _   | Reserved                                                                                     |

|        |          |                  |     | These bits are always read as 1.                                                             |

| 3, 2   | _        | All 1            |     | Reserved                                                                                     |

|        |          |                  |     | These bits are always read as 1. When the emulator is used, these bits must be cleared to 0. |

| 1      | TXD_3    | 0                | R/W | TXD_3 Output Select                                                                          |

|        |          |                  |     | Selects the function of the P57/TXD_3 pin.                                                   |

|        |          |                  |     | 0: General I/O port                                                                          |

|        |          |                  |     | 1: TXD_3 output pin                                                                          |

| 0      | MSTS3_3  | 0                | R/W | SCI3_3 Module Standby                                                                        |

|        |          |                  |     | When this bit is set to 1, the SCI3_3 enters the standby state.                              |

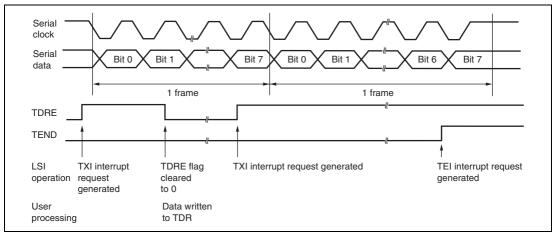

Figure 13.10 Example of SCI3 Transmission in Clocked Synchronous Mode

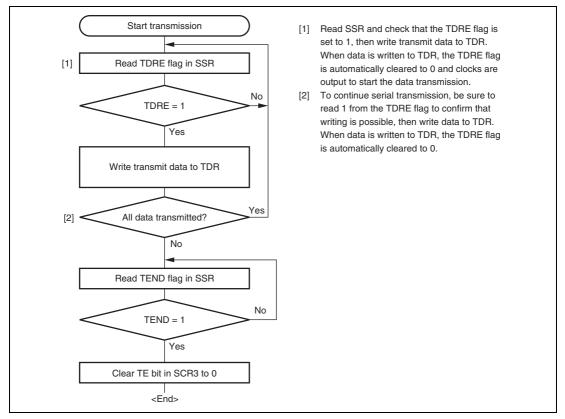

Figure 13.11 Sample Serial Transmission Flowchart (Clocked Synchronous Mode)

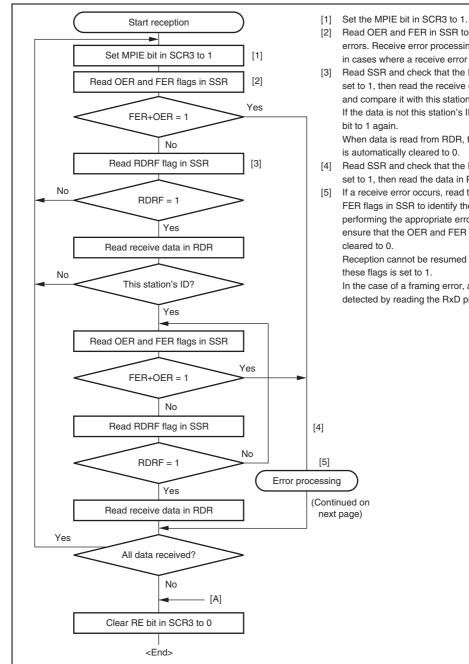

[2] Read OER and FER in SSR to check for errors. Receive error processing is performed in cases where a receive error occurs.

[3] Read SSR and check that the RDRF flag is set to 1, then read the receive data in RDR and compare it with this station's ID. If the data is not this station's ID, set the MPIE

When data is read from RDR, the RDRF flag is automatically cleared to 0.

[4] Read SSR and check that the RDRF flag is set to 1, then read the data in RDR.

[5] If a receive error occurs, read the OER and FER flags in SSR to identify the error. After performing the appropriate error processing, ensure that the OER and FER flags are all

Reception cannot be resumed if either of

In the case of a framing error, a break can be detected by reading the RxD pin value.

#### Figure 13.17 Sample Multiprocessor Serial Reception Flowchart (1)

RENESAS

# 14.5 A/D Conversion Accuracy Definitions

This LSI's A/D conversion accuracy definitions are given below.

Resolution

The number of A/D converter digital output codes

• Quantization error

The deviation inherent in the A/D converter, given by 1/2 LSB (see figure 14.4).

Offset error

The deviation of the analog input voltage value from the ideal A/D conversion characteristic when the digital output changes from the minimum voltage value 00000000000 to 0000000001 (see figure 14.5).

• Full-scale error

The deviation of the analog input voltage value from the ideal A/D conversion characteristic when the digital output changes from 1111111110 to 111111111 (see figure 14.5).

• Nonlinearity error

The error with respect to the ideal A/D conversion characteristics between zero voltage and full-scale voltage. Does not include offset error, full-scale error, or quantization error.

• Absolute accuracy

The deviation between the digital value and the analog input value. Includes offset error, full-scale error, quantization error, and nonlinearity error.

# 15.3.2 Low-Voltage Detection Circuit

# (1) LVDR (Reset by Low Voltage Detect) Circuit

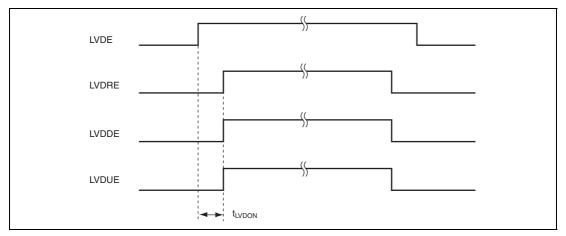

Figure 15.3 shows the timing of the LVDR function. The LVDR enters the module-standby state after a power-on reset is canceled. To operate the LVDR, set the LVDE bit in LVDCR to 1, wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc., then set the LVDRE bit in LVDCR to 1. After that, the output settings of ports must be made. To cancel the low-voltage detection circuit, first the LVDRE bit should be cleared to 0 and then the LVDE bit should be cleared to 0. The LVDE and LVDRE bits must not be cleared to 0 simultaneously because incorrect operation may occur.

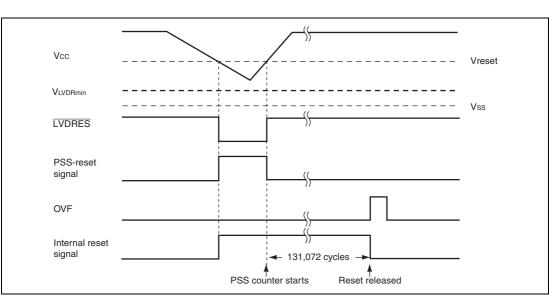

When the power-supply voltage falls below the Vreset voltage (typ. = 2.3 V or 3.6 V), the LVDR clears the  $\overline{LVDRES}$  signal to 0, and resets the prescaler S. The low-voltage detection reset state remains in place until a power-on reset is generated. When the power-supply voltage rises above the Vreset voltage again, the prescaler S starts counting. It counts 131,072 clock ( $\phi$ ) cycles, and then releases the internal reset signal. In this case, the LVDE, LVDSEL, and LVDRE bits in LVDCR are not initialized.

Note that if the power supply voltage (Vcc) falls below  $V_{LVDRmin} = 1.0$  V and then rises from that point, the low-voltage detection reset may not occur.

If the power supply voltage (Vcc) falls below Vpor = 100 mV, a power-on reset occurs.

Figure 15.3 Operational Timing of LVDR Circuit

# (3) Procedures for Clearing Settings when Using LVDR and LVDI

To operate or release the low-voltage detection circuit normally, follow the procedure described below. Figure 15.5 shows the timing for the operation and release of the low-voltage detection circuit.

- 1. To operate the low-voltage detection circuit, set the LVDE bit in LVDCR to 1.

- 2. Wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc. Then, clear the LVDDF and LVDUF bits in LVDSR to 0 and set the LVDRE, LVDDE, and LVDUE bits in LVDCR to 1, as required.

- 3. To release the low-voltage detection circuit, start by clearing all of the LVDRE, LVDDE, and LVDUE bits to 0. Then clear the LVDE bit to 0. The LVDE bit must not be cleared to 0 at the same timing as the LVDRE, LVDDE, and LVDUE bits because incorrect operation may occur.

Figure 15.5 Timing for Operation/Release of Low-Voltage Detection Circuit

#### Appendix

| Instruction | Mnemonic          | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Byte Data<br>Access<br>L | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|-------------------|---------------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| BTST        | BTST #xx:3, Rd    | 1                         |                           |                         |                          |                          |                            |

|             | BTST #xx:3, @ERd  | 2                         |                           |                         | 1                        |                          |                            |

|             | BTST #xx:3, @aa:8 | 2                         |                           |                         | 1                        |                          |                            |

|             | BTST Rn, Rd       | 1                         |                           |                         |                          |                          |                            |

|             | BTST Rn, @ERd     | 2                         |                           |                         | 1                        |                          |                            |

|             | BTST Rn, @aa:8    | 2                         |                           |                         | 1                        |                          |                            |

| BXOR        | BXOR #xx:3, Rd    | 1                         |                           |                         |                          |                          |                            |

|             | BXOR #xx:3, @ERd  | 2                         |                           |                         | 1                        |                          |                            |

|             | BXOR #xx:3, @aa:8 | 2                         |                           |                         | 1                        |                          |                            |

| CMP         | CMP.B #xx:8, Rd   | 1                         |                           |                         |                          |                          |                            |

|             | CMP.B Rs, Rd      | 1                         |                           |                         |                          |                          |                            |

|             | CMP.W #xx:16, Rd  | 2                         |                           |                         |                          |                          |                            |

|             | CMP.W Rs, Rd      | 1                         |                           |                         |                          |                          |                            |

|             | CMP.L #xx:32, ERd | 3                         |                           |                         |                          |                          |                            |

|             | CMP.L ERs, ERd    | 1                         |                           |                         |                          |                          |                            |

| DAA         | DAA Rd            | 1                         |                           |                         |                          |                          |                            |

| DAS         | DAS Rd            | 1                         |                           |                         |                          |                          |                            |

| DEC         | DEC.B Rd          | 1                         |                           |                         |                          |                          |                            |

|             | DEC.W #1/2, Rd    | 1                         |                           |                         |                          |                          |                            |

|             | DEC.L #1/2, ERd   | 1                         |                           |                         |                          |                          |                            |

| DUVXS       | DIVXS.B Rs, Rd    | 2                         |                           |                         |                          |                          | 12                         |

|             | DIVXS.W Rs, ERd   | 2                         |                           |                         |                          |                          | 20                         |

| DIVXU       | DIVXU.B Rs, Rd    | 1                         |                           |                         |                          |                          | 12                         |

|             | DIVXU.W Rs, ERd   | 1                         |                           |                         |                          |                          | 20                         |

| EEPMOV      | EEPMOV.B          | 2                         |                           |                         | 2n+2*1                   |                          |                            |

|             | EEPMOV.W          | 2                         |                           |                         | 2n+2*1                   |                          |                            |

| EXTS        | EXTS.W Rd         | 1                         |                           |                         |                          |                          |                            |

|             | EXTS.L ERd        | 1                         |                           |                         |                          |                          |                            |

| EXTU        | EXTU.W Rd         | 1                         |                           |                         |                          |                          |                            |

|             | EXTU.L ERd        | 1                         |                           |                         |                          |                          |                            |

|     |                        | Instruction<br>Fetch | Addr. Read |   | Byte Data<br>Access | Word Data<br>Access | Internal<br>Operation |

|-----|------------------------|----------------------|------------|---|---------------------|---------------------|-----------------------|

|     | Mnemonic               | I                    | J          | к | L                   | Μ                   | N                     |

| INC | INC.B Rd               | 1                    |            |   |                     |                     |                       |

|     | INC.W #1/2, Rd         | 1                    |            |   |                     |                     |                       |

|     | INC.L #1/2, ERd        | 1                    |            |   |                     |                     |                       |

| JMP | JMP @ERn               | 2                    |            |   |                     |                     |                       |

|     | JMP @aa:24             | 2                    |            |   |                     |                     | 2                     |

|     | JMP @@aa:8             | 2                    | 1          |   |                     |                     | 2                     |

| JSR | JSR @ERn               | 2                    |            | 1 |                     |                     |                       |

|     | JSR @aa:24             | 2                    |            | 1 |                     |                     | 2                     |

|     | JSR @@aa:8             | 2                    | 1          | 1 |                     |                     |                       |

| LDC | LDC #xx:8, CCR         | 1                    |            |   |                     |                     |                       |

|     | LDC Rs, CCR            | 1                    |            |   |                     |                     |                       |

|     | LDC@ERs, CCR           | 2                    |            |   |                     | 1                   |                       |

|     | LDC@(d:16, ERs), CCR   | 3                    |            |   |                     | 1                   |                       |

|     | LDC@(d:24,ERs), CCR    | 5                    |            |   |                     | 1                   |                       |

|     | LDC@ERs+, CCR          | 2                    |            |   |                     | 1                   | 2                     |

|     | LDC@aa:16, CCR         | 3                    |            |   |                     | 1                   |                       |

|     | LDC@aa:24, CCR         | 4                    |            |   |                     | 1                   |                       |

| MOV | MOV.B #xx:8, Rd        | 1                    |            |   |                     |                     |                       |

|     | MOV.B Rs, Rd           | 1                    |            |   |                     |                     |                       |

|     | MOV.B @ERs, Rd         | 1                    |            |   | 1                   |                     |                       |

|     | MOV.B @(d:16, ERs), Rd | 2                    |            |   | 1                   |                     |                       |

|     | MOV.B @(d:24, ERs), Rd | 4                    |            |   | 1                   |                     |                       |

|     | MOV.B @ERs+, Rd        | 1                    |            |   | 1                   |                     | 2                     |

|     | MOV.B @aa:8, Rd        | 1                    |            |   | 1                   |                     |                       |

|     | MOV.B @aa:16, Rd       | 2                    |            |   | 1                   |                     |                       |

|     | MOV.B @aa:24, Rd       | 3                    |            |   | 1                   |                     |                       |

|     | MOV.B Rs, @Erd         | 1                    |            |   | 1                   |                     |                       |

|     | MOV.B Rs, @(d:16, ERd) | 2                    |            |   | 1                   |                     |                       |

|     | MOV.B Rs, @(d:24, ERd) | 4                    |            |   | 1                   |                     |                       |

|     | MOV.B Rs, @-ERd        | 1                    |            |   | 1                   |                     | 2                     |

|     | MOV.B Rs, @aa:8        | 1                    |            |   | 1                   |                     |                       |

Figure B.15 Port 7 Block Diagram (P75)