Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                          |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | PWM, WDT                                                                     |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LFQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36014fpwv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# 16

# H8/36024Group, H8/36014Group

## Hardware Manual

### Renesas 16-Bit Single-Chip Microcomputer H8 Family/H8/300H Tiny Series

H8/36024F H8/36022F H8/36014F H8/36012F H8/36024 H8/36023 H8/36022 H8/36014 H8/36013 H8/36012 H8/36011

#### H8/36010 Renesas Electronics

www.renesas.com

Rev.4.00 2005.09

HD64F36024, HD64F36024G,

HD64F36022, HD64F36022G,

HD64F36014, HD64F36014G, HD64F36012G,

HD64336024, HD64336024G,

HD64336023, HD64336023G,

HD64336022, HD64336022G,

HD64336014, HD64336014G, HD64336013G,

HD64336012, HD64336012G,

HD64336011, HD64336011G,

HD64336010, HD64336010G

| Figure 5.5 Typical Connection to Ceramic Resonator                    |     |

|-----------------------------------------------------------------------|-----|

| Figure 5.6 Example of External Clock Input                            | 67  |

| Figure 5.7 Example of Incorrect Board Design                          |     |

| Section 6 Power-Down Modes                                            |     |

| Figure 6.1 Mode Transition Diagram                                    | 73  |

|                                                                       |     |

| Section 7 ROM                                                         | -   |

| Figure 7.1 Flash Memory Block Configuration.                          |     |

| Figure 7.2 Programming/Erasing Flowchart Example in User Program Mode |     |

| Figure 7.3 Program/Program-Verify Flowchart                           |     |

| Figure 7.4 Erase/Erase-Verify Flowchart                               | 90  |

| Section 9 I/O Ports                                                   |     |

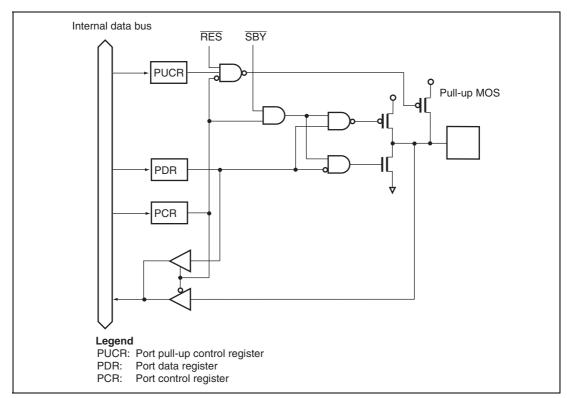

| Figure 9.1 Port 1 Pin Configuration.                                  |     |

| Figure 9.2 Port 2 Pin Configuration.                                  |     |

| Figure 9.3 Port 5 Pin Configuration.                                  |     |

| Figure 9.4 Port 7 Pin Configuration.                                  |     |

| Figure 9.5 Port 8 Pin Configuration.                                  |     |

| Figure 9.6 Port B Pin Configuration                                   |     |

| Section 10 Timer V                                                    |     |

| Figure 10.1 Block Diagram of Timer V                                  | 118 |

| Figure 10.2 Increment Timing with Internal Clock                      |     |

| Figure 10.3 Increment Timing with External Clock                      |     |

| Figure 10.4 OVF Set Timing                                            |     |

| Figure 10.5 CMFA and CMFB Set Timing                                  |     |

| Figure 10.6 TMOV Output Timing                                        |     |

| Figure 10.7 Clear Timing by Compare Match                             |     |

| Figure 10.8 Clear Timing by TMRIV Input                               |     |

| Figure 10.9 Pulse Output Example                                      |     |

| Figure 10.10 Example of Pulse Output Synchronized to TRGV Input       |     |

| Figure 10.11 Contention between TCNTV Write and Clear                 |     |

| Figure 10.12 Contention between TCORA Write and Compare Match         |     |

| Figure 10.13 Internal Clock Switching and TCNTV Operation             |     |

|                                                                       |     |

| Section 11 Timer W                                                    | 127 |

| Figure 11.1 Timer W Block Diagram                                     |     |

| Figure 11.2 Free-Running Counter Operation                            |     |

| Figure 11.3 Periodic Counter Operation                                |     |

| Figure 11.4 0 and 1 Output Example ( $TOA = 0$ , $TOB = 1$ )          |     |

| Figure 11.5 Toggle Output Example (TOA = 0, TOB = 1)                  |     |

| Figure 11.6 Toggle Output Example (TOA = 0, TOB = 1)                  | 150 |

Rev. 4.00 Sep. 23, 2005 Page xviii of xxvi

|                                                                                                                                                   | Input Capture Operating Example                                                                                                                                                                                                                                                                                                                                                                                                                                      | 151                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Figure 11.8                                                                                                                                       | Buffer Operation Example (Input Capture)                                                                                                                                                                                                                                                                                                                                                                                                                             | 152                                                                       |

| Figure 11.9                                                                                                                                       | PWM Mode Example (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 153                                                                       |

| Figure 11.10                                                                                                                                      | PWM Mode Example (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

| Figure 11.11                                                                                                                                      | Buffer Operation Example (Output Compare)                                                                                                                                                                                                                                                                                                                                                                                                                            | 155                                                                       |

| Figure 11.12                                                                                                                                      | PWM Mode Example                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

|                                                                                                                                                   | (TOB, TOC, and TOD = 0: initial output values are set to 0)                                                                                                                                                                                                                                                                                                                                                                                                          | 156                                                                       |

| Figure 11.13                                                                                                                                      | PWM Mode Example                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

|                                                                                                                                                   | (TOB, TOC, and TOD = 1: initial output values are set to 1)                                                                                                                                                                                                                                                                                                                                                                                                          | 157                                                                       |

| Figure 11.14                                                                                                                                      | Count Timing for Internal Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                               | 158                                                                       |

| Figure 11.15                                                                                                                                      | Count Timing for External Clock Source                                                                                                                                                                                                                                                                                                                                                                                                                               | 158                                                                       |

| Figure 11.16                                                                                                                                      | Output Compare Output Timing                                                                                                                                                                                                                                                                                                                                                                                                                                         | 159                                                                       |

| Figure 11.17                                                                                                                                      | Input Capture Input Signal Timing                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |

| Figure 11.18                                                                                                                                      | Timing of Counter Clearing by Compare Match                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| Figure 11.19                                                                                                                                      | Buffer Operation Timing (Compare Match)                                                                                                                                                                                                                                                                                                                                                                                                                              | 161                                                                       |

| Figure 11.20                                                                                                                                      | Buffer Operation Timing (Input Capture)                                                                                                                                                                                                                                                                                                                                                                                                                              | 161                                                                       |

| Figure 11.21                                                                                                                                      | Timing of IMFA to IMFD Flag Setting at Compare Match                                                                                                                                                                                                                                                                                                                                                                                                                 | 162                                                                       |

| Figure 11.22                                                                                                                                      | Timing of IMFA to IMFD Flag Setting at Input Capture                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

| Figure 11.23                                                                                                                                      | Timing of Status Flag Clearing by CPU                                                                                                                                                                                                                                                                                                                                                                                                                                | 163                                                                       |

| Figure 11.24                                                                                                                                      | Contention between TCNT Write and Clear                                                                                                                                                                                                                                                                                                                                                                                                                              | 164                                                                       |

| Figure 11.25                                                                                                                                      | Internal Clock Switching and TCNT Operation                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| Figure 11.26                                                                                                                                      | When Compare Match and Bit Manipulation Instruction to TCRW Occur a                                                                                                                                                                                                                                                                                                                                                                                                  | t the                                                                     |

|                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t the                                                                     |

|                                                                                                                                                   | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| Section 12                                                                                                                                        | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

|                                                                                                                                                   | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165                                                                       |

| Figure 12.1                                                                                                                                       | Same Timing<br>Watchdog Timer<br>Block Diagram of Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                     | 165                                                                       |

| Figure 12.1<br>Figure 12.2                                                                                                                        | Same Timing<br>Watchdog Timer<br>Block Diagram of Watchdog Timer<br>Watchdog Timer Operation Example                                                                                                                                                                                                                                                                                                                                                                 | 165                                                                       |

| Figure 12.1<br>Figure 12.2<br>Section 13                                                                                                          | Same Timing<br>Watchdog Timer<br>Block Diagram of Watchdog Timer<br>Watchdog Timer Operation Example<br>Serial Communication Interface 3 (SCI3)                                                                                                                                                                                                                                                                                                                      | 165<br>167<br>171                                                         |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1                                                                                           | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176                                                  |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2                                                                            | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176                                                  |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2                                                                            | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176<br>192                                           |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3                                                             | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176<br>192<br>192                                    |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3                                                             | Same Timing<br><b>Watchdog Timer</b><br>Block Diagram of Watchdog Timer<br>Watchdog Timer Operation Example<br><b>Serial Communication Interface 3 (SCI3)</b><br>Block Diagram of SCI3<br>Data Format in Asynchronous Communication<br>Relationship between Output Clock and Transfer Data Phase<br>(Asynchronous Mode)(Example with 8-Bit Data, Parity, Two Stop Bits)<br>Sample SCI3 Initialization Flowchart                                                      | 165<br>167<br>171<br>176<br>192<br>192                                    |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3                                                             | Same Timing<br><b>Watchdog Timer</b><br>Block Diagram of Watchdog Timer<br>Watchdog Timer Operation Example<br><b>Serial Communication Interface 3 (SCI3)</b><br>Block Diagram of SCI3<br>Data Format in Asynchronous Communication<br>Relationship between Output Clock and Transfer Data Phase<br>(Asynchronous Mode)(Example with 8-Bit Data, Parity, Two Stop Bits)<br>Sample SCI3 Initialization Flowchart<br>Example of SCI3 Transmission in Asynchronous Mode | 165<br>167<br>171<br>176<br>192<br>192<br>193                             |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3<br>Figure 13.4<br>Figure 13.5                               | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176<br>192<br>192<br>193<br>194                      |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3<br>Figure 13.4<br>Figure 13.5                               | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176<br>192<br>192<br>193<br>194                      |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3<br>Figure 13.4<br>Figure 13.5                               | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176<br>192<br>192<br>193<br>194<br>195               |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3<br>Figure 13.4<br>Figure 13.5<br>Figure 13.6<br>Figure 13.7 | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176<br>192<br>192<br>193<br>194<br>195<br>196        |

| Figure 12.1<br>Figure 12.2<br>Section 13<br>Figure 13.1<br>Figure 13.2<br>Figure 13.3<br>Figure 13.4<br>Figure 13.5                               | Same Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 165<br>167<br>171<br>176<br>192<br>192<br>193<br>194<br>195<br>196<br>198 |

#### RENESAS

| Figure 13.9  | Data Format in Clocked Synchronous Communication                           | 200 |

|--------------|----------------------------------------------------------------------------|-----|

| -            | Example of SCI3 Transmission in Clocked Synchronous Mode                   |     |

| Figure 13.11 |                                                                            |     |

| Figure 13.12 |                                                                            |     |

| Figure 13.13 |                                                                            |     |

| Figure 13.14 |                                                                            |     |

| 8            | (Clocked Synchronous Mode)                                                 | 206 |

| Figure 13.15 |                                                                            |     |

| C            | (Transmission of Data H'AA to Receiving Station A)                         | 208 |

| Figure 13.16 |                                                                            |     |

| Figure 13.17 | · ·                                                                        |     |

| Figure 13.17 |                                                                            |     |

| Figure 13.18 | Example of SCI3 Reception Using Multiprocessor Format                      |     |

| •            | (Example with 8-Bit Data, Multiprocessor Bit, One Stop Bit)                | 213 |

| Figure 13.19 | Receive Data Sampling Timing in Asynchronous Mode                          | 216 |

| Section 14   | A/D Converter                                                              |     |

| Figure 14.1  | Block Diagram of A/D Converter                                             | 218 |

| Figure 14.1  | A/D Conversion Timing                                                      |     |

| Figure 14.3  | External Trigger Input Timing                                              |     |

| Figure 14.4  | A/D Conversion Accuracy Definitions (1)                                    |     |

| Figure 14.5  | A/D Conversion Accuracy Definitions (2)                                    |     |

| Figure 14.6  | Analog Input Circuit Example                                               |     |

| -            |                                                                            |     |

|              | Power-On Reset and Low-Voltage Detection Circuits (Optional)               | 220 |

| Figure 15.1  | Block Diagram of Power-On Reset Circuit and Low-Voltage Detection Circuit. |     |

| Figure 15.2  | Operational Timing of Power-On Reset Circuit                               |     |

| Figure 15.3  | Operational Timing of LVDR Circuit                                         |     |

| Figure 15.4  | Operational Timing of LVDI Circuit                                         |     |

| Figure 15.5  | Timing for Operation/Release of Low-Voltage Detection Circuit              | 236 |

| Section 16   | Power Supply Circuit                                                       |     |

| Figure 16.1  | Power Supply Connection when Internal Step-Down Circuit is Used            | 237 |

| Figure 16.2  | Power Supply Connection when Internal Step-Down Circuit is Not Used        | 238 |

| Section 18   | Electrical Characteristics                                                 |     |

| Figure 18.1  | System Clock Input Timing                                                  | 281 |

| Figure 18.2  | RES Low Width Timing                                                       |     |

| Figure 18.3  | Input Timing                                                               |     |

| Figure 18.4  | SCK3 Input Clock Timing                                                    |     |

| Figure 18.5  | SCI3 Input/Output Timing in Clocked Synchronous Mode                       |     |

| Figure 18.6  | Output Load Circuit                                                        |     |

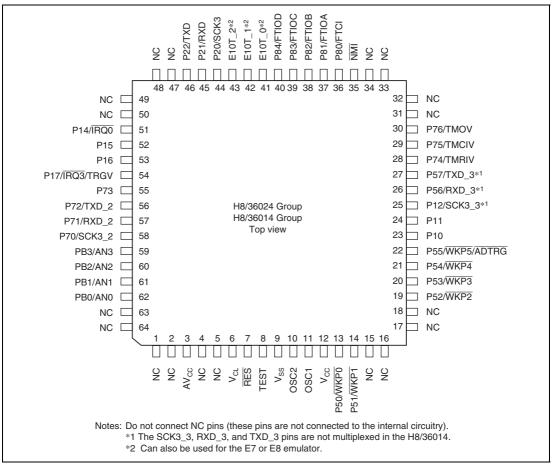

#### **1.3** Pin Arrangement

Figure 1.2 Pin Arrangement (FP-64E)

| Instruction | n Size*       | Function                                                                                                                                                                                                                                                                                   |

|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BXOR        | В             | $C \oplus (\langle bit-No. \rangle of \langle EAd \rangle) \rightarrow C$<br>XORs the carry flag with a specified bit in a general register or memory<br>operand and stores the result in the carry flag.                                                                                  |

| BIXOR       | В             | $C \oplus \neg$ ( <bit-no.> of <ead>) <math>\rightarrow C</math><br/>XORs the carry flag with the inverse of a specified bit in a general<br/>register or memory operand and stores the result in the carry flag.<br/>The bit number is specified by 3-bit immediate data.</ead></bit-no.> |

| BLD         | В             | (<br>kit-No.> of <ead>) <math display="inline">\rightarrow</math> C Transfers a specified bit in a general register or memory operand to the carry flag.</ead>                                                                                                                             |

| BILD        | В             | ¬ ( <bit-no.> of <ead>) → C<br/>Transfers the inverse of a specified bit in a general register or memory<br/>operand to the carry flag.<br/>The bit number is specified by 3-bit immediate data.</ead></bit-no.>                                                                           |

| BST         | В             | $C \rightarrow$ ( <bit-no.> of <ead>)<br/>Transfers the carry flag value to a specified bit in a general register or<br/>memory operand.</ead></bit-no.>                                                                                                                                   |

| BIST        | В             | $\neg$ C $\rightarrow$ ( <bit-no.> of <ead>)<br/>Transfers the inverse of the carry flag value to a specified bit in a<br/>general register or memory operand.<br/>The bit number is specified by 3-bit immediate data.</ead></bit-no.>                                                    |

| Note: *     | Refers to the | operand size.                                                                                                                                                                                                                                                                              |

Table 2.6

Bit Manipulation Instructions (2)

Note: \* Refers to the operand size.

B: Byte

#### 3.2.2 Interrupt Edge Select Register 2 (IEGR2)

IEGR2 selects the direction of an edge that generates interrupt requests of the pins  $\overline{\text{ADTRG}}$  and  $\overline{\text{WKP5}}$  to  $\overline{\text{WKP0}}$ .

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                       |

|------|----------|------------------|-----|-----------------------------------------------------------------------------------|

| 7, 6 |          | All 1            |     | Reserved                                                                          |

|      |          |                  |     | These bits are always read as 1.                                                  |

| 5    | WPEG5    | 0                | R/W | WKP5 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP5}$ ( $\overline{ADTRG}$ ) pin input is detected |

|      |          |                  |     | 1: Rising edge of $\overline{WKP5}$ ( $\overline{ADTRG}$ ) pin input is detected  |

| 4    | WPEG4    | 0                | R/W | WKP4 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP4}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of $\overline{WKP4}$ pin input is detected                         |

| 3    | WPEG3    | 0                | R/W | WKP3 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP3}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP3 pin input is detected                                      |

| 2    | WPEG2    | 0                | R/W | WKP2 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP2}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP2 pin input is detected                                      |

| 1    | WPEG1    | 0                | R/W | WKP1Edge Select                                                                   |

|      |          |                  |     | 0: Falling edge of $\overline{WKP1}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of $\overline{WKP1}$ pin input is detected                         |

| 0    | WPEG0    | 0                | R/W | WKP0 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP0}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP0 pin input is detected                                      |

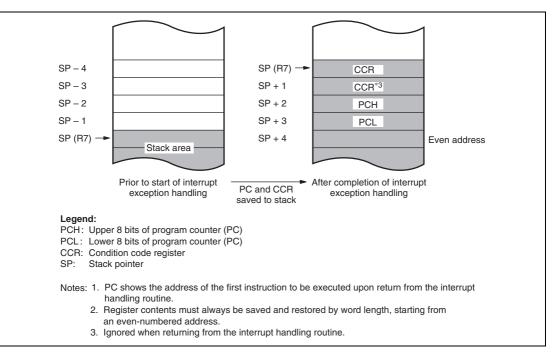

#### Figure 3.2 Stack Status after Exception Handling

#### 3.4.4 Interrupt Response Time

Table 3.2 shows the number of wait states after an interrupt request flag is set until the first instruction of the interrupt handling-routine is executed.

#### Table 3.2Interrupt Wait States

| Item                                                  | States  | Total    |

|-------------------------------------------------------|---------|----------|

| Waiting time for completion of executing instruction* | 1 to 23 | 15 to 37 |

| Saving of PC and CCR to stack                         | 4       |          |

| Vector fetch                                          | 2       |          |

| Instruction fetch                                     | 4       |          |

| Internal processing                                   | 4       |          |

| Netse W Net in shading EEDMOV/ in struction           |         |          |

Note: \* Not including EEPMOV instruction.

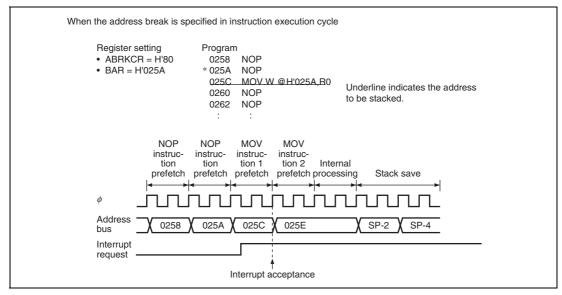

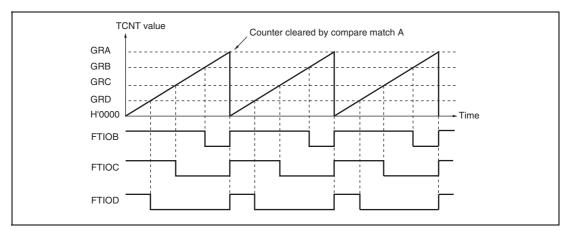

| When the address break is                                                       | s specified in the data read cycle                                                                                                       |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Register setting<br>• ABRKCR = H'A0<br>• BAR = H'025A                           | Program<br>0258 NOP<br>025A NOP<br>* 025C MOV.W @H'025A,R0<br>0260 NOP Underline indicates the address<br>0262 NOP to be stacked.<br>: : |

| MOV<br>instruc-<br>tion 1<br>prefetch<br>Address<br>bus<br>Interrupt<br>request | MOV NOP MOV NOP Next<br>instruction 2 tion tion tion tion prefetch prefetch execution prefetch prefetch processing save                  |

Figure 4.2 Address Break Interrupt Operation Example (2)

RENESAS

#### 7.5 Program/Erase Protection

There are three kinds of flash memory program/erase protection; hardware protection, software protection, and error protection.

#### 7.5.1 Hardware Protection

Hardware protection refers to a state in which programming/erasing of flash memory is forcibly disabled or aborted because of a transition to reset, subsleep mode or standby mode. Flash memory control register 1 (FLMCR1), flash memory control register 2 (FLMCR2), and erase block register 1 (EBR1) are initialized. In a reset via the  $\overline{\text{RES}}$  pin, the reset state is not entered unless the  $\overline{\text{RES}}$  pin is held low until oscillation stabilizes after powering on. In the case of a reset during operation, hold the  $\overline{\text{RES}}$  pin low for the  $\overline{\text{RES}}$  pulse width specified in the AC Characteristics section.

#### 7.5.2 Software Protection

Software protection can be implemented against programming/erasing of all flash memory blocks by clearing the SWE bit in FLMCR1. When software protection is in effect, setting the P or E bit in FLMCR1 does not cause a transition to program mode or erase mode. By setting the erase block register 1 (EBR1), erase protection can be set for individual blocks. When EBR1 is set to H'00, erase protection is set for all blocks.

#### 7.5.3 Error Protection

In error protection, an error is detected when CPU runaway occurs during flash memory programming/erasing, or operation is not performed in accordance with the program/erase algorithm, and the program/erase operation is aborted. Aborting the program/erase operation prevents damage to the flash memory due to overprogramming or overerasing.

When the following errors are detected during programming/erasing of flash memory, the FLER bit in FLMCR2 is set to 1, and the error protection state is entered.

- When the flash memory of the relevant address area is read during programming/erasing (including vector read and instruction fetch)

- Immediately after exception handling excluding a reset during programming/erasing

- When a SLEEP instruction is executed during programming/erasing

#### 9.4.3 Pin Functions

The correspondence between the register specification and the port functions is shown below.

• P76/TMOV pin

| Register      | TCSRV                             | PCR7  |                 |

|---------------|-----------------------------------|-------|-----------------|

| Bit Name      | OS3 to OS0                        | PCR76 | Pin Function    |

| Setting Value | 0000                              | 0     | P76 input pin   |

|               |                                   | 1     | P76 output pin  |

|               | Other than<br>the above<br>values | Х     | TMOV output pin |

Legend X: Don't care.

#### • P75/TMCIV pin

| Register      | PCR7  |                            |

|---------------|-------|----------------------------|

| Bit Name      | PCR75 | Pin Function               |

| Setting Value | 0     | P75 input/TMCIV input pin  |

|               | 1     | P75 output/TMCIV input pin |

#### • P74/TMRIV pin

| Register      | PCR7  |                            |

|---------------|-------|----------------------------|

| Bit Name      | PCR74 | Pin Function               |

| Setting Value | 0     | P74 input/TMRIV input pin  |

|               | 1     | P74 output/TMRIV input pin |

#### • P73 pin

| Register      | PCR7  |                |

|---------------|-------|----------------|

| Bit Name      | PCR73 | Pin Function   |

| Setting Value | 0     | P73 input pin  |

|               | 1     | P73 output pin |

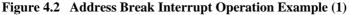

Figure 10.8 Clear Timing by TMRIV Input

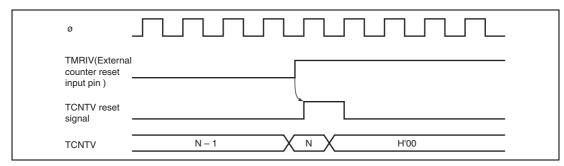

#### 11.4.2 PWM Operation

In PWM mode, PWM waveforms are generated by using GRA as the period register and GRB, GRC, and GRD as duty registers. PWM waveforms are output from the FTIOB, FTIOC, and FTIOD pins. Up to three-phase PWM waveforms can be output. In PWM mode, a general register functions as an output compare register automatically. The output level of each pin depends on the corresponding timer output level set bit (TOB, TOC, and TOD) in TCRW. When TOB is 1, the FTIOB output goes to 1 at compare match A and to 0 at compare match B. When TOB is 0, the FTIOB output goes to 0 at compare match A and to 1 at compare match B. Thus the compare match output level settings in TIOR0 and TIOR1 are ignored for the output pin set to PWM mode. If the same value is set in the cycle register and the duty register, the output does not change when a compare match occurs.

Figure 11.9 shows an example of operation in PWM mode. The output signals go to 1 and TCNT is cleared at compare match A, and the output signals go to 0 at compare match B, C, and D (TOB, TOC, and TOD = 1: initial output values are set to 1).

Figure 11.9 PWM Mode Example (1)

#### 13.6 Multiprocessor Communication Function

Use of the multiprocessor communication function enables data transfer between a number of processors sharing communication lines by asynchronous serial communication using the multiprocessor format, in which a multiprocessor bit is added to the transfer data. When multiprocessor communication is performed, each receiving station is addressed by a unique ID code. The serial communication cycle consists of two component cycles; an ID transmission cycle that specifies the receiving station, and a data transmission cycle. The multiprocessor bit is used to differentiate between the ID transmission cycle and the data transmission cycle. If the multiprocessor bit is 1, the cycle is an ID transmission cycle; if the multiprocessor bit is 0, the cycle is a data transmission cycle. Figure 13.15 shows an example of inter-processor communication using the multiprocessor format. The transmitting station first sends the ID code of the receiving station with which it wants to perform serial communication as data with a 1 multiprocessor bit added. When data with a 1 multiprocessor bit is received, the receiving station compares that data with its own ID. The station whose ID matches then receives the data sent next. Stations whose IDs do not match continue to skip data until data with a 1 multiprocessor bit is again received.

The SCI3 uses the MPIE bit in SCR3 to implement this function. When the MPIE bit is set to 1, transfer of receive data from RSR to RDR, error flag detection, and setting the SSR status flags, RDRF, FER, and OER, to 1, are inhibited until data with a 1 multiprocessor bit is received. On reception of a receive character with a 1 multiprocessor bit, the MPBR bit in SSR is set to 1 and the MPIE bit is automatically cleared, thus normal reception is resumed. If the RIE bit in SCR3 is set to 1 at this time, an RXI interrupt is generated.

When the multiprocessor format is selected, the parity bit setting is rendered invalid. All other bit settings are the same as those in normal asynchronous mode. The clock used for multiprocessor communication is the same as that in normal asynchronous mode.

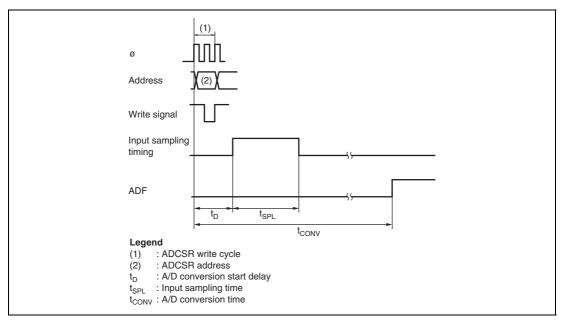

#### 14.4.3 Input Sampling and A/D Conversion Time

The A/D converter has a built-in sample-and-hold circuit. The A/D converter samples the analog input when the A/D conversion start delay time  $(t_D)$  has passed after the ADST bit is set to 1, then starts conversion. Figure 14.2 shows the A/D conversion timing. Table 14.3 shows the A/D conversion time.

As indicated in figure 14.2, the A/D conversion time includes  $t_D$  and the input sampling time. The length of  $t_D$  varies depending on the timing of the write access to ADCSR. The total conversion time therefore varies within the ranges indicated in table 14.3.

In scan mode, the values given in table 14.3 apply to the first conversion time. In the second and subsequent conversions, the conversion time is 128 states (fixed) when CKS = 0 and 66 states (fixed) when CKS = 1.

Figure 14.2 A/D Conversion Timing

RENESAS

#### Table 18.4 Serial Interface (SCI3) Timing

$V_{cc} = 3.0 \text{ V}$  to 5.5 V,  $V_{ss} = 0.0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to +75°C, unless otherwise specified.

| Item                                                 |                             | Symbol            | Applicable<br>Pins          |                           | Values           |     |     |                   | Reference   |

|------------------------------------------------------|-----------------------------|-------------------|-----------------------------|---------------------------|------------------|-----|-----|-------------------|-------------|

|                                                      |                             |                   |                             | Test Condition            | Min              | Тур | Max | Unit              | Figure      |

| Input<br>clock                                       | Asynchro-<br>nous           | t <sub>Scyc</sub> | SCK3,<br>SCK3_2,            |                           | 4                | _   | _   | t <sub>cyc</sub>  | Figure 18.4 |

| cycle                                                | Clocked<br>synchro-<br>nous | SCK3_3* 6 —       | _                           | —                         | t <sub>cyc</sub> | _   |     |                   |             |

| Input clock pulse width                              |                             | t <sub>sскw</sub> | SCK3,<br>SCK3_2,<br>SCK3_3* |                           | 0.4              | _   | 0.6 | t <sub>Scyc</sub> | _           |

| Transmit data delay<br>time (clocked<br>synchronous) |                             | t <sub>TXD</sub>  | TXD,<br>TXD_2,<br>TXD_3*    | $V_{cc}$ = 4.0 V to 5.5 V | —                | —   | 1   | t <sub>cyc</sub>  | Figure 18.5 |

|                                                      |                             |                   |                             |                           | _                | _   | 1   | t <sub>cyc</sub>  |             |

| Receive data setup<br>time (clocked<br>synchronous)  |                             | t <sub>RXS</sub>  | RXD,<br>RXD_2,<br>RXD_3*    | $V_{cc}$ = 4.0 V to 5.5 V | 50.0             | _   | _   | ns                |             |

|                                                      |                             |                   |                             |                           | 100.0            | _   | _   | ns                | _           |

|                                                      | e data hold                 | t <sub>RXH</sub>  | RXD,                        | $V_{cc}$ = 4.0 V to 5.5 V | 50.0             |     | _   | ns                |             |

| time (clocked<br>synchronous)                        |                             |                   | RXD_2,<br>RXD_3*            |                           | 100.0            | _   | _   | ns                | _           |

Note: \* The SCK3\_3, RXD\_3, and TXD\_3 pins are not available in the H8/36014.

#### 18.2.6 Flash Memory Characteristics

#### Table 18.7 Flash Memory Characteristics

$V_{cc}$  = 3.0 V to 5.5 V,  $V_{ss}$  = 0.0 V,  $T_a$  = -20°C to +75°C, unless otherwise specified.

|                                                                                            |                                              |                | Test                       |      |       |           |             |

|--------------------------------------------------------------------------------------------|----------------------------------------------|----------------|----------------------------|------|-------|-----------|-------------|

| Item                                                                                       |                                              | Symbol         | Condition                  | Min  | Тур   | Max       | Unit        |

| Programming time (per 128 bytes)*1*2*4                                                     |                                              | t <sub>P</sub> |                            | _    | 7     | 200       | ms          |

| Erase time (per block) * <sup>1</sup> * <sup>3</sup> * <sup>6</sup><br>Reprogramming count |                                              | t <sub>e</sub> |                            | _    | 100   | 1200<br>— | ms<br>Times |

|                                                                                            |                                              | $N_{wec}$      |                            | 1000 | 10000 |           |             |

| Programming                                                                                | Wait time after SWE bit setting*1            | x              |                            | 1    | _     | _         | μs          |

|                                                                                            | Wait time after PSU bit setting*1            | у              |                            | 50   | _     | _         | μs          |

|                                                                                            | Wait time after P bit setting                | z1             | $1 \le n \le 6$            | 28   | 30    | 32        | μs          |

|                                                                                            | *1*4                                         | z2             | $7 \le n \le 1000$         | 198  | 200   | 202       | μs          |

|                                                                                            |                                              | z3             | Additional-<br>programming | 8    | 10    | 12        | μs          |

|                                                                                            | Wait time after P bit clear*1                | α              |                            | 5    | —     | _         | μs          |

|                                                                                            | Wait time after PSU bit clear*1              | β              |                            | 5    | —     | —         | μs          |

|                                                                                            | Wait time after PV bit setting*1             | γ              |                            | 4    | —     | —         | μs          |

|                                                                                            | Wait time after<br>dummy write* <sup>1</sup> | ε              |                            | 2    | _     | _         | μs          |

|                                                                                            | Wait time after PV bit clear*1               | η              |                            | 2    | —     | —         | μs          |

|                                                                                            | Wait time after SWE bit clear*1              | θ              |                            | 100  | _     | _         | μs          |

|                                                                                            | Maximum<br>programming count*1*4*5           | Ν              |                            | _    |       | 1000      | Times       |

Figure B.3 Port 1 Block Diagram (P16, P15, P12\*, P10)

Note: \* This pin is available only in the H8/36014.