Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 20MHz                                                                       |

| Connectivity               | SCI                                                                         |

| Peripherals                | PWM, WDT                                                                    |

| Number of I/O              | 30                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | A/D 4x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-LQFP                                                                     |

| Supplier Device Package    | 48-LFQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36014fyv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                               | 3.2.4                                                                                                                                 | Interrupt Flag Register 1 (IRR1)                                                                                                                                                                                                                                                                                                                                   | . 50                                                                                      |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                                                               | 3.2.5                                                                                                                                 | Wakeup Interrupt Flag Register (IWPR)                                                                                                                                                                                                                                                                                                                              | . 51                                                                                      |

| 3.3                                                           | Reset                                                                                                                                 | Exception Handling                                                                                                                                                                                                                                                                                                                                                 | . 52                                                                                      |

| 3.4                                                           | Interr                                                                                                                                | upt Exception Handling                                                                                                                                                                                                                                                                                                                                             | . 53                                                                                      |

|                                                               | 3.4.1                                                                                                                                 | External Interrupts                                                                                                                                                                                                                                                                                                                                                | . 53                                                                                      |

|                                                               | 3.4.2                                                                                                                                 | Internal Interrupts                                                                                                                                                                                                                                                                                                                                                | . 54                                                                                      |

|                                                               | 3.4.3                                                                                                                                 | Interrupt Handling Sequence                                                                                                                                                                                                                                                                                                                                        | . 55                                                                                      |

|                                                               | 3.4.4                                                                                                                                 | Interrupt Response Time                                                                                                                                                                                                                                                                                                                                            | . 56                                                                                      |

| 3.5                                                           | Usage                                                                                                                                 | Notes                                                                                                                                                                                                                                                                                                                                                              | . 58                                                                                      |

|                                                               | 3.5.1                                                                                                                                 | Interrupts after Reset                                                                                                                                                                                                                                                                                                                                             | . 58                                                                                      |

|                                                               | 3.5.2                                                                                                                                 | Notes on Stack Area Use                                                                                                                                                                                                                                                                                                                                            | . 58                                                                                      |

|                                                               | 3.5.3                                                                                                                                 | Notes on Rewriting Port Mode Registers                                                                                                                                                                                                                                                                                                                             | . 58                                                                                      |

| Secti                                                         | on 4                                                                                                                                  | Address Break                                                                                                                                                                                                                                                                                                                                                      | 59                                                                                        |

| 4.1                                                           | Regist                                                                                                                                | ter Descriptions                                                                                                                                                                                                                                                                                                                                                   | . 59                                                                                      |

|                                                               | 4.1.1                                                                                                                                 | Address Break Control Register (ABRKCR)                                                                                                                                                                                                                                                                                                                            | . 60                                                                                      |

|                                                               | 4.1.2                                                                                                                                 | Address Break Status Register (ABRKSR)                                                                                                                                                                                                                                                                                                                             | . 61                                                                                      |

|                                                               | 4.1.3                                                                                                                                 | Break Address Registers (BARH, BARL)                                                                                                                                                                                                                                                                                                                               | . 62                                                                                      |

|                                                               | 4.1.4                                                                                                                                 | Break Data Registers (BDRH, BDRL)                                                                                                                                                                                                                                                                                                                                  | . 62                                                                                      |

| 4.2                                                           | Opera                                                                                                                                 | tion                                                                                                                                                                                                                                                                                                                                                               | . 62                                                                                      |

|                                                               |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                           |

| Secti                                                         | on 5                                                                                                                                  | Clock Pulse Generators                                                                                                                                                                                                                                                                                                                                             | 65                                                                                        |

| Secti<br>5.1                                                  |                                                                                                                                       | Clock Pulse Generatorsn Clock Generator                                                                                                                                                                                                                                                                                                                            |                                                                                           |

|                                                               |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    | . 65                                                                                      |

|                                                               | Syster                                                                                                                                | n Clock Generator                                                                                                                                                                                                                                                                                                                                                  | . 65<br>. 66                                                                              |

|                                                               | Syster<br>5.1.1                                                                                                                       | n Clock Generator<br>Connecting Crystal Resonator                                                                                                                                                                                                                                                                                                                  | . 65<br>. 66<br>. 66                                                                      |

|                                                               | Syster<br>5.1.1<br>5.1.2<br>5.1.3                                                                                                     | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator                                                                                                                                                                                                                                                                                  | . 65<br>. 66<br>. 66<br>. 67                                                              |

| 5.1                                                           | Syster<br>5.1.1<br>5.1.2<br>5.1.3                                                                                                     | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method                                                                                                                                                                                                                                                   | . 65<br>. 66<br>. 66<br>. 67<br>. 67                                                      |

| 5.1                                                           | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1                                                                                  | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method                                                                                                                                                                                                                                                   | . 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67                                              |

| <ul><li>5.1</li><li>5.2</li></ul>                             | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1                                                                                  | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Prescaler S                                                                                                                                                                                                                                    | . 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67                                      |

| <ul><li>5.1</li><li>5.2</li></ul>                             | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage                                                                         | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S                                                                                                                                                                                                                           | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                                      |

| <ul><li>5.1</li><li>5.2</li></ul>                             | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2                                                       | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>ilers<br>Prescaler S<br>Notes<br>Note on Resonators                                                                                                                                                                                            | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68                              |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                 | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6                                               | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Prescaler S<br>Notes<br>Note on Resonators<br>Notes on Board Design                                                                                                                                                                            | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68<br>69                        |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6                                               | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S<br>Notes<br>Notes on Resonators<br>Notes on Board Design<br>Power-Down Modes                                                                                                                                              | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68<br><b>69</b><br>. 69 |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6<br>Regist                                     | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Prescaler S<br>Notes<br>Note on Resonators<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>ter Descriptions                                                                                                              | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                      |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>con 6<br>Regiss<br>6.1.1                           | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Nets<br>Prescaler S<br>Notes<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>System Control Register 1 (SYSCR1)                                                                                                          | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68<br>. 69<br>. 70<br>. 71      |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6<br>Regiss<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4 | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S<br>Notes<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>ter Descriptions<br>System Control Register 1 (SYSCR1)<br>System Control Register 2 (SYSCR2)<br>Module Standby Control Register 1 (MSTCR1) | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                      |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6<br>Regiss<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4 | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S<br>Notes<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>ter Descriptions<br>System Control Register 1 (SYSCR1)<br>System Control Register 2 (SYSCR2)<br>Module Standby Control Register 1 (MSTCR1) | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                      |

# RENESAS

| Table 18.8  | Power-Supply-Voltage Detection Circuit Characteristics |  |

|-------------|--------------------------------------------------------|--|

| Table 18.9  | Power-On Reset Circuit Characteristics                 |  |

| Table 18.10 | DC Characteristics (1)                                 |  |

| Table 18.10 | DC Characteristics (2)                                 |  |

| Table 18.11 | AC Characteristics                                     |  |

| Table 18.12 | Serial Interface (SCI3) Timing                         |  |

| Table 18.13 | A/D Converter Characteristics                          |  |

| Table 18.14 | Watchdog Timer Characteristics                         |  |

| Table 18.15 | Power-Supply-Voltage Detection Circuit Characteristics |  |

| Table 18.16 | Power-On Reset Circuit Characteristics                 |  |

| Appendix    |                                                        |  |

| Table A.1   | Instruction Set                                        |  |

| Table A.2   | Operation Code Map (1)                                 |  |

| Table A.2   | Operation Code Map (2)                                 |  |

| Table A.2   | Operation Code Map (3)                                 |  |

| Table A.3   | Number of Cycles in Each Instruction                   |  |

Table A.4 Table A.5

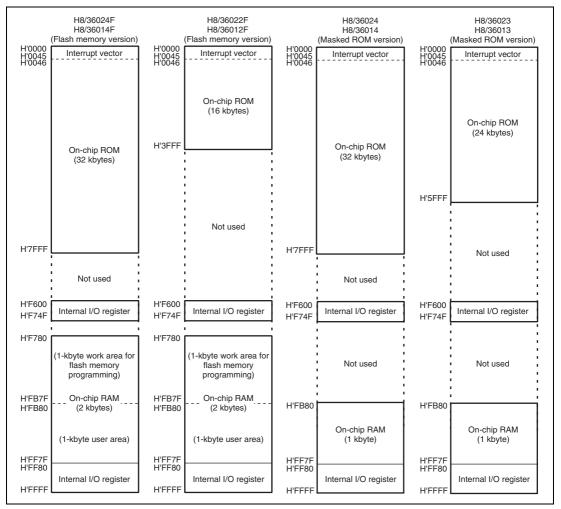

# 2.1 Address Space and Memory Map

The address space of this LSI is 64 kbytes, which includes the program area and the data area. Figures 2.1 show the memory maps.

Figure 2.1 Memory Map (1)

RENESAS

Note: \* Refers to the operand size.

- B: Byte

- W: Word

L: Longword

#### Table 2.5 Shift Instructions

| Instructio     | n Size*       | Function                                                                                  |

|----------------|---------------|-------------------------------------------------------------------------------------------|

| SHAL<br>SHAR   | B/W/L         | Rd (shift) $\rightarrow$ Rd Performs an arithmetic shift on general register contents.    |

| SHLL<br>SHLR   | B/W/L         | Rd (shift) $\rightarrow$ Rd Performs a logical shift on general register contents.        |

| ROTL<br>ROTR   | B/W/L         | Rd (rotate) $\rightarrow$ Rd<br>Rotates general register contents.                        |

| ROTXL<br>ROTXR | B/W/L         | Rd (rotate) $\rightarrow$ Rd<br>Rotates general register contents through the carry flag. |

| Note: *        | Refers to the | operand size.                                                                             |

inote: Refers to the operand size.

B: Byte

W: Word

L: Longword

| Instruction | Size* | Function                                                                                                                                                                                                               |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRAPA       |       | Starts trap-instruction exception handling.                                                                                                                                                                            |

| RTE         | _     | Returns from an exception-handling routine.                                                                                                                                                                            |

| SLEEP       |       | Causes a transition to a power-down state.                                                                                                                                                                             |

| LDC         | B/W   | $(EAs) \rightarrow CCR$<br>Moves the source operand contents to the CCR. The CCR size is one<br>byte, but in transfer from memory, data is read by word access.                                                        |

| STC         | B/W   | $CCR \rightarrow (EAd), EXR \rightarrow (EAd)$<br>Transfers the CCR contents to a destination location. The condition<br>code register size is one byte, but in transfer to memory, data is written<br>by word access. |

| ANDC        | В     | $\label{eq:CCR} CCR \wedge \#IMM \rightarrow CCR, EXR \wedge \#IMM \rightarrow EXR \\ \mbox{Logically ANDs the CCR with immediate data.}$                                                                              |

| ORC         | В     | $\label{eq:CCR} CCR \lor \#IMM \to CCR, EXR \lor \#IMM \to EXR \\ \mbox{Logically ORs the CCR with immediate data.}$                                                                                                   |

| XORC        | В     | CCR $\oplus$ #IMM $\rightarrow$ CCR, EXR $\oplus$ #IMM $\rightarrow$ EXR<br>Logically XORs the CCR with immediate data.                                                                                                |

| NOP         | —     | $PC + 2 \rightarrow PC$<br>Only increments the program counter.                                                                                                                                                        |

|             |       | operand size.                                                                                                                                                                                                          |

| B: Byt      | е     |                                                                                                                                                                                                                        |

#### Table 2.8 **System Control Instructions**

B: Byte

W: Word

| Instruction | Size | Function                                                                                                                                                  |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| EEPMOV.B    | _    | if R4L $\neq$ 0 then<br>Repeat @ER5+ $\rightarrow$ @ER6+,<br>R4L-1 $\rightarrow$ R4L<br>Until R4L = 0<br>else next;                                       |

| EEPMOV.W    | _    | if R4 $\neq$ 0 then<br>Repeat @ER5+ $\rightarrow$ @ER6+,<br>R4-1 $\rightarrow$ R4<br>Until R4 = 0<br>else next;                                           |

|             |      | Transfers a data block. Starting from the address set in ER5, transfers data for the number of bytes set in R4L or R4 to the address location set in ER6. |

|             |      | Execution of the next instruction begins as soon as the transfer is completed.                                                                            |

#### Table 2.9 Block Data Transfer Instructions

#### 2.4.2 Basic Instruction Formats

H8/300H CPU instructions consist of 2-byte (1-word) units. An instruction consists of an operation field (op field), a register field (r field), an effective address extension (EA field), and a condition field (cc).

Figure 2.7 shows examples of instruction formats.

• Operation Field

Indicates the function of the instruction, the addressing mode, and the operation to be carried out on the operand. The operation field always includes the first four bits of the instruction. Some instructions have two operation fields.

• Register Field

Specifies a general register. Address registers are specified by 3 bits, and data registers by 3 bits or 4 bits. Some instructions have two register fields. Some have no register field.

Effective Address Extension

8, 16, or 32 bits specifying immediate data, an absolute address, or a displacement. A24-bit address or displacement is treated as a 32-bit data in which the first 8 bits are 0 (H'00).

• Condition Field

Specifies the branching condition of Bcc instructions.

# Section 3 Exception Handling

Exception handling may be caused by a reset, a trap instruction (TRAPA), or interrupts.

• Reset

A reset has the highest exception priority. Exception handling starts as soon as the reset is cleared by the  $\overline{\text{RES}}$  pin. The chip is also reset when the watchdog timer overflows, and exception handling starts. Exception handling is the same as exception handling by the  $\overline{\text{RES}}$  pin.

Trap Instruction

Exception handling starts when a trap instruction (TRAPA) is executed. The TRAPA instruction generates a vector address corresponding to a vector number from 0 to 3, as specified in the instruction code. Exception handling can be executed at all times in the program execution state.

• Interrupts

External interrupts other than NMI and internal interrupts other than address break are masked by the I bit in CCR, and kept masked while the I bit is set to 1. Exception handling starts when the current instruction or exception handling ends, if an interrupt request has been issued.

# 3.1 Exception Sources and Vector Address

Table 3.1 shows the vector addresses and priority of each exception handling. When more than one interrupt is requested, handling is performed from the interrupt with the highest priority.

| Relative Module           | Exception Sources          | Vector Number | Vector Address   | Priority  |

|---------------------------|----------------------------|---------------|------------------|-----------|

| RES pin<br>Watchdog timer | Reset                      | 0             | H'0000 to H'0001 | High<br>▲ |

| _                         | Reserved for system use    | 1 to 6        | H'0002 to H'000D | -         |

| External interrupt pin    | NMI                        | 7             | H'000E to H'000F | -         |

| CPU                       | Trap instruction (#0)      | 8             | H'0010 to H'0011 | -         |

|                           | (#1)                       | 9             | H'0012 to H'0013 | -         |

|                           | (#2)                       | 10            | H'0014 to H'0015 | -         |

|                           | (#3)                       | 11            | H'0016 to H'0017 | - ↓       |

| Address break             | Break conditions satisfied | 12            | H'0018 to H'0019 | Low       |

| Table 3.1 | <b>Exception Sources and Vector Address</b> |

|-----------|---------------------------------------------|

|-----------|---------------------------------------------|

# 3.4 Interrupt Exception Handling

#### 3.4.1 External Interrupts

There are external interrupts, NMI, IRQ3, IRQ0, and WKP.

#### (1) NMI

NMI interrupt is requested by input falling edge to pin  $\overline{\text{NMI}}$ .

NMI is the highest interrupt, and can always be accepted without depending on the I bit value in CCR.

### (2) IRQ3 to IRQ0 Interrupts

IRQ3 to IRQ0 interrupts are requested by input signals to pins  $\overline{\text{IRQ3}}$  to  $\overline{\text{IRQ0}}$ . These four interrupts are given different vector addresses, and are detected individually by either rising edge sensing or falling edge sensing, depending on the settings of bits IEG3 to IEG0 in IEGR1.

When pins  $\overline{IRQ3}$  to  $\overline{IRQ0}$  are designated for interrupt input in PMR1 and the designated signal edge is input, the corresponding bit in IRR1 is set to 1, requesting the CPU of an interrupt. When IRQ3 to IRQ0 interrupt is accepted, the I bit is set to 1 in CCR. These interrupts can be masked by setting bits IEN3 to IEN0 in IENR1.

#### (3) WKP5 to WKP0 Interrupts

WKP5 to WKP0 interrupts are requested by input signals to pins  $\overline{WKP5}$  to  $\overline{WKP0}$ . These six interrupts have the same vector addresses, and are detected individually by either rising edge sensing or falling edge sensing, depending on the settings of bits WPEG5 to WPEG0 in IEGR2.

When pins  $\overline{WKP5}$  to  $\overline{WKP0}$  are designated for interrupt input in PMR5 and the designated signal edge is input, the corresponding bit in IWPR is set to 1, requesting the CPU of an interrupt. These interrupts can be masked by setting bit IENWP in IENR1.

#### 6.2.1 Sleep Mode

In sleep mode, CPU operation is halted but the on-chip peripheral modules function at the clock frequency set by the MA2 to MA0 bits in SYSCR2. CPU register contents are retained. When an interrupt is requested, sleep mode is cleared and interrupt exception handling starts. Sleep mode is not cleared if the I bit of the condition code register (CCR) is set to 1 or the requested interrupt is disabled in the interrupt enable register. a transition is made to subactive mode when the bit is 1.

When the  $\overline{\text{RES}}$  pin goes low, the CPU goes into the reset state and sleep mode is cleared.

#### 6.2.2 Standby Mode

In standby mode, the clock pulse generator stops, so the CPU and on-chip peripheral modules stop functioning. However, as long as the rated voltage is supplied, the contents of CPU registers, on-chip RAM, and some on-chip peripheral module registers are retained. On-chip RAM contents will be retained as long as the voltage set by the RAM data retention voltage is provided. The I/O ports go to the high-impedance state.

Standby mode is cleared by an interrupt. When an interrupt is requested, the system clock pulse generator starts. After the time set in bits STS2–STS0 in SYSCR1 has elapsed, and interrupt exception handling starts. Standby mode is not cleared if the I bit of CCR is set to 1 or the requested interrupt is disabled in the interrupt enable register.

When the  $\overline{\text{RES}}$  pin goes low, the system clock pulse generator starts. Since system clock signals are supplied to the entire chip as soon as the system clock pulse generator starts functioning, the  $\overline{\text{RES}}$  pin must be kept low until the pulse generator output stabilizes. After the pulse generator output has stabilized, the CPU starts reset exception handling if the  $\overline{\text{RES}}$  pin is driven high.

#### 6.2.3 Subsleep Mode

In subsleep mode, the system clock oscillator is halted, and operation of the CPU and on-chip peripheral modules is halted. As long as a required voltage is applied, the contents of CPU registers, the on-chip RAM, and some registers of the on-chip peripheral modules are retained. I/O ports keep the same states as before the transition.

Subsleep mode is cleared by an interrupt. When an interrupt is requested, the system clock oscillator starts to oscillate. Subsleep mode is cleared and an interrupt exception handling starts when the time set in bits STS2 to STS0 in SYSCR1 elapses. Subsleep mode is not cleared if the I bit of CCR is 1 or the interrupt is disabled in the interrupt enable bit.

# 7.4 Flash Memory Programming/Erasing

A software method using the CPU is employed to program and erase flash memory in the onboard programming modes. Depending on the FLMCR1 setting, the flash memory operates in one of the following four modes: Program mode, program-verify mode, erase mode, and erase-verify mode. The programming control program in boot mode and the user program/erase control program in user program mode use these operating modes in combination to perform programming/erasing. Flash memory programming and erasing should be performed in accordance with the descriptions in section 7.4.1, Program/Program-Verify and section 7.4.2, Erase/Erase-Verify, respectively.

### 7.4.1 Program/Program-Verify

When writing data or programs to the flash memory, the program/program-verify flowchart shown in figure 7.3 should be followed. Performing programming operations according to this flowchart will enable data or programs to be written to the flash memory without subjecting the chip to voltage stress or sacrificing program data reliability.

- 1. Programming must be done to an empty address. Do not reprogram an address to which programming has already been performed.

- 2. Programming should be carried out 128 bytes at a time. A 128-byte data transfer must be performed even if writing fewer than 128 bytes. In this case, H'FF data must be written to the extra addresses.

- 3. Prepare the following data storage areas in RAM: A 128-byte programming data area, a 128byte reprogramming data area, and a 128-byte additional-programming data area. Perform reprogramming data computation according to table 7.4, and additional programming data computation according to table 7.5.

- 4. Consecutively transfer 128 bytes of data in byte units from the reprogramming data area or additional-programming data area to the flash memory. The program address and 128-byte data are latched in the flash memory. The lower 8 bits of the start address in the flash memory destination area must be H'00 or H'80.

- 5. The time during which the P bit is set to 1 is the programming time. Table 7.6 shows the allowable programming times.

- 6. The watchdog timer (WDT) is set to prevent overprogramming due to program runaway, etc. An overflow cycle of approximately 6.6 ms is allowed.

- 7. For a dummy write to a verify address, write 1-byte data H'FF to an address whose lower 2 bits are B'00. Verify data can be read in words or in longwords from the address to which a dummy write was performed.

## 10.3.5 Timer Control Register V1 (TCRV1)

TCRV1 selects the edge at the TRGV pin, enables TRGV input, and selects the clock input to TCNTV.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                         |

|--------|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 5 |          | All 1            |     | Reserved                                                                                                                                                            |

|        |          |                  |     | These bits are always read as 1.                                                                                                                                    |

| 4      | TVEG1    | 0                | R/W | TRGV Input Edge Select                                                                                                                                              |

| 3      | TVEG0    | 0                | R/W | These bits select the TRGV input edge.                                                                                                                              |

|        |          |                  |     | 00: TRGV trigger input is prohibited                                                                                                                                |

|        |          |                  |     | 01: Rising edge is selected                                                                                                                                         |

|        |          |                  |     | 10: Falling edge is selected                                                                                                                                        |

|        |          |                  |     | 11: Rising and falling edges are both selected                                                                                                                      |

| 2      | TRGE     | 0                | R/W | TCNT starts counting up by the input of the edge which is selected by TVEG1 and TVEG0.                                                                              |

|        |          |                  |     | 0: Disables starting counting-up TCNTV by the input of<br>the TRGV pin and halting counting-up TCNTV when<br>TCNTV is cleared by a compare match.                   |

|        |          |                  |     | <ol> <li>Enables starting counting-up TCNTV by the input of<br/>the TRGV pin and halting counting-up TCNTV when<br/>TCNTV is cleared by a compare match.</li> </ol> |

| 1      |          | 1                |     | Reserved                                                                                                                                                            |

|        |          |                  |     | This bit is always read as 1.                                                                                                                                       |

| 0      | ICKS0    | 0                | R/W | Internal Clock Select 0                                                                                                                                             |

|        |          |                  |     | This bit selects clock signals to input to TCNTV in<br>combination with CKS2 to CKS0 in TCRV0.                                                                      |

|        |          |                  |     | Refer to table 10.2.                                                                                                                                                |

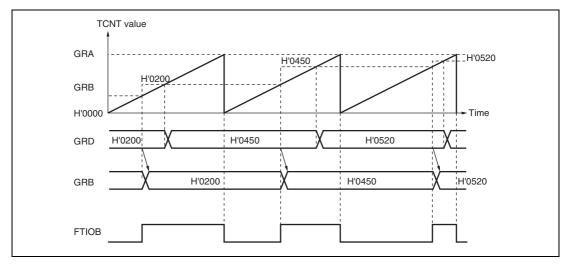

Figure 11.11 shows an example of buffer operation when the FTIOB pin is set to PWM mode and GRD is set as the buffer register for GRB. TCNT is cleared by compare match A, and FTIOB outputs 1 at compare match B and 0 at compare match A.

Due to the buffer operation, the FTIOB output level changes and the value of buffer register GRD is transferred to GRB whenever compare match B occurs. This procedure is repeated every time compare match B occurs.

Figure 11.11 Buffer Operation Example (Output Compare)

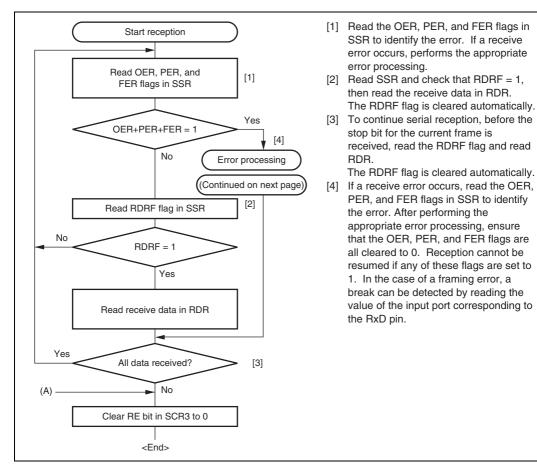

Figure 13.8 Sample Serial Reception Data Flowchart (Asynchronous Mode)(1)

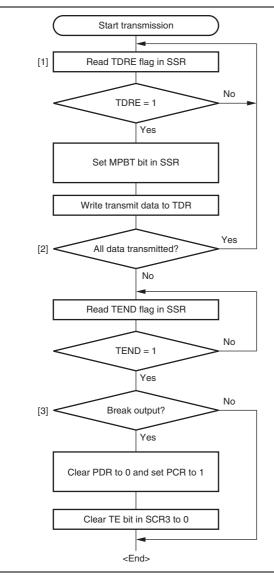

- Read SSR and check that the TDRE flag is set to 1, set the MPBT bit in SSR to 0 or 1, then write transmit data to TDR. When data is written to TDR, the TDRE flag is automatically cleared to 0.

- [2] To continue serial transmission, be sure to read 1 from the TDRE flag to confirm that writing is possible, then write data to TDR. When data is written to TDR, the TDRE flag is automatically cleared to 0.

- [3] To output a break in serial transmission, set the port PCR to 1, clear PDR to 0, then clear the TE bit in SCR3 to 0.

Figure 13.16 Sample Multiprocessor Serial Transmission Flowchart

## 14.6 Usage Notes

## 14.6.1 Permissible Signal Source Impedance

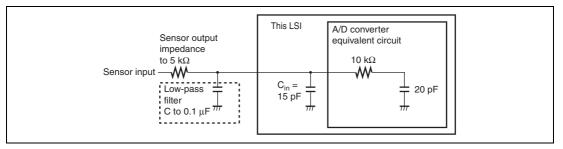

This LSI's analog input is designed such that conversion accuracy is guaranteed for an input signal for which the signal source impedance is 5 k $\Omega$  or less. This specification is provided to enable the A/D converter's sample-and-hold circuit input capacitance to be charged within the sampling time; if the sensor output impedance exceeds 5 k $\Omega$ , charging may be insufficient and it may not be possible to guarantee A/D conversion accuracy. However, for A/D conversion in single mode with a large capacitance provided externally, the input load will essentially comprise only the internal input resistance of 10 k $\Omega$ , and the signal source impedance is ignored. However, as a low-pass filter effect is obtained in this case, it may not be possible to follow an analog signal with a large differential coefficient (e.g., 5 mV/µs or greater) (see figure 14.6). When converting a high-speed analog signal or converting in scan mode, a low-impedance buffer should be inserted.

#### 14.6.2 Influences on Absolute Accuracy

Adding capacitance results in coupling with GND, and therefore noise in GND may adversely affect absolute accuracy. Be sure to make the connection to an electrically stable GND.

Care is also required to ensure that filter circuits do not interfere with digital signals or act as antennas on the mounting board.

Figure 14.6 Analog Input Circuit Example

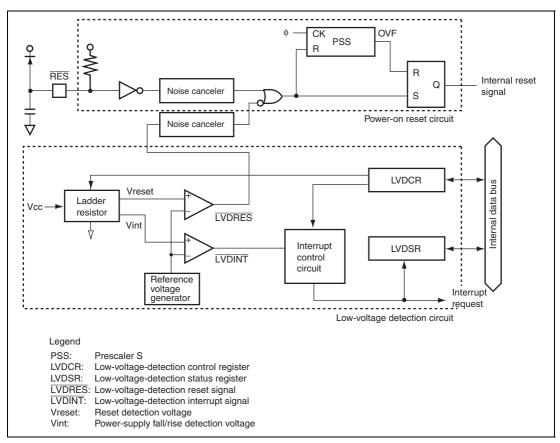

Figure 15.1 Block Diagram of Power-On Reset Circuit and Low-Voltage Detection Circuit

## **15.2 Register Descriptions**

The low-voltage detection circuit has the following registers.

- Low-voltage-detection control register (LVDCR)

- Low-voltage-detection status register (LVDSR)

| Register<br>Name | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Module<br>Name |

|------------------|--------|--------|--------|--------|--------|--------|--------|--------|----------------|

| GRC              | GRC15  | GRC14  | GRC13  | GRC12  | GRC11  | GRC10  | GRC9   | GRC8   | Timer W        |

|                  | GRC7   | GRC6   | GRC5   | GRC4   | GRC3   | GRC2   | GRC1   | GRC0   | •              |

| GRD              | GRD15  | GRD14  | GRD13  | GRD12  | GRD11  | GRD10  | GRD9   | GRD8   | •              |

|                  | GRD7   | GRD6   | GRD5   | GRD4   | GRD3   | GRD2   | GRD1   | GRD0   | •              |

| FLMCR1           | _      | SWE    | ESU    | PSU    | EV     | PV     | E      | Р      | ROM            |

| FLMCR2           | FLER   | _      | _      | _      | _      | _      | _      | _      |                |

| EBR1             | _      | _      | _      | EB4    | EB3    | EB2    | EB1    | EB0    |                |

| FENR             | FLSHE  |        | _      | _      | _      | _      |        | _      | •              |

| TCRV0            | CMIEB  | CMIEA  | OVIE   | CCLR1  | CCLR0  | CKS2   | CKS1   | CKS0   | Timer V        |

| TCSRV            | CMFB   | CMFA   | OVF    | _      | OS3    | OS2    | OS1    | OS0    | •              |

| TCORA            | TCORA7 | TCORA6 | TCORA5 | TCORA4 | TCORA3 | TCORA2 | TCORA1 | TCORA0 | •              |

| TCORB            | TCORB7 | TCORB6 | TCORB5 | TCORB4 | TCORB3 | TCORB2 | TCORB1 | TCORB0 | -              |

| TCNTV            | TCNTV7 | TCNTV6 | TCNTV5 | TCNTV4 | TCNTV3 | TCNTV2 | TCNTV1 | TCNTV0 | •              |

| TCRV1            | _      | _      | _      | TVEG1  | TVEG0  | TRGE   | _      | ICKS0  | -              |

| SMR              | COM    | CHR    | PE     | PM     | STOP   | MP     | CKS1   | CKS0   | SCI3           |

| BRR              | BRR7   | BRR6   | BRR5   | BRR4   | BRR3   | BRR2   | BRR1   | BRR0   | -              |

| SCR3             | TIE    | RIE    | TE     | RE     | MPIE   | TEIE   | CKE1   | CKE0   | -              |

| TDR              | TDR7   | TDR6   | TDR5   | TDR4   | TDR3   | TDR2   | TDR1   | TDR0   | •              |

| SSR              | TDRE   | RDRF   | OER    | FER    | PER    | TEND   | MPBR   | MPBT   | •              |

| RDR              | RDR7   | RDR6   | RDR5   | RDR4   | RDR3   | RDR2   | RDR1   | RDR0   | •              |

| ADDRA            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    | A/D converter  |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      |                |

| ADDRB            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    |                |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      | -              |

| ADDRC            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    |                |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      |                |

| ADDRD            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    |                |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      |                |

| ADCSR            | ADF    | ADIE   | ADST   | SCAN   | CKS    | CH2    | CH1    | CH0    | •              |

| ADCR             | TRGE   |        | _      | _      | —      | _      |        | —      | -              |

| TCSRWD           | B6WI   | TCWE   | B4WI   | TCSRWE | B2WI   | WDON   | B0WI   | WRST   | WDT*           |

| TCWD             | TCWD7  | TCWD6  | TCWD5  | TCWD4  | TCWD3  | TCWD2  | TCWD1  | TCWD0  | -              |

| TMWD             | _      |        | _      | _      | CKS3   | CKS2   | CKS1   | CKS0   | -              |

|          |                         | Addressing Mode and<br>Instruction Length (bytes) |     |    |      |           |             |     |          | )      |   |                                                                             |   |               |       |      |       | No<br>Stat | . of<br>es <sup>*1</sup> |          |  |  |  |  |

|----------|-------------------------|---------------------------------------------------|-----|----|------|-----------|-------------|-----|----------|--------|---|-----------------------------------------------------------------------------|---|---------------|-------|------|-------|------------|--------------------------|----------|--|--|--|--|

| Mnemonic |                         | Operand Size                                      | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @ @ aa | 1 | Operation                                                                   | 1 | Con           | ditio | n Co | v     | с          | Normal                   | Advanced |  |  |  |  |

| MOV      | MOV.W Rs, @-ERd         | w                                                 |     |    |      |           | 2           |     |          |        |   | ERd32–2 $\rightarrow$ ERd32<br>Rs16 $\rightarrow$ @ERd                      | - | -             | \$    | \$   | 0     | -          | (                        | 6        |  |  |  |  |

|          | MOV.W Rs, @aa:16        | w                                                 |     |    |      |           |             | 4   |          |        |   | Rs16 $\rightarrow$ @aa:16                                                   | _ | -             | \$    | \$   | 0     | -          | 6                        | 6        |  |  |  |  |

|          | MOV.W Rs, @aa:24        | w                                                 |     |    |      |           |             | 6   |          |        |   | Rs16 $\rightarrow$ @aa:24                                                   | _ | -             | \$    | \$   | 0     | -          | 8                        | 3        |  |  |  |  |

|          | MOV.L #xx:32, Rd        | L                                                 | 6   |    |      |           |             |     |          |        |   | #xx:32 → Rd32                                                               | _ | -             | \$    | \$   | 0     | -          | (                        | 6        |  |  |  |  |

|          | MOV.L ERs, ERd          | L                                                 |     | 2  |      |           |             |     |          |        |   | ERs32 $\rightarrow$ ERd32                                                   | _ | -             | \$    | \$   | 0     | -          | 1                        | 2        |  |  |  |  |

|          | MOV.L @ERs, ERd         | L                                                 |     |    | 4    |           |             |     |          |        |   | @ERs $\rightarrow$ ERd32                                                    | _ | -             | \$    | \$   | 0     | -          | 8                        | 3        |  |  |  |  |

|          | MOV.L @(d:16, ERs), ERd | L                                                 |     |    |      | 6         |             |     |          |        |   | @(d:16, ERs) → ERd32                                                        | _ | -             | \$    | \$   | 0     | -          | 1                        | 0        |  |  |  |  |

|          | MOV.L @(d:24, ERs), ERd | L                                                 |     |    |      | 10        |             |     |          |        |   | @(d:24, ERs) → ERd32                                                        | _ | -             | \$    | \$   | 0     | -          | 1                        | 4        |  |  |  |  |

|          | MOV.L @ERs+, ERd        | L                                                 |     |    |      |           | 4           |     |          |        |   | @ERs → ERd32<br>ERs32+4 → ERs32                                             | - | -             | \$    | \$   | 0     | -          | 1                        | 10       |  |  |  |  |

|          | MOV.L @aa:16, ERd       | L                                                 |     |    |      |           |             | 6   |          |        |   | @aa:16 $\rightarrow$ ERd32                                                  | _ | —             | \$    | \$   | 0     | -          | 1                        | 0        |  |  |  |  |

|          | MOV.L @aa:24, ERd       | L                                                 |     |    |      |           |             | 8   |          |        |   | @aa:24 $\rightarrow$ ERd32                                                  | _ | -             | \$    | \$   | 0     | -          | 1                        | 2        |  |  |  |  |

|          | MOV.L ERs, @ERd         | L                                                 |     |    | 4    |           |             |     |          |        |   | $ERs32 \rightarrow @ERd$                                                    | _ | -             | \$    | \$   | 0     | —          | 8                        | 3        |  |  |  |  |

|          | MOV.L ERs, @(d:16, ERd) | L                                                 |     |    |      | 6         |             |     |          |        |   | ERs32 $\rightarrow$ @(d:16, ERd)                                            | _ | -             | \$    | \$   | 0     | -          | 1                        | 0        |  |  |  |  |

|          | MOV.L ERs, @(d:24, ERd) | L                                                 |     |    |      | 10        |             |     |          |        |   | ERs32 $\rightarrow$ @(d:24, ERd)                                            | _ | -             | \$    | \$   | 0     | —          | 1                        | 4        |  |  |  |  |

|          | MOV.L ERs, @-ERd        | L                                                 |     |    |      |           | 4           |     |          |        |   | $\begin{array}{l} ERd32-4 \to ERd32 \\ ERs32 \to @ ERd \end{array}$         | - | -             | \$    | \$   | 0     | -          | 1                        | 0        |  |  |  |  |

|          | MOV.L ERs, @aa:16       | L                                                 |     |    |      |           |             | 6   |          |        |   | ERs32 $\rightarrow$ @aa:16                                                  | _ | -             | \$    | \$   | 0     | -          | 1                        | 0        |  |  |  |  |

|          | MOV.L ERs, @aa:24       | L                                                 |     |    |      |           |             | 8   |          |        |   | ERs32 $\rightarrow$ @aa:24                                                  | — | -             | \$    | \$   | 0     | -          | 1                        | 2        |  |  |  |  |

| POP      | POP.W Rn                | W                                                 |     |    |      |           |             |     |          |        | 2 | $\begin{array}{l} @ SP \to Rn16 \\ \\ SP+2 \to SP \end{array}$              | - | -             | \$    | \$   | 0     | -          | (                        | 6        |  |  |  |  |

|          | POP.L ERn               | L                                                 |     |    |      |           |             |     |          |        | 4 | $\begin{array}{l} @ SP \to ERn32 \\ SP+4 \to SP \end{array}$                | _ | -             | \$    | \$   | 0     | -          | 10                       |          |  |  |  |  |

| PUSH     | PUSH.W Rn               | W                                                 |     |    |      |           |             |     |          |        | 2 | $\begin{array}{l} SP-2 \rightarrow SP \\ Rn16 \rightarrow @ SP \end{array}$ | - | -             | \$    | \$   | 0     | -          | (                        | 6        |  |  |  |  |

|          | PUSH.L ERn              | L                                                 |     |    |      |           |             |     |          |        | 4 | $\begin{array}{l} SP\text{-}4 \to SP \\ ERn32 \to @SP \end{array}$          | — | -             | \$    | \$   | 0     | -          | 10                       |          |  |  |  |  |

| MOVFPE   | MOVFPE @aa:16, Rd       | В                                                 |     |    |      |           |             | 4   |          |        |   | Cannot be used in this LSI                                                  |   | annc<br>is LS |       | use  | ed ir | <br>1      |                          |          |  |  |  |  |

| MOVTPE   | MOVTPE Rs, @aa:16       | В                                                 |     |    |      |           |             | 4   |          |        |   | Cannot be used in this LSI                                                  |   | annc<br>is LS |       | use  | ed ir | in         |                          |          |  |  |  |  |

|          |            |              |                                                                                                           |     |    |      |           | ng<br>Lei   |     |          |     |   |                |                |                |                | No. of<br>States <sup>*</sup> |                |                                   |          |  |

|----------|------------|--------------|-----------------------------------------------------------------------------------------------------------|-----|----|------|-----------|-------------|-----|----------|-----|---|----------------|----------------|----------------|----------------|-------------------------------|----------------|-----------------------------------|----------|--|

| Mnemonic |            | Operand Size | Operation                                                                                                 |     |    | @ERn | @(d, ERn) | @-ERn/@ERn+ | 33  | @(d, PC) | @aa |   | Condition Code |                |                |                |                               |                |                                   | Advanced |  |

|          |            | ő            |                                                                                                           | XX# | Rn | 0    | ø         | ø           | @aa | 0        | 0   | Ι | Т              | н              | Ν              | z              | v                             | с              | Ŷ                                 | Ad       |  |

| NEG      | NEG.B Rd   | В            | $0-Rd8 \rightarrow Rd8$                                                                                   |     | 2  |      |           |             |     |          |     |   | —              | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$                | $\updownarrow$ | <ul><li>↓ 2</li><li>↓ 2</li></ul> |          |  |

|          | NEG.W Rd   | W            | $0-Rd16 \rightarrow Rd16$                                                                                 |     | 2  |      |           |             |     |          |     |   | —              | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$                | $\updownarrow$ |                                   |          |  |

|          | NEG.L ERd  | L            | $0-ERd32 \rightarrow ERd32$                                                                               |     | 2  |      |           |             |     |          |     |   | -              | \$             | \$             | \$             | $\updownarrow$                | $\updownarrow$ | 2                                 | 2        |  |

| EXTU     | EXTU.W Rd  | W            | $0 \rightarrow (\text{} \text{ of Rd16})$                                                                 |     | 2  |      |           |             |     |          |     |   | -              | —              | 0              | €              | 0                             | —              | 2                                 | 2        |  |

|          | EXTU.L ERd | L            | $0 \rightarrow (< bits 31 to 16 > of ERd32)$                                                              |     | 2  |      |           |             |     |          |     |   | -              | —              | 0              | \$             | 0                             | —              | 2                                 | 2        |  |

| EXTS     | EXTS.W Rd  | w            | ( <bit 7=""> of Rd16) <math>\rightarrow</math><br/>(<bits 15="" 8="" to=""> of Rd16)</bits></bit>         |     | 2  |      |           |             |     |          |     |   | —              | —              | \$             | \$             | 0                             | —              | 2                                 | 2        |  |

|          | EXTS.L ERd | L            | ( <bit 15=""> of ERd32) <math>\rightarrow</math><br/>(<bits 16="" 31="" to=""> of<br/>ERd32)</bits></bit> |     | 2  |      |           |             |     |          |     |   |                |                | \$             | \$             | 0                             | _              | 2                                 | 2        |  |

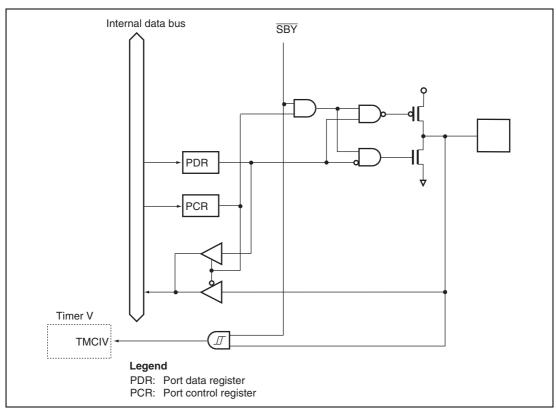

Figure B.15 Port 7 Block Diagram (P75)