Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LFQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36014gfpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 7.4                | Reprogram Data Computation Table                                         | 88  |

|--------------------------|--------------------------------------------------------------------------|-----|

| Table 7.5                | Additional-Program Data Computation Table                                | 88  |

| Table 7.6                | Programming Time                                                         | 88  |

| Section 10               | Timer V                                                                  |     |

| Table 10.1               | Pin Configuration                                                        | 119 |

| Table 10.2               | Clock Signals to Input to TCNTV and Counting Conditions                  |     |

|                          |                                                                          |     |

| Section 11               | Timer W                                                                  | 126 |

| Table 11.1               | Timer W Functions                                                        |     |

| Table 11.2               | Pin Configuration                                                        | 138 |

| Section 13               | Serial Communication Interface 3 (SCI3)                                  |     |

| Table 13.1               | Channel Configuration                                                    |     |

| Table 13.2               | Pin Configuration                                                        |     |

| Table 13.3               | Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (1)   | 185 |

| Table 13.3               | Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (2)   |     |

| Table 13.3               | Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (3)   | 187 |

| Table 13.4               | Maximum Bit Rate for Each Frequency (Asynchronous Mode)                  | 188 |

| Table 13.5               | Examples of BRR Settings for Various Bit Rates (Clocked Synchronous Mode | e)  |

|                          | (1)                                                                      | 189 |

| Table 13.5               | Examples of BRR Settings for Various Bit Rates (Clocked Synchronous Mode | e)  |

|                          | (2)                                                                      | 190 |

| Table 13.6               | SSR Status Flags and Receive Data Handling                               | 197 |

| Table 13.7               | SCI3 Interrupt Requests                                                  | 214 |

| Section 14               | A/D Converter                                                            |     |

| Table 14.1               | Pin Configuration                                                        | 219 |

| Table 14.2               | Analog Input Channels and Corresponding ADDR Registers                   |     |

| Table 14.3               | A/D Conversion Time (Single Mode)                                        |     |

| Section 15               | Power-On Reset and Low-Voltage Detection Circuits (Optional)             |     |

| Section 15<br>Table 15.1 | LVDCR Settings and Select Functions                                      | 222 |

|                          | L V DCR Settings and Select Functions                                    | 232 |

| Section 18               | Electrical Characteristics                                               |     |

| Table 18.1               | Absolute Maximum Ratings                                                 |     |

| Table 18.2               | DC Characteristics (1)                                                   |     |

| Table 18.2               | DC Characteristics (2)                                                   |     |

| Table 18.3               | AC Characteristics                                                       |     |

| Table 18.4               | Serial Interface (SCI3) Timing                                           |     |

| Table 18.5               | A/D Converter Characteristics                                            |     |

| Table 18.6               | Watchdog Timer Characteristics                                           |     |

| Table 18.7               | Flash Memory Characteristics                                             | 264 |

|                                        |                                 | Pir                            | n No.                        |          |                                                                               |

|----------------------------------------|---------------------------------|--------------------------------|------------------------------|----------|-------------------------------------------------------------------------------|

| Туре                                   | Symbol                          | FP-64E                         | FP-48F,<br>FP-48B,<br>TNP-48 | -<br>I/O | Functions                                                                     |

| Timer V                                | TMOV                            | 30                             | 24                           | Output   | This is an output pin for waveforms generated by the output compare function. |

|                                        | TMCIV                           | 29                             | 23                           | Input    | External event input pin.                                                     |

|                                        | TMRIV                           | 28                             | 22                           | Input    | Counter reset input pin.                                                      |

|                                        | TRGV                            | 54                             | 40                           | Input    | Counter start trigger input pin.                                              |

| Timer W                                | FTCI                            | 36                             | 26                           | Input    | External event input pin.                                                     |

|                                        | FTIOA to<br>FTIOD               | 37 to 40                       | 27 to 30                     | I/O      | Output compare output/ input<br>capture input/ PWM output pin                 |

| Serial com-<br>munication<br>interface | TXD,<br>TXD_2,<br>TXD_3*        | 46, 56, 27                     | 36, 42, 21                   | Output   | Transmit data output pin                                                      |

| (SCI)                                  | RXD,<br>RXD_2,<br>RXD_3*        | 45, 57, 26                     | 35, 43, 20                   | Input    | Receive data input pin                                                        |

|                                        | SCK3,<br>SCK3_2,<br>SCK3_3*     | 44, 58, 25                     | 34, 44, 19                   | I/O      | Clock I/O pin                                                                 |

| A/D                                    | AN3 to AN0                      | 59 to 62                       | 45 to 48                     | Input    | Analog input pin                                                              |

| converter                              | ADTRG                           | 22                             | 16                           | Input    | A/D converter trigger input pin.                                              |

| I/O ports                              | PB3 to PB0                      | 59 to 62                       | 45 to 48                     | Input    | 4-bit input port.                                                             |

|                                        | P17 to P14,<br>P12 to P10       | 54 to 51,<br>25 to 23          | 40 to 37,<br>19 to 17        | I/O      | 7-bit I/O port.                                                               |

|                                        | P22 to P20                      | 46 to 44                       | 36 to 34                     | I/O      | 3-bit I/O port.                                                               |

|                                        | P57 to P50                      | 27, 26,<br>22 to 19,<br>14, 13 | 21, 20,<br>16 to 11          | I/O      | 8-bit I/O port                                                                |

|                                        | P76 to P70                      | 30 to 28,<br>55 to 58          | 24 to 22,<br>41 to 44        | I/O      | 7-bit I/O port                                                                |

|                                        | P84 to P80                      | 40 to 36                       | 30 to 26                     | I/O      | 5-bit I/O port.                                                               |

| E10T                                   | E10T _0,<br>E10T _1,<br>E10T _2 | 41, 42, 43                     | 31, 32, 33                   |          | Interface pin for the E10T, E8, or E7 emulator                                |

Note: \* The SCK3\_3, RXD\_3, and TXD\_3 pins are not multiplexed in the H8/36014.

#### • Prior to executing BCLR

| MOV.B | #3F, | ROL   |

|-------|------|-------|

| MOV.B | ROL, | @RAM0 |

| MOV.B | ROL, | @PCR5 |

The PCR5 value (H'3F) is written to a work area in memory (RAM0) as well as to PCR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

| RAM0         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

#### • BCLR instruction executed

BCLR #0, @RAMO

The BCLR instructions executed for the PCR5 work area (RAM0).

#### • After executing BCLR

| MOV.B | @RAMO, ROL |  |

|-------|------------|--|

| MOV.B | ROL, @PCR5 |  |

The work area (RAM0) value is written to PCR5.

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50           |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output        |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | High<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 0             |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0             |

| RAM0         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 0             |

# **3.2 Register Descriptions**

Interrupts are controlled by the following registers.

- Interrupt edge select register 1 (IEGR1)

- Interrupt edge select register 2 (IEGR2)

- Interrupt enable register 1 (IENR1)

- Interrupt flag register 1 (IRR1)

- Wakeup interrupt flag register (IWPR)

### 3.2.1 Interrupt Edge Select Register 1 (IEGR1)

IEGR1 selects the direction of an edge that generates interrupt requests of pins and  $\overline{IRQ3}$  and  $\overline{IRQ0}.$

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                   |

|--------|----------|------------------|-----|-----------------------------------------------|

| 7      | _        | 0                | -   | Reserved                                      |

|        |          |                  |     | This bit is always read as 0.                 |

| 6 to 4 | _        | All 1            |     | Reserved                                      |

|        |          |                  |     | These bits are always read as 1.              |

| 3      | IEG3     | 0                | R/W | IRQ3 Edge Select                              |

|        |          |                  |     | 0: Falling edge of IRQ3 pin input is detected |

|        |          |                  |     | 1: Rising edge of IRQ3 pin input is detected  |

| 2, 1   | _        | All 0            |     | Reserved                                      |

|        |          |                  |     | These bits are always read as 0.              |

| 0      | IEG0     | 0                | R/W | IRQ0 Edge Select                              |

|        |          |                  |     | 0: Falling edge of IRQ0 pin input is detected |

|        |          |                  |     | 1: Rising edge of IRQ0 pin input is detected  |

## 3.2.5 Wakeup Interrupt Flag Register (IWPR)

IWPR is a status flag register for  $\overline{WKP5}$  to  $\overline{WKP0}$  interrupt requests.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                              |

|-----|----------|------------------|-----|----------------------------------------------------------------------------------------------------------|

| 7,6 |          | All 1            |     | Reserved                                                                                                 |

| 7,0 |          | 7.01 1           |     | These bits are always read as 1.                                                                         |

| 5   | IWPF5    | 0                | R/W | WKP5 Interrupt Request Flag                                                                              |

| 0   |          | U                |     | [Setting condition]                                                                                      |

|     |          |                  |     | When $\overline{WKP5}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IWPF5 is cleared by writing 0.                                                                      |

| 4   | IWPF4    | 0                | R/W | WKP4 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When $\overline{WKP4}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IWPF4 is cleared by writing 0.                                                                      |

| 3   | IWPF3    | 0                | R/W | WKP3 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When $\overline{WKP3}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IWPF3 is cleared by writing 0.                                                                      |

| 2   | IWPF2    | 0                | R/W | WKP2 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When $\overline{WKP2}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IWPF2 is cleared by writing 0.                                                                      |

| 1   | IWPF1    | 0                | R/W | WKP1 Interrupt Request Flag                                                                              |

|     |          |                  |     | [Setting condition]                                                                                      |

|     |          |                  |     | When $\overline{WKP1}$ pin is designated for interrupt input and the designated signal edge is detected. |

|     |          |                  |     | [Clearing condition]                                                                                     |

|     |          |                  |     | When IWPF1 is cleared by writing 0.                                                                      |

# Section 4 Address Break

The address break simplifies on-board program debugging. It requests an address break interrupt when the set break condition is satisfied. The interrupt request is not affected by the I bit of CCR. Break conditions that can be set include instruction execution at a specific address and a combination of access and data at a specific address. With the address break function, the execution start point of a program containing a bug is detected and execution is branched to the correcting program. Figure 4.1 shows a block diagram of the address break.

Figure 4.1 Block Diagram of Address Break

# 4.1 **Register Descriptions**

Address break has the following registers.

- Address break control register (ABRKCR)

- Address break status register (ABRKSR)

- Break address register (BARH, BARL)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                            |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | PV       | 0                | R/W | Program-Verify                                                                                                                                                         |

|     |          |                  |     | When this bit is set to 1, the flash memory changes to program-verify mode. When it is cleared to 0, program-verify mode is cancelled.                                 |

| 1   | E        | 0                | R/W | Erase                                                                                                                                                                  |

|     |          |                  |     | When this bit is set to 1, and while the SWE = 1 and ESU = 1 bits are 1, the flash memory changes to erase mode. When it is cleared to 0, erase mode is cancelled.     |

| 0   | Р        | 0                | R/W | Program                                                                                                                                                                |

|     |          |                  |     | When this bit is set to 1, and while the SWE = 1 and PSU = 1 bits are 1, the flash memory changes to program mode. When it is cleared to 0, program mode is cancelled. |

### 7.2.2 Flash Memory Control Register 2 (FLMCR2)

FLMCR2 is a register that displays the state of flash memory programming/erasing. FLMCR2 is a read-only register, and should not be written to.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                         |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | FLER     | 0                | R   | Flash Memory Error                                                                                                                                                                  |

|        |          |                  |     | Indicates that an error has occurred during an operation<br>on flash memory (programming or erasing). When FLER<br>is set to 1, flash memory goes to the error-protection<br>state. |

|        |          |                  |     | See 7.5.3, Error Protection, for details.                                                                                                                                           |

| 6 to 0 | _        | All 0            | _   | Reserved                                                                                                                                                                            |

|        |          |                  |     | These bits are always read as 0.                                                                                                                                                    |

# Section 9 I/O Ports

The group of this LSI has thirty general I/O ports and four general input-only ports. Port 8 is a large current port, which can drive 20 mA ( $@V_{ot} = 1.5$  V) when a low level signal is output. Any of these ports can become an input port immediately after a reset. They can also be used as I/O pins of the on-chip peripheral modules or external interrupt input pins, and these functions can be switched depending on the register settings. The registers for selecting these functions can be divided into two types: those included in I/O ports and those included in each on-chip peripheral module. General I/O ports are comprised of the port control register for controlling inputs/outputs and the port data register for storing output data and can select inputs/outputs in bit units. For functions in each port, see Appendix B.1, I/O Port Block Diagrams. For the execution of bit manipulation instructions to the port control register and port data register, see section 2.8.3, Bit Manipulation Instruction.

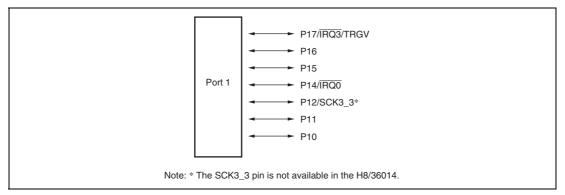

## 9.1 Port 1

Port 1 is a general I/O port also functioning as IRQ interrupt input pins, timer V input pin, and SCI3 I/O pin. Figure 9.1 shows its pin configuration.

#### Figure 9.1 Port 1 Pin Configuration

RENESAS

Port 1 has the following registers.

- Port mode register 1 (PMR1)

- Port control register 1 (PCR1)

- Port data register 1 (PDR1)

- Port pull-up control register 1 (PUCR1)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                    |

|-----|----------|------------------|-----|----------------------------------------------------------------|

| 1   | IOA1     | 0                | R/W | I/O Control A1 and A0                                          |

| 0   | IOA0     | 0                | R/W | When $IOA2 = 0$ ,                                              |

|     |          |                  |     | 00: No output at compare match                                 |

|     |          |                  |     | 01: 0 output to the FTIOA pin at GRA compare match             |

|     |          |                  |     | 10: 1 output to the FTIOA pin at GRA compare match             |

|     |          |                  |     | 11: Output toggles to the FTIOA pin at GRA compare<br>match    |

|     |          |                  |     | When IOA2 = 1,                                                 |

|     |          |                  |     | 00: Input capture at rising edge of the FTIOA pin              |

|     |          |                  |     | 01: Input capture at falling edge of the FTIOA pin             |

|     |          |                  |     | 1X: Input capture at rising and falling edges of the FTIOA pin |

Legend X: Don't care.

### 11.3.6 Timer I/O Control Register 1 (TIOR1)

TIOR1 selects the functions of GRC and GRD, and specifies the functions of the FTIOC and FTIOD pins.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                    |

|-----|----------|------------------|-----|------------------------------------------------|

| 7   | —        | 1                | —   | Reserved                                       |

|     |          |                  |     | This bit is always read as 1.                  |

| 6   | IOD2     | 0                | R/W | I/O Control D2                                 |

|     |          |                  |     | Selects the GRD function.                      |

|     |          |                  |     | 0: GRD functions as an output compare register |

|     |          |                  |     | 1: GRD functions as an input capture register  |

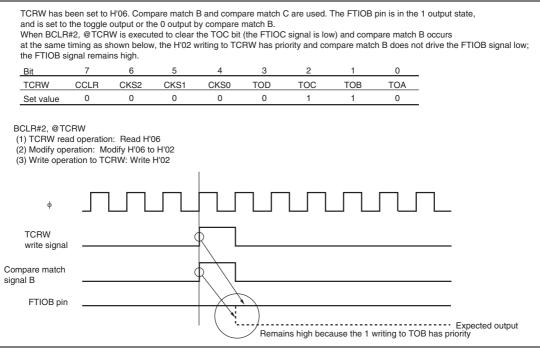

5. The TOA to TOD bits in TCRW decide the value of the FTIO pin, which is output until the first compare match occurs. Once a compare match occurs and this compare match changes the values of FTIOA to FTIOD output, the values of the FTIOA to FTIOD pin output and the values read from the TOA to TOD bits may differ. Moreover, when the writing to TCRW and the generation of the compare match A to D occur at the same timing, the writing to TCRW has the priority. Thus, output change due to the compare match is not reflected to the FTIOA to FTIOD pins. Therefore, when bit manipulation instruction is used to write to TCRW, the values of the FTIOA to FTIOD pin output may result in an unexpected result. When TCRW is to be written to while compare match is operating, stop the counter once before accessing to TCRW, read the port 8 state to reflect the values of FTIOA to FTIOD output, to TOA to TOD, and then restart the counter. Figure 11.26 shows an example when the compare match and the bit manipulation instruction to TCRW occur at the same timing.

Figure 11.26 When Compare Match and Bit Manipulation Instruction to TCRW Occur at the Same Timing

# 13.2 Input/Output Pins

Table 13.2 shows the SCI3 pin configuration.

#### Table 13.2 Pin Configuration

| Pin Name                  | Abbreviation | I/O    | Function                  |

|---------------------------|--------------|--------|---------------------------|

| SCI3 clock                | SCK3         | I/O    | SCI3 clock input/output   |

| SCI3 receive data input   | RXD          | Input  | SCI3 receive data input   |

| SCI3 transmit data output | TXD          | Output | SCI3 transmit data output |

# **13.3** Register Descriptions

The SCI3 has the following registers for each channel.

- Receive Shift Register (RSR)

- Receive Data Register (RDR)

- Transmit Shift Register (TSR)

- Transmit Data Register (TDR)

- Serial Mode Register (SMR)

- Serial Control Register 3 (SCR3)

- Serial Status Register (SSR)

- Bit Rate Register (BRR)

- SCI3\_3 Module Control Register (SMCR)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                 |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CKS1     | 0                | R/W | Clock Select 0 and 1                                                                                                                                                                                                                        |

| 0   | CKS0     | 0                | R/W | These bits select the clock source for the baud rate generator.                                                                                                                                                                             |

|     |          |                  |     | 00: φ clock (n = 0)                                                                                                                                                                                                                         |

|     |          |                  |     | 01:                                                                                                                                                                                                                                         |

|     |          |                  |     | 10: φ/16 clock (n = 2)                                                                                                                                                                                                                      |

|     |          |                  |     | 11:                                                                                                                                                                                                                                         |

|     |          |                  |     | For the relationship between the bit rate register setting<br>and the baud rate, see section 13.3.8, Bit Rate Register<br>(BRR). n is the decimal representation of the value of n in<br>BRR (see section 13.3.8, Bit Rate Register (BRR)). |

#### 13.3.6 Serial Control Register 3 (SCR3)

SCR3 is a register that enables or disables SCI3 transfer operations and interrupt requests, and is also used to select the transfer clock source. For details on interrupt requests, refer to section 13.7, Interrupts.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                            |

|-----|----------|------------------|-----|------------------------------------------------------------------------|

| 7   | TIE      | 0                | R/W | Transmit Interrupt Enable                                              |

|     |          |                  |     | When this bit is set to 1, the TXI interrupt request is enabled.       |

| 6   | RIE      | 0                | R/W | Receive Interrupt Enable                                               |

|     |          |                  |     | When this bit is set to 1, RXI and ERI interrupt requests are enabled. |

| 5   | TE       | 0                | R/W | Transmit Enable                                                        |

|     |          |                  |     | When this bit s set to 1, transmission is enabled.                     |

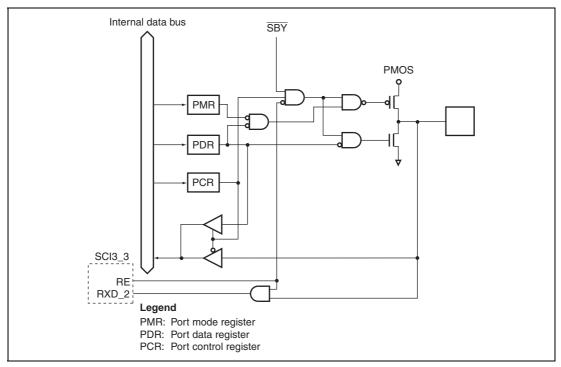

| 4   | RE       | 0                | R/W | Receive Enable                                                         |

|     |          |                  |     | When this bit is set to 1, reception is enabled.                       |

# 13.8 Usage Notes

#### 13.8.1 Break Detection and Processing

When framing error detection is performed, a break can be detected by reading the RXD pin value directly. In a break, the input from the RXD pin becomes all 0s, setting the FER flag, and possibly the PER flag. Note that as the SCI3 continues the receive operation after receiving a break, even if the FER flag is cleared to 0, it will be set to 1 again.

#### 13.8.2 Mark State and Break Sending

When TE is 0, the TXD pin is used as an I/O port whose direction (input or output) and level are determined by PCR and PDR. This can be used to set the TXD pin to mark state (high level) or send a break during serial data transmission. To maintain the communication line at mark state until TE is set to 1, set both PCR and PDR to 1. As TE is cleared to 0 at this point, the TXD pin becomes an I/O port, and 1 is output from the TXD pin. To send a break during serial transmission, first set PCR to 1 and clear PDR to 0, and then clear TE to 0. When TE is cleared to 0, the transmitter is initialized regardless of the current transmission state, the TXD pin becomes an I/O port, and 0 is output from the TXD pin.

#### 13.8.3 Receive Error Flags and Transmit Operations (Clocked Synchronous Mode Only)

Transmission cannot be started when a receive error flag (OER, PER, or FER) is set to 1, even if the TDRE flag is cleared to 0. Be sure to clear the receive error flags to 0 before starting transmission. Note also that receive error flags cannot be cleared to 0 even if the RE bit is cleared to 0.

# Section 14 A/D Converter

This LSI includes a successive approximation type 10-bit A/D converter that allows up to four analog input channels to be selected. The block diagram of the A/D converter is shown in figure 14.1.

## 14.1 Features

- 10-bit resolution

- Four input channels

- Conversion time: at least 3.5 µs per channel (at 20 MHz operation)

- Two operating modes

- Single mode: Single-channel A/D conversion

- Scan mode: Continuous A/D conversion on 1 to 4 channels

- Four data registers

- Conversion results are held in a 16-bit data register for each channel

- Sample and hold function

- Two conversion start methods

- Software

- External trigger signal

- Interrupt request

- An A/D conversion end interrupt request (ADI) can be generated

| Register Name                    | Abbre-<br>viation | Bit No | Address | Module<br>Name    | Data Bus<br>Width | Access<br>State |

|----------------------------------|-------------------|--------|---------|-------------------|-------------------|-----------------|

| Timer mode register WD           | TMWD              | 8      | H'FFC2  | WDT* <sup>3</sup> | 8                 | 2               |

| Address break control register   | ABRKCR            | 8      | H'FFC8  | Address<br>break  | 8                 | 2               |

| Address break status register    | ABRKSR            | 8      | H'FFC9  | Address<br>break  | 8                 | 2               |

| Break address register H         | BARH              | 8      | H'FFCA  | Address<br>break  | 8                 | 2               |

| Break address register L         | BARL              | 8      | H'FFCB  | Address<br>break  | 8                 | 2               |

| Break data register H            | BDRH              | 8      | H'FFCC  | Address<br>break  | 8                 | 2               |

| Break data register L            | BDRL              | 8      | H'FFCD  | Address<br>break  | 8                 | 2               |

| Port pull-up control register 1  | PUCR1             | 8      | H'FFD0  | I/O port          | 8                 | 2               |

| Port pull-up control register 5  | PUCR5             | 8      | H'FFD1  | I/O port          | 8                 | 2               |

| Port data register 1             | PDR1              | 8      | H'FFD4  | I/O port          | 8                 | 2               |

| Port data register 2             | PDR2              | 8      | H'FFD5  | I/O port          | 8                 | 2               |

| Port data register 5             | PDR5              | 8      | H'FFD8  | I/O port          | 8                 | 2               |

| Port data register 7             | PDR7              | 8      | H'FFDA  | I/O port          | 8                 | 2               |

| Port data register 8             | PDR8              | 8      | H'FFDB  | I/O port          | 8                 | 2               |

| Port data register B             | PDRB              | 8      | H'FFDD  | I/O port          | 8                 | 2               |

| Port mode register 1             | PMR1              | 8      | H'FFE0  | I/O port          | 8                 | 2               |

| Port mode register 5             | PMR5              | 8      | H'FFE1  | I/O port          | 8                 | 2               |

| Port control register 1          | PCR1              | 8      | H'FFE4  | I/O port          | 8                 | 2               |

| Port control register 2          | PCR2              | 8      | H'FFE5  | I/O port          | 8                 | 2               |

| Port control register 5          | PCR5              | 8      | H'FFE8  | I/O port          | 8                 | 2               |

| Port control register 7          | PCR7              | 8      | H'FFEA  | I/O port          | 8                 | 2               |

| Port control register 8          | PCR8              | 8      | H'FFEB  | I/O port          | 8                 | 2               |

| System control register 1        | SYSCR1            | 8      | H'FFF0  | Power-<br>down    | 8                 | 2               |

| System control register 2        | SYSCR2            | 8      | H'FFF1  | Power-<br>down    | 8                 | 2               |

| Interrupt edge select register 1 | IEGR1             | 8      | H'FFF2  | Interrupts        | 8                 | 2               |

| Register<br>Name | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Module<br>Name |

|------------------|--------|--------|--------|--------|--------|--------|--------|--------|----------------|

| GRC              | GRC15  | GRC14  | GRC13  | GRC12  | GRC11  | GRC10  | GRC9   | GRC8   | Timer W        |

|                  | GRC7   | GRC6   | GRC5   | GRC4   | GRC3   | GRC2   | GRC1   | GRC0   | •              |

| GRD              | GRD15  | GRD14  | GRD13  | GRD12  | GRD11  | GRD10  | GRD9   | GRD8   | •              |

|                  | GRD7   | GRD6   | GRD5   | GRD4   | GRD3   | GRD2   | GRD1   | GRD0   | •              |

| FLMCR1           | _      | SWE    | ESU    | PSU    | EV     | PV     | E      | Р      | ROM            |

| FLMCR2           | FLER   | _      | _      | _      | _      | _      | _      | _      |                |

| EBR1             | _      | _      | _      | EB4    | EB3    | EB2    | EB1    | EB0    |                |

| FENR             | FLSHE  |        | _      | _      | _      | _      |        | _      | •              |

| TCRV0            | CMIEB  | CMIEA  | OVIE   | CCLR1  | CCLR0  | CKS2   | CKS1   | CKS0   | Timer V        |

| TCSRV            | CMFB   | CMFA   | OVF    | _      | OS3    | OS2    | OS1    | OS0    | •              |

| TCORA            | TCORA7 | TCORA6 | TCORA5 | TCORA4 | TCORA3 | TCORA2 | TCORA1 | TCORA0 | •              |

| TCORB            | TCORB7 | TCORB6 | TCORB5 | TCORB4 | TCORB3 | TCORB2 | TCORB1 | TCORB0 | -              |

| TCNTV            | TCNTV7 | TCNTV6 | TCNTV5 | TCNTV4 | TCNTV3 | TCNTV2 | TCNTV1 | TCNTV0 | •              |

| TCRV1            | _      | _      | _      | TVEG1  | TVEG0  | TRGE   | _      | ICKS0  | -              |

| SMR              | COM    | CHR    | PE     | PM     | STOP   | MP     | CKS1   | CKS0   | SCI3           |

| BRR              | BRR7   | BRR6   | BRR5   | BRR4   | BRR3   | BRR2   | BRR1   | BRR0   | -              |

| SCR3             | TIE    | RIE    | TE     | RE     | MPIE   | TEIE   | CKE1   | CKE0   | -              |

| TDR              | TDR7   | TDR6   | TDR5   | TDR4   | TDR3   | TDR2   | TDR1   | TDR0   | •              |

| SSR              | TDRE   | RDRF   | OER    | FER    | PER    | TEND   | MPBR   | MPBT   | •              |

| RDR              | RDR7   | RDR6   | RDR5   | RDR4   | RDR3   | RDR2   | RDR1   | RDR0   | •              |

| ADDRA            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    | A/D converter  |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      |                |

| ADDRB            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    |                |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      | -              |

| ADDRC            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    |                |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      |                |

| ADDRD            | AD9    | AD8    | AD7    | AD6    | AD5    | AD4    | AD3    | AD2    |                |

|                  | AD1    | AD0    | _      | _      | _      | _      | _      | _      |                |

| ADCSR            | ADF    | ADIE   | ADST   | SCAN   | CKS    | CH2    | CH1    | CH0    | •              |

| ADCR             | TRGE   |        | _      | _      | —      | _      |        | —      | -              |

| TCSRWD           | B6WI   | TCWE   | B4WI   | TCSRWE | B2WI   | WDON   | B0WI   | WRST   | WDT*           |

| TCWD             | TCWD7  | TCWD6  | TCWD5  | TCWD4  | TCWD3  | TCWD2  | TCWD1  | TCWD0  | -              |

| TMWD             | _      |        | _      | _      | CKS3   | CKS2   | CKS1   | CKS0   | -              |

#### 18.2.3 AC Characteristics

#### Table 18.3 AC Characteristics

$V_{cc} = 3.0 \text{ V}$  to 5.5 V,  $V_{ss} = 0.0 \text{ V}$ ,  $T_a = -20^{\circ}\text{C}$  to +75°C, unless otherwise specified.

|                                                          |                  | Applicable    |                                            |      | Value | s    |                  | Reference   |

|----------------------------------------------------------|------------------|---------------|--------------------------------------------|------|-------|------|------------------|-------------|

| Item                                                     | Symbol           | Pins          | Test Condition                             | Min  | Тур   | Max  | Unit             | Figure      |

| System clock oscillation                                 | f <sub>osc</sub> | OSC1,<br>OSC2 | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$ | 2.0  | —     | 20.0 | MHz              | *1          |

| frequency                                                |                  |               |                                            | 2.0  | _     | 10.0 | MHz              | _           |

| System clock (ø)                                         | t <sub>cyc</sub> |               |                                            | 1    | _     | 64   | t <sub>osc</sub> | *2          |

| cycle time                                               |                  |               |                                            | —    | —     | 12.8 | μs               | _           |

| Instruction cycle time                                   |                  |               |                                            | 2    | _     | _    | t <sub>cyc</sub> |             |

| Oscillation<br>stabilization time<br>(crystal resonator) | t <sub>rc</sub>  | OSC1,<br>OSC2 |                                            | _    |       | 10.0 | ms               |             |

| Oscillation<br>stabilization time<br>(ceramic resonator) | t <sub>rc</sub>  | OSC1,<br>OSC2 |                                            | _    | _     | 5.0  | ms               |             |

| External clock                                           | t <sub>CPH</sub> | OSC1          | $V_{\rm CC}$ = 4.0 V to 5.5 V              | 20.0 | —     | —    | ns               | Figure 18.1 |

| high width                                               |                  |               |                                            | 40.0 | _     | —    | ns               | _           |

| External clock                                           | t <sub>cpl</sub> | OSC1          | $V_{\rm CC}$ = 4.0 V to 5.5 V              | 20.0 | _     | _    | ns               | -           |

| low width                                                |                  |               |                                            | 40.0 | _     | —    | ns               | _           |

| External clock                                           | t <sub>CPr</sub> | OSC1          | $V_{\rm CC}$ = 4.0 V to 5.5 V              | —    | _     | 10.0 | ns               | _           |

| rise time                                                |                  |               |                                            | —    | —     | 15.0 | ns               | _           |

| External clock                                           | t <sub>CPf</sub> | OSC1          | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$ | —    | —     | 10.0 | ns               | _           |

| fall time                                                |                  |               |                                            |      |       | 15.0 | ns               | -           |

Figure B.11 Port 5 Block Diagram (P56) (H8/36024)

| Product Ty | уре        |                               | Product Code  | Model Marking      | Package Code     |

|------------|------------|-------------------------------|---------------|--------------------|------------------|

| H8/36010   | Masked ROM | Standard                      | HD64336010FP  | HD64336010(***)FP  | LQFP-64 (FP-64E) |

|            | version    | product                       | HD64336010FX  | HD64336010(***)FX  | LQFP-48 (FP-48F) |

|            |            |                               | HD64336010FY  | HD64336010(***)FY  | LQFP-48 (FP-48B) |

|            |            |                               | HD64336010FT  | HD64336010(***)FT  | QFN-48(TNP-48)   |

|            |            | Product<br>with POR<br>& LVDC | HD64336010GFP | HD64336010G(***)FP | LQFP-64 (FP-64E) |

|            |            |                               | HD64336010GFX | HD64336010G(***)FX | LQFP-48 (FP-48F) |

|            |            |                               | HD64336010GFY | HD64336010G(***)FY | LQFP-48 (FP-48B) |

|            |            |                               | HD64336010GFT | HD64336010G(***)FT | QFN-48(TNP-48)   |

#### Legend

POR & LVDC: Power-on reset and low-voltage detection circuits

(\*\*\*): ROM code