Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36014gfxv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Register Configuration

The H8/300H CPU has the internal registers shown in figure 2.2. There are two types of registers; general registers and control registers. The control registers are a 24-bit program counter (PC), and an 8-bit condition code register (CCR).

| General Re                 | gisters (ERn)                                                                                      |                                       |                                                                       |  |

|----------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------|--|

|                            | 15                                                                                                 | 0 7                                   | 0 7 0                                                                 |  |

| ER0                        | E0                                                                                                 | R0H                                   | R0L                                                                   |  |

| ER1                        | E1                                                                                                 | R1H                                   | R1L                                                                   |  |

| ER2                        | E2                                                                                                 | R2H                                   | R2L                                                                   |  |

| ER3                        | E3                                                                                                 | R3H                                   | R3L                                                                   |  |

| ER4                        | E4                                                                                                 | R4H                                   | R4L                                                                   |  |

| ER5                        | E5                                                                                                 | R5H                                   | R5L                                                                   |  |

| ER6                        | E6                                                                                                 | R6H                                   | R6L                                                                   |  |

| ER7 (SP)                   | E7                                                                                                 | R7H                                   | R7L                                                                   |  |

| Control He                 | gisters (CR)<br>23                                                                                 | PC                                    | 0                                                                     |  |

|                            |                                                                                                    | СС                                    | 7 6 5 4 3 2 1 0<br>R I UIHUNZVC                                       |  |

| Legend                     |                                                                                                    |                                       |                                                                       |  |

| SP<br>PC<br>CCR<br>I<br>UI | :Stack pointer<br>:Program counter<br>:Condition-code register<br>:Interrupt mask bit<br>:User bit | U :Use<br>N :Neg<br>Z :Zero<br>V :Ove | -carry flag<br>r bit<br>ative flag<br>b flag<br>rflow flag<br>ry flag |  |

Figure 2.2 CPU Registers

# 2.3 Data Formats

The H8/300H CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data. Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data. The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

#### 2.3.1 General Register Data Formats

Data Type General Register Data Format 7 0 **RnH** 6 5 4 3 2 1 0 Don't care 7 1-bit data Don't care RnL 7 6 5 4 3 2 1-bit data 7 4 3 0 4-bit BCD data RnH Upper Lower Don't care 4 3 0 4-bit BCD data RnL Don't care Upper Lower Byte data RnH Don't care MSB LSB Byte data RnL Don't care MSB LSB

Figure 2.5 shows the data formats in general registers.

Figure 2.5 General Register Data Formats (1)

# 6.1.2 System Control Register 2 (SYSCR2)

SYSCR2 controls the power-down modes, as well as SYSCR1.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                                |

|------|----------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| 7    | SMSEL    | 0                | R/W | Sleep Mode Selection                                                                                                       |

|      |          |                  |     | This bit selects the mode to transit after the execution of a SLEEP instruction, as well as bit SSBY of SYSCR1.            |

|      |          |                  |     | For details, see table 6.2.                                                                                                |

| 6    | _        | 0                | _   | Reserved                                                                                                                   |

|      |          |                  |     | This bit is always read as 0.                                                                                              |

| 5    | DTON     | 0                | R/W | Direct Transfer on Flag                                                                                                    |

|      |          |                  |     | This bit selects the mode to transit after the execution of a SLEEP instruction, as well as bit SSBY of SYSCR1.            |

|      |          |                  |     | For details, see table 6.2.                                                                                                |

| 4    | MA2      | 0                | R/W | Active Mode Clock Select 2 to 0                                                                                            |

| 3    | MA1      | 0                | R/W | These bits select the operating clock frequency in active                                                                  |

| 2    | MAO      | 0                | R/W | and sleep modes. The operating clock frequency<br>changes to the set frequency after the SLEEP instruction<br>is executed. |

|      |          |                  |     | OXX: $\phi_{ m osc}$                                                                                                       |

|      |          |                  |     | 100: φ <sub>osc</sub> /8                                                                                                   |

|      |          |                  |     | 101: φ <sub>osc</sub> /16                                                                                                  |

|      |          |                  |     | 110:                                                                                                                       |

|      |          |                  |     | 111:                                                                                                                       |

| 1, 0 | _        | All 0            | _   | Reserved                                                                                                                   |

| _    |          |                  |     | These bits are always read as 0.                                                                                           |

Legend: X : Don't care.

#### 10.3.3 Timer Control Register V0 (TCRV0)

TCRV0 selects the input clock signals of TCNTV, specifies the clearing conditions of TCNTV, and controls each interrupt request.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                              |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CMIEB    | 0                | R/W | Compare Match Interrupt Enable B                                                                                                         |

|     |          |                  |     | When this bit is set to 1, interrupt request from the CMFB bit in TCSRV is enabled.                                                      |

| 6   | CMIEA    | 0                | R/W | Compare Match Interrupt Enable A                                                                                                         |

|     |          |                  |     | When this bit is set to 1, interrupt request from the CMFA bit in TCSRV is enabled.                                                      |

| 5   | OVIE     | 0                | R/W | Timer Overflow Interrupt Enable                                                                                                          |

|     |          |                  |     | When this bit is set to 1, interrupt request from the OVF bit in TCSRV is enabled.                                                       |

| 4   | CCLR1    | 0                | R/W | Counter Clear 1 and 0                                                                                                                    |

| 3   | CCLR0    | 0                | R/W | These bits specify the clearing conditions of TCNTV.                                                                                     |

|     |          |                  |     | 00: Clearing is disabled                                                                                                                 |

|     |          |                  |     | 01: Cleared by compare match A                                                                                                           |

|     |          |                  |     | 10: Cleared by compare match B                                                                                                           |

|     |          |                  |     | <ol> <li>Cleared on the rising edge of the TMRIV pin. The<br/>operation of TCNTV after clearing depends on TRGE<br/>in TCRV1.</li> </ol> |

| 2   | CKS2     | 0                | R/W | Clock Select 2 to 0                                                                                                                      |

| 1   | CKS1     | 0                | R/W | These bits select clock signals to input to TCNTV and the                                                                                |

| 0   | CKS0     | 0                | R/W | counting condition in combination with ICKS0 in TCRV1.                                                                                   |

|     |          |                  |     | Refer to table 10.2.                                                                                                                     |

# 10.5 Timer V Application Examples

### 10.5.1 Pulse Output with Arbitrary Duty Cycle

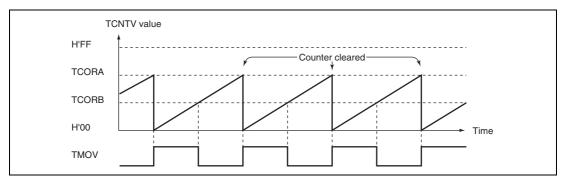

Figure 10.9 shows an example of output of pulses with an arbitrary duty cycle.

- 1. Set bits CCLR1 and CCLR0 in TCRV0 so that TCNTV will be cleared by compare match with TCORA.

- 2. Set bits OS3 to OS0 in TCSRV so that the output will go to 1 at compare match with TCORA and to 0 at compare match with TCORB.

- 3. Set bits CKS2 to CKS0 in TCRV0 and bit ICKS0 in TCRV1 to select the desired clock source.

- 4. With these settings, a waveform is output without further software intervention, with a period determined by TCORA and a pulse width determined by TCORB.

Figure 10.9 Pulse Output Example

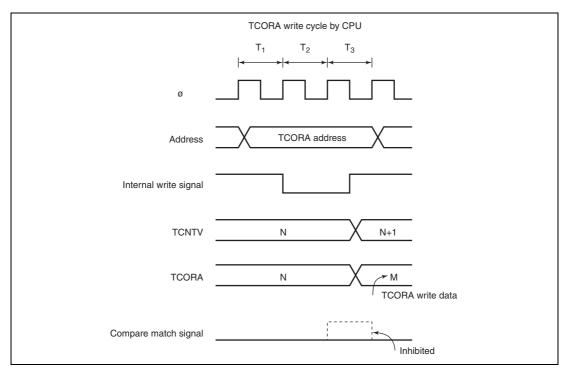

Figure 10.12 Contention between TCORA Write and Compare Match

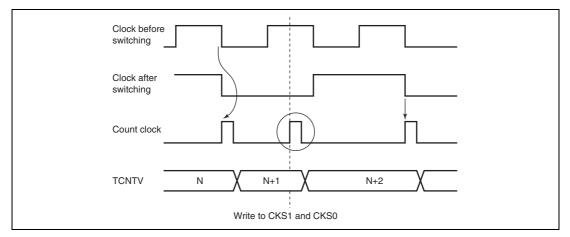

Figure 10.13 Internal Clock Switching and TCNTV Operation

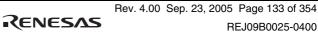

Periodic counting operation can be performed when GRA is set as an output compare register and bit CCLR in TCRW is set to 1. When the count matches GRA, TCNT is cleared to H'0000, the IMFA flag in TSRW is set to 1. If the corresponding IMIEA bit in TIERW is set to 1, an interrupt request is generated. TCNT continues counting from H'0000. Figure 11.3 shows periodic counting.

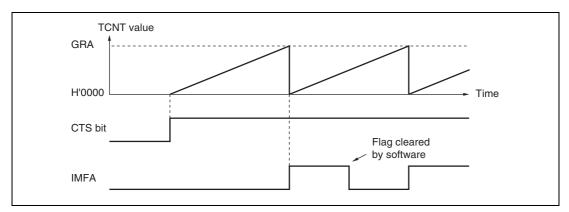

By setting a general register as an output compare register, compare match A, B, C, or D can cause the output at the FTIOA, FTIOB, FTIOC, or FTIOD pin to output 0, output 1, or toggle. Figure 11.4 shows an example of 0 and 1 output when TCNT operates as a free-running counter, 1 output is selected for compare match A, and 0 output is selected for compare match B. When signal is already at the selected output level, the signal level does not change at compare match.

Figure 11.4 0 and 1 Output Example (TOA = 0, TOB = 1)

RENESAS

|                      |   |     |              | Hz) |       |              |   |      |              |   |     |              |  |

|----------------------|---|-----|--------------|-----|-------|--------------|---|------|--------------|---|-----|--------------|--|

|                      |   | 2   |              |     | 2.097 | 152          |   | 2.45 | 76           | 3 |     |              |  |

| Bit Rate<br>(bits/s) | n | N   | Error<br>(%) | n   | N     | Error<br>(%) | n | N    | Error<br>(%) | n | N   | Error<br>(%) |  |

| 110                  | 1 | 141 | 0.03         | 1   | 148   | -0.04        | 1 | 174  | -0.26        | 1 | 212 | 0.03         |  |

| 150                  | 1 | 103 | 0.16         | 1   | 108   | 0.21         | 1 | 127  | 0.00         | 1 | 155 | 0.16         |  |

| 300                  | 0 | 207 | 0.16         | 0   | 217   | 0.21         | 0 | 255  | 0.00         | 1 | 77  | 0.16         |  |

| 600                  | 0 | 103 | 0.16         | 0   | 108   | 0.21         | 0 | 127  | 0.00         | 0 | 155 | 0.16         |  |

| 1200                 | 0 | 51  | 0.16         | 0   | 54    | -0.70        | 0 | 63   | 0.00         | 0 | 77  | 0.16         |  |

| 2400                 | 0 | 25  | 0.16         | 0   | 26    | 1.14         | 0 | 31   | 0.00         | 0 | 38  | 0.16         |  |

| 4800                 | 0 | 12  | 0.16         | 0   | 13    | -2.48        | 0 | 15   | 0.00         | 0 | 19  | -2.34        |  |

| 9600                 | 0 | 6   | -6.99        | 0   | 6     | -2.48        | 0 | 7    | 0.00         | 0 | 9   | -2.34        |  |

| 19200                | 0 | 2   | 8.51         | 0   | 2     | 13.78        | 0 | 3    | 0.00         | 0 | 4   | -2.34        |  |

| 31250                | 0 | 1   | 0.00         | 0   | 1     | 4.86         | 0 | 1    | 22.88        | 0 | 2   | 0.00         |  |

| 38400                | 0 | 1   | -18.62       | 0   | 1     | -14.67       | 0 | 1    | 0.00         |   |     | _            |  |

#### Table 13.3 Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (1)

#### Operating Frequency φ (MHz)

|                      |   | 3.68 | 64           |   | 4   |              |   | 4.91 | 52           | 5 |     |              |  |  |

|----------------------|---|------|--------------|---|-----|--------------|---|------|--------------|---|-----|--------------|--|--|

| Bit Rate<br>(bits/s) | n | N    | Error<br>(%) | n | N   | Error<br>(%) | n | N    | Error<br>(%) | n | N   | Error<br>(%) |  |  |

| 110                  | 2 | 64   | 0.70         | 2 | 70  | 0.03         | 2 | 86   | 0.31         | 2 | 88  | -0.25        |  |  |

| 150                  | 1 | 191  | 0.00         | 1 | 207 | 0.16         | 1 | 255  | 0.00         | 2 | 64  | 0.16         |  |  |

| 300                  | 1 | 95   | 0.00         | 1 | 103 | 0.16         | 1 | 127  | 0.00         | 1 | 129 | 0.16         |  |  |

| 600                  | 0 | 191  | 0.00         | 0 | 207 | 0.16         | 0 | 255  | 0.00         | 1 | 64  | 0.16         |  |  |

| 1200                 | 0 | 95   | 0.00         | 0 | 103 | 0.16         | 0 | 127  | 0.00         | 0 | 129 | 0.16         |  |  |

| 2400                 | 0 | 47   | 0.00         | 0 | 51  | 0.16         | 0 | 63   | 0.00         | 0 | 64  | 0.16         |  |  |

| 4800                 | 0 | 23   | 0.00         | 0 | 25  | 0.16         | 0 | 31   | 0.00         | 0 | 32  | -1.36        |  |  |

| 9600                 | 0 | 11   | 0.00         | 0 | 12  | 0.16         | 0 | 15   | 0.00         | 0 | 15  | 1.73         |  |  |

| 19200                | 0 | 5    | 0.00         | 0 | 6   | -6.99        | 0 | 7    | 0.00         | 0 | 7   | 1.73         |  |  |

| 31250                | _ | —    | _            | 0 | 3   | 0.00         | 0 | 4    | -1.70        | 0 | 4   | 0.00         |  |  |

| 38400                | 0 | 2    | 0.00         | 0 | 2   | 8.51         | 0 | 3    | 0.00         | 0 | 3   | 1.73         |  |  |

Legend

---: A setting is available but error occurs

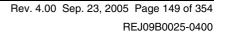

- Read the OER flag in SSR to determine if there is an error. If an overrun error has occurred, execute overrun error processing.

- [2] Read SSR and check that the RDRF flag is set to 1, then read the receive data in RDR. When data is read from RDR, the RDRF flag is automatically cleared to 0.

- [3] To continue serial reception, before the MSB (bit 7) of the current frame is received, reading the RDRF flag and reading RDR should be finished. When data is read from RDR, the RDRF flag is automatically cleared to 0.

- [4] If an overrun error occurs, read the OER flag in SSR, and after performing the appropriate error processing, clear the OER flag to 0. Reception cannot be resumed if the OER flag is set to 1.

Figure 13.13 Sample Serial Reception Flowchart (Clocked Synchronous Mode)

RENESAS

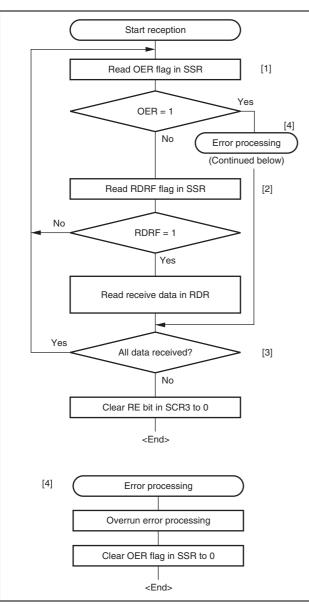

#### Figure 13.15 Example of Inter-Processor Communication Using Multiprocessor Format (Transmission of Data H'AA to Receiving Station A)

#### 13.6.1 Multiprocessor Serial Data Transmission

Figure 13.16 shows a sample flowchart for multiprocessor serial data transmission. For an ID transmission cycle, set the MPBT bit in SSR to 1 before transmission. For a data transmission cycle, clear the MPBT bit in SSR to 0 before transmission. All other SCI3 operations are the same as those in asynchronous mode.

# 14.4 Operation

The A/D converter operates by successive approximation with 10-bit resolution. It has two operating modes; single mode and scan mode. When changing the operating mode or analog input channel, in order to prevent incorrect operation, first clear the bit ADST to 0 in ADCSR. The ADST bit can be set at the same time as the operating mode or analog input channel is changed.

#### 14.4.1 Single Mode

In single mode, A/D conversion is performed once for the analog input on the specified single channel as follows:

- 1. A/D conversion is started from the first channel when the ADST bit in ADCSR is set to 1, according to software or external trigger input.

- 2. When A/D conversion is completed, the result is transferred to the corresponding A/D data register to the channel.

- 3. On completion of conversion, the ADF bit in ADCSR is set to 1. If the ADIE bit is set to 1 at this time, an ADI interrupt request is generated.

- 4. The ADST bit remains set to 1 during A/D conversion. When A/D conversion ends, the ADST bit is automatically cleared to 0 and the A/D converter enters the wait state.

#### 14.4.2 Scan Mode

In scan mode, A/D conversion is performed sequentially for the analog input on the specified channels (four channels maximum) as follows:

- 1. When the ADST bit is set to 1 by software, or external trigger input, A/D conversion starts on the first channel in the group.

- 2. When A/D conversion for each channel is completed, the result is sequentially transferred to the A/D data register corresponding to each channel.

- 3. When conversion of all the selected channels is completed, the ADF flag in ADCSR is set to 1. If the ADIE bit is set to 1 at this time, an ADI interrupt is requested. Conversion of the first channel in the group starts again.

- 4. The ADST bit is not automatically cleared to 0. Steps [2] to [3] are repeated as long as the ADST bit remains set to 1. When the ADST bit is cleared to 0, A/D conversion stops.

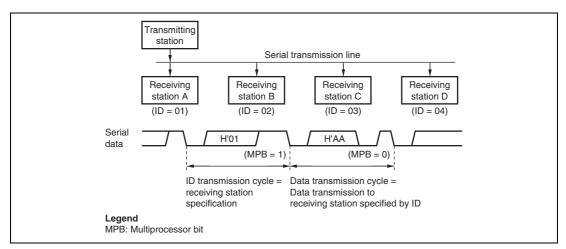

### 15.3.2 Low-Voltage Detection Circuit

# (1) LVDR (Reset by Low Voltage Detect) Circuit

Figure 15.3 shows the timing of the LVDR function. The LVDR enters the module-standby state after a power-on reset is canceled. To operate the LVDR, set the LVDE bit in LVDCR to 1, wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc., then set the LVDRE bit in LVDCR to 1. After that, the output settings of ports must be made. To cancel the low-voltage detection circuit, first the LVDRE bit should be cleared to 0 and then the LVDE bit should be cleared to 0. The LVDE and LVDRE bits must not be cleared to 0 simultaneously because incorrect operation may occur.

When the power-supply voltage falls below the Vreset voltage (typ. = 2.3 V or 3.6 V), the LVDR clears the  $\overline{LVDRES}$  signal to 0, and resets the prescaler S. The low-voltage detection reset state remains in place until a power-on reset is generated. When the power-supply voltage rises above the Vreset voltage again, the prescaler S starts counting. It counts 131,072 clock ( $\phi$ ) cycles, and then releases the internal reset signal. In this case, the LVDE, LVDSEL, and LVDRE bits in LVDCR are not initialized.

Note that if the power supply voltage (Vcc) falls below  $V_{LVDRmin} = 1.0$  V and then rises from that point, the low-voltage detection reset may not occur.

If the power supply voltage (Vcc) falls below Vpor = 100 mV, a power-on reset occurs.

Figure 15.3 Operational Timing of LVDR Circuit

|                                        |                 |                                                                                                                                                                                               |                                                                          |                       | Value | s   |      |       |

|----------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|-------|-----|------|-------|

| Item                                   | Symbol          | Applicable Pins                                                                                                                                                                               | Test Condition                                                           | Min                   | Тур   | Max | Unit | Notes |

| Output<br>high<br>voltage              | V <sub>OH</sub> | P12 to P10,<br>P17 to P14,<br>P22 to P20,                                                                                                                                                     | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$<br>$-I_{OH} = 1.5 \text{ mA}$ |                       |       | _   | V    |       |

|                                        |                 | P57 to P50,<br>P76 to P70,<br>P84 to P80                                                                                                                                                      | -I <sub>OH</sub> = 0.1 mA                                                | V <sub>cc</sub> – 0.5 | _     | —   |      |       |

| Output<br>low<br>voltage               | V <sub>ol</sub> | P12 to P10,<br>P17 to P14,<br>P22 to P20,                                                                                                                                                     | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$<br>$I_{oL} = 1.6 \text{ mA}$  | _                     | —     | 0.6 | V    |       |

|                                        |                 | P57 to P50,<br>P76 to P70                                                                                                                                                                     | I <sub>oL</sub> = 0.4 mA                                                 | _                     | _     | 0.4 |      |       |

|                                        |                 | P84 to P80                                                                                                                                                                                    | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$<br>$I_{oL} = 20.0 \text{ mA}$ | _                     | _     | 1.5 | V    | _     |

|                                        |                 |                                                                                                                                                                                               | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$<br>$I_{oL} = 10.0 \text{ mA}$ | _                     | _     | 1.0 |      |       |

|                                        |                 |                                                                                                                                                                                               | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$<br>$I_{oL} = 1.6 \text{ mA}$  | _                     | —     | 0.4 |      |       |

|                                        |                 |                                                                                                                                                                                               | I <sub>oL</sub> = 0.4 mA                                                 | —                     | _     | 0.4 |      |       |

| Input/<br>output<br>leakage<br>current | I <sub>IL</sub> | OSC1, RES,<br>NMI, WKP0 to<br>WKP5,<br>IRQ0, IRQ3,<br>ADTRG, TRGV,<br>TMRIV, TMCIV,<br>FTCI, FTIOA to<br>FTIOD, RXD,<br>RXD_2, RXD_3* <sup>1</sup> ,<br>SCK3, SCK3_2,<br>SCK3_3* <sup>1</sup> | $V_{IN} = 0.5 V \text{ to}$<br>( $V_{CC} - 0.5 V$ )                      | _                     | _     | 1.0 | μΑ   | _     |

|                                        |                 | P12 to P10,<br>P17 to P14,<br>P22 to P20,<br>P57 to P50,<br>P76 to P70,<br>P84 to P80                                                                                                         | $V_{IN} = 0.5 V to$<br>( $V_{CC} - 0.5 V$ )                              | _                     | _     | 1.0 | μΑ   | _     |

|                                        |                 | PB3 to PB0                                                                                                                                                                                    | $V_{IN} = 0.5 \text{ V to}$<br>(AV <sub>cc</sub> - 0.5 V)                | —                     | _     | 1.0 | μA   |       |

RENESAS

# 3. Logic instructions

|     | Mnemonic          |           |     |    |      |           | ng I<br>Ler |      |          |        | )   |                                           |       |     |                |                |          |   | No. of<br>States <sup>*1</sup> |   |

|-----|-------------------|-----------|-----|----|------|-----------|-------------|------|----------|--------|-----|-------------------------------------------|-------|-----|----------------|----------------|----------|---|--------------------------------|---|

|     |                   |           | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @ aa | @(d, PC) | @ @ aa |     | Operation                                 |       | Con | с              | Normal         | Advanced |   |                                |   |

| AND | AND.B #xx:8, Rd   | B Operand | 2   | -  | -    | -         | -           | -    | -        | -      | · · | Rd8∧#xx:8 → Rd8                           | <br>_ | _   | N<br>↓         | z<br>≎         | V<br>0   | Ē | _                              | 2 |

| /   | AND.B Rs, Rd      | В         |     | 2  |      |           |             |      |          |        |     | $Rd8 \land Rs8 \rightarrow Rd8$           | _     | -   | ↓              | ↓              | 0        | - | 2                              | 2 |

|     | AND.W #xx:16, Rd  | w         | 4   |    |      |           |             |      |          |        |     | Rd16∧#xx:16 → Rd16                        | _     | _   | \$             | \$             | 0        | _ | 4                              | 4 |

|     | AND.W Rs, Rd      | w         |     | 2  |      |           |             |      |          |        |     | Rd16∧Rs16 $\rightarrow$ Rd16              | _     | _   | \$             | \$             | 0        | _ | 2                              | 2 |

|     | AND.L #xx:32, ERd | L         | 6   |    |      |           |             |      |          |        |     | ERd32 $\wedge$ #xx:32 $\rightarrow$ ERd32 | _     | _   | \$             | \$             | 0        | - | e                              | 6 |

|     | AND.L ERs, ERd    | L         |     | 4  |      |           |             |      |          |        |     | $ERd32 \land ERs32 \rightarrow ERd32$     | _     |     |                | - 4            |          |   |                                |   |

| OR  | OR.B #xx:8, Rd    | В         | 2   |    |      |           |             |      |          |        |     | $Rd8/#xx:8 \rightarrow Rd8$               | _     | —   | - + + 0 -      |                | - 2      |   |                                |   |

|     | OR.B Rs, Rd       | В         |     | 2  |      |           |             |      |          |        |     | Rd8/Rs8 $\rightarrow$ Rd8                 | _     | —   | \$             | \$             | 0        | — | 2                              | 2 |

|     | OR.W #xx:16, Rd   | W         | 4   |    |      |           |             |      |          |        |     | Rd16/#xx:16 → Rd16                        | —     | -   | \$             | \$             | 0        | - | 4                              | 4 |

|     | OR.W Rs, Rd       | W         |     | 2  |      |           |             |      |          |        |     | $Rd16/Rs16 \rightarrow Rd16$              | -     | -   | \$             | \$             | 0        | - | 2                              | 2 |

|     | OR.L #xx:32, ERd  | L         | 6   |    |      |           |             |      |          |        |     | $ERd32/#xx:32 \rightarrow ERd32$          | -     | —   | $\updownarrow$ | $\uparrow$     | 0        | — | 6                              | 6 |

|     | OR.L ERs, ERd     | L         |     | 4  |      |           |             |      |          |        |     | $ERd32/ERs32 \rightarrow ERd32$           | —     | —   | $\updownarrow$ | $\uparrow$     | 0        | — | 4                              | 4 |

| XOR | XOR.B #xx:8, Rd   | В         | 2   |    |      |           |             |      |          |        |     | $Rd8 \oplus \#xx: 8 \rightarrow Rd8$      | —     | —   | $\updownarrow$ | \$             | 0        | - | 2                              | 2 |

|     | XOR.B Rs, Rd      | В         |     | 2  |      |           |             |      |          |        |     | $Rd8 \oplus Rs8 \to Rd8$                  | —     | -   | $\updownarrow$ | \$             | 0        | - | 2                              | 2 |

|     | XOR.W #xx:16, Rd  | W         | 4   |    |      |           |             |      |          |        |     | $Rd16 \oplus #xx:16 \rightarrow Rd16$     | —     | —   | \$             | \$             | 0        | — | 4                              | 4 |

|     | XOR.W Rs, Rd      | W         |     | 2  |      |           |             |      |          |        |     | $Rd16 \oplus Rs16 \rightarrow Rd16$       | —     | —   | \$             | \$             | 0        | — | 2                              | 2 |

|     | XOR.L #xx:32, ERd | L         | 6   |    |      |           |             |      |          |        |     | $ERd32 \oplus \#xx:32 \to ERd32$          | —     | -   | $\updownarrow$ | $\updownarrow$ | 0        | — | 6                              | ô |

|     | XOR.L ERs, ERd    | L         |     | 4  |      |           |             |      |          |        |     | $ERd32{\oplus}ERs32 \to ERd32$            | _     | -   | $\updownarrow$ | ↕              | 0        | - | 4                              | 4 |

| NOT | NOT.B Rd          | В         |     | 2  |      |           |             |      |          |        |     | $\neg$ Rd8 $\rightarrow$ Rd8              | —     | —   | ↕              | ↕              | 0        | - | 2                              | 2 |

|     | NOT.W Rd          | W         |     | 2  |      |           |             |      |          |        |     | $\neg$ Rd16 $\rightarrow$ Rd16            | -     | -   | ↕              | ↕              | 0        | - | 2                              | 2 |

|     | NOT.L ERd         | L         |     | 2  |      |           |             |      |          |        |     | $\neg$ Rd32 $\rightarrow$ Rd32            | -     |     | $\updownarrow$ | $\updownarrow$ | 0        | - | 2                              | 2 |

# 5. Bit manipulation instructions

|      |                   |              |     |    |      | essi<br>tion |             |     |          | nd<br>/tes | ) |                                          |                |   |   |        |          |    | No.<br>Stat |   |

|------|-------------------|--------------|-----|----|------|--------------|-------------|-----|----------|------------|---|------------------------------------------|----------------|---|---|--------|----------|----|-------------|---|

|      | Mnemonic          | Operand Size | XX# | Rn | @ERn | @(d, ERn)    | @-ERn/@ERn+ | @aa | @(d, PC) | @ @aa      | I | Operation                                | Condition Code |   | с | Normal | Advanced |    |             |   |

| BSET | BSET #xx:3, Rd    | в            |     | 2  |      |              |             |     |          |            |   | (#xx:3 of Rd8) ← 1                       | -              | - | — | —      | —        | -  | 2           | 2 |

|      | BSET #xx:3, @ERd  | В            |     |    | 4    |              |             |     |          |            |   | (#xx:3 of @ERd) ← 1                      | -              | — | — | —      | —        | -  | 8           | 3 |

|      | BSET #xx:3, @aa:8 | В            |     |    |      |              |             | 4   |          |            |   | (#xx:3 of @aa:8) ← 1                     | -              | — | — | —      | —        | -  | 8           | 3 |

|      | BSET Rn, Rd       | В            |     | 2  |      |              |             |     |          |            |   | (Rn8 of Rd8) ← 1                         | -              | — | — | —      | —        | -  | 2           | 2 |

|      | BSET Rn, @ERd     | В            |     |    | 4    |              |             |     |          |            |   | (Rn8 of @ERd) ← 1                        | -              | — | — | —      | —        | —  | 6           | 3 |

|      | BSET Rn, @aa:8    | В            |     |    |      |              |             | 4   |          |            |   | (Rn8 of @aa:8) ← 1                       | —              | — | — | —      | —        | —  | 8           | 3 |

| BCLR | BCLR #xx:3, Rd    | В            |     | 2  |      |              |             |     |          |            |   | (#xx:3 of Rd8) ← 0                       | —              | — | — | —      | —        | —  | 2           | 2 |

|      | BCLR #xx:3, @ERd  | В            |     |    | 4    |              |             |     |          |            |   | (#xx:3 of @ERd) ← 0                      | -              | — | — | —      | —        | —  | 8           | 3 |

|      | BCLR #xx:3, @aa:8 | В            |     |    |      |              |             | 4   |          |            |   | (#xx:3 of @aa:8) ← 0                     | -              | _ | — | —      | —        | —  | 8           | 3 |

|      | BCLR Rn, Rd       | В            |     | 2  |      |              |             |     |          |            |   | (Rn8 of Rd8) ← 0                         | -              | _ | _ | —      | -        | -  | 2           | 2 |

|      | BCLR Rn, @ERd     | В            |     |    | 4    |              |             |     |          |            |   | (Rn8 of @ERd) ← 0                        | -              | _ | _ | —      | _        | _  | 8           | 3 |

|      | BCLR Rn, @aa:8    | В            |     |    |      |              |             | 4   |          |            |   | (Rn8 of @aa:8) ← 0                       | -              | _ | _ | —      | _        | —  | 8           | 3 |

| BNOT | BNOT #xx:3, Rd    | В            |     | 2  |      |              |             |     |          |            |   | (#xx:3 of Rd8) ←<br>¬ (#xx:3 of Rd8)     | -              | - | - | -      | -        | -  | 2           | 2 |

|      | BNOT #xx:3, @ERd  | В            |     |    | 4    |              |             |     |          |            |   | (#xx:3 of @ERd) ←<br>¬ (#xx:3 of @ERd)   | -              | - | — | -      | -        | -  | 8           | 3 |

|      | BNOT #xx:3, @aa:8 | В            |     |    |      |              |             | 4   |          |            |   | (#xx:3 of @aa:8) ←<br>¬ (#xx:3 of @aa:8) | -              | - | — | -      | -        | -  | 8           | 3 |

|      | BNOT Rn, Rd       | В            |     | 2  |      |              |             |     |          |            |   | (Rn8 of Rd8) ←<br>¬ (Rn8 of Rd8)         | -              | - | — | -      | -        | -  | 2           | 2 |

|      | BNOT Rn, @ERd     | В            |     |    | 4    |              |             |     |          |            |   | (Rn8 of @ERd) ←<br>¬ (Rn8 of @ERd)       | -              | - | — | —      | -        | -  | 8           | 3 |

|      | BNOT Rn, @aa:8    | В            |     |    |      |              |             | 4   |          |            |   | (Rn8 of @aa:8) ←<br>¬ (Rn8 of @aa:8)     | -              | - | - | —      | _        | -  | 8           | 3 |

| BTST | BTST #xx:3, Rd    | В            |     | 2  |      |              |             |     |          |            |   | ¬ (#xx:3 of Rd8) → Z                     | -              | - | — | \$     | -        | -  | 2           | 2 |

|      | BTST #xx:3, @ERd  | В            |     |    | 4    |              |             |     |          |            |   | ¬ (#xx:3 of @ERd) → Z                    | -              | - | — | \$     | -        | -  | 6           | 3 |

|      | BTST #xx:3, @aa:8 | В            |     |    |      |              |             | 4   |          |            |   | ¬ (#xx:3 of @aa:8) → Z                   | -              | - | — | \$     | _        | -  | 6           | 3 |

|      | BTST Rn, Rd       | В            |     | 2  |      |              |             |     |          |            |   | ¬ (Rn8 of @Rd8) → Z                      | -              | - | _ | \$     | _        | -  | 2           | 2 |

|      | BTST Rn, @ERd     | в            |     |    | 4    |              |             |     |          |            |   | ¬ (Rn8 of @ERd) → Z                      | -              | - | _ | \$     | _        | -  | 6           | 3 |

|      | BTST Rn, @aa:8    | в            |     |    |      |              |             | 4   |          |            |   | ¬ (Rn8 of @aa:8) → Z                     | -              | - | _ | \$     | _        | -  | 6           | 3 |

| BLD  | BLD #xx:3, Rd     | В            |     | 2  |      |              |             |     |          |            |   | (#xx:3 of Rd8) $\rightarrow$ C           | -              | _ | _ | _      | _        | \$ | 2           | 2 |

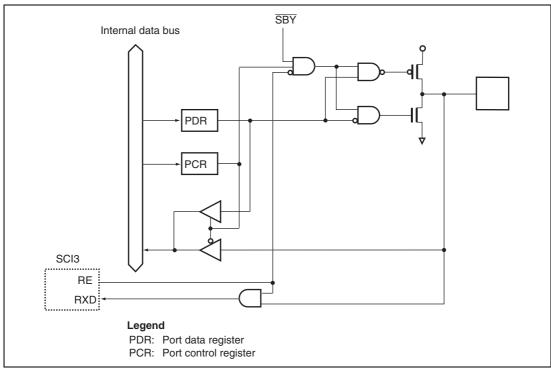

Figure B.7 Port 2 Block Diagram (P21)

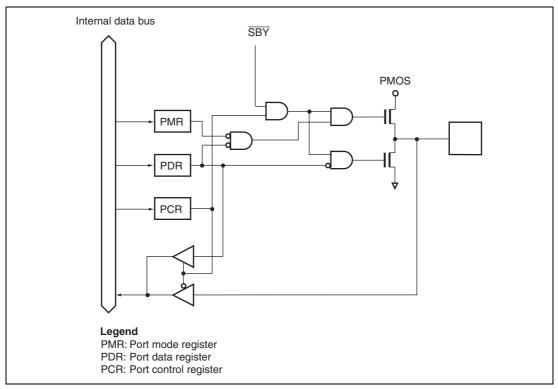

Figure B.9 Port 5 Block Diagram (P57, P56) (H8/36014)

| Product Ty | уре        |                    | Product Code  | Model Marking      | Package Code     |

|------------|------------|--------------------|---------------|--------------------|------------------|

| H8/36010   | Masked ROM | Standard           | HD64336010FP  | HD64336010(***)FP  | LQFP-64 (FP-64E) |

|            | version    | product            | HD64336010FX  | HD64336010(***)FX  | LQFP-48 (FP-48F) |

|            |            |                    | HD64336010FY  | HD64336010(***)FY  | LQFP-48 (FP-48B) |

|            |            |                    | HD64336010FT  | HD64336010(***)FT  | QFN-48(TNP-48)   |

|            |            | Product            | HD64336010GFP | HD64336010G(***)FP | LQFP-64 (FP-64E) |

|            |            | with POR<br>& LVDC | HD64336010GFX | HD64336010G(***)FX | LQFP-48 (FP-48F) |

|            |            | a 2000             | HD64336010GFY | HD64336010G(***)FY | LQFP-48 (FP-48B) |

|            |            |                    | HD64336010GFT | HD64336010G(***)FT | QFN-48(TNP-48)   |

### Legend

POR & LVDC: Power-on reset and low-voltage detection circuits

(\*\*\*): ROM code

| Item                                                 | Page | Revision             | (See Ma         | anual for Detai                                                    | ls)                           |                     |

|------------------------------------------------------|------|----------------------|-----------------|--------------------------------------------------------------------|-------------------------------|---------------------|

| Section 12 Watchdog<br>Timer                         | 168  | Bit Bi               | it Name         | Descriptio                                                         | n                             |                     |

| 12.2.1 Timer Control/Status<br>Register WD (TCSRWD)  |      | 4 T(                 | CSRWE           |                                                                    | rol/Status Registe            | r WD                |

| Section 14 A/D Converter                             | 220  |                      |                 |                                                                    | should be done by             |                     |

| 14.3.1 A/D Data Registers<br>A to D (ADDRA to ADDRD) |      |                      |                 | t then the lowe<br>initialized to H                                | r one. Word acces<br>'0000.   | ss is also          |

| Section 18 Electrical<br>Characteristics             | 254  |                      |                 |                                                                    |                               | Values              |

| Table 18.2 DC<br>Characteristics (1)                 |      | Item                 | Symbol          | Applicable Pins                                                    | Test Condition                | Min                 |

|                                                      |      | Input high           | $V_{\rm IH}$    | PB3 to PB0                                                         | $V_{cc}$ = 4.0 V to 5.5 V     | $V_{cc} \times 0.7$ |

|                                                      |      | voltage              |                 |                                                                    |                               | $V_{cc} \times 0.8$ |

|                                                      |      | Input low<br>voltage | V <sub>IL</sub> | RXD, RXD_2,<br>RXD_3* <sup>1</sup> ,<br>P12 to P10,<br>P17 to P14, | $\rm V_{cc}$ = 4.0 V to 5.5 V | -0.3                |

|                                                      |      |                      |                 | :<br>PB3 to PB0                                                    |                               |                     |

|                                                      |      |                      |                 |                                                                    |                               |                     |

| Table 18.2 DC                                        | 257  |                      |                 |                                                                    |                               |                     |

| Characteristics (1)                                  |      | Mode                 |                 | <b>RES</b> Pin                                                     | Internal State                |                     |

|                                                      |      | Active mo            | ode 1           | V <sub>cc</sub>                                                    | Operates                      |                     |

|                                                      |      | Active mo            | ode 2           |                                                                    | Operates<br>(¢OSC/64)         |                     |

|                                                      |      | Sleep mo             | de 1            | V <sub>cc</sub>                                                    | Only timers oper              | ate                 |

|                                                      |      | Sleep mo             | ode 2           |                                                                    | Only timers oper<br>(¢OSC/64) | ate                 |

|                                                      |      |                      |                 |                                                                    |                               |                     |