Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LFQFP (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36022gfyv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Preface

The H8/36024 Group and H8/36014 Group are single-chip microcomputers made up of the high-speed H8/300H CPU employing Renesas Technology original architecture as their cores, and the peripheral functions required to configure a system. The H8/300H CPU has an instruction set that is compatible with the H8/300 CPU.

- Target Users: This manual was written for users who will be using the H8/36024 Group and H8/36014 Group in the design of application systems. Target users are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

- Objective: This manual was written to explain the hardware functions and electrical characteristics of the H8/36024 Group and H8/36014 Group to the target users. Refer to the H8/300H Series Software Manual for a detailed description of the instruction set.

Notes on reading this manual:

- In order to understand the overall functions of the chip Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

- In order to understand the details of the CPU's functions Read the H8/300H Series Software Manual.

- In order to understand the details of a register when its name is known Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 17, List of Registers.

Example: Bit order: The MSB is on the left and the LSB is on the right.

Notes:

When using the on-chip emulator (E7, E8) for H8/36014 program development and debugging, the following restrictions must be noted.

- 1. The  $\overline{\text{NMI}}$  pin is reserved for the E7 or E8, and cannot be used.

- 2. Area H'7000 to H'7FFF is used by the E7 or E8, and is not available to the user.

- 3. Area H'F780 to H'FB7F must on no account be accessed.

Rev. 4.00 Sep. 23, 2005 Page viii of xxvi

|                                                               | 3.2.4                                                                                                                                 | Interrupt Flag Register 1 (IRR1)                                                                                                                                                                                                                                                                                                                                   | . 50                                                                                      |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                                                               | 3.2.5                                                                                                                                 | Wakeup Interrupt Flag Register (IWPR)                                                                                                                                                                                                                                                                                                                              | . 51                                                                                      |

| 3.3                                                           | Reset                                                                                                                                 | Exception Handling                                                                                                                                                                                                                                                                                                                                                 | . 52                                                                                      |

| 3.4                                                           | Interr                                                                                                                                | upt Exception Handling                                                                                                                                                                                                                                                                                                                                             | . 53                                                                                      |

|                                                               | 3.4.1                                                                                                                                 | External Interrupts                                                                                                                                                                                                                                                                                                                                                | . 53                                                                                      |

|                                                               | 3.4.2                                                                                                                                 | Internal Interrupts                                                                                                                                                                                                                                                                                                                                                | . 54                                                                                      |

|                                                               | 3.4.3                                                                                                                                 | Interrupt Handling Sequence                                                                                                                                                                                                                                                                                                                                        | . 55                                                                                      |

|                                                               | 3.4.4                                                                                                                                 | Interrupt Response Time                                                                                                                                                                                                                                                                                                                                            | . 56                                                                                      |

| 3.5                                                           | Usage                                                                                                                                 | Notes                                                                                                                                                                                                                                                                                                                                                              | . 58                                                                                      |

|                                                               | 3.5.1                                                                                                                                 | Interrupts after Reset                                                                                                                                                                                                                                                                                                                                             | . 58                                                                                      |

|                                                               | 3.5.2                                                                                                                                 | Notes on Stack Area Use                                                                                                                                                                                                                                                                                                                                            | . 58                                                                                      |

|                                                               | 3.5.3                                                                                                                                 | Notes on Rewriting Port Mode Registers                                                                                                                                                                                                                                                                                                                             | . 58                                                                                      |

| Secti                                                         | on 4                                                                                                                                  | Address Break                                                                                                                                                                                                                                                                                                                                                      | 59                                                                                        |

| 4.1                                                           | Regist                                                                                                                                | ter Descriptions                                                                                                                                                                                                                                                                                                                                                   | . 59                                                                                      |

|                                                               | 4.1.1                                                                                                                                 | Address Break Control Register (ABRKCR)                                                                                                                                                                                                                                                                                                                            | . 60                                                                                      |

|                                                               | 4.1.2                                                                                                                                 | Address Break Status Register (ABRKSR)                                                                                                                                                                                                                                                                                                                             | . 61                                                                                      |

|                                                               | 4.1.3                                                                                                                                 | Break Address Registers (BARH, BARL)                                                                                                                                                                                                                                                                                                                               | . 62                                                                                      |

|                                                               | 4.1.4                                                                                                                                 | Break Data Registers (BDRH, BDRL)                                                                                                                                                                                                                                                                                                                                  | . 62                                                                                      |

| 4.2                                                           | Opera                                                                                                                                 | tion                                                                                                                                                                                                                                                                                                                                                               | . 62                                                                                      |

|                                                               |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                           |

| Secti                                                         | on 5                                                                                                                                  | Clock Pulse Generators                                                                                                                                                                                                                                                                                                                                             | 65                                                                                        |

| Secti<br>5.1                                                  |                                                                                                                                       | Clock Pulse Generatorsn Clock Generator                                                                                                                                                                                                                                                                                                                            |                                                                                           |

|                                                               |                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                    | . 65                                                                                      |

|                                                               | Syster                                                                                                                                | n Clock Generator                                                                                                                                                                                                                                                                                                                                                  | . 65<br>. 66                                                                              |

|                                                               | Syster<br>5.1.1                                                                                                                       | n Clock Generator<br>Connecting Crystal Resonator                                                                                                                                                                                                                                                                                                                  | . 65<br>. 66<br>. 66                                                                      |

|                                                               | Syster<br>5.1.1<br>5.1.2<br>5.1.3                                                                                                     | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator                                                                                                                                                                                                                                                                                  | . 65<br>. 66<br>. 66<br>. 67                                                              |

| 5.1                                                           | Syster<br>5.1.1<br>5.1.2<br>5.1.3                                                                                                     | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method                                                                                                                                                                                                                                                   | . 65<br>. 66<br>. 66<br>. 67<br>. 67                                                      |

| 5.1                                                           | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1                                                                                  | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method                                                                                                                                                                                                                                                   | . 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67                                              |

| <ul><li>5.1</li><li>5.2</li></ul>                             | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1                                                                                  | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Prescaler S                                                                                                                                                                                                                                    | . 65<br>. 66<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67                                      |

| <ul><li>5.1</li><li>5.2</li></ul>                             | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage                                                                         | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S                                                                                                                                                                                                                           | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                                      |

| <ul><li>5.1</li><li>5.2</li></ul>                             | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6                                               | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S<br>Notes<br>Notes on Resonators<br>Notes on Board Design<br>Power-Down Modes                                                                                                                                              | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68<br>69                        |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                 | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6                                               | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Prescaler S<br>Notes<br>Note on Resonators<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>ter Descriptions                                                                                                              | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68<br><b>69</b><br>. 69 |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6                                               | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S<br>Notes<br>Notes on Resonators<br>Notes on Board Design<br>Power-Down Modes                                                                                                                                              | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68<br><b>69</b><br>. 69 |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6<br>Regist                                     | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Prescaler S<br>Notes<br>Note on Resonators<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>ter Descriptions                                                                                                              | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                      |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>con 6<br>Regiss<br>6.1.1                           | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>Nets<br>Prescaler S<br>Notes<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>System Control Register 1 (SYSCR1)                                                                                                          | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 68<br>. 69<br>. 70<br>. 71      |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6<br>Regiss<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4 | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S<br>Notes<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>ter Descriptions<br>System Control Register 1 (SYSCR1)<br>System Control Register 2 (SYSCR2)<br>Module Standby Control Register 1 (MSTCR1) | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                      |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Section</li></ul> | Syster<br>5.1.1<br>5.1.2<br>5.1.3<br>Presca<br>5.2.1<br>Usage<br>5.3.1<br>5.3.2<br>on 6<br>Regiss<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4 | n Clock Generator<br>Connecting Crystal Resonator<br>Connecting Ceramic Resonator<br>External Clock Input Method<br>llers<br>Prescaler S<br>Notes<br>Note on Resonators<br>Notes on Board Design<br>Power-Down Modes<br>ter Descriptions<br>System Control Register 1 (SYSCR1)<br>System Control Register 2 (SYSCR2)<br>Module Standby Control Register 1 (MSTCR1) | . 65<br>. 66<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67<br>. 67                      |

### 3.5 Usage Notes

#### 3.5.1 Interrupts after Reset

If an interrupt is accepted after a reset and before the stack pointer (SP) is initialized, the PC and CCR will not be saved correctly, leading to a program crash. To prevent this, all interrupt requests, including NMI, are disabled immediately after a reset. Since the first instruction of a program is always executed immediately after the reset state ends, make sure that this instruction initializes the stack pointer (example: MOV.W #xx: 16, SP).

#### 3.5.2 Notes on Stack Area Use

When word data is accessed, the least significant bit of the address is regarded as 0. Access to the stack always takes place in word size, so the stack pointer (SP: R7) should never indicate an odd address. Use PUSH Rn (MOV.W Rn, @–SP) or POP Rn (MOV.W @SP+, Rn) to save or restore register values.

#### 3.5.3 Notes on Rewriting Port Mode Registers

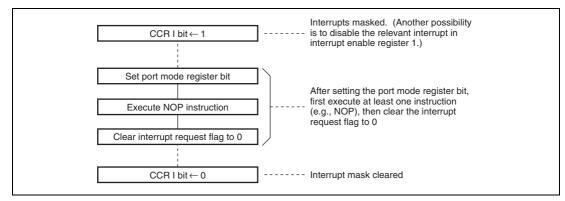

When a port mode register is rewritten to switch the functions of external interrupt pins,  $\overline{\text{IRQ3}}$ ,  $\overline{\text{IRQ0}}$ , and  $\overline{\text{WKP5}}$  to  $\overline{\text{WKP0}}$ , the interrupt request flag may be set to 1.

Figure 3.4 shows a port mode register setting and interrupt request flag clearing procedure.

When switching a pin function, mask the interrupt before setting the bit in the port mode register. After accessing the port mode register, execute at least one instruction (e.g., NOP), then clear the interrupt request flag from 1 to 0.

Figure 3.4 Port Mode Register Setting and Interrupt Request Flag Clearing Procedure

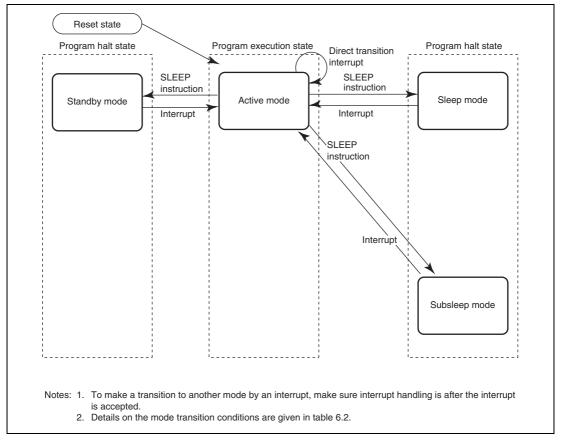

### 6.2 Mode Transitions and States of LSI

Figure 6.1 shows the possible transitions among these operating modes. A transition is made from the program execution state to the program halt state of the program by executing a SLEEP instruction. Interrupts allow for returning from the program halt state to the program execution state of the program. A direct transition from active mode to active mode changes the operating frequency.  $\overline{\text{RES}}$  input enables transitions from a mode to the reset state. Table 6.2 shows the transition conditions of each mode after the SLEEP instruction is executed and a mode to return by an interrupt. Table 6.3 shows the internal states of the LSI in each mode.

Figure 6.1 Mode Transition Diagram

The FLMCR1, FLMCR2, and EBR1 settings are retained, however program mode or erase mode is aborted at the point at which the error occurred. Program mode or erase mode cannot be reentered by re-setting the P or E bit. However, PV and EV bit setting is enabled, and a transition can be made to verify mode. Error protection can be cleared only by a reset.

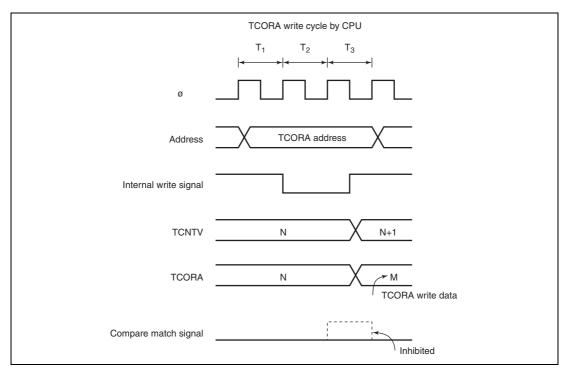

Figure 10.12 Contention between TCORA Write and Compare Match

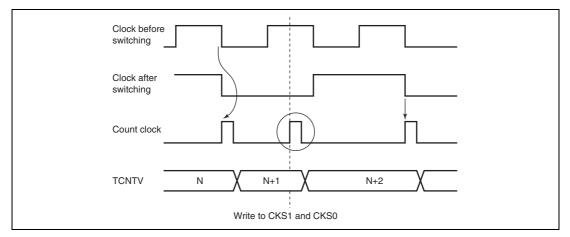

Figure 10.13 Internal Clock Switching and TCNTV Operation

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                    |

|-----|----------|------------------|-----|----------------------------------------------------------------|

| 1   | IOA1     | 0                | R/W | I/O Control A1 and A0                                          |

| 0   | IOA0     | 0                | R/W | When IOA2 = 0,                                                 |

|     |          |                  |     | 00: No output at compare match                                 |

|     |          |                  |     | 01: 0 output to the FTIOA pin at GRA compare match             |

|     |          |                  |     | 10: 1 output to the FTIOA pin at GRA compare match             |

|     |          |                  |     | 11: Output toggles to the FTIOA pin at GRA compare<br>match    |

|     |          |                  |     | When IOA2 = 1,                                                 |

|     |          |                  |     | 00: Input capture at rising edge of the FTIOA pin              |

|     |          |                  |     | 01: Input capture at falling edge of the FTIOA pin             |

|     |          |                  |     | 1X: Input capture at rising and falling edges of the FTIOA pin |

Legend X: Don't care.

### 11.3.6 Timer I/O Control Register 1 (TIOR1)

TIOR1 selects the functions of GRC and GRD, and specifies the functions of the FTIOC and FTIOD pins.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                    |

|-----|----------|------------------|-----|------------------------------------------------|

| 7   | —        | 1                | —   | Reserved                                       |

|     |          |                  |     | This bit is always read as 1.                  |

| 6   | IOD2     | 0                | R/W | I/O Control D2                                 |

|     |          |                  |     | Selects the GRD function.                      |

|     |          |                  |     | 0: GRD functions as an output compare register |

|     |          |                  |     | 1: GRD functions as an input capture register  |

#### 11.3.7 Timer Counter (TCNT)

TCNT is a 16-bit readable/writable up-counter. The clock source is selected by bits CKS2 to CKS0 in TCRW. TCNT can be cleared to H'0000 through a compare match with GRA by setting the CCLR in TCRW to 1. When TCNT overflows (changes from H'FFFF to H'0000), the OVF flag in TSRW is set to 1. If OVIE in TIERW is set to 1 at this time, an interrupt request is generated. TCNT must always be read or written in 16-bit units; 8-bit access is not allowed. TCNT is initialized to H'0000 by a reset.

#### 11.3.8 General Registers A to D (GRA to GRD)

Each general register is a 16-bit readable/writable register that can function as either an outputcompare register or an input-capture register. The function is selected by settings in TIOR0 and TIOR1.

When a general register is used as an input-compare register, its value is constantly compared with the TCNT value. When the two values match (a compare match), the corresponding flag (IMFA, IMFB, IMFC, or IMFD) in TSRW is set to 1. An interrupt request is generated at this time, when IMIEA, IMIEB, IMIEC, or IMIED is set to 1. Compare match output can be selected in TIOR.

When a general register is used as an input-capture register, an external input-capture signal is detected and the current TCNT value is stored in the general register. The corresponding flag (IMFA, IMFB, IMFC, or IMFD) in TSRW is set to 1. If the corresponding interrupt-enable bit (IMIEA, IMIEB, IMIEC, or IMIED) in TSRW is set to 1 at this time, an interrupt request is generated. The edge of the input-capture signal is selected in TIOR.

GRC and GRD can be used as buffer registers of GRA and GRB, respectively, by setting BUFEA and BUFEB in TMRW.

For example, when GRA is set as an output-compare register and GRC is set as the buffer register for GRA, the value in the buffer register GRC is sent to GRA whenever compare match A is generated.

When GRA is set as an input-capture register and GRC is set as the buffer register for GRA, the value in TCNT is transferred to GRA and the value in the buffer register GRC is transferred to GRA whenever an input capture is generated.

GRA to GRD must be written or read in 16-bit units; 8-bit access is not allowed. GRA to GRD are initialized to H'FFFF by a reset.

### 11.5.2 Output Compare Output Timing

The compare match signal is generated in the last state in which TCNT and GR match (when TCNT changes from the matching value to the next value). When the compare match signal is generated, the output value selected in TIOR is output at the compare match output pin (FTIOA, FTIOB, FTIOC, or FTIOD).

When TCNT matches GR, the compare match signal is generated only after the next counter clock pulse is input.

Figure 11.16 shows the output compare timing.

| φ                    |         |  |

|----------------------|---------|--|

| TCNT input<br>clock  |         |  |

| TCNT                 | N X N+1 |  |

| GRA to GRD           | Ν       |  |

| Compare match signal |         |  |

| FTIOA to FTIOD       | χ       |  |

Figure 11.16 Output Compare Output Timing

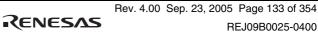

5. The TOA to TOD bits in TCRW decide the value of the FTIO pin, which is output until the first compare match occurs. Once a compare match occurs and this compare match changes the values of FTIOA to FTIOD output, the values of the FTIOA to FTIOD pin output and the values read from the TOA to TOD bits may differ. Moreover, when the writing to TCRW and the generation of the compare match A to D occur at the same timing, the writing to TCRW has the priority. Thus, output change due to the compare match is not reflected to the FTIOA to FTIOD pins. Therefore, when bit manipulation instruction is used to write to TCRW, the values of the FTIOA to FTIOD pin output may result in an unexpected result. When TCRW is to be written to while compare match is operating, stop the counter once before accessing to TCRW, read the port 8 state to reflect the values of FTIOA to FTIOD output, to TOA to TOD, and then restart the counter. Figure 11.26 shows an example when the compare match and the bit manipulation instruction to TCRW occur at the same timing.

Figure 11.26 When Compare Match and Bit Manipulation Instruction to TCRW Occur at the Same Timing

#### 13.3.7 Serial Status Register (SSR)

SSR is a register containing status flags of the SCI3 and multiprocessor bits for transfer. 1 cannot be written to flags TDRE, RDRF, OER, PER, and FER; they can only be cleared.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                 |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------|

| 7   | TDRE     | 1                | R/W | Transmit Data Register Empty                                                                                |

|     |          |                  |     | Indicates whether TDR contains transmit data.                                                               |

|     |          |                  |     | [Setting conditions]                                                                                        |

|     |          |                  |     | When the TE bit in SCR3 is 0                                                                                |

|     |          |                  |     | When data is transferred from TDR to TSR                                                                    |

|     |          |                  |     | [Clearing conditions]                                                                                       |

|     |          |                  |     | <ul> <li>When 0 is written to TDRE after reading TDRE = 1</li> </ul>                                        |

|     |          |                  |     | When the transmit data is written to TDR                                                                    |

| 6   | RDRF     | 0                | R/W | Receive Data Register Full                                                                                  |

|     |          |                  |     | Indicates that the received data is stored in RDR.                                                          |

|     |          |                  |     | [Setting condition]                                                                                         |

|     |          |                  |     | <ul> <li>When serial reception ends normally and receive data<br/>is transferred from RSR to RDR</li> </ul> |

|     |          |                  |     | [Clearing conditions]                                                                                       |

|     |          |                  |     | • When 0 is written to RDRF after reading RDRF = 1                                                          |

|     |          |                  |     | When data is read from RDR                                                                                  |

| 5   | OER      | 0                | R/W | Overrun Error                                                                                               |

|     |          |                  |     | [Setting condition]                                                                                         |

|     |          |                  |     | When an overrun error occurs in reception                                                                   |

|     |          |                  |     | [Clearing condition]                                                                                        |

|     |          |                  |     | • When 0 is written to OER after reading OER = 1                                                            |

| 4   | FER      | 0                | R/W | Framing Error                                                                                               |

|     |          |                  |     | [Setting condition]                                                                                         |

|     |          |                  |     | When a framing error occurs in reception                                                                    |

|     |          |                  |     | [Clearing condition]                                                                                        |

|     |          |                  |     | • When 0 is written to FER after reading FER = 1                                                            |

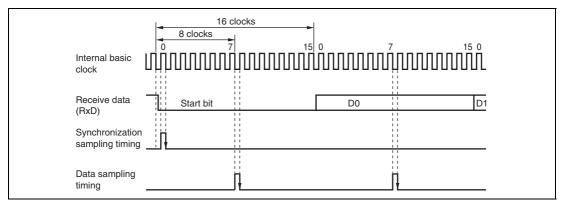

#### 13.8.4 Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

In asynchronous mode, the SCI3 operates on a basic clock with a frequency of 16 times the transfer rate. In reception, the SCI3 samples the falling edge of the start bit using the basic clock, and performs internal synchronization. Receive data is latched internally at the rising edge of the 8th pulse of the basic clock as shown in figure 13.19. Thus, the reception margin in asynchronous mode is given by formula (1) below.

$$M = \left\{ (0.5 - \frac{1}{2N}) - \frac{D - 0.5}{N} - (L - 0.5) F \right\} \times 100(\%)$$

... Formula (1)

[Legend\

N: Ratio of bit rate to clock (N = 16)

D: Clock duty (D = 0.5 to 1.0)

L: Frame length (L = 9 to 12)

F: Absolute value of clock rate deviation

Assuming values of F (absolute value of clock rate deviation) = 0 and D (clock duty) = 0.5 in formula (1), the reception margin can be given by the formula.

$M = \{0.5 - 1/(2 \times 16)\} \times 100 \ [\%] = 46.875\%$

However, this is only the computed value, and a margin of 20% to 30% should be allowed for in system design.

Figure 13.19 Receive Data Sampling Timing in Asynchronous Mode

## 14.2 Input/Output Pins

Table 14.1 summarizes the input pins used by the A/D converter.

#### Table 14.1 Pin Configuration

| Pin Name                       | Symbol    | I/O   | Function                                               |

|--------------------------------|-----------|-------|--------------------------------------------------------|

| Analog power supply pin        | $AV_{cc}$ | Input | Analog block power supply pin                          |

| Analog input pin 0             | AN0       | Input | Analog input pins                                      |

| Analog input pin 1             | AN1       | Input |                                                        |

| Analog input pin 2             | AN2       | Input |                                                        |

| Analog input pin 3             | AN3       | Input |                                                        |

| A/D external trigger input pin | ADTRG     | Input | External trigger input pin for starting A/D conversion |

# Section 18 Electrical Characteristics

### 18.1 Absolute Maximum Ratings

#### Table 18.1 Absolute Maximum Ratings

| Item                                  |        | Symbol          | Value                       | Unit | Note |

|---------------------------------------|--------|-----------------|-----------------------------|------|------|

| Power supply voltage                  | 9      | V <sub>cc</sub> | –0.3 to +7.0                | V    | *    |

| Analog power supply voltage           |        | $AV_{cc}$       | -0.3 to +7.0                | V    | _    |

| Input voltage Ports other than Port B |        | V <sub>IN</sub> | –0.3 to V $_{\rm cc}$ +0.3  | V    | _    |

|                                       | Port B | _               | –0.3 to AV $_{\rm cc}$ +0.3 | V    | _    |

| Operating temperatu                   | re     | $T_{_{opr}}$    | -20 to +75                  | °C   | _    |

| Storage temperature                   |        | $T_{stg}$       | –55 to +125                 | °C   |      |

Note: \* Permanent damage may result if maximum ratings are exceeded. Normal operation should be under the conditions specified in Electrical Characteristics. Exceeding these values can result in incorrect operation and reduced reliability.

### **18.2** Electrical Characteristics (F-ZTAT<sup>TM</sup> Version)

#### 18.2.1 Power Supply Voltage and Operating Ranges

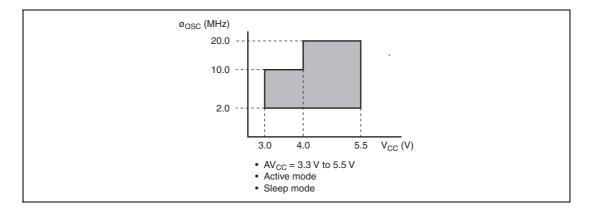

#### (1) Power Supply Voltage and Oscillation Frequency Range

### 18.2.6 Flash Memory Characteristics

#### Table 18.7 Flash Memory Characteristics

$V_{cc}$  = 3.0 V to 5.5 V,  $V_{ss}$  = 0.0 V,  $T_a$  = -20°C to +75°C, unless otherwise specified.

| Item           |                                                                  |                  | Test<br>Condition          |      | Values | ;    | Unit  |

|----------------|------------------------------------------------------------------|------------------|----------------------------|------|--------|------|-------|

|                |                                                                  | Symbol           |                            | Min  | Тур    | Max  |       |

| Programming t  | time (per 128 bytes)* <sup>1</sup> * <sup>2</sup> * <sup>4</sup> | t <sub>P</sub>   |                            | _    | 7      | 200  | ms    |

| Erase time (pe | r block) * <sup>1</sup> * <sup>3</sup> * <sup>6</sup>            | t <sub>e</sub>   |                            | _    | 100    | 1200 | ms    |

| Reprogrammin   | ng count                                                         | $N_{\text{wec}}$ |                            | 1000 | 10000  | —    | Times |

| Programming    | Wait time after SWE bit setting*1                                | x                |                            | 1    | _      | _    | μs    |

|                | Wait time after PSU bit setting*1                                | у                |                            | 50   | _      | _    | μs    |

|                | Wait time after P bit setting                                    | z1               | $1 \le n \le 6$            | 28   | 30     | 32   | μs    |

|                | *1*4                                                             | z2               | $7 \le n \le 1000$         | 198  | 200    | 202  | μs    |

|                |                                                                  | z3               | Additional-<br>programming | 8    | 10     | 12   | μs    |

|                | Wait time after P bit clear*1                                    | α                |                            | 5    | —      | _    | μs    |

|                | Wait time after PSU bit clear*1                                  | β                |                            | 5    | —      | —    | μs    |

|                | Wait time after PV bit setting*1                                 | γ                |                            | 4    | —      | —    | μs    |

|                | Wait time after<br>dummy write* <sup>1</sup>                     | ε                |                            | 2    | _      | _    | μs    |

|                | Wait time after PV bit clear*1                                   | η                |                            | 2    | —      | —    | μs    |

|                | Wait time after SWE bit clear*1                                  | θ                |                            | 100  | _      | _    | μs    |

|                | Maximum<br>programming count*1*4*5                               | Ν                |                            | _    | _      | 1000 | Times |

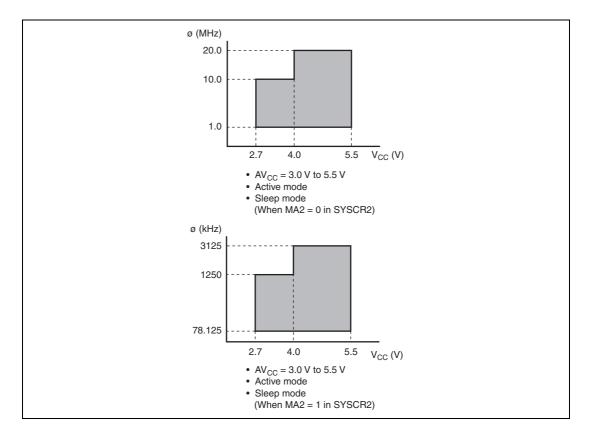

#### (2) Power Supply Voltage and Operating Frequency Range

#### 18.3.6 Power-Supply-Voltage Detection Circuit Characteristics (Optional)

#### Table 18.15 Power-Supply-Voltage Detection Circuit Characteristics

$V_{ss} = 0.0 \text{ V}, T_a = -20 \text{ to } +75^{\circ}\text{C}$ , unless otherwise indicated.

|                                                     |                         | Test                                                                               |     | Value | S   |      |

|-----------------------------------------------------|-------------------------|------------------------------------------------------------------------------------|-----|-------|-----|------|

| Item                                                | Symbol                  | Condition                                                                          | Min | Тур   | Max | Unit |

| Power-supply falling detection voltage              | Vint (D)                | LVDSEL = 0                                                                         | 3.3 | 3.7   | _   | V    |

| Power-supply rising detection voltage               | Vint (U)                | LVDSEL = 0                                                                         | —   | 4.0   | 4.5 | V    |

| Reset detection voltage 1*1                         | Vreset1                 | LVDSEL = 0                                                                         | —   | 2.3   | 2.7 | V    |

| Reset detection voltage 2* <sup>2</sup>             | Vreset2                 | LVDSEL = 1                                                                         | 3.0 | 3.6   | 4.2 | V    |

| Lower-limit voltage of LVDR operation* <sup>3</sup> | $V_{_{\text{LVDRmin}}}$ |                                                                                    | 1.0 | —     | —   | V    |

| LVD stabilization time                              | t <sub>lvdon</sub>      |                                                                                    | 50  | _     | _   | μs   |

| Current consumption in standby mode                 | I <sub>stby</sub>       | LVDE = 1,<br>Vcc = 5.0 V,<br>When a 32-<br>kHz crystal<br>resonator is<br>not used |     | _     | 350 | μΑ   |

Notes: 1. This voltage should be used when the falling and rising voltage detection function is used.

2. Select the low-voltage reset 2 when only the low-voltage detection reset is used.

When the power-supply voltage (Vcc) falls below V<sub>LVDRmin</sub> = 1.0 V and then rises, a reset may not occur. Therefore sufficient evaluation is required.