Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | •                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36024gfxv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# 16

## H8/36024Group, H8/36014Group

## Hardware Manual

### Renesas 16-Bit Single-Chip Microcomputer H8 Family/H8/300H Tiny Series

H8/36024F H8/36022F H8/36014F H8/36012F H8/36024 H8/36023 H8/36022 H8/36014 H8/36013 H8/36012 H8/36011

#### H8/36010 Renesas Electronics

www.renesas.com

Rev.4.00 2005.09

HD64F36024, HD64F36024G,

HD64F36022, HD64F36022G,

HD64F36014, HD64F36014G, HD64F36012G,

HD64336024, HD64336024G,

HD64336023, HD64336023G,

HD64336022, HD64336022G,

HD64336014, HD64336014G, HD64336013G,

HD64336012, HD64336012G,

HD64336011, HD64336011G,

HD64336010, HD64336010G

| Instruction | Size | Function        |                                                        |                                 |

|-------------|------|-----------------|--------------------------------------------------------|---------------------------------|

| Bcc*        | —    |                 | specified address if a sp<br>litions are listed below. | pecified condition is true. The |

|             |      | Mnemonic        | Description                                            | Condition                       |

|             |      | BRA(BT)         | Always (true)                                          | Always                          |

|             |      | BRN(BF)         | Never (false)                                          | Never                           |

|             |      | BHI             | High                                                   | $C \lor Z = 0$                  |

|             |      | BLS             | Low or same                                            | C ∨ Z = 1                       |

|             |      | BCC(BHS)        | Carry clear<br>(high or same)                          | C = 0                           |

|             |      | BCS(BLO)        | Carry set (low)                                        | C = 1                           |

|             |      | BNE             | Not equal                                              | Z = 0                           |

|             |      | BEQ             | Equal                                                  | Z = 1                           |

|             |      | BVC             | Overflow clear                                         | V = 0                           |

|             |      | BVS             | Overflow set                                           | V = 1                           |

|             |      | BPL             | Plus                                                   | N = 0                           |

|             |      | BMI             | Minus                                                  | N = 1                           |

|             |      | BGE             | Greater or equal                                       | $N \oplus V = 0$                |

|             |      | BLT             | Less than                                              | $N \oplus V = 1$                |

|             |      | BGT             | Greater than                                           | $Z \lor (N \oplus V) = 0$       |

|             |      | BLE             | Less or equal                                          | $Z \lor (N \oplus V) = 1$       |

|             |      |                 |                                                        |                                 |

| JMP         |      | Branches unco   | nditionally to a specified                             | address.                        |

| BSR         | —    | Branches to a s | subroutine at a specified                              | d address.                      |

| JSR         |      | Branches to a s | subroutine at a specified                              | d address.                      |

| RTS         | _    | Returns from a  | subroutine                                             |                                 |

RENESAS

#### Table 2.7 Branch Instructions

Note: \* Bcc is the general name for conditional branch instructions.

#### 3.2.2 Interrupt Edge Select Register 2 (IEGR2)

IEGR2 selects the direction of an edge that generates interrupt requests of the pins  $\overline{\text{ADTRG}}$  and  $\overline{\text{WKP5}}$  to  $\overline{\text{WKP0}}$ .

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                       |

|------|----------|------------------|-----|-----------------------------------------------------------------------------------|

| 7, 6 |          | All 1            |     | Reserved                                                                          |

|      |          |                  |     | These bits are always read as 1.                                                  |

| 5    | WPEG5    | 0                | R/W | WKP5 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP5}$ ( $\overline{ADTRG}$ ) pin input is detected |

|      |          |                  |     | 1: Rising edge of $\overline{WKP5}$ ( $\overline{ADTRG}$ ) pin input is detected  |

| 4    | WPEG4    | 0                | R/W | WKP4 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP4}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of $\overline{WKP4}$ pin input is detected                         |

| 3    | WPEG3    | 0                | R/W | WKP3 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP3}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP3 pin input is detected                                      |

| 2    | WPEG2    | 0                | R/W | WKP2 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP2}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP2 pin input is detected                                      |

| 1    | WPEG1    | 0                | R/W | WKP1Edge Select                                                                   |

|      |          |                  |     | 0: Falling edge of $\overline{WKP1}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of $\overline{WKP1}$ pin input is detected                         |

| 0    | WPEG0    | 0                | R/W | WKP0 Edge Select                                                                  |

|      |          |                  |     | 0: Falling edge of $\overline{WKP0}$ pin input is detected                        |

|      |          |                  |     | 1: Rising edge of WKP0 pin input is detected                                      |

#### Section 4 Address Break

The address break simplifies on-board program debugging. It requests an address break interrupt when the set break condition is satisfied. The interrupt request is not affected by the I bit of CCR. Break conditions that can be set include instruction execution at a specific address and a combination of access and data at a specific address. With the address break function, the execution start point of a program containing a bug is detected and execution is branched to the correcting program. Figure 4.1 shows a block diagram of the address break.

Figure 4.1 Block Diagram of Address Break

#### 4.1 **Register Descriptions**

Address break has the following registers.

- Address break control register (ABRKCR)

- Address break status register (ABRKSR)

- Break address register (BARH, BARL)

#### 7.2.3 Erase Block Register 1 (EBR1)

EBR1 specifies the flash memory erase area block. EBR1 is initialized to H'00 when the SWE bit in FLMCR1 is 0. Do not set more than one bit at a time, as this will cause all the bits in EBR1 to be automatically cleared to 0.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                              |

|--------|----------|------------------|-----|--------------------------------------------------------------------------|

| 7 to 5 | _        | All 0            | _   | Reserved                                                                 |

|        |          |                  |     | These bits are always read as 0.                                         |

| 4      | EB4      | 0                | R/W | When this bit is set to 1, 28 kbytes of H'1000 to H'7FFF will be erased. |

| 3      | EB3      | 0                | R/W | When this bit is set to 1, 1 kbyte of H'0C00 to H'0FFF will be erased.   |

| 2      | EB2      | 0                | R/W | When this bit is set to 1, 1 kbyte of H'0800 to H'0BFF will be erased.   |

| 1      | EB1      | 0                | R/W | When this bit is set to 1, 1 kbyte of H'0400 to H'07FF will be erased.   |

| 0      | EB0      | 0                | R/W | When this bit is set to 1, 1 kbyte of H'0000 to H'03FF will be erased.   |

#### 7.2.4 Flash Memory Enable Register (FENR)

Bit 7 (FLSHE) in FENR enables or disables the CPU access to the flash memory control registers, FLMCR1, FLMCR2, and EBR1.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                  |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | FLSHE    | 0                | R/W | Flash Memory Control Register Enable                                                                                                                         |

|        |          |                  |     | Flash memory control registers can be accessed when<br>this bit is set to 1. Flash memory control registers cannot<br>be accessed when this bit is set to 0. |

| 6 to 0 |          | All 0            | _   | Reserved                                                                                                                                                     |

|        |          |                  |     | These bits are always read as 0.                                                                                                                             |

#### 9.3.3 Port Data Register 5 (PDR5)

| Bit | Bit Name | Initial<br>Value | R/W                                                     | Description                                                                       |  |  |  |

|-----|----------|------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| 7   | P57      | 0                | R/W                                                     | Stores output data for port 5 pins.                                               |  |  |  |

| 6   | P56      | 0                | R/W                                                     | If PDR5 is read while PCR5 bits are set to 1, the value                           |  |  |  |

| 5   | P55      | 0                | R/W stored in PDR5 are read. If PDR5 is read while PCR5 |                                                                                   |  |  |  |

| 4   | P54      | 0                | R/W                                                     | are cleared to 0, the pin states are read regardless of the value stored in PDR5. |  |  |  |

| 3   | P53      | 0                | R/W                                                     |                                                                                   |  |  |  |

| 2   | P52      | 0                | R/W                                                     |                                                                                   |  |  |  |

| 1   | P51      | 0                | R/W                                                     |                                                                                   |  |  |  |

| 0   | P50      | 0                | R/W                                                     |                                                                                   |  |  |  |

PDR5 is a general I/O port data register of port 5.

#### 9.3.4 Port Pull-Up Control Register 5 (PUCR5)

PUCR5 controls the pull-up MOS in bit units of the pins set as the input ports.

| Bit  | Bit Name | Initial<br>Value | R/W | Description                                                                                                           |

|------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------|

| 7, 6 | —        | All 0            | _   | Reserved                                                                                                              |

|      |          |                  |     | These bits are always read as 0.                                                                                      |

| 5    | PUCR55   | 0                | R/W | Only bits for which PCR5 is cleared are valid. The pull-up                                                            |

| 4    | PUCR54   | 0                | R/W | MOS of the corresponding pins enter the on-state when<br>these bits are set to 1, while they enter the off-state when |

| 3    | PUCR53   | 0                | R/W | these bits are cleared to 0.                                                                                          |

| 2    | PUCR52   | 0                | R/W |                                                                                                                       |

| 1    | PUCR51   | 0                | R/W |                                                                                                                       |

| 0    | PUCR50   | 0                | R/W |                                                                                                                       |

| ø                       |   |    |     |  |

|-------------------------|---|----|-----|--|

| TCNTV                   | Ν | _X | N+1 |  |

| TCORA or<br>TCORB       | Ν |    |     |  |

| Compare match<br>signal |   |    |     |  |

| CMFA or                 |   |    |     |  |

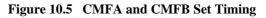

Figure 10.7 Clear Timing by Compare Match

#### 12.2.3 Timer Mode Register WD (TMWD)

TMWD selects the input clock.

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                               |

|--------|----------|------------------|-----|-------------------------------------------------------------------------------------------|

| 7 to 4 | _        | All 1            |     | Reserved                                                                                  |

|        |          |                  |     | These bits are always read as 1.                                                          |

| 3      | CKS3     | 1                | R/W | Clock Select 3 to 0                                                                       |

| 2      | CKS2     | 1                | R/W | Select the clock to be input to TCWD.                                                     |

| 1      | CKS1     | 1                | R/W | 1000: Internal clock: counts on $\phi/64$                                                 |

| 0      | CKS0     | 1                | R/W | 1001: Internal clock: counts on $\phi/128$                                                |

|        |          |                  |     | 1010: Internal clock: counts on $\phi/256$                                                |

|        |          |                  |     | 1011: Internal clock: counts on $\phi/512$                                                |

|        |          |                  |     | 1100: Internal clock: counts on $\phi/1024$                                               |

|        |          |                  |     | 1101: Internal clock: counts on $\phi/2048$                                               |

|        |          |                  |     | 1110: Internal clock: counts on $\phi/4096$                                               |

|        |          |                  |     | 1111: Internal clock: counts on $\phi$ 8192                                               |

|        |          |                  |     | 0XXX: Internal oscillator                                                                 |

|        |          |                  |     | For the internal oscillator overflow periods, see section 18, Electrical Characteristics. |

Legend X: Don't care.

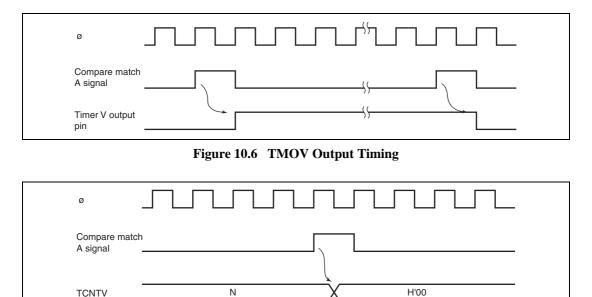

Figure 13.8 Sample Serial Reception Data Flowchart (Asynchronous Mode)(2)

|                            |                   | CKS = 0 |     |     | CKS = 1 |     |     |

|----------------------------|-------------------|---------|-----|-----|---------|-----|-----|

| Item                       | Symbol            | Min     | Тур | Max | Min     | Тур | Max |

| A/D conversion start delay | t <sub>D</sub>    | 6       |     | 9   | 4       | —   | 5   |

| Input sampling time        | t <sub>spl</sub>  | _       | 31  |     |         | 15  | _   |

| A/D conversion time        | t <sub>conv</sub> | 131     |     | 134 | 69      | _   | 70  |

#### Table 14.3 A/D Conversion Time (Single Mode)

Note: All values represent the number of states.

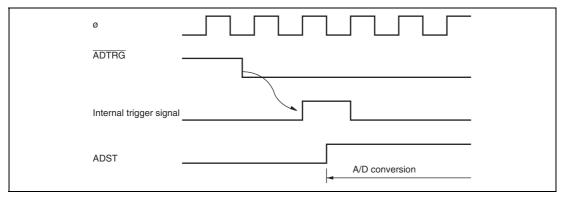

#### 14.4.4 External Trigger Input Timing

A/D conversion can also be started by an external trigger input. When the TRGE bit is set to 1 in ADCR, external trigger input is enabled at the  $\overline{\text{ADTRG}}$  pin. A falling edge at the  $\overline{\text{ADTRG}}$  input pin sets the ADST bit to 1 in ADCSR, starting A/D conversion. Other operations, in both single and scan modes, are the same as when the bit ADST has been set to 1 by software. Figure 14.3 shows the timing.

Figure 14.3 External Trigger Input Timing

#### 14.5 A/D Conversion Accuracy Definitions

This LSI's A/D conversion accuracy definitions are given below.

Resolution

The number of A/D converter digital output codes

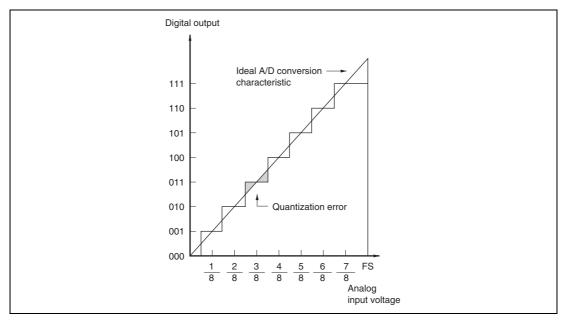

• Quantization error

The deviation inherent in the A/D converter, given by 1/2 LSB (see figure 14.4).

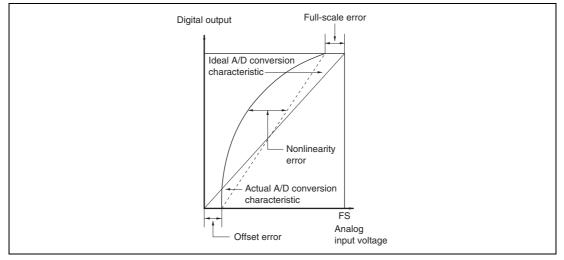

Offset error

The deviation of the analog input voltage value from the ideal A/D conversion characteristic when the digital output changes from the minimum voltage value 00000000000 to 0000000001 (see figure 14.5).

• Full-scale error

The deviation of the analog input voltage value from the ideal A/D conversion characteristic when the digital output changes from 1111111110 to 111111111 (see figure 14.5).

• Nonlinearity error

The error with respect to the ideal A/D conversion characteristics between zero voltage and full-scale voltage. Does not include offset error, full-scale error, or quantization error.

• Absolute accuracy

The deviation between the digital value and the analog input value. Includes offset error, full-scale error, quantization error, and nonlinearity error.

Figure 14.5 A/D Conversion Accuracy Definitions (2)

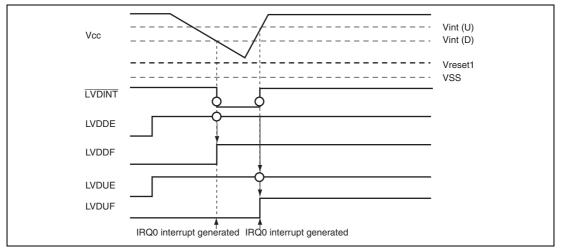

#### (2) LVDI (Interrupt by Low Voltage Detect) Circuit

Figure 15.4 shows the timing of LVDI functions. The LVDI enters the module-standby state after a power-on reset is canceled. To operate the LVDI, set the LVDE bit in LVDCR to 1, wait for 50  $\mu$ s (t<sub>LVDON</sub>) until the reference voltage and the low-voltage-detection power supply have stabilized by a software timer, etc., then set the LVDDE and LVDUE bits in LVDCR to 1. After that, the output settings of ports must be made. To cancel the low-voltage detection circuit, first the LVDDE and LVDUE bits should all be cleared to 0 and then the LVDDE bit should be cleared to 0. The LVDE bit must not be cleared to 0 at the same timing as the LVDDE and LVDUE bits because incorrect operation may occur.

When the power-supply voltage falls below Vint (D) (typ. = 3.7 V) voltage, the LVDI clears the  $\overline{\text{LVDINT}}$  signal to 0 and the LVDDF bit in LVDSR is set to 1. If the LVDDE bit is 1 at this time, an IRQ0 interrupt request is simultaneously generated. In this case, the necessary data must be saved in the external EEPROM, etc, and a transition must be made to standby mode or subsleep mode. Until this processing is completed, the power supply voltage must be higher than the lower limit of the guaranteed operating voltage.

When the power-supply voltage does not fall below Vreset1 (typ. = 2.3 V) voltage but rises above Vint (U) (typ. = 4.0 V) voltage, the LVDI sets the  $\overline{LVDINT}$  signal to 1. If the LVDUE bit is 1 at this time, the LVDUF bit in LVDSR is set to 1 and an IRQ0 interrupt request is simultaneously generated.

If the power supply voltage (Vcc) falls below Vreset1 (typ. = 2.3 V) voltage, the LVDR function is performed.

Figure 15.4 Operational Timing of LVDI Circuit

#### 18.3.2 DC Characteristics

#### Table 18.10 DC Characteristics (1)

$V_{cc} = 2.7$  V to 5.5 V,  $V_{ss} = 0.0$  V,  $T_a = -20^{\circ}$ C to +75°C, unless otherwise specified.

|                       |                 |                                                                                   |                                            |                      | Value | s                     |      |       |

|-----------------------|-----------------|-----------------------------------------------------------------------------------|--------------------------------------------|----------------------|-------|-----------------------|------|-------|

| Item                  | Symbol          | Applicable Pins                                                                   | Test Condition                             | Min                  | Тур   | Max                   | Unit | Notes |

| Input high<br>voltage | V <sub>IH</sub> | RES, NMI<br>WKP0 to WKP5,<br>IRQ0, IRQ3,<br>ADTRG,TMRIV,                          | $V_{\rm cc}$ = 4.0 V to 5.5 V              | $V_{cc} \times 0.8$  | _     | V <sub>cc</sub> + 0.3 | V    |       |

|                       |                 | TMCIV, FTCI,<br>FTIOA to FTIOD,<br>SCK3, SCK3_2,<br>SCK3_3* <sup>1</sup> , TRGV   |                                            | V <sub>cc</sub> ×0.9 | _     | V <sub>cc</sub> + 0.3 | _    |       |

|                       |                 | RXD, RXD_2,<br>RXD_3* <sup>1</sup> ,<br>P12 to P10,<br>P17 to P14,<br>P22 to P20, | $V_{\rm cc}$ = 4.0 V to 5.5 V              | $V_{cc} \times 0.7$  |       | V <sub>cc</sub> + 0.3 | V    | _     |

|                       |                 | P57 to P50,<br>P76 to P70,<br>P84 to P80                                          |                                            | V <sub>cc</sub> ×0.8 | —     | V <sub>cc</sub> + 0.3 | _    |       |

|                       |                 | PB3 to PB0                                                                        | $V_{\rm cc}$ = 4.0 V to 5.5 V              | $V_{cc} 	imes 0.7$   | _     | $AV_{cc} + 0.3$       | V    | -     |

|                       |                 |                                                                                   |                                            | $V_{cc} 	imes 0.8$   |       | $AV_{cc} + 0.3$       | _    |       |

|                       |                 | OSC1                                                                              | $V_{\rm cc}$ = 4.0 V to 5.5 V              | $V_{cc} - 0.5$       | —     | $V_{cc}$ + 0.3        | V    | _     |

|                       |                 |                                                                                   |                                            | $V_{\rm cc} - 0.3$   | _     | V <sub>cc</sub> + 0.3 | _    |       |

| Input low<br>voltage  | V <sub>IL</sub> | RES, NMI<br>WKP0 to WKP5,<br>IRQ0, IRQ3,<br>ADTRG,TMRIV,                          | $V_{\rm cc}$ = 4.0 V to 5.5 V              | -0.3                 | —     | $V_{cc} \times 0.2$   | V    |       |

|                       |                 | TMCIV, FTCI,<br>FTIOA to FTIOD,<br>SCK3, SCK3_2,<br>SCK3_3* <sup>1</sup> , TRGV   |                                            | -0.3                 | _     | V <sub>cc</sub> ×0.1  | -    |       |

|                       |                 | RXD, RXD_2,<br>RXD_3* <sup>1</sup> ,<br>P12 to P10,<br>P17 to P14,<br>P22 to P20, | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$ | -0.3                 | _     | $V_{cc} \times 0.3$   | V    | _     |

|                       |                 | P57 to P50,<br>P76 to P70,<br>P84 to P80<br>PB3 to PB0                            |                                            | -0.3                 |       | $V_{cc} \times 0.2$   |      | _     |

|                       |                 | OSC1                                                                              | $V_{\rm cc}$ = 4.0 V to 5.5 V              | -0.3                 | _     | 0.5                   | V    |       |

|                       |                 |                                                                                   |                                            | -0.3                 | _     | 0.3                   |      |       |

RENESAS

|                                                |                     |                                               |                                                                 |      | Value | s     |      |                                      |

|------------------------------------------------|---------------------|-----------------------------------------------|-----------------------------------------------------------------|------|-------|-------|------|--------------------------------------|

| Item                                           | Symbol              | Applicable Pins                               | Test Condition                                                  | Min  | Тур   | Мах   | Unit | Notes                                |

| Pull-up<br>MOS                                 | −I <sub>p</sub>     | P12 to P10,<br>P17 to P14,                    | $V_{cc} = 5.0 \text{ V},$<br>$V_{IN} = 0.0 \text{ V}$           | 50.0 |       | 300.0 | μΑ   |                                      |

| current                                        |                     | P55 to P50                                    | $V_{cc} = 3.0 \text{ V},$<br>$V_{IN} = 0.0 \text{ V}$           | _    | 60.0  | —     |      | Reference value                      |

| Input<br>capaci-<br>tance                      | C <sub>in</sub>     | All input pins<br>except power<br>supply pins | f = 1 MHz,<br>V <sub>IN</sub> = 0.0 V,<br>T <sub>a</sub> = 25°C | —    | _     | 15.0  | pF   |                                      |

| Active<br>mode<br>current                      | I <sub>OPE1</sub>   | V <sub>cc</sub>                               | Active mode 1<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$       | —    | 15.0  | 30.0  | mA   | *2                                   |

| consump-<br>tion                               |                     |                                               | Active mode 1<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$       | _    | 8.0   | _     |      | * <sup>2</sup><br>Reference<br>value |

|                                                | I <sub>OPE2</sub>   | V <sub>cc</sub>                               | Active mode 2<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$       | _    | 1.8   | 3.0   | mA   | * <sup>2</sup>                       |

|                                                |                     |                                               | Active mode 2<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$       | —    | 1.2   | _     |      | * <sup>2</sup><br>Reference<br>value |

| Sleep<br>mode<br>current                       | I <sub>SLEEP1</sub> | V <sub>cc</sub>                               | Sleep mode 1<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$        | —    | 11.5  | 22.5  | mA   | *2                                   |

| consump-<br>tion                               |                     |                                               | Sleep mode 1<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$        | _    | 6.5   | _     |      | * <sup>2</sup><br>Reference<br>value |

|                                                | I <sub>SLEEP2</sub> | V <sub>cc</sub>                               | Sleep mode 2<br>$V_{cc} = 5.0 V$ ,<br>$f_{osc} = 20 MHz$        | _    | 1.7   | 2.7   | mA   | *2                                   |

|                                                |                     |                                               | Sleep mode 2<br>$V_{cc} = 3.0 V$ ,<br>$f_{osc} = 10 MHz$        | _    | 1.1   | _     |      | * <sup>2</sup><br>Reference<br>value |

| Standby<br>mode<br>current<br>consump-<br>tion | I <sub>stby</sub>   | V <sub>cc</sub>                               |                                                                 | _    | _     | 5.0   | μΑ   | *2                                   |

RENESAS

|          |                         |              | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |             |     |          |        |   |                                                                     |                            |          |        | No<br>Stat | . of<br>es <sup>*1</sup> |   |      |   |

|----------|-------------------------|--------------|---------------------------------------------------|----|------|-----------|-------------|-----|----------|--------|---|---------------------------------------------------------------------|----------------------------|----------|--------|------------|--------------------------|---|------|---|

| Mnemonic |                         | Operand Size | #xx                                               | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @ @ aa | 1 | Operation                                                           | 1                          | Con<br>H | Normal | Advanced   |                          |   |      |   |

| MOV      | MOV.W Rs, @-ERd         | w            |                                                   |    |      |           | 2           |     |          |        |   | ERd32–2 $\rightarrow$ ERd32<br>Rs16 $\rightarrow$ @ERd              | -                          | -        | \$     | \$         | 0                        | - | (    | 6 |

|          | MOV.W Rs, @aa:16        | w            |                                                   |    |      |           |             | 4   |          |        |   | Rs16 $\rightarrow$ @aa:16                                           | _                          | _        | \$     | \$         | 0                        | - | 6    | 6 |

|          | MOV.W Rs, @aa:24        | w            |                                                   |    |      |           |             | 6   |          |        |   | Rs16 $\rightarrow$ @aa:24                                           | _                          | -        | \$     | \$         | 0                        | - | 8    | 8 |

|          | MOV.L #xx:32, Rd        | L            | 6                                                 |    |      |           |             |     |          |        |   | #xx:32 → Rd32                                                       | _                          | -        | \$     | \$         | 0                        | - | (    | 6 |

|          | MOV.L ERs, ERd          | L            |                                                   | 2  |      |           |             |     |          |        |   | ERs32 $\rightarrow$ ERd32                                           | _                          | _        | \$     | \$         | 0                        | - | 1    | 2 |

|          | MOV.L @ERs, ERd         | L            |                                                   |    | 4    |           |             |     |          |        |   | @ERs $\rightarrow$ ERd32                                            | _                          | -        | \$     | \$         | 0                        | - | 8    | 8 |

|          | MOV.L @(d:16, ERs), ERd | L            |                                                   |    |      | 6         |             |     |          |        |   | @(d:16, ERs) → ERd32                                                | _                          | -        | \$     | \$         | 0                        | - | 1    | 0 |

|          | MOV.L @(d:24, ERs), ERd | L            |                                                   |    |      | 10        |             |     |          |        |   | @(d:24, ERs) → ERd32                                                | _                          | -        | \$     | \$         | 0                        | - | 1    | 4 |

|          | MOV.L @ERs+, ERd        | L            |                                                   |    |      |           | 4           |     |          |        |   | @ERs → ERd32<br>ERs32+4 → ERs32                                     | -                          | -        | \$     | \$         | 0                        | - | 1    | 0 |

|          | MOV.L @aa:16, ERd       | L            |                                                   |    |      |           |             | 6   |          |        |   | @aa:16 $\rightarrow$ ERd32                                          | _                          | -        | \$     | \$         | 0                        | - | 1    | 0 |

|          | MOV.L @aa:24, ERd       | L            |                                                   |    |      |           |             | 8   |          |        |   | @aa:24 $\rightarrow$ ERd32                                          | _                          | -        | \$     | \$         | 0                        | - | 1    | 2 |

|          | MOV.L ERs, @ERd         | L            |                                                   |    | 4    |           |             |     |          |        |   | $ERs32 \rightarrow @ERd$                                            | _                          | —        | \$     | \$         | 0                        | — | 8    | В |

|          | MOV.L ERs, @(d:16, ERd) | L            |                                                   |    |      | 6         |             |     |          |        |   | ERs32 $\rightarrow$ @(d:16, ERd)                                    | —                          | -        | \$     | \$         | 0                        | - | 1    | 0 |

|          | MOV.L ERs, @(d:24, ERd) | L            |                                                   |    |      | 10        |             |     |          |        |   | ERs32 $\rightarrow$ @(d:24, ERd)                                    | —                          | -        | \$     | \$         | 0                        | — | 1    | 4 |

|          | MOV.L ERs, @-ERd        | L            |                                                   |    |      |           | 4           |     |          |        |   | $\begin{array}{l} ERd32-4 \to ERd32 \\ ERs32 \to @ ERd \end{array}$ | -                          | -        | \$     | \$         | 0                        | - | 1    | 0 |

|          | MOV.L ERs, @aa:16       | L            |                                                   |    |      |           |             | 6   |          |        |   | ERs32 $\rightarrow$ @aa:16                                          | —                          | -        | \$     | \$         | 0                        | - | 1    | 0 |

|          | MOV.L ERs, @aa:24       | L            |                                                   |    |      |           |             | 8   |          |        |   | ERs32 $\rightarrow$ @aa:24                                          | —                          | -        | \$     | \$         | 0                        | - | 1    | 2 |

| POP      | POP.W Rn                | W            |                                                   |    |      |           |             |     |          |        | 2 | $\begin{array}{l} @ SP \to Rn16 \\ \\ SP+2 \to SP \end{array}$      | -                          | -        | \$     | \$         | 0                        | - | (    | 6 |

|          | POP.L ERn               | L            |                                                   |    |      |           |             |     |          |        | 4 | $\begin{array}{l} @ SP \to ERn32 \\ SP+4 \to SP \end{array}$        | -                          | -        | \$     | \$         | 0                        | - | 10   |   |

| PUSH     | PUSH.W Rn               | W            |                                                   |    |      |           |             |     |          |        | 2 | $SP-2 \rightarrow SP$<br>Rn16 $\rightarrow @SP$                     | _                          | -        | \$     | \$         | 0                        | - | - 6  |   |

|          | PUSH.L ERn              | L            |                                                   |    |      |           |             |     |          |        | 4 | $\begin{array}{l} SP\text{-}4 \to SP \\ ERn32 \to @SP \end{array}$  | -                          | -        | \$     | \$         | 0                        | - | - 10 |   |

| MOVFPE   | MOVFPE @aa:16, Rd       | В            |                                                   |    |      |           |             | 4   |          |        |   | Cannot be used in this LSI                                          | Cannot be used in this LSI |          |        |            |                          |   |      |   |

| MOVTPE   | MOVTPE Rs, @aa:16       | В            |                                                   |    |      |           |             | 4   |          |        |   | Cannot be used in this LSI                                          | Cannot be used in this LSI |          |        |            |                          |   |      |   |

|      |            |              |                                                                                                           |     | Addressing Mode and<br>Instruction Length (bytes) |      |           |             |     |          |     |   |                |                |                |                |                | No. of<br>States <sup>*1</sup> |   |    |

|------|------------|--------------|-----------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------|------|-----------|-------------|-----|----------|-----|---|----------------|----------------|----------------|----------------|----------------|--------------------------------|---|----|

|      | Mnemonic   | Operand Size | Operation                                                                                                 | ×   |                                                   | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @aa |   | Condition Code |                | Normal         | Advanced       |                |                                |   |    |

|      |            | ő            |                                                                                                           | XX# | Rn                                                | 0    | 0         | ġ           | 0   | 0        | 0   | Ι | Т              | н              | Ν              | z              | v              | с                              | Ŷ | Ad |

| NEG  | NEG.B Rd   | В            | $0-Rd8 \rightarrow Rd8$                                                                                   |     | 2                                                 |      |           |             |     |          |     |   | —              | $\updownarrow$ | $\updownarrow$ | $\uparrow$     | $\updownarrow$ | $\updownarrow$                 | 2 | 2  |

|      | NEG.W Rd   | W            | $0-Rd16 \rightarrow Rd16$                                                                                 |     | 2                                                 |      |           |             |     |          |     |   | —              | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$ | $\updownarrow$                 | 2 | 2  |

|      | NEG.L ERd  | L            | $0-ERd32 \rightarrow ERd32$                                                                               |     | 2                                                 |      |           |             |     |          |     |   | -              | \$             | \$             | \$             | $\updownarrow$ | $\updownarrow$                 | 2 | 2  |

| EXTU | EXTU.W Rd  | W            | $0 \rightarrow (\text{} \text{ of Rd16})$                                                                 |     | 2                                                 |      |           |             |     |          |     |   | -              | —              | 0              | €              | 0              | —                              | 2 | 2  |

|      | EXTU.L ERd | L            | $0 \rightarrow (< bits 31 to 16 > of ERd32)$                                                              |     | 2                                                 |      |           |             |     |          |     |   | -              | —              | 0              | \$             | 0              | —                              | 2 | 2  |

| EXTS | EXTS.W Rd  | W            | ( <bit 7=""> of Rd16) <math>\rightarrow</math><br/>(<bits 15="" 8="" to=""> of Rd16)</bits></bit>         |     | 2                                                 |      |           |             |     |          |     |   | —              | —              | \$             | \$             | 0              | —                              | 2 | 2  |

|      | EXTS.L ERd | L            | ( <bit 15=""> of ERd32) <math>\rightarrow</math><br/>(<bits 16="" 31="" to=""> of<br/>ERd32)</bits></bit> |     | 2                                                 |      |           |             |     |          |     |   |                |                | \$             | \$             | 0              |                                | 2 | 2  |

#### Appendix

| Instruction | Mnemonic           | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Byte Data<br>Access<br>L | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|--------------------|---------------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| Bcc         | BLT d:8            | 2                         |                           |                         |                          |                          |                            |

|             | BGT d:8            | 2                         |                           |                         |                          |                          |                            |

|             | BLE d:8            | 2                         |                           |                         |                          |                          |                            |

|             | BRA d:16(BT d:16)  | 2                         |                           |                         |                          |                          | 2                          |

|             | BRN d:16(BF d:16)  | 2                         |                           |                         |                          |                          | 2                          |

|             | BHI d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BLS d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BCC d:16(BHS d:16) | 2                         |                           |                         |                          |                          | 2                          |

|             | BCS d:16(BLO d:16) | 2                         |                           |                         |                          |                          | 2                          |

|             | BNE d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BEQ d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BVC d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BVS d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BPL d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BMI d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BGE d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BLT d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BGT d:16           | 2                         |                           |                         |                          |                          | 2                          |

|             | BLE d:16           | 2                         |                           |                         |                          |                          | 2                          |

| BCLR        | BCLR #xx:3, Rd     | 1                         |                           |                         |                          |                          |                            |

|             | BCLR #xx:3, @ERd   | 2                         |                           |                         | 2                        |                          |                            |

|             | BCLR #xx:3, @aa:8  | 2                         |                           |                         | 2                        |                          |                            |

|             | BCLR Rn, Rd        | 1                         |                           |                         |                          |                          |                            |

|             | BCLR Rn, @ERd      | 2                         |                           |                         | 2                        |                          |                            |

|             | BCLR Rn, @aa:8     | 2                         |                           |                         | 2                        |                          |                            |

| BIAND       | BIAND #xx:3, Rd    | 1                         |                           |                         |                          |                          |                            |

|             | BIAND #xx:3, @ERd  | 2                         |                           |                         | 1                        |                          |                            |

|             | BIAND #xx:3, @aa:8 | 2                         |                           |                         | 1                        |                          |                            |

| BILD        | BILD #xx:3, Rd     | 1                         |                           |                         |                          |                          |                            |

|             | BILD #xx:3, @ERd   | 2                         |                           |                         | 1                        |                          |                            |

|             | BILD #xx:3, @aa:8  | 2                         |                           |                         | 1                        |                          |                            |