Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LFQFP (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36024gfyv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                              | 13.4.2                                                                                                                                               | SCI3 Initialization                                                                                                                                                             | 193                                                                                                   |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                              | 13.4.3                                                                                                                                               | Data Transmission                                                                                                                                                               | 194                                                                                                   |

|                              | 13.4.4                                                                                                                                               | Serial Data Reception                                                                                                                                                           | 196                                                                                                   |

| 13.5                         | Operat                                                                                                                                               | ion in Clocked Synchronous Mode                                                                                                                                                 | 200                                                                                                   |

|                              | 13.5.1                                                                                                                                               | Clock                                                                                                                                                                           | 200                                                                                                   |

|                              | 13.5.2                                                                                                                                               | SCI3 Initialization                                                                                                                                                             | 201                                                                                                   |

|                              | 13.5.3                                                                                                                                               | Serial Data Transmission                                                                                                                                                        | 201                                                                                                   |

|                              | 13.5.4                                                                                                                                               | Serial Data Reception (Clocked Synchronous Mode)                                                                                                                                | 203                                                                                                   |

|                              | 13.5.5                                                                                                                                               | Simultaneous Serial Data Transmission and Reception                                                                                                                             | 205                                                                                                   |

| 13.6                         | Multip                                                                                                                                               | rocessor Communication Function                                                                                                                                                 | 207                                                                                                   |

|                              | 13.6.1                                                                                                                                               | Multiprocessor Serial Data Transmission                                                                                                                                         | 208                                                                                                   |

|                              | 13.6.2                                                                                                                                               | Multiprocessor Serial Data Reception                                                                                                                                            | 210                                                                                                   |

| 13.7                         | Interru                                                                                                                                              | pts                                                                                                                                                                             | 214                                                                                                   |

| 13.8                         | Usage                                                                                                                                                | Notes                                                                                                                                                                           | 215                                                                                                   |

|                              | 13.8.1                                                                                                                                               | Break Detection and Processing                                                                                                                                                  | 215                                                                                                   |

|                              | 13.8.2                                                                                                                                               | Mark State and Break Sending                                                                                                                                                    | 215                                                                                                   |

|                              | 13.8.3                                                                                                                                               | Receive Error Flags and Transmit Operations                                                                                                                                     |                                                                                                       |

|                              |                                                                                                                                                      | (Clocked Synchronous Mode Only)                                                                                                                                                 | 215                                                                                                   |

|                              |                                                                                                                                                      |                                                                                                                                                                                 |                                                                                                       |

|                              | 13.8.4                                                                                                                                               | Receive Data Sampling Timing and Reception Margin in Asynchronous                                                                                                               |                                                                                                       |

|                              | 13.8.4                                                                                                                                               | Receive Data Sampling Timing and Reception Margin in Asynchronous<br>Mode                                                                                                       | 216                                                                                                   |

|                              |                                                                                                                                                      | Mode                                                                                                                                                                            |                                                                                                       |

| Secti                        |                                                                                                                                                      |                                                                                                                                                                                 |                                                                                                       |

| Secti<br>14.1                | ion 14                                                                                                                                               | Mode                                                                                                                                                                            | 217                                                                                                   |

|                              | ion 14<br>Feature                                                                                                                                    | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217                                                                                            |

| 14.1                         | ion 14<br>Feature<br>Input/C                                                                                                                         | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217<br>219                                                                                     |

| 14.1<br>14.2                 | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1                                                                                                    | Mode<br>A/D Converter<br>es<br>Dutput Pins<br>er Description<br>A/D Data Registers A to D (ADDRA to ADDRD)                                                                      | 217<br>217<br>219<br>220<br>220                                                                       |

| 14.1<br>14.2                 | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1                                                                                                    | Mode<br>A/D Converter<br>ss.<br>Dutput Pins<br>er Description                                                                                                                   | 217<br>217<br>219<br>220<br>220                                                                       |

| 14.1<br>14.2                 | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2                                                                                          | Mode<br>A/D Converter<br>es<br>Dutput Pins<br>er Description<br>A/D Data Registers A to D (ADDRA to ADDRD)                                                                      | 217<br>217<br>219<br>220<br>220<br>221                                                                |

| 14.1<br>14.2                 | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3                                                                                | Mode         A/D Converter         cs         Dutput Pins         cr Description         A/D Data Registers A to D (ADDRA to ADDRD)         A/D Control/Status Register (ADCSR) | 217<br>217<br>219<br>220<br>220<br>221<br>221                                                         |

| 14.1<br>14.2<br>14.3         | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3                                                                                | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217<br>219<br>220<br>220<br>221<br>222<br>222<br>223                                           |

| 14.1<br>14.2<br>14.3         | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3<br>Operat<br>14.4.1                                                            | Mode<br>A/D Converter<br>Ss<br>Dutput Pins<br>er Description                                                                                                                    | 217<br>217<br>219<br>220<br>220<br>221<br>222<br>223<br>223                                           |

| 14.1<br>14.2<br>14.3         | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3<br>Operat:<br>14.4.1<br>14.4.2                                                 | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217<br>219<br>220<br>220<br>221<br>222<br>223<br>223<br>223                                    |

| 14.1<br>14.2<br>14.3         | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3<br>Operat:<br>14.4.1<br>14.4.2<br>14.4.3<br>14.4.3                             | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217<br>220<br>220<br>220<br>221<br>222<br>223<br>223<br>223<br>224<br>225                      |

| 14.1<br>14.2<br>14.3         | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3<br>Operat:<br>14.4.1<br>14.4.2<br>14.4.3<br>14.4.3                             | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217<br>220<br>220<br>220<br>221<br>222<br>223<br>223<br>223<br>224<br>225                      |

| 14.1<br>14.2<br>14.3         | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3<br>Operat<br>14.4.1<br>14.4.2<br>14.4.3<br>14.4.3<br>14.4.4<br>A/D Co          | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217<br>219<br>220<br>220<br>221<br>222<br>223<br>223<br>223<br>223<br>223<br>224<br>225<br>226 |

| 14.1<br>14.2<br>14.3<br>14.4 | ion 14<br>Feature<br>Input/C<br>Registe<br>14.3.1<br>14.3.2<br>14.3.3<br>Operat<br>14.4.1<br>14.4.2<br>14.4.3<br>14.4.3<br>14.4.4<br>A/D Co<br>Usage | Mode<br>A/D Converter                                                                                                                                                           | 217<br>217<br>219<br>220<br>220<br>221<br>222<br>223<br>223<br>223<br>224<br>224<br>226<br>228        |

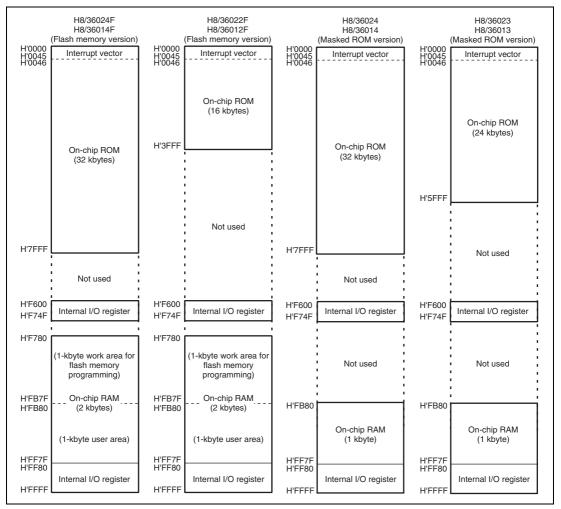

## 2.1 Address Space and Memory Map

The address space of this LSI is 64 kbytes, which includes the program area and the data area. Figures 2.1 show the memory maps.

Figure 2.1 Memory Map (1)

RENESAS

### (2) Bit Manipulation in a Register Containing a Write-Only Bit

### Example 3: BCLR instruction executed designating port 5 control register PCR5

P57 and P56 are input pins, with a low-level signal input at P57 and a high-level signal input at P56. P55 to P50 are output pins that output low-level signals. An example of setting the P50 pin as an input pin by the BCLR instruction is shown below. It is assumed that a high-level signal will be input to this input pin.

• Prior to executing BCLR

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50          |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Input/output | Input        | Input         | Output       | Output       | Output       | Output       | Output       | Output       |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level |

| PCR5         | 0            | 0             | 1            | 1            | 1            | 1            | 1            | 1            |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0            |

### BCLR instruction executed

| BCLR #0, @PCR5 |

|----------------|

|----------------|

The BCLR instruction is executed for PCR5.

### • After executing BCLR

|              | P57          | P56           | P55          | P54          | P53          | P52          | P51          | P50           |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Input/output | Output       | Output        | Output       | Output       | Output       | Output       | Output       | Input         |

| Pin state    | Low<br>level | High<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | Low<br>level | High<br>level |

| PCR5         | 1            | 1             | 1            | 1            | 1            | 1            | 1            | 0             |

| PDR5         | 1            | 0             | 0            | 0            | 0            | 0            | 0            | 0             |

- Description on operation

- 1. When the BCLR instruction is executed, first the CPU reads PCR5. Since PCR5 is a write-only register, the CPU reads a value of H'FF, even though the PCR5 value is actually H'3F.

- 2. Next, the CPU clears bit 0 in the read data to 0, changing the data to H'FE.

3. Finally, H'FE is written to PCR5 and BCLR instruction execution ends. As a result of this operation, bit 0 in PCR5 becomes 0, making P50 an input port. However, bits 7 and 6 in PCR5 change to 1, so that P57 and P56 change from input pins to output pins. To prevent this problem, store a copy of the PCR5 data in a work area in memory and manipulate data of the bit in the work area, then write this data to PCR5.

### 5.1.3 External Clock Input Method

Connect an external clock signal to pin  $OSC_1$ , and leave pin  $OSC_2$  open. Figure 5.6 shows a typical connection. The duty cycle of the external clock signal must be 45 to 55%.

Figure 5.6 Example of External Clock Input

### 5.2 Prescalers

### 5.2.1 Prescaler S

Prescaler S is a 13-bit counter using the system clock ( $\phi$ ) as its input clock. It is incremented once per clock period. Prescaler S is initialized to H'0000 by a reset, and starts counting on exit from the reset state. In standby mode and subsleep mode, the system clock pulse generator stops. Prescaler S also stops and is initialized to H'0000. The CPU cannot read or write prescaler S.

The output from prescaler S is shared by the on-chip peripheral modules. The divider ratio can be set separately for each on-chip peripheral function. In active mode and sleep mode, the clock input to prescaler S is determined by the division factor designated by MA2 to MA0 in SYSCR2.

## 5.3 Usage Notes

### 5.3.1 Note on Resonators

Resonator characteristics are closely related to board design and should be carefully evaluated by the user, referring to the examples shown in this section. Resonator circuit constants will differ depending on the resonator element, stray capacitance in its interconnecting circuit, and other factors. Suitable constants should be determined in consultation with the resonator element manufacturer. Design the circuit so that the resonator element never receives voltages exceeding its maximum rating.

- 4. After matching the bit rates, the chip transmits one H'00 byte to the host to indicate the completion of bit rate adjustment. The host should confirm that this adjustment end indication (H'00) has been received normally, and transmit one H'55 byte to the chip. If reception could not be performed normally, initiate boot mode again by a reset. Depending on the host's transfer bit rate and system clock frequency of this LSI, there will be a discrepancy between the bit rates of the host and the chip. To operate the SCI properly, set the host's transfer bit rate and system clock frequency of this LSI within the ranges listed in table 7.3.

- 5. In boot mode, a part of the on-chip RAM area is used by the boot program. The area H'F780 to H'FEEF is the area to which the programming control program is transferred from the host. The boot program area cannot be used until the execution state in boot mode switches to the programming control program.

- 6. Before branching to the programming control program, the chip terminates transfer operations by SCI3 (by clearing the RE and TE bits in SCR3 to 0), however the adjusted bit rate value remains set in BRR. Therefore, the programming control program can still use it for transfer of write data or verify data with the host. The TxD pin is high (PCR22 = 1, P22 = 1). The contents of the CPU general registers are undefined immediately after branching to the programming control program. These registers must be initialized at the beginning of the programming control program, as the stack pointer (SP), in particular, is used implicitly in subroutine calls, etc.

- 7. Boot mode can be cleared by a reset. End the reset after driving the reset pin low, waiting at least 20 states, and then setting the  $\overline{\text{NMI}}$  pin. Boot mode is also cleared when a WDT overflow occurs.

- 8. Do not change the TEST pin and  $\overline{\text{NMI}}$  pin input levels in boot mode.

## Section 11 Timer W

The timer W has a 16-bit timer having output compare and input capture functions. The timer W can count external events and output pulses with an arbitrary duty cycle by compare match between the timer counter and four general registers. Thus, it can be applied to various systems.

## 11.1 Features

- Selection of five counter clock sources: four internal clocks ( $\phi$ ,  $\phi/2$ ,  $\phi/4$ , and  $\phi/8$ ) and an external clock (external events can be counted)

- Capability to process up to four pulse outputs or four pulse inputs

- Four general registers:

- Independently assignable output compare or input capture functions

- Usable as two pairs of registers; one register of each pair operates as a buffer for the output compare or input capture register

- Four selectable operating modes :

- Waveform output by compare match

- Selection of 0 output, 1 output, or toggle output

- Input capture function

- Rising edge, falling edge, or both edges

- Counter clearing function

- Counters can be cleared by compare match

- PWM mode

- Up to three-phase PWM output can be provided with desired duty ratio.

- Any initial timer output value can be set

- Five interrupt sources

Four compare match/input capture interrupts and an overflow interrupt.

Table 11.1 summarizes the timer W functions, and figure 11.1 shows a block diagram of the timer W.

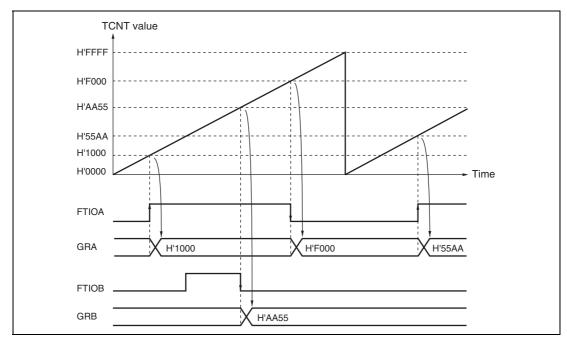

The TCNT value can be captured into a general register (GRA, GRB, GRC, or GRD) when a signal level changes at an input-capture pin (FTIOA, FTIOB, FTIOC, or FTIOD). Capture can take place on the rising edge, falling edge, or both edges. By using the input-capture function, the pulse width and periods can be measured. Figure 11.7 shows an example of input capture when both edges of FTIOA and the falling edge of FTIOB are selected as capture edges. TCNT operates as a free-running counter.

Figure 11.7 Input Capture Operating Example

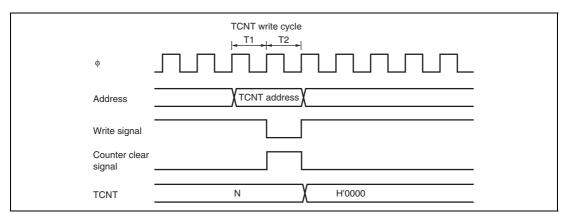

Figure 11.24 Contention between TCNT Write and Clear

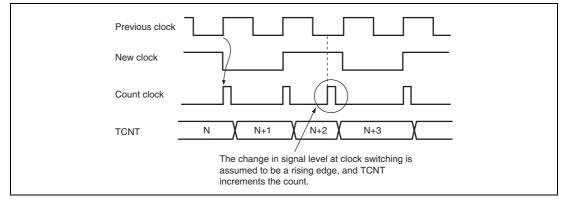

Figure 11.25 Internal Clock Switching and TCNT Operation

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-----|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | MPIE     | 0                | R/W | Multiprocessor Interrupt Enable (enabled only when the MP bit in SMR is 1 in asynchronous mode)                                                                                                                                                                                                                                                                                         |

|     |          |                  |     | When this bit is set to 1, receive data in which the<br>multiprocessor bit is 0 is skipped, and setting of the<br>RDRF, FER, and OER status flags in SSR is disabled.<br>On receiving data in which the multiprocessor bit is 1, this<br>bit is automatically cleared and normal reception is<br>resumed. For details, refer to section 13.6, Multiprocessor<br>Communication Function. |

| 2   | TEIE     | 0                | R/W | Transmit End Interrupt Enable                                                                                                                                                                                                                                                                                                                                                           |

|     |          |                  |     | When this bit is set to 1, TEI interrupt request is enabled.                                                                                                                                                                                                                                                                                                                            |

| 1   | CKE1     | 0                | R/W | Clock Enable 0 and 1                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | CKE0     | 0                | R/W | Selects the clock source.                                                                                                                                                                                                                                                                                                                                                               |

|     |          |                  |     | Asynchronous mode                                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | 00: On-chip baud rate generator                                                                                                                                                                                                                                                                                                                                                         |

|     |          |                  |     | 01: On-chip baud rate generator                                                                                                                                                                                                                                                                                                                                                         |

|     |          |                  |     | Outputs a clock of the same frequency as the bit rate from the SCK3 pin.                                                                                                                                                                                                                                                                                                                |

|     |          |                  |     | 10: External clock                                                                                                                                                                                                                                                                                                                                                                      |

|     |          |                  |     | Inputs a clock with a frequency 16 times the bit rate from the SCK3 pin.                                                                                                                                                                                                                                                                                                                |

|     |          |                  |     | 11:Reserved                                                                                                                                                                                                                                                                                                                                                                             |

|     |          |                  |     | Clocked synchronous mode                                                                                                                                                                                                                                                                                                                                                                |

|     |          |                  |     | 00: On-chip clock (SCK3 pin functions as clock output)                                                                                                                                                                                                                                                                                                                                  |

|     |          |                  |     | 01:Reserved                                                                                                                                                                                                                                                                                                                                                                             |

|     |          |                  |     | 10: External clock (SCK3 pin functions as clock input)                                                                                                                                                                                                                                                                                                                                  |

|     |          |                  |     | 11:Reserved                                                                                                                                                                                                                                                                                                                                                                             |

## 13.4 Operation in Asynchronous Mode

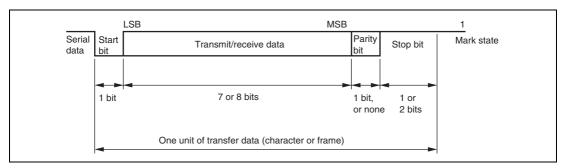

Figure 13.2 shows the general format for asynchronous serial communication. One character (or frame) consists of a start bit (low level), followed by data (in LSB-first order), a parity bit (high or low level), and finally stop bits (high level). Inside the SCI3, the transmitter and receiver are independent units, enabling full-duplex. Both the transmitter and the receiver also have a double-buffered structure, so data can be read or written during transmission or reception, enabling continuous data transfer.

Figure 13.2 Data Format in Asynchronous Communication

### 13.4.1 Clock

Either an internal clock generated by the on-chip baud rate generator or an external clock input at the SCK3 pin can be selected as the SCI3's serial clock, according to the setting of the COM bit in SMR and the CKE0 and CKE1 bits in SCR3. When an external clock is input at the SCK3 pin, the clock frequency should be 16 times the bit rate used.

When the SCI3 is operated on an internal clock, the clock can be output from the SCK3 pin. The frequency of the clock output in this case is equal to the bit rate, and the phase is such that the rising edge of the clock is in the middle of the transmit data, as shown in figure 13.3.

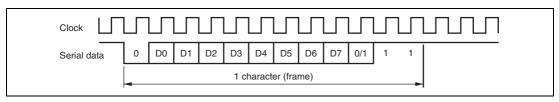

Figure 13.3 Relationship between Output Clock and Transfer Data Phase (Asynchronous Mode)(Example with 8-Bit Data, Parity, Two Stop Bits)

### 15.2.1 Low-Voltage-Detection Control Register (LVDCR)

LVDCR is used to enable or disable the low-voltage detection circuit, set the detection levels for the LVDR function, enable or disable the LVDR function, and enable or disable generation of an interrupt when the power-supply voltage rises above or falls below the respective levels.

Table 15.1 shows the relationship between the LVDCR settings and select functions. LVDCR should be set according to table 15.1.

| Bit    | Bit Name     | Initial<br>Value | R/W       | Description                                                                                                                                                                                                                    |

|--------|--------------|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | LVDE         | 0*               | R/W       | LVD Enable                                                                                                                                                                                                                     |

|        |              |                  |           | 0: The low-voltage detection circuit is not used (In standby mode)                                                                                                                                                             |

|        |              |                  |           | 1: The low-voltage detection circuit is used                                                                                                                                                                                   |

| 6 to 4 | _            | All 1            |           | Reserved                                                                                                                                                                                                                       |

|        |              |                  |           | These bits are always read as 1, and cannot be modified.                                                                                                                                                                       |

| 3      | LVDSEL       | 0*               | R/W       | LVDR Detection Level Select                                                                                                                                                                                                    |

|        |              |                  |           | 0: Reset detection voltage is 2.3 V (typ.)                                                                                                                                                                                     |

|        |              |                  |           | 1: Reset detection voltage is 3.6 V (typ.)                                                                                                                                                                                     |

|        |              |                  |           | When the falling or rising voltage detection interrupt is used, reset detection voltage of 2.3 V (typ.) should be used. When only a reset detection interrupt is used, reset detection voltage of 3.6 V (typ.) should be used. |

| 2      | LVDRE        | 0*               | R/W       | LVDR Enable                                                                                                                                                                                                                    |

|        |              |                  |           | 0: Disables the LVDR function                                                                                                                                                                                                  |

|        |              |                  |           | 1: Enables the LVDR function                                                                                                                                                                                                   |

| 1      | LVDDE        | 0                | R/W       | Voltage-Fall-Interrupt Enable                                                                                                                                                                                                  |

|        |              |                  |           | 0: Interrupt on the power-supply voltage falling below the<br>selected detection level disabled                                                                                                                                |

|        |              |                  |           | 1: Interrupt on the power-supply voltage falling below the<br>selected detection level enabled                                                                                                                                 |

| 0      | LVDUE        | 0                | R/W       | Voltage-Rise-Interrupt Enable                                                                                                                                                                                                  |

|        |              |                  |           | 0: Interrupt on the power-supply voltage rising above the<br>selected detection level disabled                                                                                                                                 |

|        |              |                  |           | 1: Interrupt on the power-supply voltage rising above the<br>selected detection level enabled                                                                                                                                  |

| Note:  | * Not initia | lized by LV      | /DR but i |                                                                                                                                                                                                                                |

## Section 18 Electrical Characteristics

### 18.1 Absolute Maximum Ratings

#### Table 18.1 Absolute Maximum Ratings

| Item                 |                         | Symbol          | Value                       | Unit | Note |

|----------------------|-------------------------|-----------------|-----------------------------|------|------|

| Power supply voltage |                         | V <sub>cc</sub> | –0.3 to +7.0                | V    | *    |

| Analog power supply  | voltage                 | $AV_{cc}$       | -0.3 to +7.0                | V    | _    |

| Input voltage        | Ports other than Port B | V <sub>IN</sub> | –0.3 to V $_{\rm cc}$ +0.3  | V    | _    |

|                      | Port B                  | _               | –0.3 to AV $_{\rm cc}$ +0.3 | V    | _    |

| Operating temperatu  | re                      | $T_{_{opr}}$    | -20 to +75                  | °C   | _    |

| Storage temperature  |                         | $T_{stg}$       | –55 to +125                 | °C   |      |

Note: \* Permanent damage may result if maximum ratings are exceeded. Normal operation should be under the conditions specified in Electrical Characteristics. Exceeding these values can result in incorrect operation and reduced reliability.

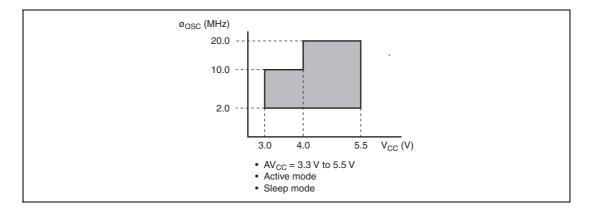

## **18.2** Electrical Characteristics (F-ZTAT<sup>TM</sup> Version)

### 18.2.1 Power Supply Voltage and Operating Ranges

### (1) Power Supply Voltage and Oscillation Frequency Range

RENESAS

|                         |                  | Applicable                                                                                                                     |                                                       |                 | Value | S   |                  | Reference   |

|-------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|-------|-----|------------------|-------------|

| Item                    | Symbol           | Pins                                                                                                                           | Test Condition                                        | Min             | Тур   | Max | Unit             | Figure      |

| RES pin low width       | t <sub>REL</sub> | RES                                                                                                                            | At power-on and in<br>modes other than<br>those below | t <sub>rc</sub> | —     | _   | ms               | Figure 18.2 |

|                         |                  |                                                                                                                                | In active mode and sleep mode operation               | 200             | _     | _   | ns               | _           |

| Input pin high<br>width | t <sub>iH</sub>  | NMI,<br>IRQ0, IRQ3,<br>WKP0 to<br>WKP5,<br>TMCIV,<br>TMRIV,<br>TRGV,<br>ADTRG,<br>FTCI,<br>FTIOA to<br>FTIOD                   |                                                       | 2               |       |     | t <sub>cyc</sub> | Figure 18.3 |

| Input pin low<br>width  | t <sub>ı.</sub>  | NMI,       IRQ0, IRQ3,       WKP0 to       WKP5,       TMCIV,       TMRIV,       TRGV,       ADTRG,       FTIOA to       FTIOD |                                                       | 2               | _     |     | t <sub>cyc</sub> | _           |

Notes: 1. When an external clock is input, the minimum system clock oscillator frequency is 1.0 MHz.

2. Determined by MA2 to MA0 in system control register 2 (SYSCR2).

### 18.2.6 Flash Memory Characteristics

### Table 18.7 Flash Memory Characteristics

$V_{cc}$  = 3.0 V to 5.5 V,  $V_{ss}$  = 0.0 V,  $T_a$  = -20°C to +75°C, unless otherwise specified.

| Item           |                                                                  |                  | Test                       |      |       |      |       |

|----------------|------------------------------------------------------------------|------------------|----------------------------|------|-------|------|-------|

|                |                                                                  | Symbol           | Condition                  | Min  | Тур   | Max  | Unit  |

| Programming t  | time (per 128 bytes)* <sup>1</sup> * <sup>2</sup> * <sup>4</sup> | t <sub>P</sub>   |                            | _    | 7     | 200  | ms    |

| Erase time (pe | r block) * <sup>1</sup> * <sup>3</sup> * <sup>6</sup>            | t <sub>e</sub>   |                            | _    | 100   | 1200 | ms    |

| Reprogrammin   | ng count                                                         | $N_{\text{wec}}$ |                            | 1000 | 10000 | —    | Times |

| Programming    | Wait time after SWE bit setting*1                                | x                |                            | 1    | _     | _    | μs    |

|                | Wait time after PSU bit setting*1                                | у                |                            | 50   | _     | _    | μs    |

|                | Wait time after P bit setting                                    | z1               | $1 \le n \le 6$            | 28   | 30    | 32   | μs    |

|                | *1*4                                                             | z2               | $7 \le n \le 1000$         | 198  | 200   | 202  | μs    |

|                |                                                                  | z3               | Additional-<br>programming | 8    | 10    | 12   | μs    |

|                | Wait time after P bit clear*1                                    | α                |                            | 5    | —     | _    | μs    |

|                | Wait time after PSU bit clear*1                                  | β                |                            | 5    | —     | —    | μs    |

|                | Wait time after PV bit setting*1                                 | γ                |                            | 4    | —     | —    | μs    |

|                | Wait time after<br>dummy write* <sup>1</sup>                     | ε                |                            | 2    | _     | _    | μs    |

|                | Wait time after PV bit clear*1                                   | η                |                            | 2    | —     | —    | μs    |

|                | Wait time after SWE bit clear*1                                  | θ                |                            | 100  | _     | _    | μs    |

|                | Maximum<br>programming count*1*4*5                               | Ν                |                            | _    | _     | 1000 | Times |

### 18.3.7 Power-On Reset Circuit Characteristics (Optional)

### Table 18.16 Power-On Reset Circuit Characteristics

$V_{ss} = 0.0 \text{ V}, T_a = -20 \text{ to } +75^{\circ}\text{C}$ , unless otherwise indicated.

|                               |                  | Test             |         |        |        |      |

|-------------------------------|------------------|------------------|---------|--------|--------|------|

| Item                          | Symbol           | Condition        | Min     | Тур    | Max    | Unit |

| Pull-up resistance of RES pin | R <sub>RES</sub> |                  | 100     | 0 150  | —      | kΩ   |

| Power-on reset start voltage* | $V_{por}$        |                  | —       | _      | 100    | mV   |

| Note: * The power-supply      | por              | t fall below Voc | r = 100 | mV and | thon i | rico |

Note: \* The power-supply voltage (Vcc) must fall below Vpor = 100 mV and then rise after charge of the RES pin is removed completely. In order to remove charge of the RES pin, it is recommended that the diode be placed in the Vcc side. If the power-supply voltage (Vcc) rises from the point over 100 mV, a power-on reset may not occur.

## **18.4** Operation Timing

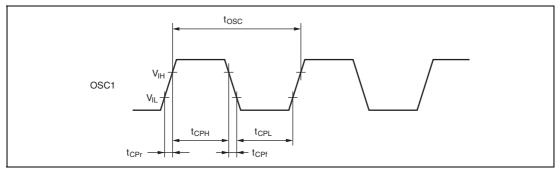

Figure 18.1 System Clock Input Timing

# Appendix B I/O Port Block Diagrams

## B.1 I/O Port Block Diagrams

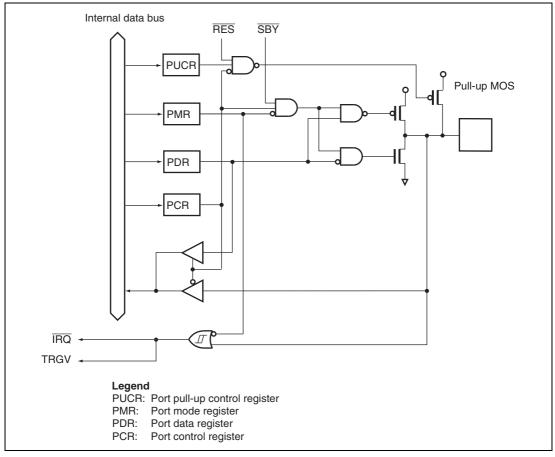

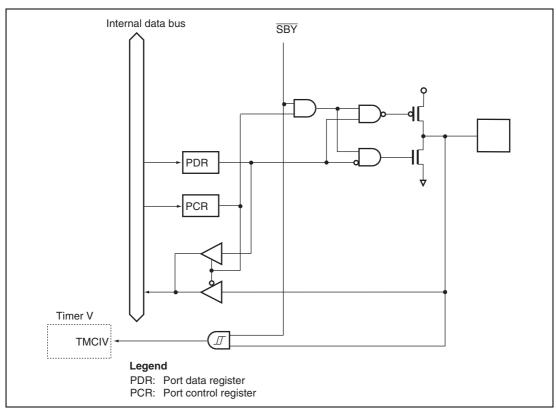

$\overline{\text{RES}}$  goes low in a reset, and  $\overline{\text{SBY}}$  goes low in a reset and in standby mode.

Figure B.1 Port 1 Block Diagram (P17)

Figure B.15 Port 7 Block Diagram (P75)

# Appendix D Package Dimensions

The package dimensions that are shows in the Renesas Semiconductor Packages Data Book have priority.