#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                              |

| Peripherals                | DMA, WDT                                                                         |

| Number of I/O              | 68                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 10K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                      |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-BQFP                                                                          |

| Supplier Device Package    | 80-QFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30621fcpgp-u9c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.2 Performance Outline

Table 1.1 to 1.3 list Performance Outline of M16C/62P Group (M16C/62P, M16C/62PT)(128-pin version).

| Table 1.1 | Performance Outline of M16C/62P Group (M16C/62P, M16C/62PT)(128-pin version) |

|-----------|------------------------------------------------------------------------------|

|-----------|------------------------------------------------------------------------------|

|                            | Item                                                | Performance                                                                         |  |  |

|----------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------|--|--|

|                            |                                                     | M16C/62P                                                                            |  |  |

| CPU                        | Number of Basic Instructions                        | 91 instructions                                                                     |  |  |

| 1                          | Minimum Instruction Execution                       | 41.7ns(f(BCLK)=24MHz, VCC1=3.3 to 5.5V)                                             |  |  |

|                            | Time                                                | 100ns(f(BCLK)=10MHz, VCC1=2.7 to 5.5V)                                              |  |  |

|                            | Operating Mode                                      | Single-chip, memory expansion and microprocessor mode                               |  |  |

|                            | Address Space                                       | 1 Mbyte (Available to 4 Mbytes by memory space expansion                            |  |  |

|                            | -                                                   | function)                                                                           |  |  |

|                            | Memory Capacity                                     | See Table 1.4 to 1.5 Product List                                                   |  |  |

| Peripheral                 | Port                                                | Input/Output : 113 pins, Input : 1 pin                                              |  |  |

| Function                   | Multifunction Timer                                 | Timer A : 16 bits x 5 channels,                                                     |  |  |

|                            |                                                     | Timer B : 16 bits x 6 channels,                                                     |  |  |

|                            |                                                     | Three phase motor control circuit                                                   |  |  |

|                            | Serial Interface                                    | 3 channels                                                                          |  |  |

|                            |                                                     | Clock synchronous, UART, I <sup>2</sup> C bus <sup>(1)</sup> , IEBus <sup>(2)</sup> |  |  |

|                            |                                                     | 2 channels                                                                          |  |  |

|                            |                                                     | Clock synchronous                                                                   |  |  |

|                            | A/D Converter                                       | 10-bit A/D converter: 1 circuit, 26 channels                                        |  |  |

|                            | D/A Converter                                       | 8 bits x 2 channels                                                                 |  |  |

|                            | DMAC                                                | 2 channels                                                                          |  |  |

|                            | CRC Calculation Circuit                             | CCITT-CRC                                                                           |  |  |

| -                          | Watchdog Timer 15 bits x 1 channel (with prescaler) |                                                                                     |  |  |

|                            | Interrupt                                           | Internal: 29 sources, External: 8 sources, Software: 4 sources,                     |  |  |

|                            |                                                     | Priority level: 7 levels                                                            |  |  |

|                            | Clock Generation Circuit                            | 4 circuits                                                                          |  |  |

|                            |                                                     | Main clock generation circuit (*),                                                  |  |  |

|                            |                                                     | Subclock generation circuit (*),                                                    |  |  |

|                            |                                                     | On-chip oscillator, PLL synthesizer                                                 |  |  |

|                            |                                                     | (*)Equipped with a built-in feedback resistor.                                      |  |  |

|                            | Oscillation Stop Detection                          | Stop detection of main clock oscillation, re-oscillation detection                  |  |  |

|                            | Function                                            | function (A)                                                                        |  |  |

|                            | Voltage Detection Circuit                           | Available (option <sup>(4)</sup> )                                                  |  |  |

| Electric                   | Supply Voltage                                      | VCC1=3.0 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=24MHz)                                 |  |  |

| Characteristics            |                                                     | VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=10MHz)                                 |  |  |

|                            | Power Consumption                                   | 14 mA (VCC1=VCC2=5V, f(BCLK)=24MHz)                                                 |  |  |

|                            |                                                     | 8 mA (VCC1=VCC2=3V, f(BCLK)=10MHz)                                                  |  |  |

|                            |                                                     | 1.8μA (VCC1=VCC2=3V, f(XCIN)=32kHz, wait mode)<br>0.7μA (VCC1=VCC2=3V, stop mode)   |  |  |

| Flash memory               | Program/Erase Supply Voltage                        | 3.3±0.3 V or 5.0±0.5 V                                                              |  |  |

| version                    | Program and Erase Endurance                         | 100 times (all area)                                                                |  |  |

|                            |                                                     | 100 times (all area)<br>or 1,000 times (user ROM area without block A and block 1)  |  |  |

|                            |                                                     | / 10,000 times (block A, block 1) $^{(3)}$                                          |  |  |

| Operating Ambie            | nt Temperature                                      | -20 to 85°C,                                                                        |  |  |

|                            |                                                     |                                                                                     |  |  |

| Package                    |                                                     |                                                                                     |  |  |

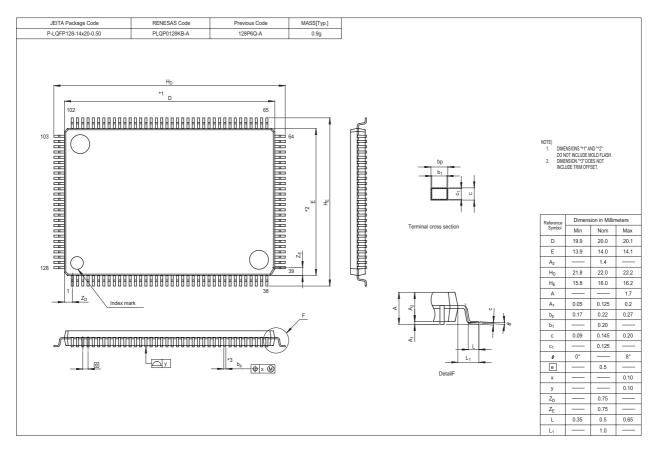

| Operating Ambie<br>Package | nt Temperature                                      | -20 to 85°C,<br>-40 to 85°C <sup>(3)</sup><br>128-pin plastic mold LQFP             |  |  |

NOTES:

- 1. I<sup>2</sup>C bus is a registered trademark of Koninklijke Philips Electronics N. V.

- 2. IEBus is a registered trademark of NEC Electronics Corporation.

- 3. See **Table 1.8 Product Code** for the program and erase endurance, and operating ambient temperature. In addition 1,000 times/10,000 times are under development as of Jul., 2005. Please inquire about a release schedule.

- 4. All options are on request basis.

|                             | Item                                   | Performance                                                                                                                                                                               |                                                                                                              |  |  |  |  |

|-----------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                             |                                        | M16C/62P                                                                                                                                                                                  | M16C/62PT <sup>(4)</sup>                                                                                     |  |  |  |  |

| CPU                         | Number of Basic Instructions           | 91 instructions                                                                                                                                                                           |                                                                                                              |  |  |  |  |

|                             | Minimum Instruction<br>Execution Time  | 41.7ns(f(BCLK)=24MHz, VCC1=3.3 to 5.5V) 41.7ns(f(BCLK)=24MHz, VCC1=4.0<br>100ns(f(BCLK)=10MHz, VCC1=2.7 to 5.5V)                                                                          |                                                                                                              |  |  |  |  |

|                             | Operating Mode                         | Single-chip mode                                                                                                                                                                          |                                                                                                              |  |  |  |  |

|                             | Address Space                          | 1 Mbyte                                                                                                                                                                                   |                                                                                                              |  |  |  |  |

|                             | Memory Capacity                        | See Table 1.4 to 1.7 Product Lis                                                                                                                                                          | st                                                                                                           |  |  |  |  |

| Peripheral                  | Port                                   | Input/Output : 70 pins, Input : 1 pin                                                                                                                                                     |                                                                                                              |  |  |  |  |

| Function                    | Multifunction Timer                    | Timer A : 16 bits x 5 channels (Time<br>Timer B : 16 bits x 6 channels (Time                                                                                                              |                                                                                                              |  |  |  |  |

|                             | Serial Interface                       | 2 channels<br>Clock synchronous, UART, 1 <sup>2</sup> C bu<br>1 channel<br>Clock synchronous, 1 <sup>2</sup> C bus <sup>(1)</sup> , IE<br>2 channels<br>Clock synchronous (1 channel is c | Bus <sup>(2)</sup><br>only transmission)                                                                     |  |  |  |  |

| 1                           | A/D Converter                          | 10-bit A/D converter: 1 circuit, 26 ch                                                                                                                                                    | annels                                                                                                       |  |  |  |  |

|                             | D/A Converter                          | 8 bits x 2 channels                                                                                                                                                                       |                                                                                                              |  |  |  |  |

|                             | DMAC                                   | 2 channels                                                                                                                                                                                |                                                                                                              |  |  |  |  |

|                             | CRC Calculation Circuit                | CCITT-CRC                                                                                                                                                                                 |                                                                                                              |  |  |  |  |

|                             | Watchdog Timer                         | 15 bits x 1 channel (with prescaler)                                                                                                                                                      |                                                                                                              |  |  |  |  |

|                             | Interrupt                              | Internal: 29 sources, External: 5 sources, Sof                                                                                                                                            | tware: 4 sources, Priority level: 7 levels                                                                   |  |  |  |  |

|                             | Clock Generation Circuit               | 4 circuits<br>Main clock generation circuit (*), Subclock generation circuit (*),<br>On-chip oscillator, PLL synthesizer<br>(*)Equipped with a built-in feedback resistor.                |                                                                                                              |  |  |  |  |

|                             | Oscillation Stop<br>Detection Function | Stop detection of main clock oscillati                                                                                                                                                    | ock oscillation, re-oscillation detection function                                                           |  |  |  |  |

|                             | Voltage Detection Circuit              |                                                                                                                                                                                           | Absent                                                                                                       |  |  |  |  |

| Electric<br>Characteristics | Supply Voltage                         | VCC1=3.0 to 5.5 V, (f(BCLK=24MHz)<br>VCC1=2.7 to 5.5 V, (f(BCLK=10MHz)                                                                                                                    | VCC1=4.0 to 5.5V, (f(BCLK=24MHz)                                                                             |  |  |  |  |

|                             | Power Consumption                      | 14 mA (VCC1=5V, f(BCLK)=24MHz)<br>8 mA (VCC1=3V, f(BCLK)=10MHz)<br>1.8μA (VCC1=3V, f(XCIN)=32kHz,<br>wait mode)<br>0.7μA (VCC1=3V, stop mode)                                             | 14 mA (VCC1=5V, f(BCLK)=24MHz)<br>2.0μA (VCC1=5V, f(XCIN)=32kHz,<br>wait mode)<br>0.8μA (VCC1=5V, stop mode) |  |  |  |  |

| Flash memory                | Program/Erase Supply Voltage           | 3.3 ± 0.3V or 5.0 ± 0.5V                                                                                                                                                                  | 5.0 ± 0.5V                                                                                                   |  |  |  |  |

| version                     | Program and Erase<br>Endurance         | 100 times (all area)<br>or 1,000 times (user ROM area without block A and block 1)<br>/ 10,000 times (block A, block 1) <sup>(3)</sup>                                                    |                                                                                                              |  |  |  |  |

| Operating Amb               | ient Temperature                       | -20 to 85°C,<br>-40 to 85°C <sup>(3)</sup>                                                                                                                                                | T version : -40 to 85°C<br>V version : -40 to 125°C                                                          |  |  |  |  |

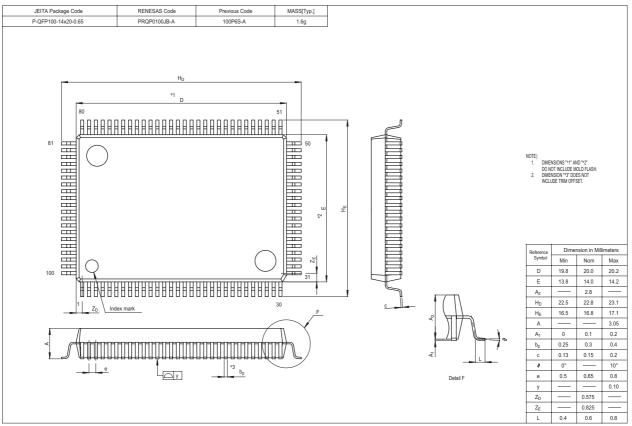

| Package                     |                                        | 80-pin plastic mold QFP                                                                                                                                                                   | 1                                                                                                            |  |  |  |  |

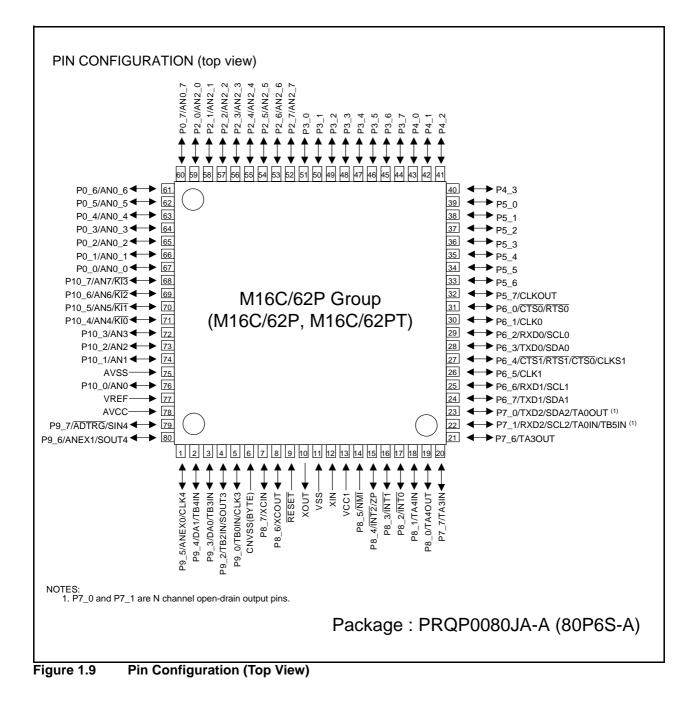

#### Table 1.3 Performance Outline of M16C/62P Group (M16C/62P, M16C/62PT)(80-pin version)

NOTES:

- 1. I<sup>2</sup>C bus is a registered trademark of Koninklijke Philips Electronics N. V.

- 2. IEBus is a registered trademark of NEC Electronics Corporation.

- 3. See **Table 1.8 and 1.9 Product Code** for the program and erase endurance, and operating ambient temperature.

In addition 1,000 times/10,000 times are under development as of Jul., 2005. Please inquire about a release schedule.

4. All options are on request basis.

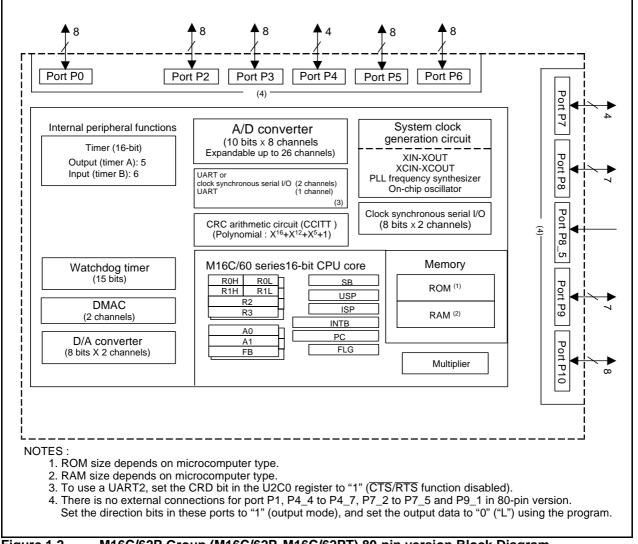

M16C/62P Group (M16C/62P, M16C/62PT) 80-pin version Block Diagram

As of Dec. 2005

|                 |     |               | -               | -                           |                        |                   |

|-----------------|-----|---------------|-----------------|-----------------------------|------------------------|-------------------|

| Туре No.        |     | ROM Capacity  | RAM<br>Capacity | Package Type <sup>(1)</sup> | Re                     | emarks            |

| M3062CM6V-XXXFP | (P) | 48 Kbytes     | 4 Kbytes        | PRQP0100JB-A                | Mask ROM               | V Version         |

| M3062CM6V-XXXGP | (P) |               |                 | PLQP0100KB-A                | version                | (High reliability |

| M3062EM6V-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        | 125°C version)    |

| M3062CM8V-XXXFP | (P) | 64 Kbytes     | 4 Kbytes        | PRQP0100JB-A                |                        |                   |

| M3062CM8V-XXXGP | (P) |               |                 | PLQP0100KB-A                |                        |                   |

| M3062EM8V-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        |                   |

| M3062CMAV-XXXFP | (P) | 96 Kbytes     | 5 Kbytes        | PRQP0100JB-A                |                        |                   |

| M3062CMAV-XXXGP | (P) |               |                 | PLQP0100KB-A                |                        |                   |

| M3062EMAV-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        |                   |

| M3062AMCV-XXXFP | (D) | 128 Kbytes    | 10 Kbytes       | PRQP0100JB-A                |                        |                   |

| M3062AMCV-XXXGP | (D) |               |                 | PLQP0100KB-A                |                        |                   |

| M3062BMCV-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        |                   |

| M3062AFCVFP     | (D) | 128K+4 Kbytes | 10 Kbytes       | PRQP0100JB-A                | Flash                  |                   |

| M3062AFCVGP     | (D) |               |                 | PLQP0100KB-A                | memory                 |                   |

| M3062BFCVGP     | (P) |               |                 | PRQP0080JA-A                | version <sup>(2)</sup> |                   |

| M3062JFHVFP     | (P) | 384K+4 Kbytes | 31 Kbytes       | PRQP0100JB-A                |                        |                   |

| M3062JFHVGP     | (P) |               |                 | PLQP0100KB-A                |                        |                   |

Table 1.7 Product List (4) (V version (M16C/62PT))

(D): Under development

(P): Under planning

NOTES:

1. The old package type numbers of each package type are as follows.

PLQP0128KB-A : 128P6Q-A, PRQP0100JB-A : 100P6S-A, PLQP0100KB-A : 100P6Q-A,

PRQP0080JA-A : 80P6S-A

2. In the flash memory version, there is 4K bytes area (block A).

| Pin<br>FP | No.<br>GP | Control Pin | Port         | Interrupt Pin | Timer Pin   | UART Pin             | Analog Pin | Bus Control Pin    |

|-----------|-----------|-------------|--------------|---------------|-------------|----------------------|------------|--------------------|

| 1         | 99        |             | P9_6         |               |             | SOUT4                | ANEX1      |                    |

| 2         | 100       |             | P9_5         |               |             | CLK4                 | ANEX0      |                    |

| 3         | 1         |             | P9_4         |               | TB4IN       |                      | DA1        |                    |

| 4         | 2         |             | P9_3         |               | TB3IN       |                      | DA0        |                    |

| 5         | 3         |             | P9_2         |               | TB2IN       | SOUT3                |            |                    |

| 6         | 4         |             | <br>P9_1     |               | TB1IN       | SIN3                 |            |                    |

| 7         | 5         |             | P9_0         |               | TBOIN       | CLK3                 |            |                    |

| 8         | 6         | BYTE        |              |               |             |                      |            |                    |

| 9         | 7         | CNVSS       |              |               |             |                      |            |                    |

| 10        | 8         | XCIN        | P8_7         |               |             |                      |            |                    |

| 11        | 9         | XCOUT       | P8_6         |               |             |                      |            |                    |

| 12        | 10        | RESET       |              |               |             |                      |            |                    |

| 13        | 11        | XOUT        |              |               |             |                      |            |                    |

| 14        | 12        | VSS         |              |               |             |                      |            |                    |

| 15        | 13        | XIN         |              |               |             |                      |            |                    |

| 16        | 14        | VCC1        |              |               |             |                      |            |                    |

| 17        | 15        |             | P8_5         | NMI           |             |                      |            |                    |

| 18        | 16        |             | <br>P8_4     | INT2          | ZP          |                      |            | 1                  |

| 19        | 17        |             | P8_3         | INT1          |             |                      |            |                    |

| 20        | 18        |             |              |               |             |                      |            |                    |

|           |           |             | P8_2         | INT0          |             |                      |            |                    |

| 21        | 19        |             | P8_1         |               | TA4IN/U     |                      |            |                    |

| 22        | 20        |             | P8_0         |               | TA4OUT/U    |                      |            |                    |

| 23        | 21        |             | P7_7         |               | TA3IN       |                      |            |                    |

| 24        | 22        |             | P7_6         |               | TA3OUT      |                      |            |                    |

| 25        | 23        |             | P7_5         |               | TA2IN/W     |                      |            |                    |

| 26        | 24        |             | P7_4         |               | TA2OUT/W    |                      |            |                    |

| 27        | 25        |             | P7_3         |               | TA1IN/V     | CTS2/RTS2            |            |                    |

| 28        | 26        |             | P7_2         |               | TA1OUT/V    | CLK2                 |            |                    |

| 29        | 27        |             | P7_1         |               | TA0IN/TB5IN | RXD2/SCL2            |            |                    |

| 30        | 28        |             | P7_0         |               | TA0OUT      | TXD2/SDA2            |            |                    |

| 31        | 29        |             | P6_7         |               |             | TXD1/SDA1            |            |                    |

| 32        | 30        |             | P6_6         |               |             | RXD1/SCL1            |            |                    |

| 33        | 31        |             | P6_5         |               |             | CLK1                 |            |                    |

| 34        | 32        |             | P6_4         |               |             | CTS1/RTS1/CTS0/CLKS1 |            |                    |

| 35        | 33        |             | P6_3         |               |             | TXD0/SDA0            |            |                    |

| 36        | 34        |             | P6_2         |               |             | RXD0/SCL0            |            |                    |

| 37        | 35        |             | P6_1         |               |             | CLK0                 |            |                    |

| 38        | 36        |             | P6_0         |               |             | CTS0/RTS0            |            |                    |

| 39        | 37        |             | P5_7         |               |             |                      |            | RDY/CLKOUT         |

| 40        | 38        |             | P5_6         |               |             |                      |            | ALE                |

| 41        | 39        |             | <br>P5_5     |               |             |                      |            | HOLD               |

| 42        | 40        |             | P5_4         |               |             |                      |            | HLAD               |

| 42        | 40        |             | P5_4<br>P5_3 |               | <u> </u>    |                      |            | BCLK               |

|           |           |             |              |               |             |                      |            |                    |

| 44        | 42        |             | P5_2         |               |             |                      |            | RD                 |

| 45        | 43        |             | P5_1         |               |             |                      |            | WRH/BHE            |

| 46        | 44        |             | P5_0         |               |             |                      |            | WRL/WR             |

| 47        | 45        |             | P4_7         |               |             |                      |            | CS3                |

| 48        | 46        |             | P4_6         |               |             |                      |            | CS2                |

| 49        | 47        |             | <br>P4_5     |               |             |                      |            | CS1                |

| 49        |           |             | ·_~          | 1             | 1           | 1                    | 1          | 1 - <del>-</del> - |

Table 1.13

Pin Characteristics for 100-Pin Package (1)

RENESAS

| Signal Name                            | Pin Name                   | I/O  | Power                 | Description                                                                                                                                   |

|----------------------------------------|----------------------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                      |                            | Туре | Supply <sup>(1)</sup> | '                                                                                                                                             |

| Main clock                             | XIN                        | I    | VCC1                  | I/O pins for the main clock generation circuit. Connect a ceramic                                                                             |

| input                                  |                            |      |                       | resonator or crystal oscillator between XIN and XOUT <sup>(3)</sup> . To use                                                                  |

| Main clock                             | XOUT                       | 0    | VCC1                  | the external clock, input the clock from XIN and leave XOUT open.                                                                             |

| output                                 | XON                        |      | 1/004                 |                                                                                                                                               |

| Sub clock input                        |                            |      | VCC1                  | I/O pins for a sub clock oscillation circuit. Connect a crystal oscillator between XCIN and XCOUT <sup>(3)</sup> . To use the external clock, |

| Sub clock<br>output                    | XCOUT                      | 0    | VCC1                  | input the clock from XCIN and leave XCOUT open.                                                                                               |

| BCLK output <sup>(2)</sup>             | BCLK                       | 0    | VCC2                  | Outputs the BCLK signal.                                                                                                                      |

| Clock output                           | CLKOUT                     | 0    | VCC2                  | The clock of the same cycle as fC, f8, or f32 is outputted.                                                                                   |

| INT interrupt                          | INTO to INT2               | - U  | VCC1                  | Input pins for the INT interrupt.                                                                                                             |

| input                                  |                            |      |                       | input pins for the INT interrupt.                                                                                                             |

|                                        | NT3 to INT5                | I    | VCC2                  |                                                                                                                                               |

| NMI interrupt<br>input                 | NMI                        | Ι    | VCC1                  | Input pin for the NMI interrupt. Pin states can be read by the P8_5 bit in the P8 register.                                                   |

| Key input<br>interrupt input           | KI0 to KI3                 | Ι    | VCC1                  | Input pins for the key input interrupt.                                                                                                       |

| Timer A                                | TA0OUT to                  | I/O  | VCC1                  | These are timer A0 to timer A4 I/O pins. (however, output of                                                                                  |

|                                        | TA4OUT                     |      |                       | TA0OUT for the N-channel open drain output.)                                                                                                  |

|                                        | TA0IN to<br>TA4IN          | Ι    | VCC1                  | These are timer A0 to timer A4 input pins.                                                                                                    |

|                                        | ZP                         |      | VCC1                  | Input pin for the Z-phase.                                                                                                                    |

| Timer B                                | TB0IN to<br>TB5IN          | Ι    | VCC1                  | These are timer B0 to timer B5 input pins.                                                                                                    |

| Three-phase<br>motor control<br>output | U, <u>Ū,</u> V, ⊽,<br>W, ₩ | 0    | VCC1                  | These are Three-phase motor control output pins.                                                                                              |

| Serial interface                       | CTS0<br>CTS2               | l    | VCC1                  | These are send control input pins.                                                                                                            |

|                                        | RTS0<br>RTS2               | 0    | VCC1                  | These are receive control output pins.                                                                                                        |

|                                        | CLK0 to<br>CLK4            | I/O  | VCC1                  | These are transfer clock I/O pins.                                                                                                            |

|                                        | RXD0 to<br>RXD2            | Ι    | VCC1                  | These are serial data input pins.                                                                                                             |

|                                        | SIN3, SIN4                 | I    | VCC1                  | These are serial data input pins.                                                                                                             |

|                                        | TXD0 to<br>TXD2            | 0    | VCC1                  | These are serial data output pins. (however, output of TXD2 for the N-channel open drain output.)                                             |

|                                        | SOUT3,<br>SOUT4            | 0    | VCC1                  | These are serial data output pins.                                                                                                            |

|                                        | CLKS1                      | 0    | VCC1                  | This is output pin for transfer clock output from multiple pins function.                                                                     |

| I <sup>2</sup> C mode                  | SDA0 to<br>SDA2            | I/O  | VCC1                  | These are serial data I/O pins. (however, output of SDA2 for the N-<br>channel open drain output.)                                            |

|                                        | SCL0 to<br>SCL2            | I/O  | VCC1                  | These are transfer clock I/O pins. (however, output of SCL2 for the N-channel open drain output.)                                             |

| Table 1.18 | Pin Description (100-pin and 128-pin Version) (2) |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

I : Input O : Output I/O : Input and output

NOTES:

- 1. When use VCC1 > VCC2, contacts due to some points or restrictions to be checked.

- 2. This pin function in M16C/62PT cannot be used.

- 3. Ask the oscillator maker the oscillation characteristic.

### 2.8.8 Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is "0"; USP is selected when the U flag is "1".

The U flag is cleared to "0" when a hardware interrupt request is accepted or an INT instruction for software interrupt Nos. 0 to 31 is executed.

### 2.8.9 Processor Interrupt Priority Level (IPL)

IPL is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than IPL, the interrupt is enabled.

#### 2.8.10 Reserved Area

When write to this bit, write "0". When read, its content is indeterminate.

| Table 4.2 | SFR Information ( | ( <b>2)</b> <sup>(1)</sup> |

|-----------|-------------------|----------------------------|

|-----------|-------------------|----------------------------|

| Address         | Register                                                                                      | Symbol         | After Reset            |

|-----------------|-----------------------------------------------------------------------------------------------|----------------|------------------------|

| 0040h           |                                                                                               |                |                        |

| 0041h           |                                                                                               |                |                        |

| 0042h           |                                                                                               |                |                        |

| 0043h           |                                                                                               |                |                        |

| 0044h           | INT3 Interrupt Control Register                                                               | INT3IC         | XX00X000b              |

| 0045h           | Timer B5 Interrupt Control Register                                                           | TB5IC          | XXXXX000b              |

| 0046h           | Timer B4 Interrupt Control Register, UART1 BUS Collision Detection Interrupt Control Register | TB4IC, U1BCNIC | XXXXX000b              |

| 0047h           | Timer B3 Interrupt Control Register, UART0 BUS Collision Detection Interrupt Control Register | TB3IC, U0BCNIC | XXXXX000b              |

| 0048h           | SI/O4 Interrupt Control Register, INT5 Interrupt Control Register                             | S4IC, INT5IC   | XX00X000b              |

| 0049h           | SI/O3 Interrupt Control Register, INT4 Interrupt Control Register                             | S3IC, INT4IC   | XX00X000b              |

| 004Ah           | UART2 Bus Collision Detection Interrupt Control Register                                      | BCNIC          | XXXXX000b              |

| 004Bh           | DMA0 Interrupt Control Register                                                               | DM0IC          | XXXXX000b              |

| 004Ch           | DMA1 Interrupt Control Register                                                               | DM1IC          | XXXXX000b              |

| 004Dh           | Key Input Interrupt Control Register                                                          | KUPIC          | XXXXX000b              |

| 004Eh           | A/D Conversion Interrupt Control Register                                                     | ADIC           | XXXXX000b              |

| 004Fh           | UART2 Transmit Interrupt Control Register                                                     | S2TIC          | XXXXX000b              |

| 0050h           | UART2 Receive Interrupt Control Register                                                      | S2RIC          | XXXXX000b              |

| 0051h           | UARTO Transmit Interrupt Control Register                                                     | SOTIC          | XXXXX000b              |

| 0052h           | UARTO Receive Interrupt Control Register                                                      | SORIC          | XXXXX000b              |

| 0053h           | UART1 Transmit Interrupt Control Register                                                     | S1TIC          | XXXXX000b              |

| 0054h           | UART1 Receive Interrupt Control Register                                                      | S1RIC          | XXXXX000b              |

| 0055h           | Timer A0 Interrupt Control Register                                                           | TAOIC          | XXXXX000b              |

| 0055h           | Timer A1 Interrupt Control Register                                                           | TAIIC          | XXXXX000b              |

| 0050n<br>0057h  | Timer A2 Interrupt Control Register                                                           | TATIC          | XXXXX000b              |

| 0057h<br>0058h  | Timer A3 Interrupt Control Register                                                           | TA3IC          | XXXXX000b              |

| 0058h<br>0059h  |                                                                                               | TASIC          |                        |

|                 | Timer A4 Interrupt Control Register                                                           |                | XXXXX000b<br>XXXXX000b |

| 005Ah           | Timer B0 Interrupt Control Register                                                           | TBOIC          |                        |

| 005Bh           | Timer B1 Interrupt Control Register                                                           | TB1IC          | XXXXX000b              |

| 005Ch           | Timer B2 Interrupt Control Register                                                           | TB2IC          | XXXXX000b              |

| 005Dh           | INT0 Interrupt Control Register                                                               | INTOIC         | XX00X000b              |

| 005Eh           | INT1 Interrupt Control Register                                                               | INT1IC         | XX00X000b              |

| 005Fh           | INT2 Interrupt Control Register                                                               | INT2IC         | XX00X000b              |

| 0060h           |                                                                                               |                |                        |

| 0061h           |                                                                                               |                |                        |

| 0062h           |                                                                                               |                |                        |

| 0063h           |                                                                                               |                |                        |

| 0064h           |                                                                                               |                |                        |

| 0065h           |                                                                                               |                |                        |

| 0066h           |                                                                                               |                |                        |

| 0067h           |                                                                                               |                |                        |

| 0068h           |                                                                                               |                |                        |

| 0069h           |                                                                                               |                |                        |

| 006Ah           |                                                                                               |                |                        |

| 006Bh           |                                                                                               |                |                        |

| 006Ch           |                                                                                               | 1              |                        |

| 006Dh           |                                                                                               | 1              |                        |

| 006Eh           |                                                                                               | 1              |                        |

| 006Fh           |                                                                                               |                |                        |

| 0070h           |                                                                                               |                |                        |

| 0070h           |                                                                                               |                |                        |

| 0072h           |                                                                                               | +              |                        |

| 0072h           |                                                                                               | +              |                        |

| 0073h<br>0074h  |                                                                                               |                |                        |

| 007411<br>0075h |                                                                                               |                |                        |

| 0075h           |                                                                                               |                |                        |

| 0076h           |                                                                                               | -              |                        |

|                 |                                                                                               | +              | -                      |

| 0078h           |                                                                                               |                |                        |

| 0079h           |                                                                                               |                |                        |

| 007Ah           |                                                                                               | 1              |                        |

| 007Bh           |                                                                                               |                |                        |

| 007Ch           |                                                                                               |                |                        |

| 007Dh           |                                                                                               |                |                        |

| 007Eh           |                                                                                               |                |                        |

| 007Eh           |                                                                                               |                |                        |

NOTES: 1. The blank areas are reserved and cannot be accessed by users.

X : Nothing is mapped to this bit

| Symbol                   |                                                                                                                                   | Parameter                                                                                                                                                                 |                                                                                      | Measuring Condition     | St       | andard |      | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------|----------|--------|------|------|

| Symbol                   | Falametei                                                                                                                         |                                                                                                                                                                           |                                                                                      | Measuring Condition     | Min.     | Тур.   | Max. | Unit |

| Vон                      | HIGH Output         P6_0 to P6_7, P7_2 to P7_           Voltage <sup>(3)</sup> P8_6, P8_7, P9_0 to P9_7, P11_0 to P11_7, P14_0, P |                                                                                                                                                                           | P10_0 to P10_7,                                                                      | IOH=-1mA                | Vcc1-0.5 |        | Vcc1 | v    |

|                          |                                                                                                                                   | P0_0 to P0_7, P1_0 to P1_<br>P3_0 to P3_7, P4_0 to P4_<br>P12_0 to P12_7, P13_0 to P                                                                                      | 7, P5_0 to P5_7,                                                                     | IOH=-1mA <sup>(2)</sup> | Vcc2-0.5 |        | Vcc2 |      |

| Vон                      | HIGH Output                                                                                                                       | Voltage XOUT                                                                                                                                                              | HIGHPOWER                                                                            | IOH=-0.1mA              | Vcc1-0.5 |        | Vcc1 | v    |

|                          |                                                                                                                                   |                                                                                                                                                                           | LOWPOWER                                                                             | ІОН=-50μА               | Vcc1-0.5 |        | Vcc1 | v    |

|                          | HIGH Output                                                                                                                       | Voltage XCOUT                                                                                                                                                             | HIGHPOWER                                                                            | With no load applied    |          | 2.5    |      | v    |

|                          |                                                                                                                                   |                                                                                                                                                                           | LOWPOWER                                                                             | With no load applied    |          | 1.6    |      | v    |

| Vol                      | LOW Output<br>Voltage <sup>(3)</sup>                                                                                              | P6_0 to P6_7, P7_0 to P7_<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P1                                                                                       | P10_0 to P10_7,                                                                      | IOL=1mA                 |          |        | 0.5  | v    |

|                          |                                                                                                                                   | P0_0 to P0_7, P1_0 to P1_<br>P3_0 to P3_7, P4_0 to P4_<br>P12_0 to P12_7, P13_0 to P                                                                                      | 7, P5_0 to P5_7,                                                                     | IOL=1mA <sup>(2)</sup>  |          |        | 0.5  |      |

| Vol                      | LOW Output \                                                                                                                      | /oltage XOUT                                                                                                                                                              | HIGHPOWER                                                                            | IOL=0.1mA               |          |        | 0.5  | v    |

|                          |                                                                                                                                   |                                                                                                                                                                           | LOWPOWER                                                                             | IOL=50μA                |          |        | 0.5  | v    |

| LOW Output Voltage XCOUT |                                                                                                                                   | Output Voltage XCOUT HIGHPOWER                                                                                                                                            |                                                                                      | With no load applied    |          | 0      |      |      |

|                          |                                                                                                                                   | LOWPOWER                                                                                                                                                                  | With no load applied                                                                 |                         | 0        |        | V    |      |

| Vt+-Vt-                  | Hysteresis                                                                                                                        | HOLD, RDY, TA0IN to TA4I<br>TB0IN to TB5IN, INTO to IN<br>ADTRG, CTS0 to CTS2, CL<br>TA0OUT to TA4OUT, KI0 to<br>SCL0 to SCL2, SDA0 to SD                                 | T5, NMI,<br>K <u>0 to</u> CLK4,<br>KI3, RXD0 to RXD2,                                |                         | 0.2      |        | 0.8  | V    |

| Vt+-Vt-                  | Hysteresis                                                                                                                        | RESET                                                                                                                                                                     |                                                                                      |                         | 0.2      | (0.7)  | 1.8  | V    |

| Ін                       | HIGH Input<br>Current <sup>(3)</sup>                                                                                              | P0_0 to P0_7, P1_0 to P1_<br>P3_0 to P3_7, P4_0 to P4_<br>P6_0 to P6_7, P7_0 to P7_<br>P9_0 to P9_7, P10_0 to P10<br>P12_0 to P12_7, P13_0 to F<br>XIN, RESET, CNVSS, BYT | 7, P5_0 to P5_7,<br>7, P8_0 to P8_7,<br>0_7, P11_0 to P11_7,<br>P13_7, P14_0, P14_1, | VI=3V                   |          |        | 4.0  | μΑ   |

| lıL                      | LOW Input<br>Current <sup>(3)</sup>                                                                                               | P0_0 to P0_7, P1_0 to P1_<br>P3_0 to P3_7, P4_0 to P4_<br>P6_0 to P6_7, P7_0 to P7_<br>P9_0 to P9_7, P10_0 to P1<br>P12_0 to P12_7, P13_0 to F1<br>XIN, RESET, CNVSS, BYT | 7, P5_0 to P5_7,<br>7, P8_0 to P8_7,<br>0_7, P11_0 to P11_7,<br>P13_7, P14_0, P14_1, | VI=0V                   |          |        | -4.0 | μΑ   |

| Rpullup                  | Pull-Up<br>Resistance<br>(3)                                                                                                      | P0_0 to P0_7, P1_0 to P1_<br>to P3_7, P4_0 to P4_7, P5_<br>P6_7, P7_2 to P7_7, P8_0<br>P9_0 to P9_7, P10_0 to P10<br>P11_0 to P11_7, P12_0 to P<br>P14_0, P14_1           | 0 to P5_7, P6_0 to<br>to P8_4, P8_6, P8_7,<br>0_7,                                   | VI=0V                   | 50       | 100    | 500  | kΩ   |

| Rfxin                    | Feedback Res                                                                                                                      | sistance XIN                                                                                                                                                              |                                                                                      |                         |          | 3.0    |      | MΩ   |

| Rfxcin                   | Feedback Res                                                                                                                      | sistance XCIN                                                                                                                                                             |                                                                                      |                         |          | 25     |      | MΩ   |

| Vram                     | RAM Retentio                                                                                                                      | n Voltage                                                                                                                                                                 | At stop mode                                                                         | 2.0                     |          |        | V    |      |

#### Table 5.30 Electrical Characteristics (1) (1)

NOTES:

1. Referenced to Vcc1 = Vcc2 = 2.7 to 3.3V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(XIN)=10MHz no wait unless otherwise specified.

2. Vcc1 for the port P6 to P11 and P14, and Vcc2 for the port P0 to P5 and P12 to P13

3. There is no external connections for port P1\_0 to P1\_7, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version.

#### **Switching Characteristics**

#### (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

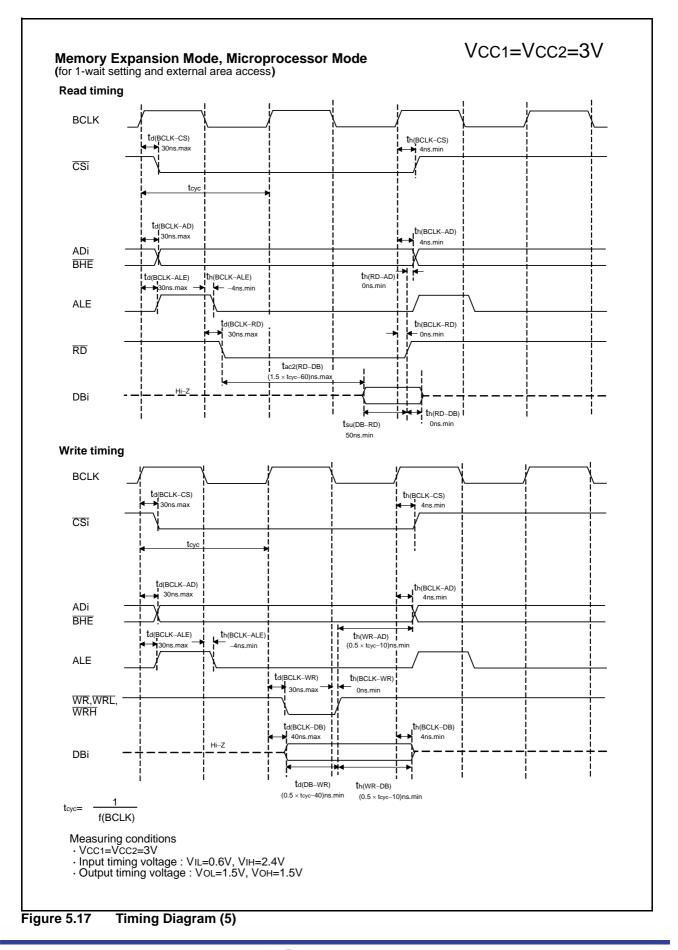

| Table 5.46 | Memory Expansion and Microprocessor Modes (for setting with no wait) |

|------------|----------------------------------------------------------------------|

|            | · · · · · · · · · · · · · · · · · · ·                                |

| Currente e l  | Parameter                                          |                 | Stan     | Unit |      |  |

|---------------|----------------------------------------------------|-----------------|----------|------|------|--|

| Symbol        | Falanielei                                         |                 |          | Max. | Unit |  |

| td(BCLK-AD)   | Address Output Delay Time                          |                 |          | 30   | ns   |  |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)     |                 | 4        |      | ns   |  |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)       |                 | 0        |      | ns   |  |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)       |                 | (NOTE 2) |      | ns   |  |

| td(BCLK-CS)   | Chip Select Output Delay Time                      |                 |          | 30   | ns   |  |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK) |                 | 4        |      | ns   |  |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                       |                 | 25       | ns   |      |  |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                        | -4              |          |      |      |  |

| td(BCLK-RD)   | RD Signal Output Delay Time                        | See Figure 5.12 |          | 30   | ns   |  |

| th(BCLK-RD)   | RD Signal Output Hold Time                         | I igure 5.12    | 0        |      | ns   |  |

| td(BCLK-WR)   | WR Signal Output Delay Time                        |                 |          | 30   | ns   |  |

| th(BCLK-WR)   | WR Signal Output Hold Time                         |                 | 0        |      |      |  |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)       |                 |          | 40   | ns   |  |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) (3)    |                 | 4        |      | ns   |  |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)         |                 | (NOTE 1) |      | ns   |  |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) (3)      |                 | (NOTE 2) |      | ns   |  |

| td(BCLK-HLDA) | HLDA Output Delay Time                             |                 |          | 40   | ns   |  |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 40[ns] \qquad f(BCLK) \text{ is } 12.5 \text{MHz or less.}$$

2. Calculated according to the BCLK frequency as follows:

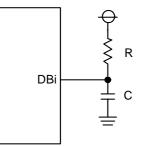

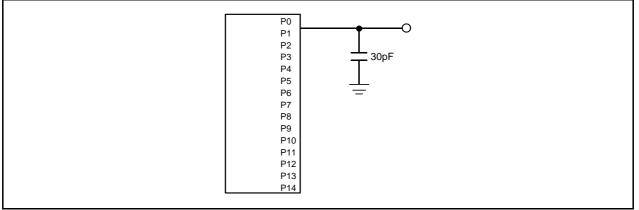

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in  $t = -CR X \ln (1 - VoL / VcC2)$ by a circuit of the right figure. For example, when VoL = 0.2Vcc2, C = 30pF, R = 1k\Omega, hold time of output "L" level is

t = -30pF X 1k  $\Omega$  X In(1-0.2Vcc2 / Vcc2)

= 6.7ns.

Figure 5.12 Ports P0 to P14 Measurement Circuit

#### Switching Characteristics

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

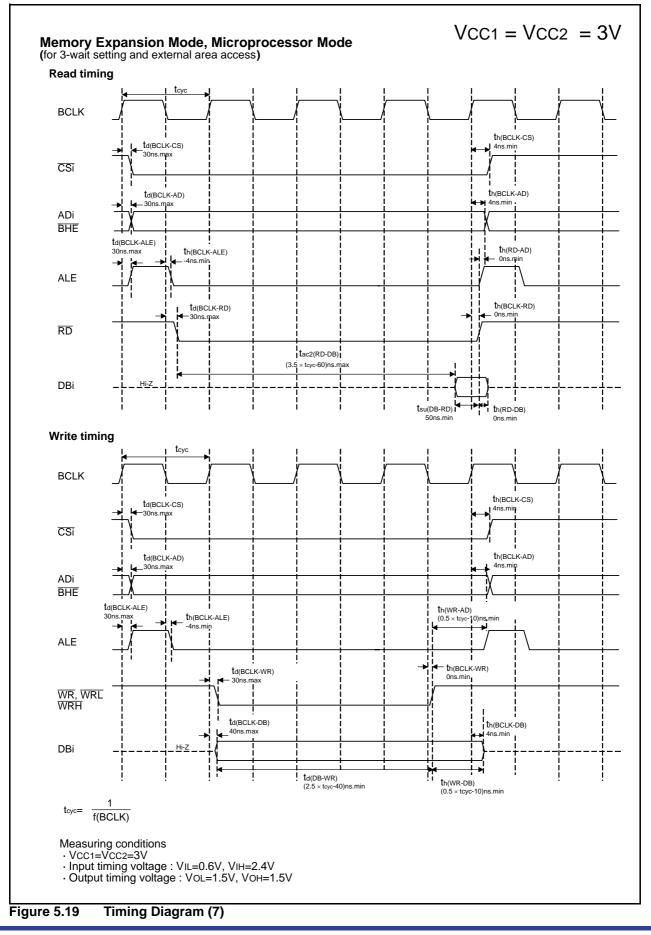

| Table 5.47 | Memory Expansion and Microprocessor Modes (for 1- to 3-wait setting and external |

|------------|----------------------------------------------------------------------------------|

|            | area access)                                                                     |

| Cumbal        | Deremeter                                                | Parameter          |          |      | Linit |

|---------------|----------------------------------------------------------|--------------------|----------|------|-------|

| Symbol        | Parameter                                                | Min.               | Max.     | Unit |       |

| td(BCLK-AD)   | Address Output Delay Time                                |                    |          | 30   | ns    |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)           |                    | 4        |      | ns    |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)             |                    | 0        |      | ns    |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)             |                    | (NOTE 2) |      | ns    |

| td(BCLK-CS)   | Chip Select Output Delay Time                            |                    |          | 30   | ns    |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)       |                    | 4        |      | ns    |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                             |                    |          |      |       |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                              |                    | -4       |      | ns    |

| td(BCLK-RD)   | RD Signal Output Delay Time                              | See<br>Figure 5.12 |          | 30   | ns    |

| th(BCLK-RD)   | RD Signal Output Hold Time                               |                    | 0        |      | ns    |

| td(BCLK-WR)   | WR Signal Output Delay Time                              |                    |          | 30   | ns    |

| th(BCLK-WR)   | WR Signal Output Hold Time                               | 0                  |          |      | ns    |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)             |                    |          | 40   | ns    |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) (3)          | 4                  |          | ns   |       |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)               |                    |          | ns   |       |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) <sup>(3)</sup> |                    | (NOTE 2) |      | ns    |

| td(BCLK-HLDA) | HLDA Output Delay Time                                   |                    |          | 40   | ns    |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5)x10^9}{f(\text{BCLK})} - 40[\text{ns}]$

n is "1" for 1-wait setting, "2" for 2-wait setting and "3" for 3-wait setting. (BCLK) is 12.5MHz or less.

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \text{x10}^9}{f(\text{BCLK})} - 10[\text{ns}]$$

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in t = -CR X ln (1-VoL / VCc2) by a circuit of the right figure. For example, when VoL = 0.2Vcc2, C = 30pF, R = 1kΩ, hold time of output "L" level is

> $t = -30pF X 1k\Omega X ln(1-0.2Vcc2 / Vcc2)$ = 6.7ns.

#### Switching Characteristics

.

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

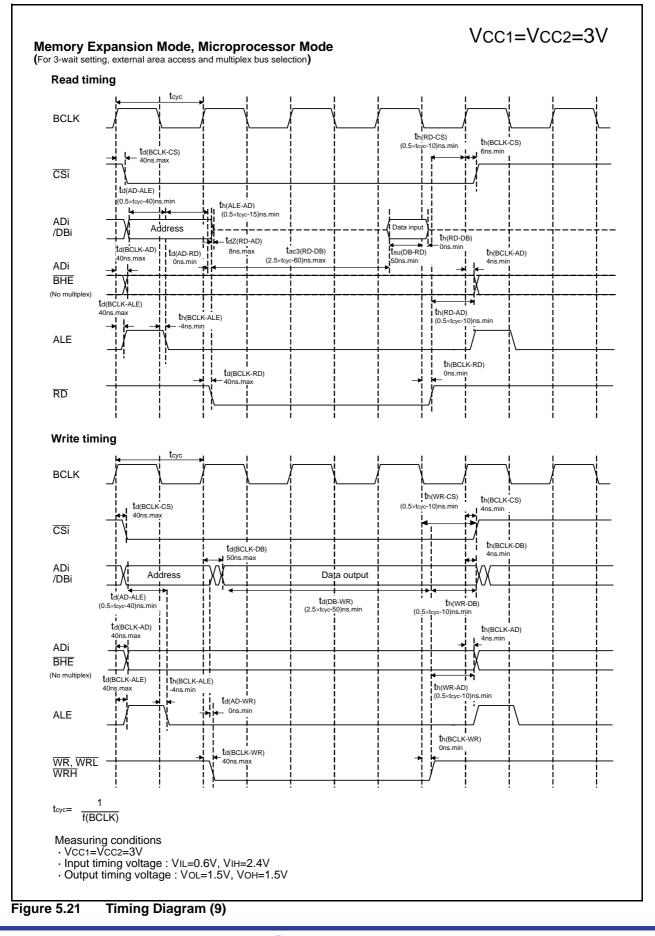

| Table 5.48 | Memory Expansion and Microprocessor Modes (for 2- to 3-wait setting, external area |  |  |  |  |

|------------|------------------------------------------------------------------------------------|--|--|--|--|

|            | access and multiplex bus selection)                                                |  |  |  |  |

| Symphol       | Parameter                                                     |             | Standard |        | l la it |

|---------------|---------------------------------------------------------------|-------------|----------|--------|---------|

| Symbol        | Parameter                                                     | Min.        | Max.     | - Unit |         |

| td(BCLK-AD)   | Address Output Delay Time                                     |             |          | 50     | ns      |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)                |             | 4        |        | ns      |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)                  |             | (NOTE 1) |        | ns      |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)                  |             | (NOTE 1) |        | ns      |

| td(BCLK-CS)   | Chip Select Output Delay Time                                 |             |          | 50     | ns      |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)            |             | 4        |        | ns      |

| th(RD-CS)     | Chip Select Output Hold Time (in relation to RD)              |             | (NOTE 1) |        | ns      |

| th(WR-CS)     | Chip Select Output Hold Time (in relation to WR)              |             | (NOTE 1) |        | ns      |

| td(BCLK-RD)   | RD Signal Output Delay Time                                   |             |          | 40     | ns      |

| th(BCLK-RD)   | RD Signal Output Hold Time                                    |             | 0        |        | ns      |

| td(BCLK-WR)   | WR Signal Output Delay Time                                   |             |          | 40     | ns      |

| th(BCLK-WR)   | WR Signal Output Hold Time                                    | See         | 0        |        | ns      |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)                  | Figure 5.12 |          | 50     | ns      |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK)                   |             | 4        |        | ns      |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)                    |             | (NOTE 2) |        | ns      |

| th(WR-DB)     | Data Output Hold Time (in relation to WR)                     |             | (NOTE 1) |        | ns      |

| td(BCLK-HLDA) | HLDA Output Delay Time                                        |             |          | 40     | ns      |

| td(BCLK-ALE)  | ALE Signal Output Delay Time (in relation to BCLK)            |             |          | 25     | ns      |

| th(BCLK-ALE)  | ALE Signal Output Hold Time (in relation to BCLK)             |             | -4       |        | ns      |

| td(AD-ALE)    | ALE Signal Output Delay Time (in relation to Address) (NOTE 3 |             |          |        | ns      |

| th(AD-ALE)    | ALE Signal Output Hold Time (in relation to Address)          |             | (NOTE 4) |        | ns      |

| td(AD-RD)     | RD Signal Output Delay From the End of Address                |             | 0        |        | ns      |

| td(AD-WR)     | WR Signal Output Delay From the End of Address                |             | 0        |        | ns      |

| tdz(RD-AD)    | Address Output Floating Start Time                            |             |          | 8      | ns      |

n is "2" for 2-wait setting, "3" for 3-wait setting.

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10[ns]$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 50[ns]$$

3. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(\text{BCLK})} - 40[\text{ns}]$$

4. Calculated according to the BCLK frequency as follows:

### 5.2 Electrical Characteristics (M16C/62PT)

| Symbol     |                      | Parameter                                                                                                                                                           | Condition                                                                | Rated Value                     | Unit |  |

|------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------|------|--|