Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                             |

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                             |

| Peripherals                | DMA, WDT                                                                        |

| Number of I/O              | 50                                                                              |

| Program Memory Size        | -                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30622spgp-u5c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1.3 Performance Outline of M16C/62P Group (M16C/62P, M16C/62PT)(80-pin version)

|                             | Item                                | Performance                                                                                                                                                                |                                                                                                     |  |  |  |  |

|-----------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

|                             |                                     | M16C/62P                                                                                                                                                                   | M16C/62PT <sup>(4)</sup>                                                                            |  |  |  |  |

| CPU                         | Number of Basic Instructions        | 91 instructions                                                                                                                                                            | W1700/021 1 ( )                                                                                     |  |  |  |  |

| 0.0                         | Minimum Instruction                 | 41.7ns(f(BCLK)=24MHz, VCC1=3.3 to 5.5V)                                                                                                                                    | 41.7ns(f(BCLK)=24MHz, VCC1=4.0 to 5.5V)                                                             |  |  |  |  |

|                             | Execution Time                      | 100ns(f(BCLK)=10MHz, VCC1=2.7 to 5.5V)                                                                                                                                     |                                                                                                     |  |  |  |  |

|                             | Operating Mode                      | Single-chip mode                                                                                                                                                           |                                                                                                     |  |  |  |  |

|                             | Address Space                       | 1 Mbyte                                                                                                                                                                    |                                                                                                     |  |  |  |  |

|                             | Memory Capacity                     | See Table 1.4 to 1.7 Product List                                                                                                                                          | st                                                                                                  |  |  |  |  |

| Peripheral                  | Port                                | Input/Output: 70 pins, Input: 1 pin                                                                                                                                        |                                                                                                     |  |  |  |  |

| Function                    | Multifunction Timer                 | Timer A: 16 bits x 5 channels (Time Timer B: 16 bits x 6 channels (Time                                                                                                    |                                                                                                     |  |  |  |  |

|                             | Serial Interface                    | 2 channels Clock synchronous, UART, I <sup>2</sup> C bu 1 channel Clock synchronous, I <sup>2</sup> C bus <sup>(1)</sup> , IE 2 channels Clock synchronous (1 channel is c | Bus <sup>(2)</sup>                                                                                  |  |  |  |  |

|                             | A/D Converter                       | 10-bit A/D converter: 1 circuit, 26 ch                                                                                                                                     | annels                                                                                              |  |  |  |  |

|                             | D/A Converter                       | 8 bits x 2 channels                                                                                                                                                        |                                                                                                     |  |  |  |  |

|                             | DMAC                                | 2 channels                                                                                                                                                                 |                                                                                                     |  |  |  |  |

|                             | CRC Calculation Circuit             | cuit CCITT-CRC                                                                                                                                                             |                                                                                                     |  |  |  |  |

|                             | Watchdog Timer                      | 15 bits x 1 channel (with prescaler)                                                                                                                                       |                                                                                                     |  |  |  |  |

|                             | Interrupt                           | Internal: 29 sources, External: 5 sources, Software: 4 sources, Priority level: 7 levels                                                                                   |                                                                                                     |  |  |  |  |

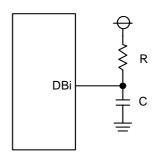

|                             | Clock Generation Circuit            | 4 circuits  Main clock generation circuit (*), Subclock generation circuit (*), On-chip oscillator, PLL synthesizer (*)Equipped with a built-in feedback resistor.         |                                                                                                     |  |  |  |  |

|                             | Oscillation Stop Detection Function | Stop detection of main clock oscillation, re-oscillation detection function                                                                                                |                                                                                                     |  |  |  |  |

|                             | Voltage Detection Circuit           |                                                                                                                                                                            | Absent                                                                                              |  |  |  |  |

| Electric<br>Characteristics | Supply Voltage                      | VCC1=3.0 to 5.5 V, (f(BCLK=24MHz)<br>VCC1=2.7 to 5.5 V, (f(BCLK=10MHz)                                                                                                     | VCC1=4.0 to 5.5V, (f(BCLK=24MHz)                                                                    |  |  |  |  |

|                             | Power Consumption                   | 14 mA (VCC1=5V, f(BCLK)=24MHz)<br>8 mA (VCC1=3V, f(BCLK)=10MHz)<br>1.8μA (VCC1=3V, f(XCIN)=32kHz,<br>wait mode)<br>0.7μA (VCC1=3V, stop mode)                              | 14 mA (VCC1=5V, f(BCLK)=24MHz) 2.0μA (VCC1=5V, f(XCIN)=32kHz, wait mode) 0.8μA (VCC1=5V, stop mode) |  |  |  |  |

| Flash memory                | Program/Erase Supply Voltage        | 3.3 ± 0.3V or 5.0 ± 0.5V                                                                                                                                                   | 5.0 ± 0.5V                                                                                          |  |  |  |  |

| version                     | Program and Erase<br>Endurance      | 100 times (all area) or 1,000 times (user ROM area without block A and block 1) / 10,000 times (block A, block 1) (3)                                                      |                                                                                                     |  |  |  |  |

| Operating Amb               | ient Temperature                    | -20 to 85°C,<br>-40 to 85°C (3) T version : -40 to 85°C<br>V version : -40 to 125°C                                                                                        |                                                                                                     |  |  |  |  |

| Package                     |                                     | 80-pin plastic mold QFP                                                                                                                                                    |                                                                                                     |  |  |  |  |

- 1. I<sup>2</sup>C bus is a registered trademark of Koninklijke Philips Electronics N. V.

- 2. IEBus is a registered trademark of NEC Electronics Corporation.

- 3. See **Table 1.8 and 1.9 Product Code** for the program and erase endurance, and operating ambient temperature.

- In addition 1,000 times/10,000 times are under development as of Jul., 2005. Please inquire about a release schedule.

- 4. All options are on request basis.

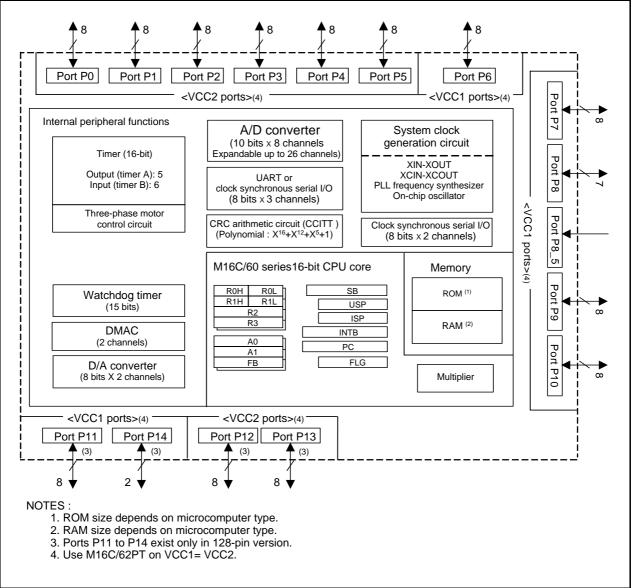

### 1.3 Block Diagram

Figure 1.1 is a M16C/62P Group (M16C/62P, M16C/62PT) 128-pin and 100-pin version Block Diagram, Figure 1.2 is a M16C/62P Group (M16C/62P, M16C/62PT) 80-pin version Block Diagram.

Figure 1.1 M16C/62P Group (M16C/62P, M16C/62PT) 128-pin and 100-pin version Block Diagram

Page 5 of 96

Table 1.5 Product List (2) (M16C/62P)

As of Dec. 2005

|                                |               | RAM       |                  |                  |

|--------------------------------|---------------|-----------|------------------|------------------|

| Type No.                       | ROM Capacity  | Capacity  | Package Type (1) | Remarks          |

| M30622MHP-XXXFP                | 384 Kbytes    | 16 Kbytes | PRQP0100JB-A     | Mask ROM version |

| M30622MHP-XXXGP                | 1             |           | PLQP0100KB-A     |                  |

| M30623MHP-XXXGP                | 1             |           | PLQP0128KB-A     |                  |

| M30624MHP-XXXFP                | 1             | 24 Kbytes | PRQP0100JB-A     |                  |

| M30624MHP-XXXGP                | 1             |           | PLQP0100KB-A     |                  |

| M30625MHP-XXXGP                | 1             |           | PLQP0128KB-A     |                  |

| M30626MHP-XXXFP                | 1             | 31 Kbytes | PRQP0100JB-A     |                  |

| M30626MHP-XXXGP                | 7             |           | PLQP0100KB-A     |                  |

| M30627MHP-XXXGP                | 1             |           | PLQP0128KB-A     |                  |

| M30626MJP-XXXFP (D)            | 512 Kbytes    | 31 Kbytes | PRQP0100JB-A     |                  |

| M30626MJP-XXXGP (D)            | 7             |           | PLQP0100KB-A     |                  |

| M30627MJP-XXXGP (D)            | 1             |           | PLQP0128KB-A     |                  |

| M30622F8PFP                    | 64K+4 Kbytes  | 4 Kbytes  | PRQP0100JB-A     | Flash memory     |

| M30622F8PGP                    | 7             |           | PLQP0100KB-A     | version (2)      |

| M30623F8PGP                    | 1             |           | PRQP0080JA-A     |                  |

| M30620FCPFP                    | 128K+4 Kbytes | 10 Kbytes | PRQP0100JB-A     |                  |

| M30620FCPGP                    | 7             |           | PLQP0100KB-A     |                  |

| M30621FCPGP                    | 7             |           | PRQP0080JA-A     |                  |

| M3062LFGPFP <sup>(3)</sup> (D) | 256K+4 Kbytes | 20 Kbytes | PRQP0100JB-A     |                  |

| M3062LFGPGP <sup>(3)</sup> (D) | 1             |           | PLQP0100KB-A     |                  |

| M30625FGPGP                    |               |           | PLQP0128KB-A     |                  |

| M30626FHPFP                    | 384K+4 Kbytes | 31 Kbytes | PRQP0100JB-A     |                  |

| M30626FHPGP                    | -             |           | PLQP0100KB-A     |                  |

| M30627FHPGP                    | 1             |           | PLQP0128KB-A     |                  |

| M30626FJPFP                    | 512K+4 Kbytes | 31 Kbytes | PRQP0100JB-A     |                  |

| M30626FJPGP                    | 1             |           | PLQP0100KB-A     |                  |

| M30627FJPGP                    | 1             |           | PLQP0128KB-A     |                  |

| M30622SPFP                     | _             | 4 Kbytes  | PRQP0100JB-A     | ROM-less version |

| M30622SPGP                     | 1             |           | PLQP0100KB-A     |                  |

| M30620SPFP                     | 1             | 10 Kbytes | PRQP0100JB-A     | 1                |

| M30620SPGP                     | 7             |           | PLQP0100KB-A     | 1                |

| M30624SPFP (D)                 | _             | 20 Kbytes | PRQP0100JB-A     | 1                |

| M30624SPGP (D)                 | 1             |           | PLQP0100KB-A     | 1                |

| M30626SPFP (D)                 | 7             | 31 Kbytes | PRQP0100JB-A     | 1                |

| M30626SPGP (D)                 |               |           | PLQP0100KB-A     |                  |

(D): Under development

#### NOTES:

1. The old package type numbers of each package type are as follows.

PLQP0128KB-A: 128P6Q-A, PRQP0100JB-A: 100P6S-A, PLQP0100KB-A: 100P6Q-A, PRQP0080JA-A: 80P6S-A

2. In the flash memory version, there is 4K bytes area (block A).

3. Please use M3062LFGPFP and M3062LFGPGP for your new system instead of M30624FGPFP and M30624FGPGP. The M16C/62P Group (M16C/62P, M16C/62PT) hardware manual is still good for M30624FGPFP and M30624FGPGP.

| M30624FGPFP | 256K+4 Kbytes | 20 Kbytes | PRQP0100JB-A | Flash memory version |

|-------------|---------------|-----------|--------------|----------------------|

| M30624FGPGP |               |           | PLQP0100KB-A |                      |

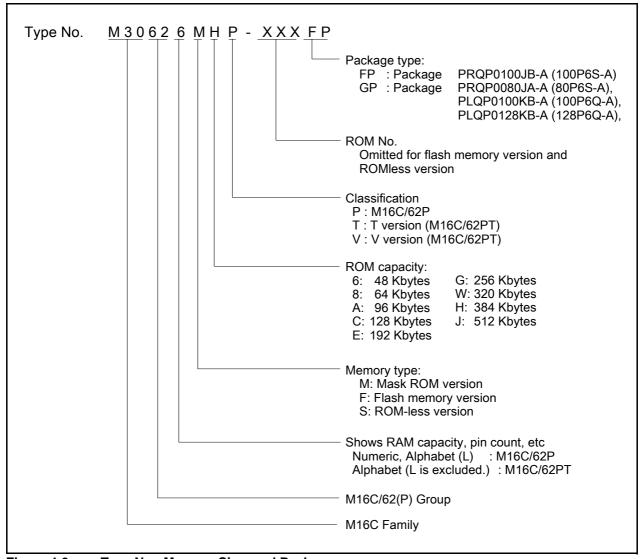

Figure 1.3 Type No., Memory Size, and Package

**Table 1.11** Pin Characteristics for 128-Pin Package (2)

| Pin No. | Control Pin |              | Interrupt Pin | Timer Pin | UART Pin | Analog Pin | Bus Control Pi |

|---------|-------------|--------------|---------------|-----------|----------|------------|----------------|

| 51      |             | P5_6         |               |           |          |            | ALE            |

| 52      |             | P5_5         |               |           |          |            | HOLD           |

| 53      |             | P5_4         |               |           |          |            | HLDA           |

| 54      |             | P13_3        |               |           |          |            |                |

| 55      |             | P13_2        |               |           |          |            |                |

| 56      |             | P13_1        |               |           |          |            |                |

| 57      |             | P13_0        |               |           |          |            |                |

| 58      |             | P5_3         |               |           |          |            | BCLK           |

| 59      |             | P5_2         |               |           |          |            | RD             |

| 60      |             | P5_1         |               |           |          |            | WRH/BHE        |

| 61      |             | P5_0         |               |           |          |            | WRL/WR         |

| 62      |             | P12_7        |               |           |          |            |                |

| 63      |             | P12_6        |               |           |          |            |                |

| 64      |             | P12_5        |               |           |          |            |                |

| 65      |             | P4_7         |               |           |          |            | CS3            |

| 66      |             | P4_6         |               |           |          |            | CS2            |

| 67      |             | P4_5         |               |           |          |            | CS1            |

| 68      |             | P4_4         |               |           |          |            | CS0            |

| 69      |             | P4_4<br>P4_3 |               |           |          |            | A19            |

| 70      |             | P4_3<br>P4_2 |               |           |          |            | A18            |

| 71      |             | P4_2<br>P4_1 |               |           |          |            | A17            |

| 72      |             | P4_0         |               |           |          |            | A16            |

| 73      |             | P3_7         |               |           |          |            | A15            |

| 74      |             | P3_6         |               |           |          |            | A14            |

| 75      |             | P3_5         |               |           |          |            | A13            |

| 76      |             | P3_4         |               |           |          |            | A12            |

| 77      |             | P3_3         |               |           |          |            | A11            |

| 78      |             | P3_2         |               |           |          |            | A10            |

| 79      |             | P3_1         |               |           |          |            | A9             |

| 80      |             | P12_4        |               |           |          |            |                |

| 81      |             | P12_3        |               |           |          |            |                |

| 82      |             | P12_2        |               |           |          |            |                |

| 83      |             | P12_1        |               |           |          |            |                |

| 84      |             | P12_0        |               |           |          |            |                |

| 85      | VCC2        |              |               |           |          |            |                |

| 86      |             | P3_0         |               |           |          |            | A8(/-/D7)      |

| 87      | VSS         |              |               |           |          |            |                |

| 88      |             | P2_7         |               |           |          | AN2_7      | A7(/D7/D6)     |

| 89      |             | P2_6         |               |           |          | AN2_6      | A6(/D6/D5)     |

| 90      |             | P2_5         |               |           |          | AN2_5      | A5(/D5/D4)     |

| 91      |             | P2_4         |               |           |          | AN2_4      | A4(/D4/D3)     |

| 92      |             | P2_3         |               |           |          | AN2_3      | A3(/D3/D2)     |

| 93      |             | P2_2         |               |           |          | AN2_2      | A2(/D2/D1)     |

| 94      |             | P2_1         |               |           |          | AN2_1      | A1(/D1/D0)     |

| 95      |             | P2_0         | <u> </u>      |           |          | AN2_0      | A0(/D0/-)      |

| 96      |             | P1_7         | ĪNT5          |           |          |            | D15            |

| 97      |             | P1_6         | ĪNT4          |           |          |            | D14            |

| 98      |             | P1_5         | ĪNT3          |           |          |            | D13            |

| 99      |             | P1_4         |               |           |          |            | D12            |

| 100     |             | P1_3         |               |           |          |            | D11            |

Pin Characteristics for 128-Pin Package (3) **Table 1.12**

| Pin No. | Control Pin | Port  | Interrupt Pin | Timer Pin | UART Pin | Analog Pin | Bus Control Pin |

|---------|-------------|-------|---------------|-----------|----------|------------|-----------------|

| 101     |             | P1_2  |               |           |          |            | D10             |

| 102     |             | P1_1  |               |           |          |            | D9              |

| 103     |             | P1_0  |               |           |          |            | D8              |

| 104     |             | P0_7  |               |           |          | AN0_7      | D7              |

| 105     |             | P0_6  |               |           |          | AN0_6      | D6              |

| 106     |             | P0_5  |               |           |          | AN0_5      | D5              |

| 107     |             | P0_4  |               |           |          | AN0_4      | D4              |

| 108     |             | P0_3  |               |           |          | AN0_3      | D3              |

| 109     |             | P0_2  |               |           |          | AN0_2      | D2              |

| 110     |             | P0_1  |               |           |          | AN0_1      | D1              |

| 111     |             | P0_0  |               |           |          | AN0_0      | D0              |

| 112     |             | P11_7 |               |           |          |            |                 |

| 113     |             | P11_6 |               |           |          |            |                 |

| 114     |             | P11_5 |               |           |          |            |                 |

| 115     |             | P11_4 |               |           |          |            |                 |

| 116     |             | P11_3 |               |           |          |            |                 |

| 117     |             | P11_2 |               |           |          |            |                 |

| 118     |             | P11_1 |               |           |          |            |                 |

| 119     |             | P11_0 |               |           |          |            |                 |

| 120     |             | P10_7 | KI3           |           |          | AN7        |                 |

| 121     |             | P10_6 | KI2           |           |          | AN6        |                 |

| 122     |             | P10_5 | KI1           |           |          | AN5        |                 |

| 123     |             | P10_4 | KI0           |           |          | AN4        |                 |

| 124     |             | P10_3 |               |           |          | AN3        |                 |

| 125     |             | P10_2 |               |           |          | AN2        |                 |

| 126     |             | P10_1 |               |           |          | AN1        |                 |

| 127     | AVSS        |       |               |           |          |            |                 |

| 128     |             | P10_0 |               |           |          | AN0        |                 |

Table 1.21 Pin Description (80-pin Version) (2)

| Signal Name             | Pin Name                                                                                               | I/O  | Power                         | Description                                                                                                                                                                                                             |

|-------------------------|--------------------------------------------------------------------------------------------------------|------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference voltage input | VREF                                                                                                   | Type | Supply <sup>(1)</sup><br>VCC1 | Applies the reference voltage for the A/D converter and D/A converter.                                                                                                                                                  |

| A/D converter           | AN0 to AN7,<br>AN0_0 to<br>AN0_7,<br>AN2_0 to<br>AN2_7                                                 | I    | VCC1                          | Analog input pins for the A/D converter.                                                                                                                                                                                |

|                         | ADTRG                                                                                                  | I    | VCC1                          | This is an A/D trigger input pin.                                                                                                                                                                                       |

|                         | ANEX0                                                                                                  | I/O  | VCC1                          | This is the extended analog input pin for the A/D converter, and is the output in external op-amp connection mode.                                                                                                      |

|                         | ANEX1                                                                                                  | I    | VCC1                          | This is the extended analog input pin for the A/D converter.                                                                                                                                                            |

| D/A converter           | DA0, DA1                                                                                               | 0    | VCC1                          | This is the output pin for the D/A converter.                                                                                                                                                                           |

| I/O port <sup>(1)</sup> | P0_0 to P0_7,<br>P2_0 to P2_7,<br>P3_0 to P3_7,<br>P5_0 to P5_7,<br>P6_0 to P6_7,<br>P10_0 to<br>P10_7 | I/O  | VCC1                          | 8-bit I/O ports in CMOS, having a direction register to select an input or output.  Each pin is set as an input port or output port. An input port can be set for a pull-up or for no pull-up in 4-bit unit by program. |

|                         | P8_0 to P8_4,<br>P8_6, P8_7,<br>P9_0,<br>P9_2 to P9_7                                                  | I/O  | VCC1                          | I/O ports having equivalent functions to P0.                                                                                                                                                                            |

|                         | P4_0 to P4_3,<br>P7_0, P7_1,<br>P7_6, P7_7                                                             | I/O  | VCC1                          | I/O ports having equivalent functions to P0. (however, output of P7_0 and P7_1 for the N-channel open drain output.)                                                                                                    |

| Input port              | P8_5                                                                                                   | I    | VCC1                          | Input pin for the NMI interrupt. Pin states can be read by the P8_5 bit in the P8 register.                                                                                                                             |

I: Input O: Output I/O: Input and output

#### NOTES:

1. There is no external connections for port P1, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version. Set the direction bits in these ports to "1" (output mode), and set the output data to "0" ("L") using the program.

Recommended Operating Conditions (1) (1) Table 5.2

| Symbol     |                 | Parameter                                                    |           | Standard |          |      |  |

|------------|-----------------|--------------------------------------------------------------|-----------|----------|----------|------|--|

| Symbol     |                 | Parameter                                                    | Min.      | Тур.     | Max.     | Unit |  |

| VCC1, VCC2 | Supply Voltage  | (Vcc1 ≥ Vcc2)                                                | 2.7       | 5.0      | 5.5      | V    |  |

| AVcc       | Analog Supply V | /oltage                                                      |           | Vcc1     |          | V    |  |

| Vss        | Supply Voltage  | ·                                                            |           | 0        |          | V    |  |

| AVss       | Analog Supply \ | Voltage                                                      |           | 0        |          | V    |  |

| ViH        | HIGH Input      | P3 1 to P3 7, P4 0 to P4 7, P5 0 to P5 7,                    | 0.8Vcc2   | -        | VCC2     | V    |  |

| VIII       | Voltage         | P12_0 to P12_7, P13_0 to P13_7                               | 0.67002   |          | VCC2     | V    |  |

|            | , onage         | P0 0 to P0 7, P1 0 to P1 7, P2 0 to P2 7, P3 0               | 0.8Vcc2   |          | VCC2     | V    |  |

|            |                 | (during single-chip mode)                                    | 0.0 0 002 |          | V 002    | •    |  |

|            |                 | P0 0 to P0 7, P1 0 to P1 7, P2 0 to P2 7, P3 0               | 0.5Vcc2   |          | VCC2     | V    |  |

|            |                 | (data input during memory expansion and microprocessor mode) | 0.01002   |          | 1 002    | ,    |  |

|            |                 | P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_7, P9_0 to P9_7,      | 0.8Vcc1   |          | Vcc1     | V    |  |

|            |                 | P10_0 to P10_7, P11_0 to P11_7, P14_0, P14_1,                |           |          |          |      |  |

|            |                 | XIN, RESET, CNVSS, BYTE                                      |           |          |          |      |  |

|            |                 | P7_0, P7_1                                                   | 0.8Vcc1   |          | 6.5      | V    |  |

| VIL        | LOW Input       | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7,                    | 0         |          | 0.2Vcc2  | V    |  |

|            | Voltage         | P12_0 to P12_7, P13_0 to P13_7                               |           |          |          |      |  |

|            |                 | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0               | 0         |          | 0.2Vcc2  | V    |  |

|            |                 | (during single-chip mode)                                    |           |          |          |      |  |

|            |                 | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0               | 0         |          | 0.16Vcc2 | V    |  |

|            |                 | (data input during memory expansion and microprocessor mode) |           |          |          |      |  |

|            |                 | P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7,      | 0         |          | 0.2Vcc   | V    |  |

|            |                 | P10_0 to P10_7, P11_0 to P11_7, P14_0, P14_1,                |           |          |          |      |  |

|            |                 | XIN, RESET, CNVSS, BYTE                                      |           |          |          |      |  |

| IOH(peak)  | HIGH Peak       | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,      |           |          | -10.0    | mA   |  |

|            | Output Current  | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,      |           |          |          |      |  |

|            |                 | P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,      |           |          |          |      |  |

|            |                 | P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |           |          |          |      |  |

| IOH(avg)   | HIGH Average    | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,      |           |          | -5.0     | mA   |  |

|            | Output Current  | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,      |           |          |          |      |  |

|            |                 | P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,      |           |          |          |      |  |

|            |                 | P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |           |          |          |      |  |

| IOL(peak)  | LOW Peak        | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,      |           |          | 10.0     | mA   |  |

|            | Output Current  | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,      |           |          |          |      |  |

|            |                 | P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,      |           |          |          |      |  |

|            |                 | P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |           |          |          |      |  |

| IOL(avg)   | LOW Average     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,      |           |          | 5.0      | mA   |  |

|            | Output Current  | P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,      |           |          |          |      |  |

|            |                 | P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,      |           |          |          |      |  |

|            |                 | P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |           |          |          |      |  |

- 1. Referenced to Vcc1 = Vcc2 = 2.7 to 5.5V at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified.

- 2. The Average Output Current is the mean value within 100ms.

- 3. The total IoL(peak) for ports P0, P1, P2, P8\_6, P8\_7, P9, P10, P11, P14\_0, and P14\_1 must be 80mA max. The total IoL(peak) for ports P3, P4, P5, P6, P7, P8\_0 to P8\_4, P12, and P13 must be 80mA max. The total IOH(peak) for ports P0, P1, and P2 must be -40mA max. The total IoH(peak) for ports P3, P4, P5, P12, and P13 must be -40mA max. The total IoH(peak) for ports P6, P7, and P8\_0 to P8\_4 must be -40mA max. The total IOH(peak) for ports P8\_6, P8\_7, P9, P10, P14\_0, and P14\_1 must be -40mA max. Set Average Output Current to 1/2 of peak. The total IOH(peak) for ports P8\_6, P8\_7, P9, P10, P11, P14\_0, and P14\_1 must be -40mA max.

- As for 80-pin version, the total IoL(peak) for all ports and IoH(peak) must be 80mA. max. due to one Vcc and one Vss.

- 4. There is no external connections for port P1\_0 to P1\_7, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version.

Table 5.4 A/D Conversion Characteristics (1)

| Symbol  | Parame                                | tor           |                        | Measuring Condition                                                                       |      | Standard |      |      |

|---------|---------------------------------------|---------------|------------------------|-------------------------------------------------------------------------------------------|------|----------|------|------|

| Symbol  | Faiaille                              | , aramotor    |                        | 3                                                                                         | Min. | Тур.     | Max. | Unit |

| -       | Resolution                            |               | VREF=V                 | /CC1                                                                                      |      |          | 10   | Bits |

| INL     | Integral Non-Linearity<br>Error       | 10bit         | VREF=<br>VCC1=<br>5V   | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input |      |          | ±3   | LSB  |

|         |                                       |               |                        | External operation amp connection mode                                                    |      |          | ±7   | LSB  |

|         |                                       |               | VREF=<br>VCC1=<br>3.3V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input |      |          | ±5   | LSB  |

|         |                                       |               |                        | External operation amp connection mode                                                    |      |          | ±7   | LSB  |

|         |                                       | 8bit          | VREF=V                 | /cc1=5V, 3.3V                                                                             |      |          | ±2   | LSB  |

| _       | Absolute Accuracy                     | 10bit         | VREF=<br>VCC1=<br>5V   | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input |      |          | ±3   | LSB  |

|         |                                       |               |                        | External operation amp connection mode                                                    |      |          | ±7   | LSB  |

|         |                                       |               | VREF=<br>VCC1<br>=3.3V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>AN2_0 to AN2_7 input,<br>ANEX0, ANEX1 input |      |          | ±5   | LSB  |

|         |                                       |               |                        | External operation amp connection mode                                                    |      |          | ±7   | LSB  |

|         |                                       | 8bit          | VREF=V                 | /cc1=5V, 3.3V                                                                             |      |          | ±2   | LSB  |

| =       | Tolerance Level Impeda                | ance          |                        |                                                                                           |      | 3        |      | kΩ   |

| DNL     | Differential Non-Linearit             | y Error       |                        |                                                                                           |      |          | ±1   | LSB  |

| -       | Offset Error                          |               |                        |                                                                                           |      |          | ±3   | LSB  |

| _       | Gain Error                            |               |                        |                                                                                           |      |          | ±3   | LSB  |

| RLADDER | Ladder Resistance                     |               | VREF=V                 | /cc1                                                                                      | 10   |          | 40   | kΩ   |

| tconv   | 10-bit Conversion Time,<br>Available  | •             | VREF=V                 | /cc1=5V, φAD=12MHz                                                                        | 2.75 |          |      | μS   |

| tconv   | 8-bit Conversion Time, S<br>Available | Sample & Hold | VREF=V                 | /cc1=5V, φAD=12MHz                                                                        | 2.33 |          |      | μS   |

| tsamp   | Sampling Time                         |               |                        |                                                                                           | 0.25 |          |      | μS   |

| VREF    | Reference Voltage                     |               |                        |                                                                                           | 2.0  |          | Vcc1 | V    |

| VIA     | Analog Input Voltage                  |               |                        |                                                                                           | 0    |          | VREF | V    |

- 1. Referenced to Vcc1=AVcc=VREF=3.3 to 5.5V, Vss=AVss=0V at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified.

- 2. If Vcc1 > Vcc2, do not use AN0\_0 to AN0\_7 and AN2\_0 to AN2\_7 as analog input pins.

- 3. φAD frequency must be 12 MHz or less. And divide the fAD if Vcc1 is less than 4.0V, and φAD frequency into 10 MHz or less.

- When sample & hold is disabled, φAD frequency must be 250 kHz or more, in addition to the limitation in Note 3.

When sample & hold is enabled, φAD frequency must be 1MHz or more, in addition to the limitation in Note 3.

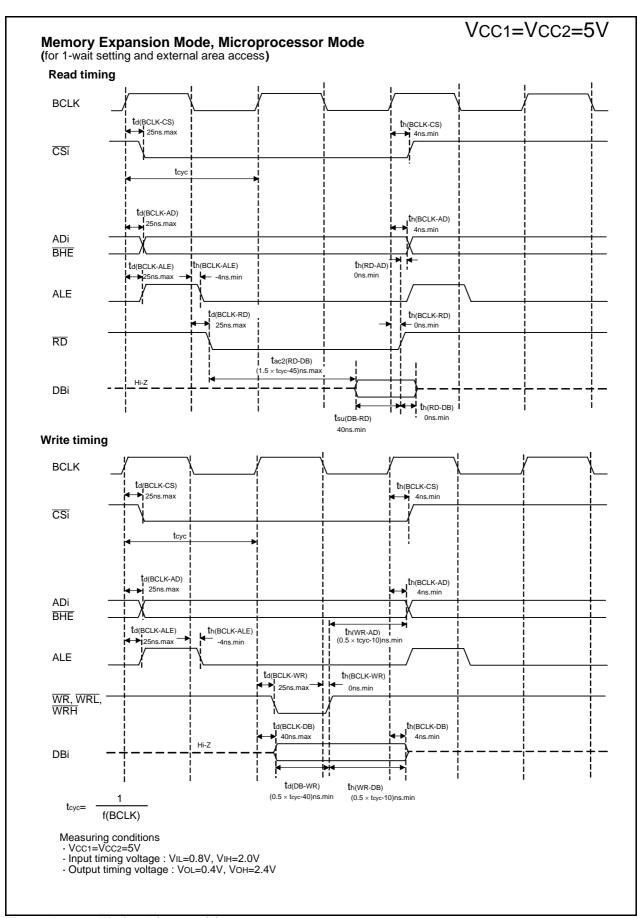

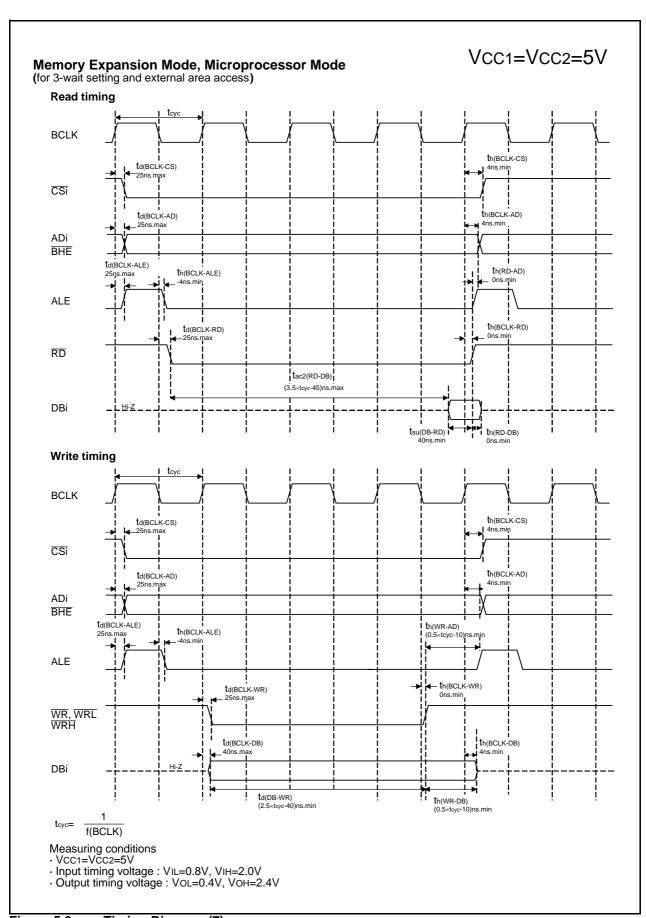

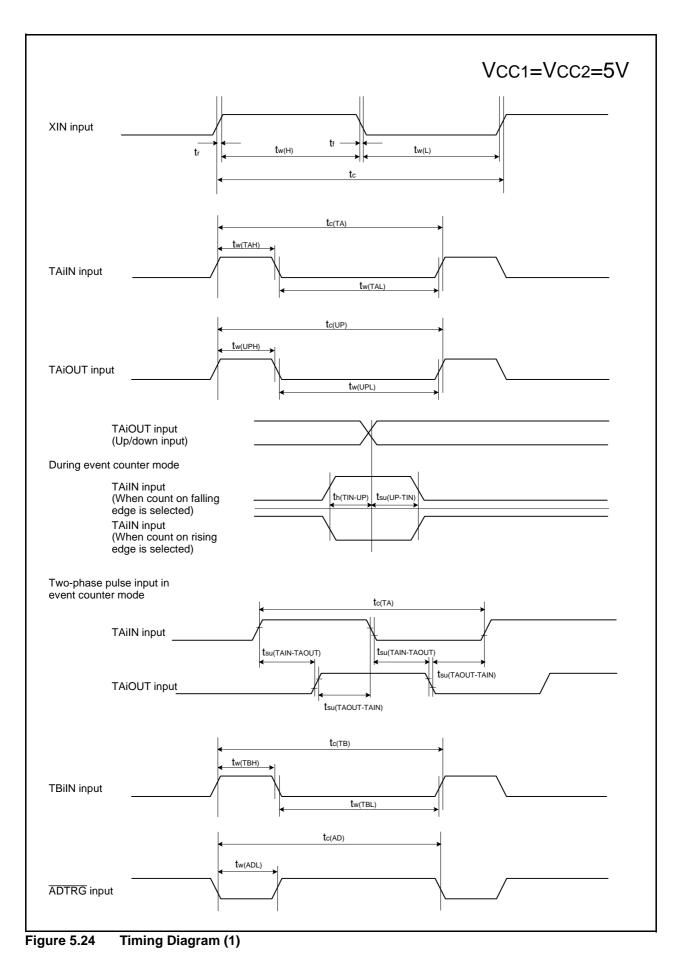

# VCC1=VCC2=5V

#### **Timing Requirements**

(VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

Table 5.21 Timer B Input (Counter Input in Event Counter Mode)

| Symbol  | Parameter                                            | Stan | Unit |       |

|---------|------------------------------------------------------|------|------|-------|

|         | Falanielei                                           | Min. | Max. | Offic |

| tc(TB)  | TBilN Input Cycle Time (counted on one edge)         | 100  |      | ns    |

| tw(TBH) | TBilN Input HIGH Pulse Width (counted on one edge)   | 40   |      | ns    |

| tw(TBL) | TBiIN Input LOW Pulse Width (counted on one edge)    | 40   |      | ns    |

| tc(TB)  | TBilN Input Cycle Time (counted on both edges)       | 200  |      | ns    |

| tw(TBH) | TBilN Input HIGH Pulse Width (counted on both edges) | 80   |      | ns    |

| tw(TBL) | TBilN Input LOW Pulse Width (counted on both edges)  | 80   |      | ns    |

### Table 5.22 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Stan | Unit |       |

|---------|------------------------------|------|------|-------|

|         | Falameter                    | Min. | Max. | Offic |

| tc(TB)  | TBilN Input Cycle Time       | 400  |      | ns    |

| tw(TBH) | TBilN Input HIGH Pulse Width | 200  |      | ns    |

| tw(TBL) | TBiIN Input LOW Pulse Width  | 200  |      | ns    |

#### Table 5.23 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                    | Stan | Unit |       |

|---------|------------------------------|------|------|-------|

| Symbol  | Falanielei                   | Min. | Max. | Offic |

| tc(TB)  | TBilN Input Cycle Time       | 400  |      | ns    |

| tw(TBH) | TBilN Input HIGH Pulse Width | 200  |      | ns    |

| tw(TBL) | TBilN Input LOW Pulse Width  | 200  |      | ns    |

### Table 5.24 A/D Trigger Input

| Symbol  | Symbol Parameter -          |      | Standard |      |  |

|---------|-----------------------------|------|----------|------|--|

| Symbol  |                             |      | Max.     | Unit |  |

| tc(AD)  | ADTRG Input Cycle Time      | 1000 |          | ns   |  |

| tw(ADL) | ADTRG input LOW Pulse Width | 125  |          | ns   |  |

#### Table 5.25 Serial Interface

| Symbol   | Parameter                   | Star | Unit |       |

|----------|-----------------------------|------|------|-------|

| Symbol   | Falanetei                   | Min. | Max. | Offic |

| tc(CK)   | CLKi Input Cycle Time       | 200  |      | ns    |

| tw(CKH)  | CLKi Input HIGH Pulse Width | 100  |      | ns    |

| tw(CKL)  | CLKi Input LOW Pulse Width  | 100  |      | ns    |

| td(C-Q)  | TXDi Output Delay Time      |      | 80   | ns    |

| th(C-Q)  | TXDi Hold Time              | 0    |      | ns    |

| tsu(D-C) | RXDi Input Setup Time       | 70   |      | ns    |

| th(C-D)  | RXDi Input Hold Time        | 90   |      | ns    |

### Table 5.26 External Interrupt INTi Input

| Symbol  | Parameter                   | Stan | Unit |       |

|---------|-----------------------------|------|------|-------|

| Symbol  | Symbol                      |      | Max. | Offic |

| tw(INH) | INTi Input HIGH Pulse Width | 250  |      | ns    |

| tw(INL) | INTi Input LOW Pulse Width  | 250  |      | ns    |

Figure 5.9 Timing Diagram (7)

# VCC1=VCC2=3V

Table 5.30 Electrical Characteristics (1) (1)

| Symbol  | Parameter                                                                                                                                |                                                                                                                                                                                                                                                                            |                      | Measuring Condition  | Standard |       |       | Unit |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------|-------|-------|------|

| Symbol  |                                                                                                                                          | raiaiiielei                                                                                                                                                                                                                                                                | wiedsuring Condition | Min.                 | Тур.     | Max.  | Uiill |      |

| Vон     | HIGH Output Voltage (3) P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7, P11_0 to P11_7, P14_0, P14_1 |                                                                                                                                                                                                                                                                            |                      | IOH=-1mA             | Vcc1-0.5 |       | Vcc1  | V    |

|         |                                                                                                                                          | P0_0 to P0_7, P1_0 to P1_7<br>P3_0 to P3_7, P4_0 to P4_7<br>P12_0 to P12_7, P13_0 to F                                                                                                                                                                                     | IOH=-1mA (2)         | Vcc2-0.5             |          | VCC2  |       |      |

| Vон     | HIGH Output                                                                                                                              | Voltage XOUT                                                                                                                                                                                                                                                               | HIGHPOWER            | IOH=-0.1mA           | Vcc1-0.5 |       | Vcc1  | V    |

|         |                                                                                                                                          |                                                                                                                                                                                                                                                                            | LOWPOWER             | IOH=-50μA            | Vcc1-0.5 |       | Vcc1  | , v  |

|         | HIGH Output                                                                                                                              | Voltage XCOUT                                                                                                                                                                                                                                                              | HIGHPOWER            | With no load applied |          | 2.5   |       | V    |

|         |                                                                                                                                          |                                                                                                                                                                                                                                                                            | LOWPOWER             | With no load applied |          | 1.6   |       | V    |

| Vol     | LOW Output<br>Voltage (3)                                                                                                                | P6_0 to P6_7, P7_0 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P1                                                                                                                                                                                       | P10_0 to P10_7,      | IOL=1mA              |          |       | 0.5   | V    |

|         |                                                                                                                                          | P0_0 to P0_7, P1_0 to P1_<br>P3_0 to P3_7, P4_0 to P4_1<br>P12_0 to P12_7, P13_0 to P                                                                                                                                                                                      | 7, P5 0 to P5 7,     | IOL=1mA (2)          |          |       | 0.5   | V    |

| Vol     | LOW Output \                                                                                                                             | /oltage XOUT                                                                                                                                                                                                                                                               | HIGHPOWER            | IOL=0.1mA            |          |       | 0.5   | V    |

| -       |                                                                                                                                          |                                                                                                                                                                                                                                                                            | IOL=50μA             |                      |          | 0.5   | \ \   |      |

|         | LOW Output \                                                                                                                             | /oltage XCOUT                                                                                                                                                                                                                                                              | With no load applied |                      | 0        |       | V     |      |

|         | LOWPOWER                                                                                                                                 |                                                                                                                                                                                                                                                                            |                      | With no load applied |          | 0     |       | V    |

| VT+-VT- | Hysteresis                                                                                                                               | HOLD, RDY, TA0IN to TA4I TB0IN to TB5IN, INTO to IN ADTRG, CTS0 to CTS2, CL TA0OUT to TA4OUT, KI0 to SCL0 to SCL2, SDA0 to SD                                                                                                                                              |                      | 0.2                  |          | 0.8   | V     |      |

| VT+-VT- | Hysteresis                                                                                                                               | RESET                                                                                                                                                                                                                                                                      |                      |                      | 0.2      | (0.7) | 1.8   | V    |

| Іін     | HIGH Input<br>Current (3)                                                                                                                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7, P10_0 to P10_7, P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1,                                                  |                      | VI=3V                |          |       | 4.0   | μА   |

| li∟     | LOW Input<br>Current (3)                                                                                                                 | XIN, RESET, CNVSS, BYTE  P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7, P10_0 to P10_7, P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1, XIN, RESET, CNVSS, BYTE |                      | VI=0V                |          |       | -4.0  | μА   |

| RPULLUP | Pull-Up<br>Resistance<br>(3)                                                                                                             | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 e to P3_7, P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7, P11_0 to P11_7,P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1                                      |                      | VI=0V                | 50       | 100   | 500   | kΩ   |

| RfXIN   | Feedback Res                                                                                                                             | sistance XIN                                                                                                                                                                                                                                                               |                      |                      |          | 3.0   |       | МΩ   |

| RfXCIN  | Feedback Res                                                                                                                             | sistance XCIN                                                                                                                                                                                                                                                              |                      |                      |          | 25    |       | МΩ   |

| VRAM    | RAM Retentio                                                                                                                             | n Voltage                                                                                                                                                                                                                                                                  |                      | At stop mode         | 2.0      |       |       | V    |

- 1. Referenced to Vcc1 = Vcc2 = 2.7 to 3.3V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(XIN)=10MHz no wait unless otherwise specified.

- 2. Vcc1 for the port P6 to P11 and P14, and Vcc2 for the port P0 to P5 and P12 to P13

- 3. There is no external connections for port P1\_0 to P1\_7, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version.

**Table 5.31** Electrical Characteristics (2) (1)

| Cumbal | Parameter                                                                      |                      | Measuring Condition           |                                                                             | Standard |      |      | Unit |

|--------|--------------------------------------------------------------------------------|----------------------|-------------------------------|-----------------------------------------------------------------------------|----------|------|------|------|

| Symbol | Paramet                                                                        | eı                   | ivieasuring Condition         |                                                                             | Min.     | Тур. | Max. | Unit |

| Icc    | (Vcc1=Vcc2=2.7V to 3.6V) mode, the output pins are open and other pins are Vss |                      | Mask ROM                      | f(BCLK)=10MHz<br>No division                                                |          | 8    | 11   | mA   |

|        |                                                                                |                      |                               | No division,<br>On-chip oscillation                                         |          | 1    |      | mA   |

|        |                                                                                | Flash<br>Memory      | f(BCLK)=10MHz,<br>No division |                                                                             | 8        | 13   | mA   |      |

|        |                                                                                |                      | ,                             | No division,<br>On-chip oscillation                                         |          | 1.8  |      | mA   |

|        |                                                                                | Program              | Flash Memory<br>Program       | f(BCLK)=10MHz,<br>VCC1=3.0V                                                 |          | 12   |      | mA   |

|        |                                                                                |                      | Flash Memory<br>Erase         | f(BCLK)=10MHz,<br>VCC1=3.0V                                                 |          | 22   |      | mA   |

|        |                                                                                |                      | Mask ROM                      | f(XCIN)=32kHz<br>Low power dissipation<br>mode, ROM <sup>(3)</sup>          |          | 25   |      | μА   |

|        |                                                                                |                      | Flash Memory                  | f(BCLK)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |          | 25   |      | μА   |

|        |                                                                                |                      |                               | f(BCLK)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |          | 420  |      | μА   |

|        |                                                                                |                      |                               | On-chip oscillation,<br>Wait mode                                           |          | 45   |      | μА   |

|        |                                                                                |                      | Mask ROM<br>Flash Memory      | f(BCLK)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability High  |          | 6.0  |      | μА   |

|        |                                                                                |                      |                               | f(BCLK)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability Low   |          | 1.8  |      | μА   |

|        |                                                                                |                      |                               | Stop mode<br>Topr =25°C                                                     |          | 0.7  | 3.0  | μА   |

| Idet4  | Low Voltage Detection Diss                                                     | sipation Current (4) |                               |                                                                             |          | 0.6  | 4    | μА   |

| Idet3  | Reset Area Detection Dissi                                                     | pation Current (4)   |                               |                                                                             |          | 0.4  | 2    | μА   |

- NOTES:

1. Referenced to Vcc1=Vcc2=2.7 to 3.3V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(BCLK)=10MHz unless otherwise specified.

2. With one timer operated using fC32.

3. This indicates the memory in which the program to be executed exists.

4. Idea is dissipation current when the following bit is set to "1" (detection circuit enabled).

Idet4: VC27 bit in the VCR2 register Idet3: VC26 bit in the VCR2 register

## VCC1=VCC2=3V

#### **Timing Requirements**

(VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

Table 5.32 External Clock Input (XIN input)(1)

| Symbol | Parameter                             | Stan     | Unit     |       |  |

|--------|---------------------------------------|----------|----------|-------|--|

| Symbol | Faiametei                             | Min.     | Max.     | Offic |  |

| tc     | External Clock Input Cycle Time       |          | ns       |       |  |

| tw(H)  | External Clock Input HIGH Pulse Width | (NOTE 3) |          | ns    |  |

| tw(L)  | External Clock Input LOW Pulse Width  | (NOTE 3) |          | ns    |  |

| tr     | External Clock Rise Time              |          | (NOTE 4) | ns    |  |

| tf     | External Clock Fall Time              |          | (NOTE 4) | ns    |  |

#### NOTES:

- 1. The condition is Vcc1=Vcc2=2.7 to 3.0V.

- 2. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times V \text{CC2} - 44} \text{ [ns]}$$

3. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times V\text{CC1} - 44} \times 0.4 \text{ [ns]}$$

4. Calculated according to the Vcc1 voltage as follows:

$$-10 \times Vcc1 + 45 [ns]$$

Table 5.33 Memory Expansion Mode and Microprocessor Mode

| Cumbal         | Parameter                                                           | Star | Standard  |    |  |  |

|----------------|---------------------------------------------------------------------|------|-----------|----|--|--|

| Symbol         | Parameter                                                           | Min. | Min. Max. |    |  |  |

| tac1(RD-DB)    | Data Input Access Time (for setting with no wait) (NOTE 1)          |      |           |    |  |  |

| tac2(RD-DB)    | Data Input Access Time (for setting with wait) (NOTE 2)             |      |           |    |  |  |

| tac3(RD-DB)    | Data Input Access Time (when accessing multiplex bus area) (NOTE 3) |      |           |    |  |  |

| tsu(DB-RD)     | Data Input Setup Time                                               | 50   |           | ns |  |  |

| tsu(RDY-BCLK)  | RDY Input Setup Time                                                | 40   |           | ns |  |  |

| tsu(HOLD-BCLK) | HOLD Input Setup Time                                               | 50   |           | ns |  |  |

| th(RD-DB)      | Data Input Hold Time                                                | 0    |           | ns |  |  |

| th(BCLK-RDY)   | RDY Input Hold Time                                                 | 0    |           | ns |  |  |

| th(BCLK-HOLD)  | HOLD Input Hold Time                                                | 0    |           | ns |  |  |

#### NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5x10^9}{f(BCLK)} - 60[ns]$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)}-60[ns] \qquad \text{n is "2" for 1-wait setting, "3" for 2-wait setting and "4" for 3-wait setting.}$$

3. Calculated according to the BCLK frequency as follows:

Page 67 of 96

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 60[ns] \qquad \text{n is "2" for 2-wait setting, "3" for 3-wait setting.}$$

## VCC1=VCC2=3V

#### **Switching Characteristics**

(VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

Table 5.46 Memory Expansion and Microprocessor Modes (for setting with no wait)

| Cumbal        | Parameter                                          |                    | Stan     | dard | Unit  |  |

|---------------|----------------------------------------------------|--------------------|----------|------|-------|--|

| Symbol        | i didilicici                                       |                    | Min.     | Max. | Oille |  |

| td(BCLK-AD)   | Address Output Delay Time                          |                    |          | 30   | ns    |  |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)     |                    | 4        |      | ns    |  |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)       |                    | 0        |      | ns    |  |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)       |                    | (NOTE 2) |      | ns    |  |

| td(BCLK-CS)   | Chip Select Output Delay Time                      |                    |          | 30   | ns    |  |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK) |                    | 4        |      | ns    |  |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                       |                    |          | 25   | ns    |  |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                        | 1                  | -4       |      | ns    |  |

| td(BCLK-RD)   | RD Signal Output Delay Time                        | See<br>Figure 5.12 |          | 30   | ns    |  |

| th(BCLK-RD)   | RD Signal Output Hold Time                         | l iguic 3.12       | 0        |      | ns    |  |

| td(BCLK-WR)   | WR Signal Output Delay Time                        |                    |          | 30   | ns    |  |

| th(BCLK-WR)   | WR Signal Output Hold Time                         |                    | 0        |      | ns    |  |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)       |                    |          | 40   | ns    |  |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) (3)    | 4                  |          | ns   |       |  |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)         |                    | (NOTE 1) |      | ns    |  |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) (3)      | 7                  | (NOTE 2) |      | ns    |  |

| td(BCLK-HLDA) | HLDA Output Delay Time                             | 7                  |          | 40   | ns    |  |

#### NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \text{x} 10^9}{\text{f(BCLK)}} - 40 [\text{ns}] \hspace{1cm} \text{f(BCLK) is 12.5MHz or less.}$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10[ns]$$

3. This standard value shows the timing when the output is off, and does not show hold time of data bus.

Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value.

Hold time of data bus is expressed in

$$t = -CR X In (1-VoL / Vcc2)$$

by a circuit of the right figure.

For example, when VoL = 0.2Vcc2, C = 30pF, R = 1k $\Omega$ , hold time of output "L" level is

$$t = -30pF X 1k \Omega X In(1-0.2Vcc2 / Vcc2)$$

= 6.7 ns.

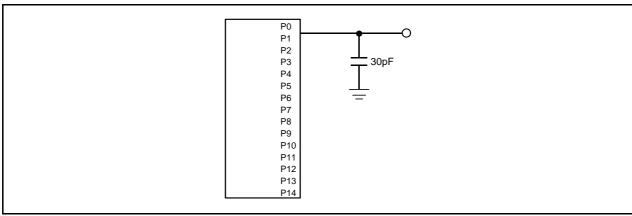

Figure 5.12 Ports P0 to P14 Measurement Circuit

Page 70 of 96

# VCC1=VCC2=5V

### **Timing Requirements**

(VCC1 = VCC2 = 5V, Vss = 0V, at  $T_{opr}$  = -40 to 85°C (T version) / -40 to 125°C (V version) unless otherwise specified)

Table 5.59 External Clock Input (XIN input)

| Symbol | Parameter                             | Stan | Unit |       |

|--------|---------------------------------------|------|------|-------|

|        | Faianietei                            | Min. | Max. | UTIIL |

| tc     | External Clock Input Cycle Time       | 62.5 |      | ns    |

| tw(H)  | External Clock Input HIGH Pulse Width | 25   |      | ns    |

| tw(L)  | External Clock Input LOW Pulse Width  | 25   |      | ns    |

| tr     | External Clock Rise Time              |      | 15   | ns    |

| tf     | External Clock Fall Time              |      | 15   | ns    |

RENESAS

# REVISION HISTORY

| Pov  | Data         |             | Description                                                                                                                      |

|------|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| Rev. | Date         | Page        | Summary                                                                                                                          |

| 1.10 | May 28, 2003 | 1           | Applications are partly revised.                                                                                                 |

|      |              | 2           | Table 1.1.1 is partly revised.                                                                                                   |

|      |              | 4-5         | Table 1.1.2 and 1.1.3 is partly revised.                                                                                         |

|      |              |             | "Note 1" is partly revised.                                                                                                      |

|      |              | 22          | Table 1.5.3 is partly revised.                                                                                                   |

|      |              | 23          | Table 1.5.5 is partly revised.                                                                                                   |

|      |              |             | Table 1.5.6 is added.                                                                                                            |

|      |              | 24          | Table 1.5.9 is partly revised.                                                                                                   |

|      |              | 30          | Notes 1 and 2 in Table 1.5.26 is partly revised.                                                                                 |

|      |              | 31          | Notes 1 in Table 1.5.27 is partly revised.                                                                                       |

|      |              | 30-31       | Note 3 is added to "Data output hold time (refers to BCLK)" in Table 1.5.26 and 1.5.27.                                          |

|      |              | 32          | Note 4 is added to "th(ALE-AD)" in Table 1.5.28.                                                                                 |

|      |              | 30-32       | Switching Characteristics is partly revised.                                                                                     |

|      |              | 36-39       | th(WR-AD) and th(WR-DB) in Figure 1.5.5 to 1.5.8 is partly revised.                                                              |

|      |              | 40-41       | th(ALE-AD), th(WR-CS), th(WR-DB) and th(WR-AD) in Figure 1.5.9 to                                                                |

|      |              | 42          | 1.5.10 is partly revised.                                                                                                        |

|      |              |             | Note 2 is added to Table 1.5.29.                                                                                                 |

|      |              | 47          | Notes 1 and 2 in Table 1.5.45 is partly revised.                                                                                 |

|      |              | 48<br>47-48 | Notes 1 in Table 1.5.46 is partly revised.                                                                                       |

|      |              | 47-40       | Note 3 is added to "Data output hold time (refers to BCLK)" in Table                                                             |

|      |              | 49          | 1.5.45 and 1.5.46.                                                                                                               |