Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                              |

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                              |

| Peripherals                | DMA, WDT                                                                         |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 384KB (384K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 31K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                      |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-BQFP                                                                         |

| Supplier Device Package    | 100-QFP (14x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30626fhpfp-u5c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# M16C/62P Group (M16C/62P, M16C/62PT) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

REJ03B0001-0241 Rev.2.41 Jan 10, 2006

#### 1. Overview

The M16C/62P Group (M16C/62P, M16C/62PT) of single-chip microcomputers are built using the high performance silicon gate CMOS process using a M16C/60 Series CPU core and are packaged in a 80-pin, 100-pin and 128-pin plastic molded QFP. These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1M bytes of address space, they are capable of executing instructions at high speed. In addition, this microcomputer contains a multiplier and DMAC which combined with fast instruction processing capability, makes it suitable for control of various OA, communication, and industrial equipment which requires high-speed arithmetic/logic operations.

#### 1.1 Applications

Audio, cameras, television, home appliance, office/communications/portable/industrial equipment, automobile, etc

Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free of error. Specifications in this manual may be changed for functional or performance improvements. Please make sure your manual is the latest edition.

RENESAS

Table 1.2 Performance Outline of M16C/62P Group (M16C/62P, M16C/62PT)(100-pin version)

| Number of Basic Instructions   91 instructions   11 instructions   12 instructions   13 instructions   14 inst[IRGLK]=24MHz, VCC1=3.3 to 5.5V    14.7ns(IRGLK)=24MHz, VCC1=4.0 to 5.5   10 inst[IRGLK]=24MHz, VCC1=2.7 to 5.5V    14.7ns(IRGLK)=24MHz, VCC1=4.0 to 5.5   10 instructions   14 instruction   14 instruction   15 instruction   15 instruction   15 instruction   16 instru    |                | Item                         | Performance                                                                                             | , . ,                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------|--|--|--|

| Number of Basic Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | nem                          |                                                                                                         | M46C/62DT(4)                             |  |  |  |

| Minimum Instruction   Execution Time   41.7ns(f(BCLK)=24MHz, VCC1=3.3 to 5.5V)   41.7ns(f(BCLK)=24MHz, VCC1=4.0 to 5.5 to 00srel(f(BCLK)=10MHz, VCC1=2.7 to 5.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ODLI           | Number of Desir Instructions |                                                                                                         | W116C/62P1(+)                            |  |  |  |

| Execution Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CPU            |                              |                                                                                                         | AA 7::-///DOLIG OANUL VOOA A 0 t- 5 5V)  |  |  |  |

| Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                              |                                                                                                         | 41./ns(f(BCLK)=24MHz, VCC1=4.0 to 5.5V)  |  |  |  |

| Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                              |                                                                                                         | Single-chip                              |  |  |  |

| Memory Capacity   See Table 1.4 to 1.7 Product List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | Sporaurig Mode               | • • • • • • • • • • • • • • • • • • • •                                                                 | Omg.o omp                                |  |  |  |

| Peripheral Function   Port   Input/Output: 87 pins, Input: 1 pin   Multifunction Timer   Timer A: 16 bits x 5 channels, Timer B: 16 bits x 6 channels, Three phase motor control circuit   Serial Interface   3 channels   Clock synchronous, UART, I2C bus(1), IEBus(2)   2 channels   Clock synchronous   UART, I2C bus(1), IEBus(2)   2 channels   CRC Calculation Circuit   CCITT-CRC   UAtchdog Timer   15 bits x 2 channels   CRC Calculation Circuit   CCITT-CRC   UAtchdog Timer   15 bits x 1 channel (with prescaler)   Interrupt   Interrupt   Interrupt   Interrupt   Interrupt   Interrupt   Uatchdog Ua    |                | Address Space                | 1 Mbyte (Available to 4 Mbytes by                                                                       | 1 Mbyte                                  |  |  |  |

| Peripheral Function   Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                              |                                                                                                         |                                          |  |  |  |

| Function   Multifunction Timer   Timer A : 16 bits x 5 channels, Timer B : 16 bits x 6 channels, Three phase motor control circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | Memory Capacity              | See Table 1.4 to 1.7 Product Lis                                                                        | st                                       |  |  |  |

| Three phase motor control circuit  Serial Interface  3 channels Clock synchronous, UART, I2C bus(1), IEBus(2) 2 channels Clock synchronous  A/D Converter 10-bit A/D converter: 1 circuit, 26 channels D/A Converter | •              |                              |                                                                                                         |                                          |  |  |  |

| Clock synchronous, UART, I²C bus(1), IEBus(2) 2 channels Clock synchronous  A/D Converter D/A Converter B bits x 2 channels  DMAC 2 channels  CRC Calculation Circuit CCITT-CRC Watchdog Timer Interrupt Interrupt Clock Generation Circuit Von-chip oscillator, PLL synthesizer (*)Equipped with a built-in feedback resistor.  Oscillation Stop Detection Function Voltage Detection Circuit VoC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (*(BCLK=24MHz) VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (*(BCLK=10MHz) 1.8 µA (VCC1=VCC2=3V, f(BCLK)=10MHz) 1.8 µA (VCC1=VCC2=3V, f(BCLK)=24MHz) 2.0 µA (VCC1=VCC2=5V, f(SCIN)=32kHz, wait mode) 0.7 µA (VCC1=VCC2=3V, stop mode)  Flash memory Version  Program Ale Fase Endurance Clock synchronous 10-bit A/D converter: 1 circuit, 26 channels 10-bit A/D converter: 1 circuit, 26 channels 2 c | Function       | Multifunction Timer          |                                                                                                         | r B: 16 bits x 6 channels,               |  |  |  |

| D/A Converter   8 bits x 2 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | Serial Interface             | Clock synchronous, UART, I <sup>2</sup> C bu 2 channels                                                 | us <sup>(1)</sup> , IEBus <sup>(2)</sup> |  |  |  |

| DMAC   2 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                | A/D Converter                | 10-bit A/D converter: 1 circuit, 26 channels                                                            |                                          |  |  |  |

| CRC Calculation Circuit   CCITT-CRC   Watchdog Timer   15 bits x 1 channel (with prescaler)   Interrupt   Internal: 29 sources, External: 8 sources, Software: 4 sources, Priority level: 7 levels   Clock Generation Circuit   4 circuits   Main clock generation circuit (*), Subclock generation circuit (*), On-chip oscillator, PLL synthesizer (*)Equipped with a built-in feedback resistor.   Oscillation Stop Detection Function   Voltage Detection Circuit   Available (option (5))   Absent   Supply Voltage   VCC1=3.0 to 5.5 V, VCC2=2.7V to VCC1=VCC2=4.0 to 5.5V (f(BCLK=24MHz) VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=24MHz) VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=10MHz) RmA (VCC1=VCC2=3V, f(BCLK)=24MHz) RmA (VCC1=VCC2=3V, f(BCLK)=10MHz) RmA (VCC1=VCC2=3V, f(BCLK)=10MHz) RmA (VCC1=VCC2=3V, f(BCLK)=24MHz) RmA (VCC1=VCC2=5V, f(BCLK)=24MHz) RmA (VCC1=VCC2=3V, f(BCLK)=24MHz) RmA (VCC1=VCC2=5V, f(BCLK)=24MHz) RmA (V |                | D/A Converter                |                                                                                                         |                                          |  |  |  |

| Watchdog Timer   15 bits x 1 channel (with prescaler)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | DMAC                         | 2 channels                                                                                              |                                          |  |  |  |

| Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                | CRC Calculation Circuit      | CCITT-CRC                                                                                               |                                          |  |  |  |

| Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                | Watchdog Timer               | 15 bits x 1 channel (with prescaler)                                                                    |                                          |  |  |  |

| Clock Generation Circuit  A circuits  Main clock generation circuit (*), Subclock generation circuit (*), On-chip oscillator, PLL synthesizer  (*)Equipped with a built-in feedback resistor.  Stop detection of main clock oscillation, re-oscillation detection function  Voltage Detection Circuit  Available (option (5))  Electric Characteristics  Supply Voltage  VCC1=3.0 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=24MHz) VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=24MHz) VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=24MHz)  Power Consumption  14 mA (VCC1=VCC2=5V, f(BCLK)=24MHz) 8 mA (VCC1=VCC2=3V, f(BCLK)=10MHz) 1.8µA (VCC1=VCC2=3V, f(BCLK)=10MHz) 1.8µA (VCC1=VCC2=3V, f(XCIN)=32kHz, wait mode) 0.8µA (VCC1=VCC2=5V, stop mode)  Flash memory Version  Program and Erase Endurance  100 times (all area) or 1,000 times (user ROM area without block A and block 1) / 10,000 times (block A, block 1) (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                              |                                                                                                         |                                          |  |  |  |

| Detection Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | Clock Generation Circuit     | Main clock generation circuit (*), Subclock generation circuit (*), On-chip oscillator, PLL synthesizer |                                          |  |  |  |

| Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                              | Stop detection of main clock oscillation, re-oscillation detection                                      |                                          |  |  |  |

| Characteristics         VCC1 (f(BCLK=24MHz) VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1=2.7 to 5.5 V, VCC2=2.7V to VCC1 (f(BCLK=10MHz))         (f(BCLK=24MHz))         (2,0,0,0)         (f(BCLK=24MHz))         (2,0,0,0)         (f(BCLK=24MHz))         (2,0,0,0)         (f(BCLK=24MHz))         (2,0,0,0)         (2,0,0,0)         (2,0,0,0)         (3,0,0)         (3,0,0)         (3,0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | Voltage Detection Circuit    | Available (option <sup>(5)</sup> )                                                                      | Absent                                   |  |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | Supply Voltage               | VCC1 (f(BCLK=24MHz)<br>VCC1=2.7 to 5.5 V, VCC2=2.7V to                                                  |                                          |  |  |  |

| version  Program and Erase Endurance  100 times (all area) or 1,000 times (user ROM area without block A and block 1) / 10,000 times (block A, block 1) (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | Power Consumption            | 8 mA (VCC1=VCC2=3V, $f(BCLK)=10MHz$ ) 1.8 $\mu$ A (VCC1=VCC2=3V, $f(XCIN)=32kHz$ , wait mode)           | wait mode)                               |  |  |  |

| Endurance or 1,000 times (user ROM area without block A and block 1) / 10,000 times (block A, block 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Flash memory   | Program/Erase Supply Voltage | 3.3±0.3 V or 5.0±0.5 V                                                                                  | 5.0±0.5 V                                |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | version        | _                            | or 1,000 times (user ROM area with                                                                      | out block A and block 1)                 |  |  |  |

| Operating Ambient Temperature -20 to 85°C, -40 to 85°C   V version : -40 to 85°C   V version : -40 to 125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Operating Ambi | ent Temperature              | -20 to 85°C,                                                                                            | T version : -40 to 85°C                  |  |  |  |

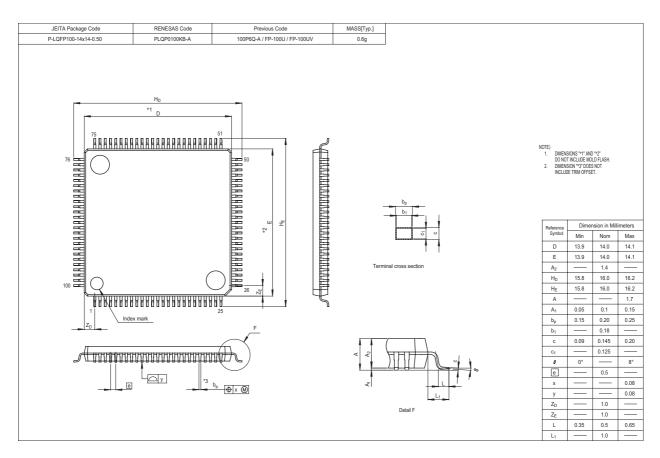

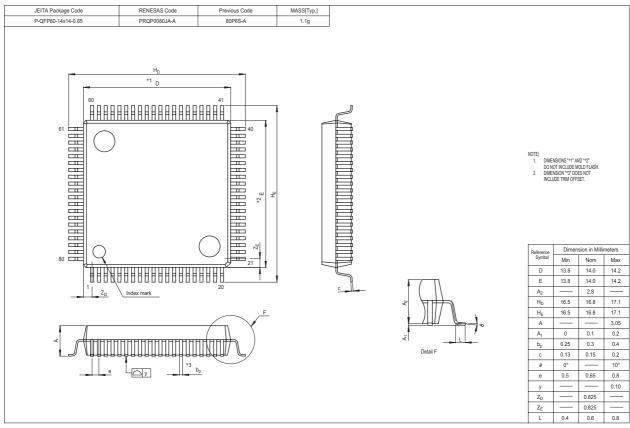

| Package 100-pin plastic mold QFP, LQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Package        |                              | 100-pin plastic mold QFP, LQFP                                                                          | ı                                        |  |  |  |

- 1. I<sup>2</sup>C bus is a registered trademark of Koninklijke Philips Electronics N. V.

- 2. IEBus is a registered trademark of NEC Electronics Corporation.

- 3. See Table 1.8 and 1.9 Product Code for the program and erase endurance, and operating ambient temperature.

- In addition 1,000 times/10,000 times are under development as of Jul., 2005. Please inquire about a release schedule.

- 4. Use the M16C/62PT on VCC1=VCC2

- 5. All options are on request basis.

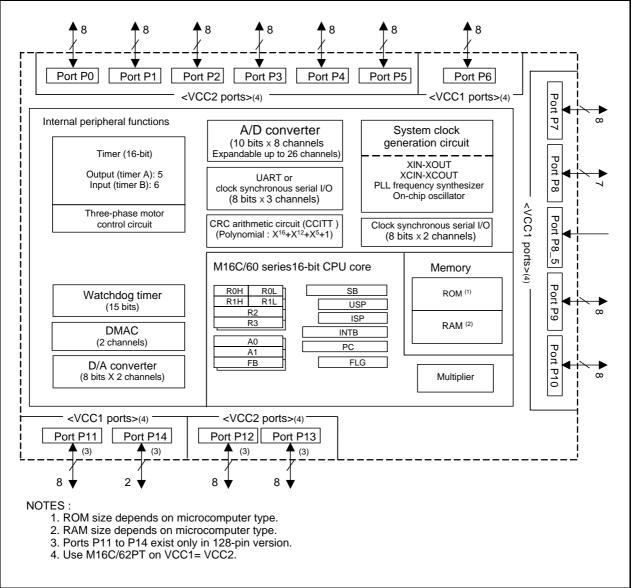

### 1.3 Block Diagram

Figure 1.1 is a M16C/62P Group (M16C/62P, M16C/62PT) 128-pin and 100-pin version Block Diagram, Figure 1.2 is a M16C/62P Group (M16C/62P, M16C/62PT) 80-pin version Block Diagram.

Figure 1.1 M16C/62P Group (M16C/62P, M16C/62PT) 128-pin and 100-pin version Block Diagram

Page 5 of 96

Table 1.21 Pin Description (80-pin Version) (2)

| Signal Name             | Pin Name                                                                                               | I/O  | Power                         | Description                                                                                                                                                                                                             |

|-------------------------|--------------------------------------------------------------------------------------------------------|------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference voltage input | VREF                                                                                                   | Type | Supply <sup>(1)</sup><br>VCC1 | Applies the reference voltage for the A/D converter and D/A converter.                                                                                                                                                  |

| A/D converter           | AN0 to AN7,<br>AN0_0 to<br>AN0_7,<br>AN2_0 to<br>AN2_7                                                 | I    | VCC1                          | Analog input pins for the A/D converter.                                                                                                                                                                                |

|                         | ADTRG                                                                                                  | I    | VCC1                          | This is an A/D trigger input pin.                                                                                                                                                                                       |

|                         | ANEX0                                                                                                  | I/O  | VCC1                          | This is the extended analog input pin for the A/D converter, and is the output in external op-amp connection mode.                                                                                                      |

|                         | ANEX1                                                                                                  | I    | VCC1                          | This is the extended analog input pin for the A/D converter.                                                                                                                                                            |

| D/A converter           | DA0, DA1                                                                                               | 0    | VCC1                          | This is the output pin for the D/A converter.                                                                                                                                                                           |

| I/O port <sup>(1)</sup> | P0_0 to P0_7,<br>P2_0 to P2_7,<br>P3_0 to P3_7,<br>P5_0 to P5_7,<br>P6_0 to P6_7,<br>P10_0 to<br>P10_7 | I/O  | VCC1                          | 8-bit I/O ports in CMOS, having a direction register to select an input or output.  Each pin is set as an input port or output port. An input port can be set for a pull-up or for no pull-up in 4-bit unit by program. |

|                         | P8_0 to P8_4,<br>P8_6, P8_7,<br>P9_0,<br>P9_2 to P9_7                                                  | I/O  | VCC1                          | I/O ports having equivalent functions to P0.                                                                                                                                                                            |

|                         | P4_0 to P4_3,<br>P7_0, P7_1,<br>P7_6, P7_7                                                             | I/O  | VCC1                          | I/O ports having equivalent functions to P0. (however, output of P7_0 and P7_1 for the N-channel open drain output.)                                                                                                    |

| Input port              | P8_5                                                                                                   | I    | VCC1                          | Input pin for the NMI interrupt. Pin states can be read by the P8_5 bit in the P8 register.                                                                                                                             |

I: Input O: Output I/O: Input and output

#### NOTES:

1. There is no external connections for port P1, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version. Set the direction bits in these ports to "1" (output mode), and set the output data to "0" ("L") using the program.

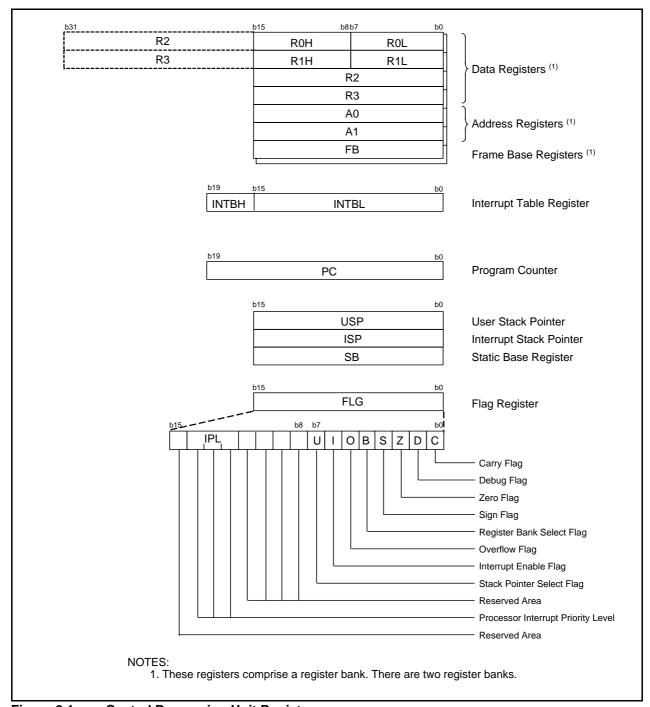

# 2. Central Processing Unit (CPU)

Figure 2.1 shows the CPU registers. The CPU has 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB comprise a register bank. There are two register banks.

Figure 2.1 Central Processing Unit Register

#### 2.1 Data Registers (R0, R1, R2 and R3)

The R0 register consists of 16 bits, and is used mainly for transfers and arithmetic/logic operations. R1 to R3 are the same as R0.

The R0 register can be separated between high (R0H) and low (R0L) for use as two 8-bit data registers.

R1H and R1L are the same as R0H and R0L. Conversely, R2 and R0 can be combined for use as a 32-bit data register (R2R0). R3R1 is the same as R2R0.

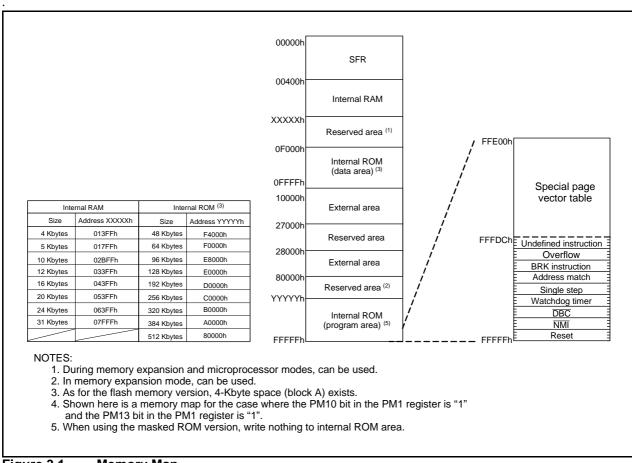

# 3. Memory

Figure 3.1 is a Memory Map of the M16C/62P group. The address space extends the 1M bytes from address 00000h to FFFFFh.

The internal ROM is allocated in a lower address direction beginning with address FFFFFh. For example, a 64-Kbyte internal ROM is allocated to the addresses from F0000h to FFFFFh.

As for the flash memory version, 4-Kbyte space (block A) exists in 0F000h to 0FFFFh. 4-Kbyte space is mainly for storing data. In addition to storing data, 4-Kbyte space also can store programs.

The fixed interrupt vector table is allocated to the addresses from FFFDCh to FFFFFh. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 00400h. For example, a 10-Kbyte internal RAM is allocated to the addresses from 00400h to 02BFFh. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SRF is allocated to the addresses from 00000h to 003FFh. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE00h to FFFDBh. This vector is used by the JMPS or JSRS instruction. For details, refer to the M16C/60 and M16C/20 Series Software Manual.

In memory expansion and microprocessor modes, some areas are reserved for future use and cannot be used by users. Use M16C/62P (80-pin version) and M16C/62PT in single-chip mode. The memory expansion and microprocessor modes cannot be used

Figure 3.1 Memory Map

Page 33 of 96

#### **Special Function Register (SFR)** 4.

SFR(Special Function Register) is the control register of peripheral functions. Tables 4.1 to 4.6 list the SFR information.

Table 4.1 SFR Information (1) (1)

| 0005h         Processor Mode Register 1         PM1         00           0006h         System Clock Control Register 0         CM0         01           0007h         System Clock Control Register 1         CM1         00           0008h         Chip Select Control Register (6)         CSR         00           0009h         Address Match Interrupt Enable Register         AIER         XX           000Ah         Protect Register         PRCR         XX           000Bh         Data Bank Register (6)         DBR         00           000Ch         Oscillation Stop Detection Register (3)         CM2         0X           000Dh         000Eh         Watchdog Timer Start Register         WDTS         XX           000Fh         Watchdog Timer Control Register         WDC         00           0010h         Address Match Interrupt Register 0         RMAD0         00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | After Reset  00000000b(CNVSS pin is "L") 0000011b(CNVSS pin is "H") 0001000b 1001000b 0100000b 0000001b XXXXX00b X000000b 0h X000000b Xh 0XXXXXXb(4) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0001h         0002h           0003h         0004h           0004h         Processor Mode Register 0 (2)           0005h         Processor Mode Register 1           0006h         System Clock Control Register 0           0007h         System Clock Control Register 1           0008h         Chip Select Control Register (6)           0009h         Address Match Interrupt Enable Register           000Ah         Protect Register           000Bh         Data Bank Register (6)           000Ch         Oscillation Stop Detection Register (3)           000Ch         Oscillation Stop Detection Register (3)           000Bh         Watchdog Timer Start Register           000Fh         Watchdog Timer Control Register           000Fh         Watchdog Timer Control Register           0010h         Address Match Interrupt Register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0001000b<br>1001000b<br>0100000b<br>0000001b<br>XXXXX00b<br>X000000b<br>0h<br>X000000b                                                               |

| 0002h         0003h           0004h         Processor Mode Register 0 (2)         PM0         00           0005h         Processor Mode Register 1         PM1         00           0006h         System Clock Control Register 0         CM0         01           0007h         System Clock Control Register 1         CM1         00           0008h         Chip Select Control Register (6)         CSR         00           0009h         Address Match Interrupt Enable Register         AIER         XX           000Ah         Protect Register         PRCR         XX           000Bh         Data Bank Register (6)         DBR         00           000Ch         Oscillation Stop Detection Register (3)         CM2         03           000Dh         Watchdog Timer Start Register         WDTS         XX           000Fh         Watchdog Timer Control Register         WDC         00           0010h         Address Match Interrupt Register 0         RMAD0         00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0001000b<br>1001000b<br>0100000b<br>0000001b<br>XXXXX00b<br>X000000b<br>0h<br>X000000b                                                               |

| 0003h         Processor Mode Register 0 (2)         PM0         00           0004h         Processor Mode Register 1         PM1         00           0005h         Processor Mode Register 1         PM1         00           0006h         System Clock Control Register 0         CM0         01           0007h         System Clock Control Register 1         CM1         00           0008h         Chip Select Control Register (6)         CSR         00           0009h         Address Match Interrupt Enable Register         AIER         XX           000Ah         Protect Register         PRCR         XX           000Bh         Data Bank Register (6)         DBR         00           000Ch         Oscillation Stop Detection Register (3)         CM2         0X           000Dh         Wolden Watchdog Timer Start Register         WDTS         XX           000Fh         Watchdog Timer Control Register         WDC         00           0010h         Address Match Interrupt Register 0         RMAD0         00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0001000b<br>1001000b<br>0100000b<br>0000001b<br>XXXXX00b<br>X000000b<br>0h<br>X000000b                                                               |