Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                              |

| Peripherals                | DMA, WDT                                                                         |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 384KB (384K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 31K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                      |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP                                                                         |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30626fhpgp-u3c |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | Product | Dealasa   | Internal ROM<br>(User ROM Area Without Block A,<br>Block 1) |                      | Interna<br>(Block A,              | Operating<br>Ambient |               |

|--------------|---------|-----------|-------------------------------------------------------------|----------------------|-----------------------------------|----------------------|---------------|

|              | Code    | Package   | Program<br>and Erase<br>Endurance                           | Temperature<br>Range | Program<br>and Erase<br>Endurance | Temperature<br>Range | Temperature   |

| Flash memory | D3      | Lead-     | 100                                                         | 0°C to 60°C          | 100                               | 0°C to 60°C          | -40°C to 85°C |

| Version      | D5      | included  |                                                             |                      |                                   |                      | -20°C to 85°C |

|              | D7      |           | 1,000                                                       |                      | 10,000                            | -40°C to 85°C        | -40°C to 85°C |

|              | D9      |           |                                                             |                      |                                   | -20°C to 85°C        | -20°C to 85°C |

|              | U3      | Lead-free | 100                                                         |                      | 100                               | 0°C to 60°C          | -40°C to 85°C |

|              | U5      |           |                                                             |                      |                                   |                      | -20°C to 85°C |

|              | U7      |           | 1,000                                                       |                      | 10,000                            | -40°C to 85°C        | -40°C to 85°C |

|              | U9      |           |                                                             |                      |                                   | -20°C to 85°C        | -20°C to 85°C |

| ROM-less     | D3      | Lead-     | -                                                           | -                    | -                                 | -                    | -40°C to 85°C |

| version      | D5      | included  |                                                             |                      |                                   |                      | -20°C to 85°C |

|              | U3      | Lead-free | -                                                           | -                    | -                                 | -                    | -40°C to 85°C |

|              | U5      |           |                                                             |                      |                                   |                      | -20°C to 85°C |

### Table 1.8 Product Code of Flash Memory version and ROMless version for M16C/62P

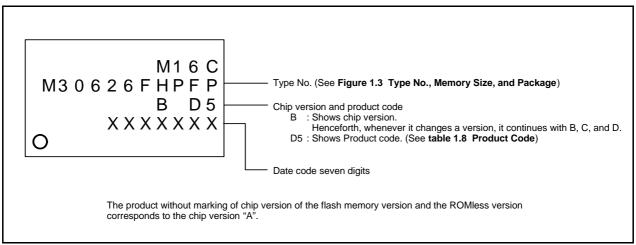

Figure 1.4 Marking Diagram of Flash Memory version and ROM-less version for M16C/62P (Top View)

| Signal Name                            | Pin Name                   | I/O  | Power                 | Description                                                                                                                                   |

|----------------------------------------|----------------------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                      |                            | Туре | Supply <sup>(1)</sup> | '                                                                                                                                             |

| Main clock                             | XIN                        | I    | VCC1                  | I/O pins for the main clock generation circuit. Connect a ceramic                                                                             |

| input                                  |                            |      |                       | resonator or crystal oscillator between XIN and XOUT <sup>(3)</sup> . To use                                                                  |

| Main clock                             | XOUT                       | 0    | VCC1                  | the external clock, input the clock from XIN and leave XOUT open.                                                                             |

| output                                 | XON                        |      | 1/004                 |                                                                                                                                               |

| Sub clock input                        |                            |      | VCC1                  | I/O pins for a sub clock oscillation circuit. Connect a crystal oscillator between XCIN and XCOUT <sup>(3)</sup> . To use the external clock, |

| Sub clock<br>output                    | XCOUT                      | 0    | VCC1                  | input the clock from XCIN and leave XCOUT open.                                                                                               |

| BCLK output <sup>(2)</sup>             | BCLK                       | 0    | VCC2                  | Outputs the BCLK signal.                                                                                                                      |

| Clock output                           | CLKOUT                     | 0    | VCC2                  | The clock of the same cycle as fC, f8, or f32 is outputted.                                                                                   |

| INT interrupt                          | INTO to INT2               | - U  | VCC1                  | Input pins for the INT interrupt.                                                                                                             |

| input                                  |                            |      |                       | input pins for the INT interrupt.                                                                                                             |

|                                        | NT3 to INT5                | I    | VCC2                  |                                                                                                                                               |

| NMI interrupt<br>input                 | NMI                        | Ι    | VCC1                  | Input pin for the NMI interrupt. Pin states can be read by the P8_5 bit in the P8 register.                                                   |

| Key input<br>interrupt input           | KI0 to KI3                 | Ι    | VCC1                  | Input pins for the key input interrupt.                                                                                                       |

| Timer A                                | TA0OUT to                  | I/O  | VCC1                  | These are timer A0 to timer A4 I/O pins. (however, output of                                                                                  |

|                                        | TA4OUT                     |      |                       | TA0OUT for the N-channel open drain output.)                                                                                                  |

|                                        | TA0IN to<br>TA4IN          | Ι    | VCC1                  | These are timer A0 to timer A4 input pins.                                                                                                    |

|                                        | ZP                         |      | VCC1                  | Input pin for the Z-phase.                                                                                                                    |

| Timer B                                | TB0IN to<br>TB5IN          | Ι    | VCC1                  | These are timer B0 to timer B5 input pins.                                                                                                    |

| Three-phase<br>motor control<br>output | U, <u>Ū,</u> V, ⊽,<br>W, ₩ | 0    | VCC1                  | These are Three-phase motor control output pins.                                                                                              |

| Serial interface                       | CTS0<br>CTS2               | l    | VCC1                  | These are send control input pins.                                                                                                            |

|                                        | RTS0 to<br>RTS2            | 0    | VCC1                  | These are receive control output pins.                                                                                                        |

|                                        | CLK0 to<br>CLK4            | I/O  | VCC1                  | These are transfer clock I/O pins.                                                                                                            |

|                                        | RXD0 to<br>RXD2            | Ι    | VCC1                  | These are serial data input pins.                                                                                                             |

|                                        | SIN3, SIN4                 | I    | VCC1                  | These are serial data input pins.                                                                                                             |

|                                        | TXD0 to<br>TXD2            | 0    | VCC1                  | These are serial data output pins. (however, output of TXD2 for the N-channel open drain output.)                                             |

|                                        | SOUT3,<br>SOUT4            | 0    | VCC1                  | These are serial data output pins.                                                                                                            |

|                                        | CLKS1                      | 0    | VCC1                  | This is output pin for transfer clock output from multiple pins function.                                                                     |

| I <sup>2</sup> C mode                  | SDA0 to<br>SDA2            | I/O  | VCC1                  | These are serial data I/O pins. (however, output of SDA2 for the N-<br>channel open drain output.)                                            |

|                                        | SCL0 to<br>SCL2            | I/O  | VCC1                  | These are transfer clock I/O pins. (however, output of SCL2 for the N-channel open drain output.)                                             |

| Table 1.18 | Pin Description (100-pin and 128-pin Version) (2) |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

I : Input O : Output I/O : Input and output

NOTES:

- 1. When use VCC1 > VCC2, contacts due to some points or restrictions to be checked.

- 2. This pin function in M16C/62PT cannot be used.

- 3. Ask the oscillator maker the oscillation characteristic.

| Signal Name                  | Pin Name                     | I/O<br>Type | Power<br>Supply | Description                                                                                                                                                                                                                                                                |

|------------------------------|------------------------------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply input           | VCC1, VSS                    |             | -               | Apply 2.7 to 5.5 V to the VCC1 pin and 0 V to the VSS pin. $^{(1, 2)}$                                                                                                                                                                                                     |

| Analog power supply input    | AVCC<br>AVSS                 | l           | VCC1            | Applies the power supply for the A/D converter. Connect the AVCC pin to VCC1. Connect the AVSS pin to VSS.                                                                                                                                                                 |

| Reset input                  | RESET                        | Ι           | VCC1            | The microcomputer is in a reset state when applying "L" to the this pin.                                                                                                                                                                                                   |

| CNVSS                        | CNVSS<br>(BYTE)              | Ι           | VCC1            | Switches processor mode. Connect this pin to VSS to when after a reset to start up in single-chip mode. Connect this pin to VCC1 to start up in microprocessor mode. As for the BYTE pin of the 80-pin versions, pull-up processing is performed within the microcomputer. |

| Main clock<br>input          | XIN                          | Ι           | VCC1            | I/O pins for the main clock generation circuit. Connect a ceramic resonator or crystal oscillator between XIN and XOUT <sup>(3)</sup> . To use                                                                                                                             |

| Main clock<br>output         | XOUT                         | 0           | VCC1            | the external clock, input the clock from XIN and leave XOUT open.                                                                                                                                                                                                          |

| Sub clock input              | XCIN                         | Ι           | VCC1            | I/O pins for a sub clock oscillation circuit. Connect a crystal                                                                                                                                                                                                            |

| Sub clock<br>output          | XCOUT                        | 0           | VCC1            | oscillator between XCIN and XCOUT <sup>(3)</sup> . To use the external clock, input the clock from XCIN and leave XCOUT open.                                                                                                                                              |

| Clock output                 | CLKOUT                       | 0           | VCC2            | The clock of the same cycle as fC, f8, or f32 is outputted.                                                                                                                                                                                                                |

| INT interrupt input          | INT0 to INT2                 | I           | VCC1            | Input pins for the INT interrupt.                                                                                                                                                                                                                                          |

| NMI interrupt input          | NMI                          | Ι           | VCC1            | Input pin for the MMI interrupt.                                                                                                                                                                                                                                           |

| Key input<br>interrupt input | KI0 to KI3                   | I           | VCC1            | Input pins for the key input interrupt.                                                                                                                                                                                                                                    |

| Timer A                      | TA0OUT,<br>TA3OUT,<br>TA4OUT | I/O         | VCC1            | These are Timer A0, Timer A3 and Timer A4 I/O pins. (however, output of TA0OUT for the N-channel open drain output.)                                                                                                                                                       |

|                              | TA0IN, TA3IN,<br>TA4IN       | Ι           | VCC1            | These are Timer A0, Timer A3 and Timer A4 input pins.                                                                                                                                                                                                                      |

|                              | ZP                           | I           | VCC1            | Input pin for the Z-phase.                                                                                                                                                                                                                                                 |

| Timer B                      | TB0IN, TB2IN<br>to TB5IN     | Ι           | VCC1            | These are Timer B0, Timer B2 to Timer B5 input pins.                                                                                                                                                                                                                       |

| Serial interface             | CTS0 to CTS1                 | I           | VCC1            | These are send control input pins.                                                                                                                                                                                                                                         |

|                              | RTS0 to RTS1                 | 0           | VCC1            | These are receive control output pins.                                                                                                                                                                                                                                     |

|                              | CLK0, CLK1,<br>CLK3, CLK4    | I/O         | VCC1            | These are transfer clock I/O pins.                                                                                                                                                                                                                                         |

|                              | RXD0 to RXD2                 | Ι           | VCC1            | These are serial data input pins.                                                                                                                                                                                                                                          |

|                              | SIN4                         | I           | VCC1            | This is serial data input pin.                                                                                                                                                                                                                                             |

|                              | TXD0 to TXD2                 | 0           | VCC1            | These are serial data output pins. (however, output of TXD2 for the N-channel open drain output.)                                                                                                                                                                          |

|                              | SOUT3,<br>SOUT4              | 0           | VCC1            | These are serial data output pins.                                                                                                                                                                                                                                         |

|                              | CLKS1                        | 0           | VCC1            | This is output pin for transfer clock output from multiple pins function.                                                                                                                                                                                                  |

| I <sup>2</sup> C mode        | SDA0 to SDA2                 | I/O         | VCC1            | These are serial data I/O pins. (however, output of SDA2 for the N-channel open drain output.)                                                                                                                                                                             |

|                              | SCL0 to SCL2                 | I/O         | VCC1            | These are transfer clock I/O pins. (however, output of SCL2 for the N-channel open drain output.)                                                                                                                                                                          |

| Table 1.20 | Pin Descrip | otion (80-pir | n Version) | (1 | ) (1) |

|------------|-------------|---------------|------------|----|-------|

|            |             |               |            |    |       |

I : Input O : Output I/O : Input and output

NOTES:

1. In this manual, hereafter, VCC refers to VCC1 unless otherwise noted.

2. In M16C/62PT, apply 4.0 to 5.5 V to the VCC1 pin.

3. Ask the oscillator maker the oscillation characteristic.

### 3. Memory

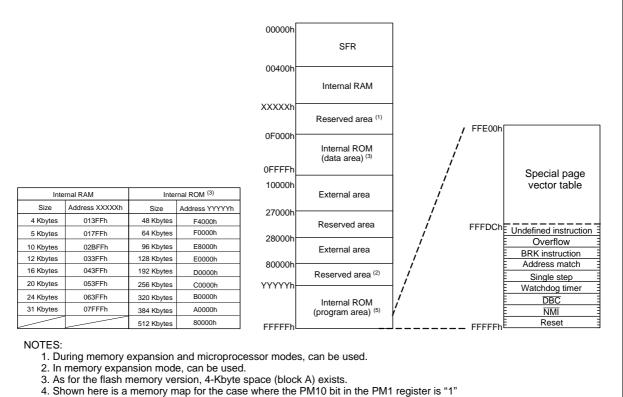

Figure 3.1 is a Memory Map of the M16C/62P group. The address space extends the 1M bytes from address 00000h to FFFFFh.

The internal ROM is allocated in a lower address direction beginning with address FFFFFh. For example, a 64-Kbyte internal ROM is allocated to the addresses from F0000h to FFFFFh.

As for the flash memory version, 4-Kbyte space (block A) exists in 0F000h to 0FFFFh. 4-Kbyte space is mainly for storing data. In addition to storing data, 4-Kbyte space also can store programs.

The fixed interrupt vector table is allocated to the addresses from FFFDCh to FFFFFh. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 00400h. For example, a 10-Kbyte internal RAM is allocated to the addresses from 00400h to 02BFFh. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SRF is allocated to the addresses from 00000h to 003FFh. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE00h to FFFDBh. This vector is used by the JMPS or JSRS instruction. For details, refer to the **M16C/60 and M16C/20 Series Software Manual**.

In memory expansion and microprocessor modes, some areas are reserved for future use and cannot be used by users. Use M16C/62P (80-pin version) and M16C/62PT in single-chip mode. The memory expansion and microprocessor modes cannot be used

RENESAS

and the PM13 bit in the PM1 register is "1"

5. When using the masked ROM version, write nothing to internal ROM area.

| Address                 | Register                                                                             | Symbol  | After Reset      |

|-------------------------|--------------------------------------------------------------------------------------|---------|------------------|

| 0080h                   |                                                                                      |         |                  |

| 0081h                   |                                                                                      |         |                  |

| 0082h                   |                                                                                      |         |                  |

| 0083h                   |                                                                                      |         |                  |

| 0084h                   |                                                                                      |         |                  |

| 0085h                   |                                                                                      |         |                  |

| 0086h                   |                                                                                      |         |                  |

| 0087h                   |                                                                                      |         |                  |

| to                      |                                                                                      |         |                  |

| 01AFh                   |                                                                                      |         |                  |

| 01B0h                   |                                                                                      |         |                  |

| 01B1h                   |                                                                                      |         |                  |

| 01B2h                   |                                                                                      |         |                  |

| 01B3h                   |                                                                                      |         |                  |

| 01B3h                   | Flash Identification Register <sup>(2)</sup>                                         | FIDR    | XXXXXX00b        |

| 01B5h                   | Flash Memory Control Register 1 <sup>(2)</sup>                                       | FMR1    | 0X00XX0Xb        |

| 01B6h                   |                                                                                      | TWIRT   | 0,00,000         |

|                         | Elash Momony Control Register 0 (2)                                                  | FMR0    | 0000001h         |

| 01B7h<br>01B8h          | Flash Memory Control Register 0 <sup>(2)</sup><br>Address Match Interrupt Register 2 | RMAD2   | 00000001b<br>00h |

|                         | Audress watch interrupt Register 2                                                   | RIVIADZ |                  |

| 01B9h                   | 4                                                                                    |         | 00h              |

| 01BAh                   | Address Match Interrupt Enable Register 2                                            |         | XXh              |

| 01BBh                   | Address Match Interrupt Enable Register 2                                            | AIER2   | XXXXXX00b        |

| 01BCh                   | Address Match Interrupt Register 3                                                   | RMAD3   | 00h              |

| 01BDh                   |                                                                                      |         | 00h              |

| 01BEh                   |                                                                                      |         | XXh              |

| 01C0h                   |                                                                                      |         |                  |

| to                      |                                                                                      |         |                  |

| 024Fh                   |                                                                                      |         |                  |

| 0250h                   |                                                                                      |         |                  |

| 0251h                   |                                                                                      |         |                  |

| 0252h                   |                                                                                      |         |                  |

| 0253h                   |                                                                                      |         |                  |

| 0254h                   |                                                                                      |         |                  |

| 0255h                   |                                                                                      |         |                  |

| 0256h                   |                                                                                      |         |                  |

| 0257h                   |                                                                                      |         |                  |

| 0258h                   |                                                                                      |         |                  |

| 0259h                   |                                                                                      |         |                  |

| 025Ah                   |                                                                                      |         |                  |

| 025Bh                   |                                                                                      |         |                  |

| 025Ch                   |                                                                                      |         |                  |

| 025Dh                   |                                                                                      |         |                  |

| 025Eh                   | Peripheral Clock Select Register                                                     | PCLKR   | 00000011b        |

| 025Fh                   |                                                                                      |         | 1                |

| 0260h                   |                                                                                      |         | 1                |

| to                      |                                                                                      |         |                  |

| 032Fh                   |                                                                                      |         |                  |

| 0330h                   |                                                                                      |         | 1                |

| 0331h                   |                                                                                      |         |                  |

| 0332h                   |                                                                                      |         |                  |

| 0333h                   |                                                                                      |         |                  |

| 0334h                   |                                                                                      |         |                  |

| 0335h                   |                                                                                      |         |                  |

| 0336h                   |                                                                                      |         |                  |

| 0337h                   |                                                                                      |         |                  |

| 0338h                   |                                                                                      |         |                  |

| 0339h                   |                                                                                      |         |                  |

| 0339h<br>033Ah          |                                                                                      |         |                  |

| 033An<br>033Bh          |                                                                                      |         |                  |

|                         |                                                                                      |         |                  |

| 033Ch                   |                                                                                      |         |                  |

|                         |                                                                                      |         |                  |

| 033Dh                   |                                                                                      |         |                  |

| 033Dh<br>033Eh<br>033Fh |                                                                                      |         |                  |

#### SFR Information (3) <sup>(1)</sup> Table 4.3

NOTES:

The blank areas are reserved and cannot be accessed by users.

This register is included in the flash memory version.

X : Nothing is mapped to this bit

| Address                                   | Register                                  | Symbol        | After Reset        |

|-------------------------------------------|-------------------------------------------|---------------|--------------------|

| 0380h                                     | Count Start Flag                          | TABSR         | 00h                |

| 0381h                                     | Clock Prescaler Reset Fag                 | CPSRF         | 0XXXXXXb           |

| 0382h                                     | One-Shot Start Flag                       | ONSF          | 00h                |

| 0383h                                     | Trigger Select Register                   | TRGSR         | 00h                |

| 0384h                                     | Up-Down Flag                              | UDF           | 00h <sup>(2)</sup> |

| 0385h                                     |                                           |               |                    |

| 0386h                                     | Timer A0 Register                         | TA0           | XXh                |

| 0387h                                     |                                           |               | XXh                |

| 0388h                                     | Timer A1 Register                         | TA1           | XXh                |

| 0389h                                     |                                           |               | XXh                |

| 038Ah                                     | Timer A2 Register                         | TA2           | XXh                |

| 038Bh                                     |                                           |               | XXh                |

| 038Ch                                     | Timer A3 Register                         | TA3           | XXh                |

| 038Dh                                     | 1                                         |               | XXh                |

| 038Eh                                     | Timer A4 Register                         | TA4           | XXh                |

| 038Fh                                     | 1                                         |               | XXh                |

| 0390h                                     | Timer B0 Register                         | TB0           | XXh                |

| 0391h                                     |                                           |               | XXh                |

| 0392h                                     | Timer B1 Register                         | TB1           | XXh                |

| 0393h                                     |                                           |               | XXh                |

| 0394h                                     | Timer B2 Register                         | TB2           | XXh                |

| 0395h                                     |                                           |               | XXh                |

| 0396h                                     | Timer A0 Mode Register                    | TAOMR         | 00h                |

| 0397h                                     | Timer A1 Mode Register                    | TA1MR         | 00h                |

| 0398h                                     | Timer A2 Mode Register                    | TA2MR         | 00h                |

| 0399h                                     | Timer A3 Mode Register                    | TA3MR         | 00h                |

| 039Ah                                     | Timer A4 Mode Register                    | TA4MR         | 00h                |

| 039Bh                                     | Timer B0 Mode Register                    | TBOMR         | 00XX0000b          |

| 039Ch                                     | Timer B1 Mode Register                    | TB1MR         | 00XX0000b          |

| 039Dh                                     | Timer B2 Mode Register                    | TB2MR         | 00XX0000b          |

| 039Eh                                     | Timer B2 Special Mode Register            | TB2SC         | XXXXXX00b          |

| 039Fh                                     |                                           |               |                    |

| 03A0h                                     | UART0 Transmit/Receive Mode Register      | U0MR          | 00h                |

| 03A1h                                     | UART0 Bit Rate Generator                  | U0BRG         | XXh                |

| 03A2h                                     | UART0 Transmit Buffer Register            | UOTB          | XXh                |

| 03A3h                                     |                                           |               | XXh                |

| 03A4h                                     | UART0 Transmit/Receive Control Register 0 | UOCO          | 00001000b          |

| 03A5h                                     | UART0 Transmit/Receive Control Register 1 | U0C1          | 00XX0010b          |

| 03A6h                                     | UART0 Receive Buffer Register             | UORB          | XXh                |

| 03A7h                                     |                                           |               | XXh                |

| 03A8h                                     | UART1 Transmit/Receive Mode Register      | U1MR          | 00h                |

| 03A9h                                     | UART1 Bit Rate Generator                  | U1BRG         | XXh                |

| 03AAh                                     | UART1 Transmit Buffer Register            | U1TB          | XXh                |

| 03ABh                                     |                                           | 114.00        | XXh                |

| 03ACh                                     | UART1 Transmit/Receive Control Register 0 | U1C0          | 00001000b          |

| 03ADh                                     | UART1 Transmit/Receive Control Register 1 | U1C1          | 00XX0010b          |

| 03AEh<br>03AFh                            | UART1 Receive Buffer Register             | U1RB          | XXh                |

| 03AFn<br>03B0h                            | UART Transmit/Receive Control Register 2  | UCON          | XXh<br>X0000000b   |

| 03B0h<br>03B1h                            |                                           |               | 4000000            |

| 03B1h<br>03B2h                            |                                           |               |                    |

| 03B2h<br>03B3h                            |                                           |               |                    |

| 03B3h<br>03B4h                            |                                           |               |                    |

| 03B5h                                     |                                           |               |                    |

| 03B6h                                     |                                           |               |                    |

| 03B01                                     |                                           |               |                    |

|                                           | DMA0 Request Factor Select Register       | DM0SL         | 00h                |

|                                           |                                           | DIVIOSE       | 001                |

| 03B8h                                     |                                           |               |                    |

| 03B8h<br>03B9h                            |                                           | DM1SI         | 00b                |

| 03B8h<br>03B9h<br>03BAh                   | DMA1 Request Factor Select Register       | DM1SL         | 00h                |

| 03B8h<br>03B9h<br>03BAh<br>03BBh          | DMA1 Request Factor Select Register       |               |                    |

| 03B8h<br>03B9h<br>03BAh<br>03BBh<br>03BCh |                                           | DM1SL<br>CRCD | XXh                |

| 03B8h<br>03B9h<br>03BAh<br>03BBh          | DMA1 Request Factor Select Register       |               |                    |

| Table 4.5 | SFR Information (5) <sup>(1)</sup> |

|-----------|------------------------------------|

|-----------|------------------------------------|

NOTES:

The blank areas are reserved and cannot be accessed by users.

Bit 5 in the Up-down flag is "0" by reset. However, The values in these bits when read are indeterminate.

X : Nothing is mapped to this bit

| Symbol      | Parameter                                                                           | Measuring Condition |      | Standard |      | Unit |

|-------------|-------------------------------------------------------------------------------------|---------------------|------|----------|------|------|

| Symbol      | Falanielei                                                                          | weasuring condition | Min. | Тур.     | Max. | Unit |

| Vdet4       | Low Voltage Detection Voltage (1)                                                   | Vcc1=0.8V to 5.5V   | 3.3  | 3.8      | 4.4  | V    |

| Vdet3       | Reset Level Detection Voltage (1, 2)                                                |                     | 2.2  | 2.8      | 3.6  | V    |

| Vdet4-Vdet3 | Electric potential difference of Low Voltage<br>Detection and Reset Level Detection |                     | 0.3  |          |      | V    |

| Vdet3s      | Low Voltage Reset Retention Voltage                                                 |                     |      |          | 0.8  | V    |

| Vdet3r      | Low Voltage Reset Release Voltage (3)                                               |                     | 2.2  | 2.9      | 4.0  | V    |

Table 5.9

Low Voltage Detection Circuit Electrical Characteristics

NOTES:

1. Vdet4 > Vdet3.

2. Where reset level detection voltage is less than 2.7 V, if the supply power voltage is greater than the reset level detection voltage, the microcomputer operates with  $f(BCLK) \le 10MHz$ .

3. Vdet3r > Vdet3 is not guaranteed.

4. The voltage detection circuit is designed to use when VCC1 is set to 5V.

### Table 5.10 Power Supply Circuit Timing Characteristics

| Symbol  | Parameter                                                          | Measuring Condition |      | Standard |      | Unit |

|---------|--------------------------------------------------------------------|---------------------|------|----------|------|------|

| Symbol  | Falanlelei                                                         | Measuring Condition | Min. | Тур.     | Max. | Unit |

| td(P-R) | Time for Internal Power Supply Stabilization<br>During Powering-On | Vcc1=2.7V to 5.5V   |      |          | 2    | ms   |

| td(R-S) | STOP Release Time                                                  |                     |      |          | 150  | μS   |

| td(W-S) | Low Power Dissipation Mode Wait Mode<br>Release Time               |                     |      |          | 150  | μS   |

| td(S-R) | Brown-out Detection Reset (Hardware Reset 2)<br>Release Wait Time  | VCC1=Vdet3r to 5.5V |      | 6 (1)    | 20   | ms   |

| td(E-A) | Low Voltage Detection Circuit Operation Start<br>Time              | Vcc1=2.7V to 5.5V   |      |          | 20   | μs   |

NOTES:

1. When Vcc1 = 5V.

| Symbol | Doromot                                          | Parameter                            |                             | Measuring Condition Sta                                                     |      | Standard | b    | Unit |

|--------|--------------------------------------------------|--------------------------------------|-----------------------------|-----------------------------------------------------------------------------|------|----------|------|------|

| Symbol | Falamen                                          | ei                                   | Ivieas                      |                                                                             | Min. | Тур.     | Max. | Onit |

| Icc    | Power Supply Current<br>(Vcc1=Vcc2=2.7V to 3.6V) | In single-chip<br>mode, the output   | Mask ROM                    | f(BCLK)=10MHz<br>No division                                                |      | 8        |      | mA   |

|        | · · · · · · · · · · · · · · · · · · ·            | pins are open and other pins are Vss |                             | No division,<br>On-chip oscillation                                         |      | 1        |      | mA   |

|        |                                                  |                                      | Flash<br>Memory             | f(BCLK)=10MHz,<br>No division                                               |      | 8        | 13   | mA   |

|        |                                                  |                                      | ,                           | No division,<br>On-chip oscillation                                         |      | 1.8      |      | mA   |

|        |                                                  | Program                              | f(BCLK)=10MHz,<br>VCC1=3.0V |                                                                             | 12   |          | mA   |      |

|        |                                                  |                                      | Flash Memory<br>Erase       | f(BCLK)=10MHz,<br>VCC1=3.0V                                                 |      | 22       |      | mA   |

|        |                                                  |                                      | Mask ROM                    | f(XCIN)=32kHz<br>Low power dissipation<br>mode, ROM <sup>(3)</sup>          |      | 25       |      | μA   |

|        |                                                  |                                      | Flash Memory                | f(BCLK)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |      | 25       |      | μA   |

|        |                                                  |                                      |                             | f(BCLK)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |      | 420      |      | μA   |

|        |                                                  |                                      |                             | On-chip oscillation,<br>Wait mode                                           |      | 45       |      | μA   |

|        |                                                  |                                      | Mask ROM<br>Flash Memory    | f(BCLK)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability High  |      | 6.0      |      | μΑ   |

|        |                                                  |                                      |                             | f(BCLK)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability Low   |      | 1.8      |      | μA   |

|        |                                                  |                                      |                             | Stop mode<br>Topr =25°C                                                     |      | 0.7      | 3.0  | μΑ   |

| Idet4  | Low Voltage Detection Diss                       | sipation Current (4)                 |                             |                                                                             |      | 0.6      | 4    | μΑ   |

| Idet3  | Reset Area Detection Dissi                       | pation Current (4)                   |                             |                                                                             |      | 0.4      | 2    | μΑ   |

Table 5.31 Electrical Characteristics (2) (1)

NOTES:

1. Referenced to Vcc1=Vcc2=2.7 to 3.3V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(BCLK)=10MHz unless otherwise specified.

2. With one timer operated using fC32.

3. This indicates the memory in which the program to be executed exists.

4. Idet is dissipation current when the following bit is set to "1" (detection circuit enabled).

Idet4: VC27 bit in the VCR2 register

Idet3: VC26 bit in the VCR2 register

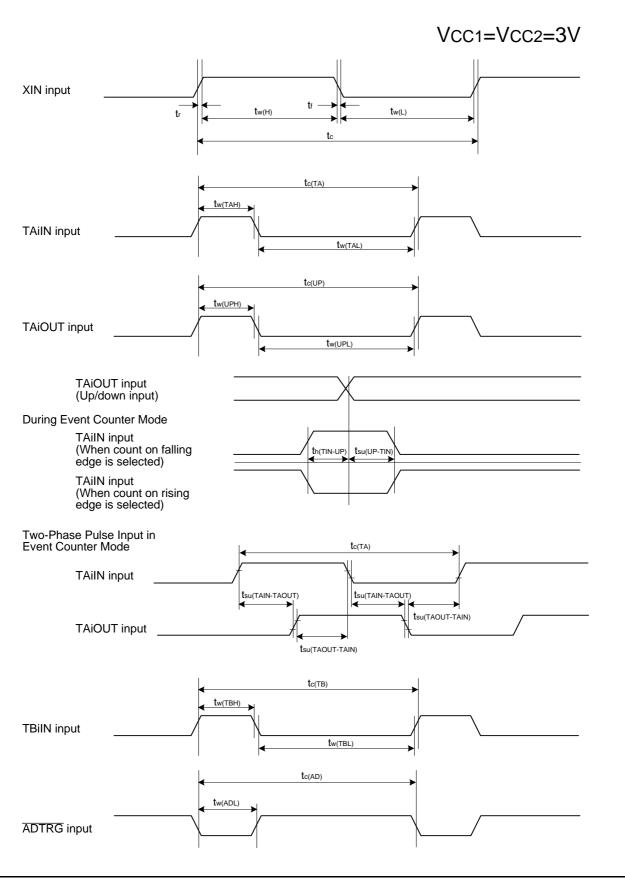

### VCC1=VCC2=3V

### **Timing Requirements**

### (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

### Table 5.32 External Clock Input (XIN input)<sup>(1)</sup>

| Symbol | Parameter                             | Stan     | Unit     |       |

|--------|---------------------------------------|----------|----------|-------|

|        |                                       | Min.     | Max.     | Offic |

| tc     | External Clock Input Cycle Time       | (NOTE 2) |          | ns    |

| tw(H)  | External Clock Input HIGH Pulse Width | (NOTE 3) |          | ns    |

| tw(L)  | External Clock Input LOW Pulse Width  | (NOTE 3) |          | ns    |

| tr     | External Clock Rise Time              |          | (NOTE 4) | ns    |

| tr     | External Clock Fall Time              |          | (NOTE 4) | ns    |

NOTES:

- 1. The condition is Vcc1=Vcc2=2.7 to 3.0V.

- 2. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times Vcc_2 - 44}$$

[ns]

3. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times \text{Vcc1} - 44} \times 0.4 \text{ [ns]}$$

4. Calculated according to the Vcc1 voltage as follows:  $-10 \times Vcc1 + 45$  [ns]

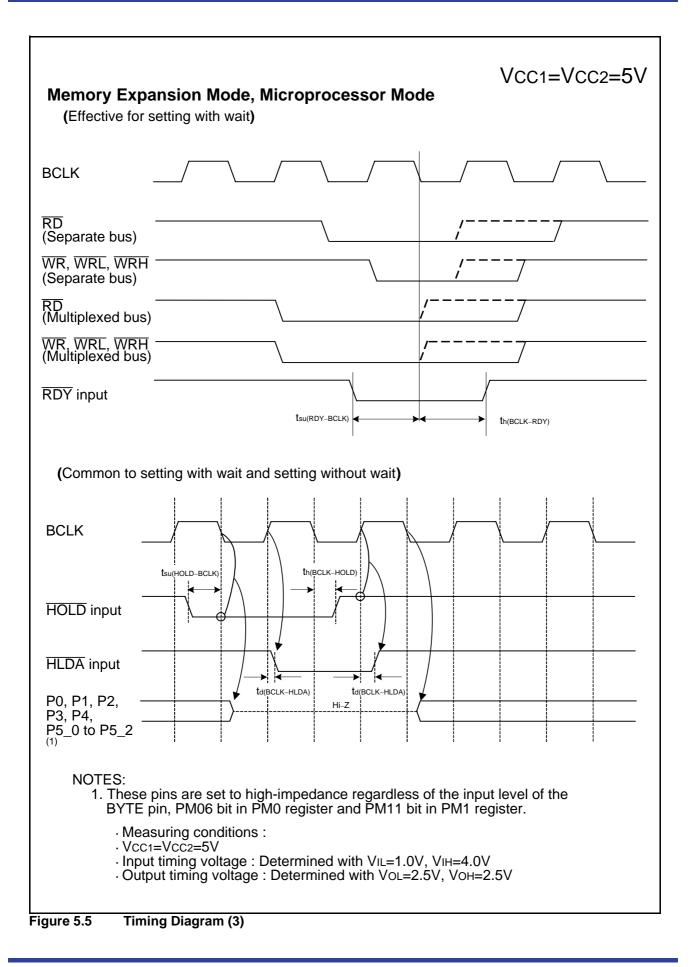

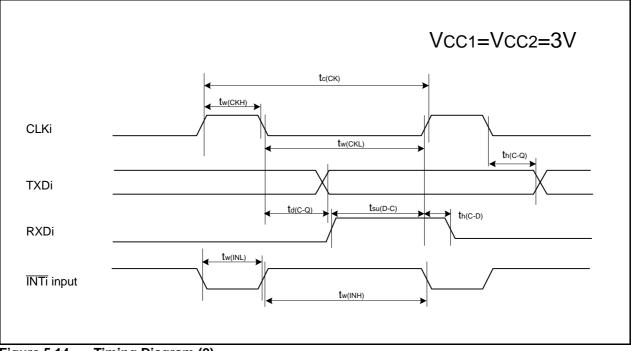

### Table 5.33 Memory Expansion Mode and Microprocessor Mode

| Symbol         | Parameter                                                  | Star | Standard |      |  |

|----------------|------------------------------------------------------------|------|----------|------|--|

|                | Parameter                                                  | Min. | Max.     | Unit |  |

| tac1(RD-DB)    | Data Input Access Time (for setting with no wait)          |      | (NOTE 1) | ns   |  |

| tac2(RD-DB)    | Data Input Access Time (for setting with wait)             |      | (NOTE 2) | ns   |  |

| tac3(RD-DB)    | Data Input Access Time (when accessing multiplex bus area) |      | (NOTE 3) | ns   |  |

| tsu(DB-RD)     | Data Input Setup Time                                      | 50   |          | ns   |  |

| tsu(RDY-BCLK)  | RDY Input Setup Time                                       | 40   |          | ns   |  |

| tsu(HOLD-BCLK) | HOLD Input Setup Time                                      | 50   |          | ns   |  |

| th(RD-DB)      | Data Input Hold Time                                       | 0    |          | ns   |  |

| th(BCLK-RDY)   | RDY Input Hold Time                                        | 0    |          | ns   |  |

| th(BCLK-HOLD)  | HOLD Input Hold Time                                       | 0    |          | ns   |  |

NOTES:

1. Calculated according to the BCLK frequency as follows:

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 60[ns]$$

n is "2" for 1-wait setting, "3" for 2-wait setting and "4" for 3-wait setting.

RENESAS

3. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 60[ns]$$

n is "2" for 2-wait setting, "3" for 3-wait setting.

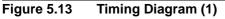

### VCC1=VCC2=3V

### Switching Characteristics

.

### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

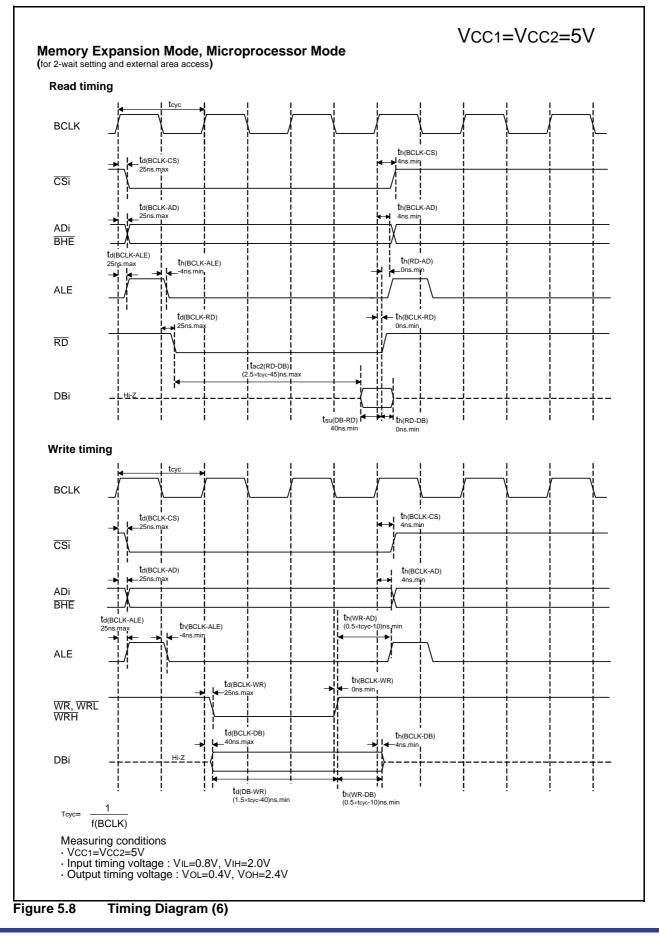

| Table 5.48 | Memory Expansion and Microprocessor Modes (for 2- to 3-wait setting, external area |

|------------|------------------------------------------------------------------------------------|

|            | access and multiplex bus selection)                                                |

| Symbol        | Parameter                                             |             | Stan     | dard | Unit |

|---------------|-------------------------------------------------------|-------------|----------|------|------|

| Symbol        | Parameter                                             | IEIEI       |          | Max. |      |

| td(BCLK-AD)   | Address Output Delay Time                             |             |          | 50   | ns   |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)        |             | 4        |      | ns   |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)          |             | (NOTE 1) |      | ns   |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)          |             | (NOTE 1) |      | ns   |

| td(BCLK-CS)   | Chip Select Output Delay Time                         |             |          | 50   | ns   |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)    |             | 4        |      | ns   |

| th(RD-CS)     | Chip Select Output Hold Time (in relation to RD)      |             | (NOTE 1) |      | ns   |

| th(WR-CS)     | Chip Select Output Hold Time (in relation to WR)      |             | (NOTE 1) |      | ns   |

| td(BCLK-RD)   | RD Signal Output Delay Time                           |             |          | 40   | ns   |

| th(BCLK-RD)   | RD Signal Output Hold Time                            |             | 0        |      | ns   |

| td(BCLK-WR)   | WR Signal Output Delay Time                           |             |          | 40   | ns   |

| th(BCLK-WR)   | WR Signal Output Hold Time                            | See         | 0        |      | ns   |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)          | Figure 5.12 |          | 50   | ns   |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK)           |             | 4        |      | ns   |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)            |             | (NOTE 2) |      | ns   |

| th(WR-DB)     | Data Output Hold Time (in relation to WR)             |             | (NOTE 1) |      | ns   |

| td(BCLK-HLDA) | HLDA Output Delay Time                                |             |          | 40   | ns   |

| td(BCLK-ALE)  | ALE Signal Output Delay Time (in relation to BCLK)    |             |          | 25   | ns   |

| th(BCLK-ALE)  | ALE Signal Output Hold Time (in relation to BCLK)     |             | -4       |      | ns   |

| td(AD-ALE)    | ALE Signal Output Delay Time (in relation to Address) |             | (NOTE 3) |      | ns   |

| th(AD-ALE)    | ALE Signal Output Hold Time (in relation to Address)  |             | (NOTE 4) |      | ns   |

| td(AD-RD)     | RD Signal Output Delay From the End of Address        |             | 0        |      | ns   |

| td(AD-WR)     | WR Signal Output Delay From the End of Address        |             | 0        |      | ns   |

| tdz(RD-AD)    | Address Output Floating Start Time                    |             |          | 8    | ns   |

n is "2" for 2-wait setting, "3" for 3-wait setting.

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10[ns]$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 50[ns]$$

3. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(\text{BCLK})} - 40[\text{ns}]$$

4. Calculated according to the BCLK frequency as follows:

RENESAS

Figure 5.14 Timing Diagram (2)

| Symbol | Parameter                                    |                |      | Unit |      |       |

|--------|----------------------------------------------|----------------|------|------|------|-------|

| Symbol |                                              |                | Min. | Тур. | Max. | Unit  |

| -      | Program and Erase Endurance <sup>(3)</sup>   |                | 100  |      |      | cycle |

| -      | Word Program Time (Vcc1=5.0V)                |                |      | 25   | 200  | μS    |

| -      | Lock Bit Program Time                        |                |      | 25   | 200  | μS    |

| -      | Block Erase Time                             | 4-Kbyte block  | 4    | 0.3  | 4    | S     |

| -      | (Vcc1=5.0V)                                  | 8-Kbyte block  |      | 0.3  | 4    | S     |

| -      |                                              | 32-Kbyte block |      | 0.5  | 4    | S     |

| -      |                                              | 64-Kbyte block |      | 0.8  | 4    | S     |

| -      | Erase All Unlocked Blocks Time (2)           |                |      |      | 4×n  | S     |

| tPS    | Flash Memory Circuit Stabilization Wait Time | e              |      |      | 15   | μS    |

| -      | Data Hold Time <sup>(5)</sup>                |                | 20   |      |      | year  |

### Table 5.53 Flash Memory Version Electrical Characteristics (1) for 100 cycle products (B, U)

# Table 5.54Flash Memory Version Electrical Characteristics (6) for 10,000 cycle products (B7, U7)(Block A and Block 1 (7))

| Symbol | Parameter                                        |               |            | Unit |      |       |

|--------|--------------------------------------------------|---------------|------------|------|------|-------|

| Symbol | Faranielei                                       |               | Min.       | Тур. | Max. | Unit  |

| -      | Program and Erase Endurance <sup>(3, 8, 9)</sup> |               | 10,000 (4) |      |      | cycle |

| -      | Word Program Time (Vcc1=5.0V)                    |               |            | 25   |      | μS    |

| -      | Lock Bit Program Time                            |               |            | 25   |      | μS    |

| _      | Block Erase Time<br>(Vcc1=5.0V)                  | 4-Kbyte block | 4          | 0.3  |      | S     |

| tPS    | Flash Memory Circuit Stabilization Wait Time     |               |            |      | 15   | μS    |

| -      | Data Hold Time <sup>(5)</sup>                    |               | 20         |      |      | year  |

NOTES:

- 1. Referenced to Vcc1=4.5 to 5.5V at  $T_{opr} = 0$  to 60 °C unless otherwise specified.

- 2. n denotes the number of block erases.

Program and Erase Endurance refers to the number of times a block erase can be performed. If the program and erase endurance is n (n=100, 1,000, or 10,000), each block can be erased n times. For example, if a 4 Kbytes block A is erased after writing 1 word data 2,048 times, each to a different address, this counts as one program and erase endurance. Data cannot be written to the same address more than once without erasing the block. (Rewrite prohibited)

- 4. Maximum number of E/W cycles for which operation is guaranteed.

- 5. Ta (ambient temperature)=55 °C. As to the data hold time except Ta=55 °C, please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor.

- 6. Referenced to Vcc1 = 4.5 to 5.5V at Topr = −40 to 85 °C (B7, U7 (T version)) / −40 to 125 °C (B7, U7 (V version)) unless otherwise specified.

- 7. Table 5.54 applies for block A or block 1 program and erase endurance > 1,000. Otherwise, use Table 5.53.

- 8. To reduce the number of program and erase endurance when working with systems requiring numerous rewrites, write to unused word addresses within the block instead of rewrite. Erase block only after all possible addresses are used. For example, an 8-word program can be written 256 times maximum before erase becomes necessary. Maintaining an equal number of erasure between block A and block 1 will also improve efficiency. It is important to track the total number of times erasure is used.

- 9. Should erase error occur during block erase, attempt to execute clear status register command, then block erase command at least three times until erase error disappears.

- 10. Set the PM17 bit in the PM1 register to "1" (wait state) when executing more than 100 times rewrites (B7 and U7).

- 11. Customers desiring E/W failure rate information should contact their Renesas technical support representative.

# Table 5.55Flash Memory Version Program/Erase Voltage and Read Operation Voltage<br/>Characteristics (at Topr = 0 to 60 °C(B, U), Topr = -40 to 85 °C (B7, U7 (T version)) / -40<br/>to 125 °C (B7, U7 (V version))

| Flash Program, Erase Voltage | Flash Read Operation Voltage |

|------------------------------|------------------------------|

| $VCC1 = 5.0 V \pm 0.5 V$     | Vcc1=4.0 to 5.5 V            |

# VCC1=VCC2=5V

| Symbol  | Parameter                                                                                              |                                                                                                                | Measuring Condition                                                                                                      | Standard             |          |      | Unit |      |

|---------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|----------|------|------|------|

| ,       |                                                                                                        |                                                                                                                |                                                                                                                          | modeuring contaition | Min.     | Тур. | Max. | Onic |

| Vон     | HIGH<br>Output<br>Voltage <sup>(2)</sup>                                                               | P6_0 to P6_7, P7_2 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P1                           | P10_0 to P10_7,                                                                                                          | IOH=-5mA             | Vcc1-2.0 |      | Vcc1 | v    |

|         | P0_0 to P0_7, P1_0 to P1_7, P2_0<br>P3_0 to P3_7, P4_0 to P4_7, P5_0<br>P12_0 to P12_7, P13_0 to P13_7 |                                                                                                                | 7, P5_0 to P5_7,                                                                                                         | IOH=-5mA             | Vcc2-2.0 |      | Vcc2 |      |

| Vон     | HIGH<br>Output<br>Voltage <sup>(2)</sup>                                                               | P6_0 to P6_7, P7_2 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P1                           | P10_0 to P10_7,                                                                                                          | ОН=-200μА            | Vcc1-0.3 |      | Vcc1 | v    |

|         |                                                                                                        | P0_0 to P0_7, P1_0 to P1_7<br>P3_0 to P3_7, P4_0 to P4_7<br>P12_0 to P12_7, P13_0 to P                         | ', P5_0 to P5_7,                                                                                                         | ЮН=-200μА            | Vcc2-0.3 |      | Vcc2 |      |

| Vон     | HIGH Outpu                                                                                             | t Voltage XOUT                                                                                                 | HIGHPOWER                                                                                                                | IOH=-1mA             | Vcc1-2.0 |      | VCC1 | V    |

|         |                                                                                                        |                                                                                                                | LOWPOWER                                                                                                                 | IOH=-0.5mA           | Vcc1-2.0 |      | VCC1 | v    |

|         | HIGH Outpu                                                                                             | t Voltage XCOUT                                                                                                | HIGHPOWER                                                                                                                | With no load applied |          | 2.5  |      | v    |

|         |                                                                                                        |                                                                                                                | LOWPOWER                                                                                                                 | With no load applied |          | 1.6  |      | v    |

| Vol     | LOW<br>Output<br>Voltage <sup>(2)</sup>                                                                | P6_0 to P6_7, P7_0 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P1                           | P10 0 to P10 7,                                                                                                          | IOL=5mA              |          |      | 2.0  | v    |

|         |                                                                                                        | P0_0 to P0_7, P1_0 to P1_7<br>P3_0 to P3_7, P4_0 to P4_7<br>P12_0 to P12_7, P13_0 to P                         | 7, P2_0 to P2_7,<br>7, P5_0 to P5_7,                                                                                     | IOL=5mA              |          |      | 2.0  | V    |

| Vol     | LOW<br>Output<br>Voltage <sup>(2)</sup>                                                                | P6_0 to P6_7, P7_0 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P1                           | P10_0 to P10_7,                                                                                                          | IOL=200μA            |          |      | 0.45 | v    |

|         | P0_0 to P0_7, P1_0 to P1_7, F<br>P3_0 to P3_7, P4_0 to P4_7, F<br>P12_0 to P12_7, P13_0 to P13         | 7, P5_0 to P5_7,                                                                                               | IOL=200μA                                                                                                                |                      |          | 0.45 | V    |      |

| Vol     | LOW Output                                                                                             | t Voltage XOUT                                                                                                 | HIGHPOWER                                                                                                                | IOL=1mA              |          |      | 2.0  |      |

|         |                                                                                                        |                                                                                                                | LOWPOWER                                                                                                                 | IOL=0.5mA            |          |      | 2.0  | V    |

|         | LOW Output                                                                                             | t Voltage XCOUT                                                                                                | HIGHPOWER                                                                                                                | With no load applied |          | 0    |      |      |

|         |                                                                                                        |                                                                                                                | LOWPOWER                                                                                                                 | With no load applied |          | 0    |      | V    |

| Vt+-Vt- | Hysteresis                                                                                             | HOLD, RDY, TA0IN to TA4I<br>INT0 to INT5, NMI, ADTRG,<br>TA0OUT to TA4OUT, KI0 to<br>SCL0 to SCL2, SDA0 to SD. | CTS0 to CTS2, CLK0 to CLK4,<br>KI3, RXD0 to RXD2,                                                                        |                      | 0.2      |      | 1.0  | V    |

| Vt+-Vt- | Hysteresis                                                                                             | RESET                                                                                                          |                                                                                                                          |                      | 0.2      |      | 2.5  | V    |

| Ін      | HIGH Input<br>Current <sup>(2)</sup>                                                                   |                                                                                                                | P12_7, P13_0 to P13_7,                                                                                                   | VI=5V                |          |      | 5.0  | μΑ   |

| lı.     | LOW Input<br>Current <sup>(2)</sup>                                                                    |                                                                                                                | 12_7, P13_0 to P13_7,                                                                                                    | VI=0V                |          |      | -5.0 | μΑ   |

| Rpullup | Pull-Up<br>Resistance<br>(2)                                                                           | P4_0 to P4_7, P5_0 to P5_7                                                                                     | , P2_0 to P2_7, P3_0 to P3_7,<br>, P6_0 to P6_7, P7_2 to P7_7,<br>P9_0 to P9_7, P10_0 to P10_7,<br>12_7, P13_0 to P13_7, | VI=0V                | 30       | 50   | 170  | kΩ   |

| Rfxin   | Feedback R                                                                                             | esistance XIN                                                                                                  |                                                                                                                          |                      |          | 1.5  |      | MΩ   |

| Rfxcin  | Feedback R                                                                                             | esistance XCIN                                                                                                 |                                                                                                                          |                      |          | 15   |      | MΩ   |

| Vram    | RAM Retent                                                                                             | ion Voltage                                                                                                    |                                                                                                                          | At stop mode         | 2.0      |      |      | V    |

#### Table 5.57 Electrical Characteristics (1) (1)

NOTES:

1. Referenced to Vcc1=Vcc2=4.0 to 5.5V, Vss = 0V at Topr = -40 to 85°C / -40 to 125°C, f(BCLK)=24MHz unless otherwise specified. T version = -40 to 85°C, V version =-40 to 125°C.

2. There is no external connections for port P1\_0 to P1\_7, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version.

# VCC1=VCC2=5V

### **Timing Requirements**

# (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -40 to $85^{\circ}$ C (T version) / -40 to $125^{\circ}$ C (V version) unless otherwise specified)

### Table 5.60 Timer A Input (Counter Input in Event Counter Mode)

| Symbol  | Parameter                    |      | Standard |      |  |

|---------|------------------------------|------|----------|------|--|

| Symbol  | Falanlelei                   | Min. | Max.     | Unit |  |

| tc(TA)  | TAiIN Input Cycle Time       | 100  |          | ns   |  |

| tw(TAH) | TAIIN Input HIGH Pulse Width | 40   |          | ns   |  |