Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 24MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                              |

| Peripherals                | DMA, WDT                                                                         |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 4K x 8                                                                           |

| RAM Size                   | 31K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                      |

| Data Converters            | A/D 26x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP                                                                         |

| Supplier Device Package    | 100-LFQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30626fjpgp-u5c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

As of Dec. 2005

|                 |     |               | -               | -                           |                        |                   |

|-----------------|-----|---------------|-----------------|-----------------------------|------------------------|-------------------|

| Туре No.        |     | ROM Capacity  | RAM<br>Capacity | Package Type <sup>(1)</sup> | Re                     | emarks            |

| M3062CM6V-XXXFP | (P) | 48 Kbytes     | 4 Kbytes        | PRQP0100JB-A                | Mask ROM               | V Version         |

| M3062CM6V-XXXGP | (P) |               |                 | PLQP0100KB-A                | version                | (High reliability |

| M3062EM6V-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        | 125°C version)    |

| M3062CM8V-XXXFP | (P) | 64 Kbytes     | 4 Kbytes        | PRQP0100JB-A                |                        |                   |

| M3062CM8V-XXXGP | (P) |               |                 | PLQP0100KB-A                |                        |                   |

| M3062EM8V-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        |                   |

| M3062CMAV-XXXFP | (P) | 96 Kbytes     | 5 Kbytes        | PRQP0100JB-A                |                        |                   |

| M3062CMAV-XXXGP | (P) |               |                 | PLQP0100KB-A                |                        |                   |

| M3062EMAV-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        |                   |

| M3062AMCV-XXXFP | (D) | 128 Kbytes    | 10 Kbytes       | PRQP0100JB-A                |                        |                   |

| M3062AMCV-XXXGP | (D) |               |                 | PLQP0100KB-A                |                        |                   |

| M3062BMCV-XXXGP | (P) |               |                 | PRQP0080JA-A                |                        |                   |

| M3062AFCVFP     | (D) | 128K+4 Kbytes | 10 Kbytes       | PRQP0100JB-A                | Flash                  |                   |

| M3062AFCVGP     | (D) |               |                 | PLQP0100KB-A                | memory                 |                   |

| M3062BFCVGP     | (P) |               |                 | PRQP0080JA-A                | version <sup>(2)</sup> |                   |

| M3062JFHVFP     | (P) | 384K+4 Kbytes | 31 Kbytes       | PRQP0100JB-A                |                        |                   |

| M3062JFHVGP     | (P) |               |                 | PLQP0100KB-A                |                        |                   |

Table 1.7 Product List (4) (V version (M16C/62PT))

(D): Under development

(P): Under planning

NOTES:

1. The old package type numbers of each package type are as follows.

PLQP0128KB-A : 128P6Q-A, PRQP0100JB-A : 100P6S-A, PLQP0100KB-A : 100P6Q-A,

PRQP0080JA-A : 80P6S-A

2. In the flash memory version, there is 4K bytes area (block A).

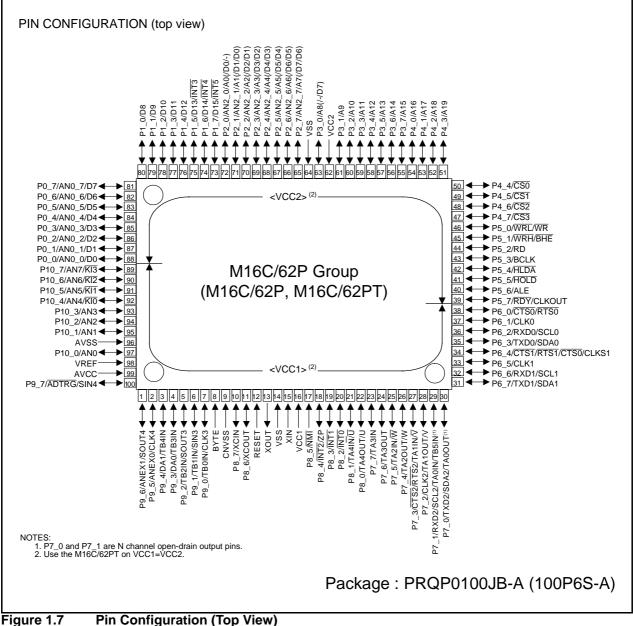

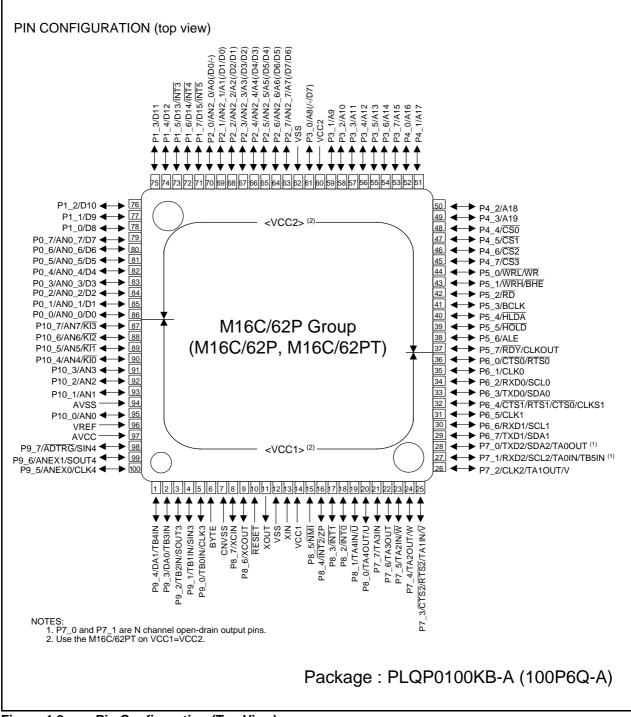

#### Pin Configuration (Top View)

Figure 1.8 Pin Configuration (Top View)

### 2. Central Processing Unit (CPU)

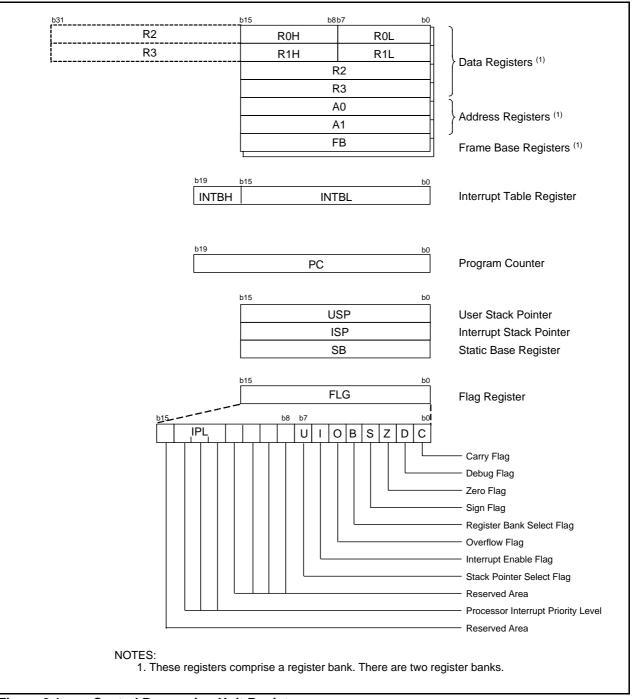

Figure 2.1 shows the CPU registers. The CPU has 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB comprise a register bank. There are two register banks.

### 2.1 Data Registers (R0, R1, R2 and R3)

The R0 register consists of 16 bits, and is used mainly for transfers and arithmetic/logic operations. R1 to R3 are the same as R0.

The R0 register can be separated between high (R0H) and low (R0L) for use as two 8-bit data registers. R1H and R1L are the same as R0H and R0L. Conversely, R2 and R0 can be combined for use as a 32-bit data register (R2R0). R3R1 is the same as R2R0.

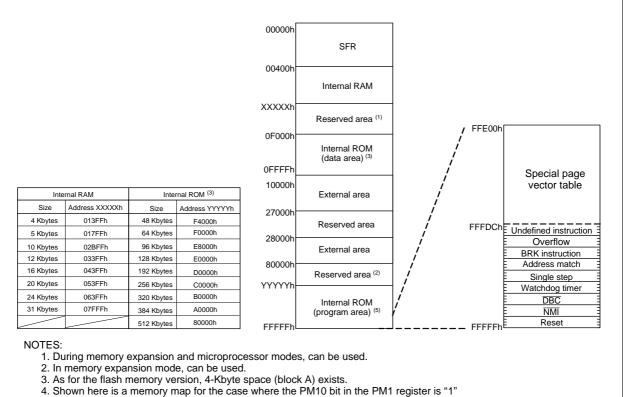

### 3. Memory

Figure 3.1 is a Memory Map of the M16C/62P group. The address space extends the 1M bytes from address 00000h to FFFFFh.

The internal ROM is allocated in a lower address direction beginning with address FFFFFh. For example, a 64-Kbyte internal ROM is allocated to the addresses from F0000h to FFFFFh.

As for the flash memory version, 4-Kbyte space (block A) exists in 0F000h to 0FFFFh. 4-Kbyte space is mainly for storing data. In addition to storing data, 4-Kbyte space also can store programs.

The fixed interrupt vector table is allocated to the addresses from FFFDCh to FFFFFh. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 00400h. For example, a 10-Kbyte internal RAM is allocated to the addresses from 00400h to 02BFFh. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SRF is allocated to the addresses from 00000h to 003FFh. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE00h to FFFDBh. This vector is used by the JMPS or JSRS instruction. For details, refer to the **M16C/60 and M16C/20 Series Software Manual**.

In memory expansion and microprocessor modes, some areas are reserved for future use and cannot be used by users. Use M16C/62P (80-pin version) and M16C/62PT in single-chip mode. The memory expansion and microprocessor modes cannot be used

RENESAS

and the PM13 bit in the PM1 register is "1"

5. When using the masked ROM version, write nothing to internal ROM area.

| Table 4.2 | SFR Information ( | ( <b>2)</b> <sup>(1)</sup> |

|-----------|-------------------|----------------------------|

|-----------|-------------------|----------------------------|

| Address         | Register                                                                                      | Symbol         | After Reset            |

|-----------------|-----------------------------------------------------------------------------------------------|----------------|------------------------|

| 0040h           |                                                                                               |                |                        |

| 0041h           |                                                                                               |                |                        |

| 0042h           |                                                                                               |                |                        |

| 0043h           |                                                                                               |                |                        |

| 0044h           | INT3 Interrupt Control Register                                                               | INT3IC         | XX00X000b              |

| 0045h           | Timer B5 Interrupt Control Register                                                           | TB5IC          | XXXXX000b              |

| 0046h           | Timer B4 Interrupt Control Register, UART1 BUS Collision Detection Interrupt Control Register | TB4IC, U1BCNIC | XXXXX000b              |

| 0047h           | Timer B3 Interrupt Control Register, UART0 BUS Collision Detection Interrupt Control Register | TB3IC, U0BCNIC | XXXXX000b              |

| 0048h           | SI/O4 Interrupt Control Register, INT5 Interrupt Control Register                             | S4IC, INT5IC   | XX00X000b              |

| 0049h           | SI/O3 Interrupt Control Register, INT4 Interrupt Control Register                             | S3IC, INT4IC   | XX00X000b              |

| 004Ah           | UART2 Bus Collision Detection Interrupt Control Register                                      | BCNIC          | XXXXX000b              |

| 004Bh           | DMA0 Interrupt Control Register                                                               | DM0IC          | XXXXX000b              |

| 004Ch           | DMA1 Interrupt Control Register                                                               | DM1IC          | XXXXX000b              |

| 004Dh           | Key Input Interrupt Control Register                                                          | KUPIC          | XXXXX000b              |

| 004Eh           | A/D Conversion Interrupt Control Register                                                     | ADIC           | XXXXX000b              |

| 004Fh           | UART2 Transmit Interrupt Control Register                                                     | S2TIC          | XXXXX000b              |

| 0050h           | UART2 Receive Interrupt Control Register                                                      | S2RIC          | XXXXX000b              |

| 0051h           | UARTO Transmit Interrupt Control Register                                                     | SOTIC          | XXXXX000b              |

| 0052h           | UARTO Receive Interrupt Control Register                                                      | SORIC          | XXXXX000b              |

| 0053h           | UART1 Transmit Interrupt Control Register                                                     | S1TIC          | XXXXX000b              |

| 0054h           | UART1 Receive Interrupt Control Register                                                      | S1RIC          | XXXXX000b              |

| 0055h           | Timer A0 Interrupt Control Register                                                           | TAOIC          | XXXXX000b              |

| 0055h           | Timer A1 Interrupt Control Register                                                           | TAIIC          | XXXXX000b              |

| 0050n<br>0057h  | Timer A2 Interrupt Control Register                                                           | TATIC          | XXXXX000b              |

| 0057h<br>0058h  | Timer A3 Interrupt Control Register                                                           | TA3IC          | XXXXX000b              |

| 0058h<br>0059h  |                                                                                               | TASIC          |                        |

|                 | Timer A4 Interrupt Control Register                                                           |                | XXXXX000b<br>XXXXX000b |

| 005Ah           | Timer B0 Interrupt Control Register                                                           | TBOIC          |                        |

| 005Bh           | Timer B1 Interrupt Control Register                                                           | TB1IC          | XXXXX000b              |

| 005Ch           | Timer B2 Interrupt Control Register                                                           | TB2IC          | XXXXX000b              |

| 005Dh           | INT0 Interrupt Control Register                                                               | INTOIC         | XX00X000b              |

| 005Eh           | INT1 Interrupt Control Register                                                               | INT1IC         | XX00X000b              |

| 005Fh           | INT2 Interrupt Control Register                                                               | INT2IC         | XX00X000b              |

| 0060h           |                                                                                               |                |                        |

| 0061h           |                                                                                               |                |                        |

| 0062h           |                                                                                               |                |                        |

| 0063h           |                                                                                               |                |                        |

| 0064h           |                                                                                               |                |                        |

| 0065h           |                                                                                               |                |                        |

| 0066h           |                                                                                               |                |                        |

| 0067h           |                                                                                               |                |                        |

| 0068h           |                                                                                               |                |                        |

| 0069h           |                                                                                               |                |                        |

| 006Ah           |                                                                                               |                |                        |

| 006Bh           |                                                                                               |                |                        |

| 006Ch           |                                                                                               | 1              |                        |

| 006Dh           |                                                                                               | 1              |                        |

| 006Eh           |                                                                                               | 1              |                        |

| 006Fh           |                                                                                               |                |                        |

| 0070h           |                                                                                               |                |                        |

| 0070h           |                                                                                               |                |                        |

| 0072h           |                                                                                               | 1              |                        |

| 0072h           |                                                                                               | 1              |                        |

| 0073h<br>0074h  |                                                                                               |                |                        |

| 007411<br>0075h |                                                                                               |                |                        |

| 0075h           |                                                                                               |                |                        |

| 0076h           |                                                                                               | -              |                        |

|                 |                                                                                               | +              | -                      |

| 0078h           |                                                                                               |                |                        |

| 0079h           |                                                                                               |                |                        |

| 007Ah           |                                                                                               | 1              |                        |

| 007Bh           |                                                                                               |                |                        |

| 007Ch           |                                                                                               |                |                        |

| 007Dh           |                                                                                               |                |                        |

| 007Eh           |                                                                                               |                |                        |

| 007Eh           |                                                                                               |                |                        |

NOTES: 1. The blank areas are reserved and cannot be accessed by users.

X : Nothing is mapped to this bit

| Cumple al  |                                | Devenueter                                                                                                                                                                                                                                    |                                 | Standar | d                                                                                    | الما ا |

|------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------|--------------------------------------------------------------------------------------|--------|

| Symbol     |                                | Parameter                                                                                                                                                                                                                                     | Min.                            | Тур.    | Max.                                                                                 | Unit   |

| VCC1, VCC2 | Supply Voltage (               | (Vcc1 ≥ Vcc2)                                                                                                                                                                                                                                 | 2.7                             | 5.0     | 5.5                                                                                  | V      |

| AVcc       | Analog Supply V                | /oltage                                                                                                                                                                                                                                       |                                 | Vcc1    |                                                                                      | V      |

| Vss        | Supply Voltage                 | •                                                                                                                                                                                                                                             |                                 | 0       |                                                                                      | V      |

| AVss       | Analog Supply V                | /oltage                                                                                                                                                                                                                                       |                                 | 0       |                                                                                      | V      |

| Vih        | HIGH Input<br>Voltage          | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P12_0 to P12_7, P13_0 to P13_7                                                                                                                                                                   | 0.8Vcc2                         |         | Vcc2                                                                                 | V      |

|            |                                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(during single-chip mode)                                                                                                                                                                   | 0.8Vcc2                         |         | Vcc2                                                                                 | V      |

|            |                                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(data input during memory expansion and microprocessor mode)                                                                                                                                | 0.5Vcc2                         |         | Vcc2                                                                                 | V      |

|            |                                | P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_7, P14_0, P14_1,<br>XIN, RESET, CNVSS, BYTE                                                                                                           | 0.8Vcc1                         |         | Vcc1                                                                                 | V      |

|            |                                | P7_0, P7_1                                                                                                                                                                                                                                    | 0.8Vcc1                         |         | 6.5                                                                                  | V      |

| VIL        | LOW Input<br>Voltage           | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P12_0 to P12_7, P13_0 to P13_7                                                                                                                                                                   | 0                               |         | 0.2Vcc2                                                                              | V      |

|            |                                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(during single-chip mode)                                                                                                                                                                   | to P1_7, P2_0 to P2_7, P3_0 0.2 | 0.2Vcc2 | V                                                                                    |        |

|            |                                | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(data input during memory expansion and microprocessor mode)                                                                                                                                | 0                               |         | 0.16Vcc2                                                                             | V      |

|            |                                | P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, P11_0 to P11_7, P14_0, P14_1,<br>XIN, RESET, CNVSS, BYTE                                                                                                           | 0                               |         | Vcc2           Vcc2           Vcc1           6.5           0.2Vcc2           0.2Vcc2 | V      |

| IOH(peak)  | HIGH Peak<br>Output Current    | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |                                 |         | -10.0                                                                                | mA     |

| IOH(avg)   | HIGH Average<br>Output Current | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |                                 |         | -5.0                                                                                 | mA     |

| IOL(peak)  | LOW Peak<br>Output Current     | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |                                 |         | 10.0                                                                                 | mA     |

| IOL(avg)   | LOW Average<br>Output Current  | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,<br>P11_0 to P11_7, P12_0 to P12_7, P13_0 to P13_7, P14_0, P14_1 |                                 |         | 5.0                                                                                  | mA     |

Table 5.2

Recommended Operating Conditions (1) <sup>(1)</sup>

NOTES:

- 1. Referenced to Vcc1 = Vcc2 = 2.7 to 5.5V at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified.

- 2. The Average Output Current is the mean value within 100ms.

- 3. The total IOL(peak) for ports P0, P1, P2, P8\_6, P8\_7, P9, P10, P11, P14\_0, and P14\_1 must be 80mA max. The total IOL(peak) for ports P3, P4, P5, P6, P7, P8\_0 to P8\_4, P12, and P13 must be 80mA max. The total IOH(peak) for ports P0, P1, and P2 must be –40mA max. The total IOH(peak) for ports P3, P4, P5, P12, and P13 must be –40mA max. The total IOH(peak) for ports P6, P7, and P8\_0 to P8\_4 must be –40mA max. The total IOH(peak) for ports P3, P4, P5, P12, and P13 must be –40mA max. The total IOH(peak) for ports P6, P7, and P8\_0 to P8\_4 must be –40mA max. The total IOH(peak) for ports P8\_6, P8\_7, P9, P10, P14\_0, and P14\_1 must be –40mA max. Set Average Output Current to 1/2 of peak. The total IOH(peak) for ports P8\_6, P8\_7, P9, P10, P11, P14\_0, and P14\_1 must be –40mA max.

- As for 80-pin version, the total IOL(peak) for all ports and IOH(peak) must be 80mA. max. due to one Vcc and one Vss.

- 4. There is no external connections for port P1\_0 to P1\_7, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version.

| Symbol      | Parameter                                                                           | Measuring Condition |      | Standard    |      | Unit |

|-------------|-------------------------------------------------------------------------------------|---------------------|------|-------------|------|------|

| Symbol      | Falanielei                                                                          | weasuring condition | Min. | . Typ. Max. | Unit |      |

| Vdet4       | Low Voltage Detection Voltage (1)                                                   | Vcc1=0.8V to 5.5V   | 3.3  | 3.8         | 4.4  | V    |

| Vdet3       | Reset Level Detection Voltage (1, 2)                                                |                     | 2.2  | 2.8         | 3.6  | V    |

| Vdet4-Vdet3 | Electric potential difference of Low Voltage<br>Detection and Reset Level Detection |                     | 0.3  |             |      | V    |

| Vdet3s      | Low Voltage Reset Retention Voltage                                                 |                     |      |             | 0.8  | V    |

| Vdet3r      | Low Voltage Reset Release Voltage (3)                                               |                     | 2.2  | 2.9         | 4.0  | V    |

Table 5.9

Low Voltage Detection Circuit Electrical Characteristics

NOTES:

1. Vdet4 > Vdet3.

2. Where reset level detection voltage is less than 2.7 V, if the supply power voltage is greater than the reset level detection voltage, the microcomputer operates with  $f(BCLK) \le 10MHz$ .

3. Vdet3r > Vdet3 is not guaranteed.

4. The voltage detection circuit is designed to use when VCC1 is set to 5V.

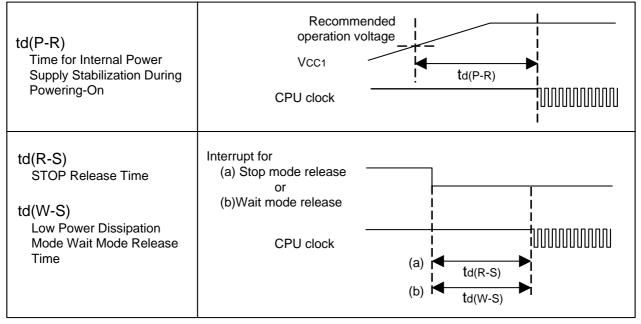

#### Table 5.10 Power Supply Circuit Timing Characteristics

| Symbol  | Parameter                                                          | Measuring Condition |      | Standard |      | Unit |

|---------|--------------------------------------------------------------------|---------------------|------|----------|------|------|

| Symbol  | Falanlelei                                                         | Measuring Condition | Min. | Тур.     | Max. | Unit |

| td(P-R) | Time for Internal Power Supply Stabilization<br>During Powering-On | Vcc1=2.7V to 5.5V   |      |          | 2    | ms   |

| td(R-S) | STOP Release Time                                                  |                     |      |          | 150  | μS   |

| td(W-S) | Low Power Dissipation Mode Wait Mode<br>Release Time               |                     |      |          | 150  | μS   |

| td(S-R) | Brown-out Detection Reset (Hardware Reset 2)<br>Release Wait Time  | VCC1=Vdet3r to 5.5V |      | 6 (1)    | 20   | ms   |

| td(E-A) | Low Voltage Detection Circuit Operation Start<br>Time              | Vcc1=2.7V to 5.5V   |      |          | 20   | μs   |

NOTES:

1. When Vcc1 = 5V.

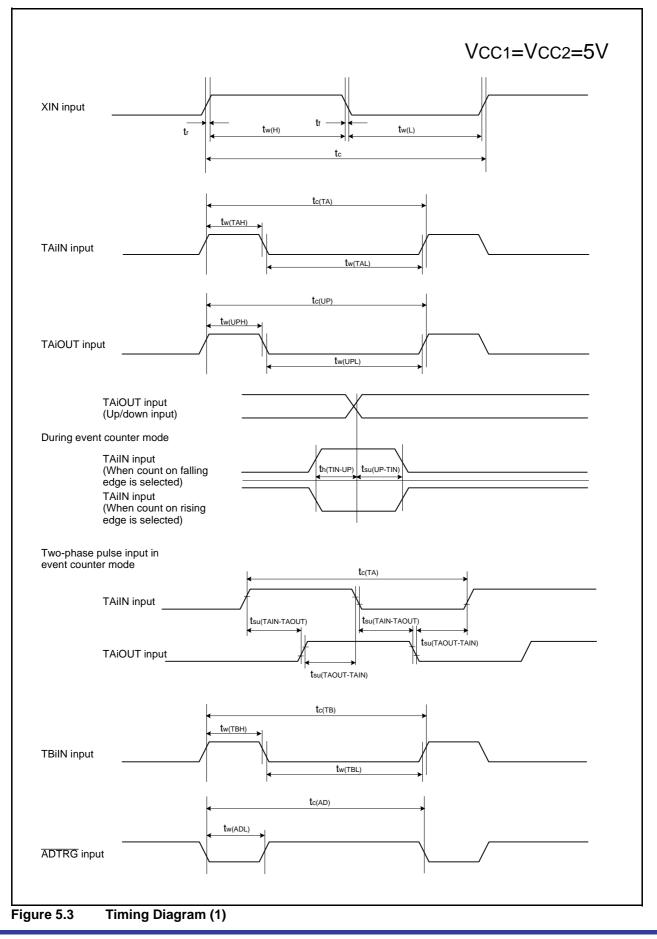

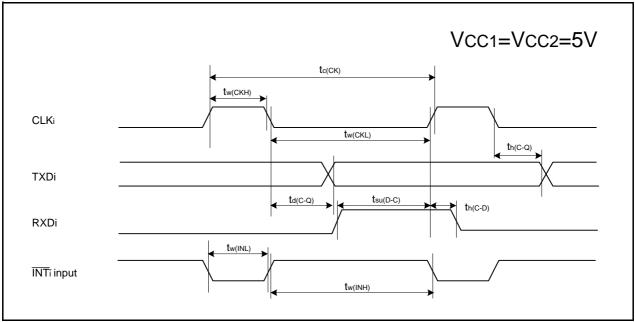

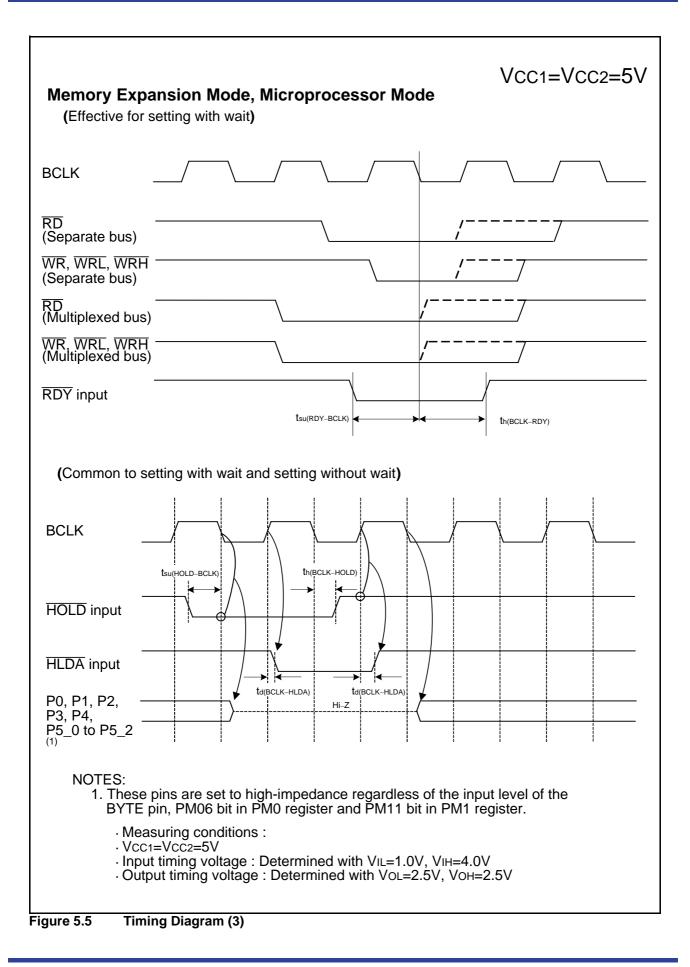

# VCC1=VCC2=5V

#### **Timing Requirements**

### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

#### Table 5.13 External Clock Input (XIN input) (1)

| Symbol | Parameter                             | Stan | Idard | Unit  |

|--------|---------------------------------------|------|-------|-------|

| Symbol | Falametei                             | Min. | Max.  | Offic |

| tc     | External Clock Input Cycle Time       | 62.5 |       | ns    |

| ťw(H)  | External Clock Input HIGH Pulse Width | 25   |       | ns    |

| tw(L)  | External Clock Input LOW Pulse Width  | 25   |       | ns    |

| tr     | External Clock Rise Time              |      | 15    | ns    |

| tf     | External Clock Fall Time              |      | 15    | ns    |

NOTES:

1. The condition is Vcc1=Vcc2=3.0 to 5.0V.

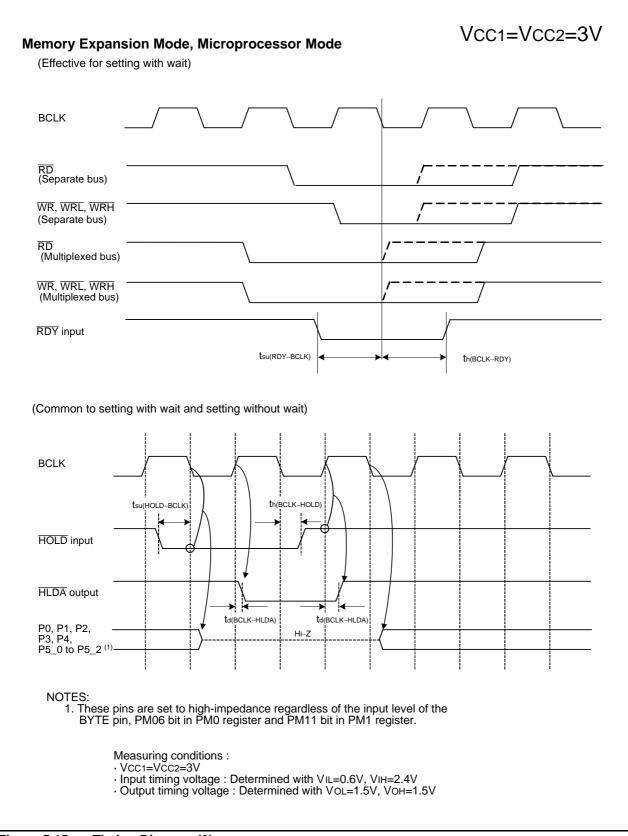

#### Table 5.14 Memory Expansion Mode and Microprocessor Mode

| Symbol         | Parameter                                                  | Standard |          | Standard |  | Unit |  |

|----------------|------------------------------------------------------------|----------|----------|----------|--|------|--|

| Symbol         | Falametei                                                  | Min.     | Max.     | Unit     |  |      |  |

| tac1(RD-DB)    | Data Input Access Time (for setting with no wait)          |          | (NOTE 1) | ns       |  |      |  |

| tac2(RD-DB)    | Data Input Access Time (for setting with wait)             |          | (NOTE 2) | ns       |  |      |  |

| tac3(RD-DB)    | Data Input Access Time (when accessing multiplex bus area) |          | (NOTE 3) | ns       |  |      |  |

| tsu(DB-RD)     | Data Input Setup Time                                      | 40       |          | ns       |  |      |  |

| tsu(RDY-BCLK)  | RDY Input Setup Time                                       | 30       |          | ns       |  |      |  |

| tsu(HOLD-BCLK) | HOLD Input Setup Time                                      | 40       |          | ns       |  |      |  |

| th(RD-DB)      | Data Input Hold Time                                       | 0        |          | ns       |  |      |  |

| th(BCLK-RDY)   | RDY Input Hold Time                                        | 0        |          | ns       |  |      |  |

| th(BCLK-HOLD)  | HOLD Input Hold Time                                       | 0        |          | ns       |  |      |  |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 45[ns]$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 45[ns]$$

n is "2" for 1-wait setting, "3" for 2-wait setting and "4" for 3-wait setting

3. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 45[ns]$$

n is "2" for 2-wait setting, "3" for 3-wait setting.

RENESAS

RENESAS

| Symbol | Paramet                                          | or                                   | Maaa                     | uring Condition                                                             | ;    | Standard | b    | Unit |

|--------|--------------------------------------------------|--------------------------------------|--------------------------|-----------------------------------------------------------------------------|------|----------|------|------|

| Symbol | Falamet                                          | ei                                   | Ivieas                   |                                                                             | Min. | Тур.     | Max. | Onit |

| Icc    | Power Supply Current<br>(Vcc1=Vcc2=2.7V to 3.6V) | In single-chip<br>mode, the output   | Mask ROM                 | f(BCLK)=10MHz<br>No division                                                |      | 8        | 11   | mA   |

|        | · · · · · · · · · · · · · · · · · · ·            | pins are open and other pins are Vss |                          | No division,<br>On-chip oscillation                                         |      | 1        | Max. | mA   |

|        |                                                  |                                      | Flash<br>Memory          | f(BCLK)=10MHz,<br>No division                                               |      | 8        | 13   | mA   |

|        |                                                  |                                      | ,                        | No division,<br>On-chip oscillation                                         |      | 1.8      |      | mA   |

|        |                                                  |                                      | Flash Memory<br>Program  | f(BCLK)=10MHz,<br>VCC1=3.0V                                                 |      | 12       |      | mA   |

|        |                                                  |                                      | Flash Memory<br>Erase    | f(BCLK)=10MHz,<br>VCC1=3.0V                                                 |      | 22       |      | mA   |

|        |                                                  |                                      | Mask ROM                 | f(XCIN)=32kHz<br>Low power dissipation<br>mode, ROM <sup>(3)</sup>          |      | 25       |      | μA   |

|        |                                                  |                                      | Flash Memory             | f(BCLK)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |      | 25       |      | μA   |

|        |                                                  |                                      |                          | f(BCLK)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |      | 420      |      | μA   |

|        |                                                  |                                      |                          | On-chip oscillation,<br>Wait mode                                           |      | 45       |      | μA   |

|        |                                                  |                                      | Mask ROM<br>Flash Memory | f(BCLK)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability High  |      | 6.0      |      | μΑ   |

|        |                                                  |                                      |                          | f(BCLK)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability Low   |      | 1.8      |      | μA   |

|        |                                                  |                                      |                          | Stop mode<br>Topr =25°C                                                     |      | 0.7      | 3.0  | μA   |

| Idet4  | Low Voltage Detection Diss                       | sipation Current (4)                 |                          |                                                                             |      | 0.6      | 4    | μΑ   |

| Idet3  | Reset Area Detection Dissi                       | pation Current (4)                   |                          |                                                                             |      | 0.4      | 2    | μΑ   |

Table 5.31 Electrical Characteristics (2) (1)

NOTES:

1. Referenced to Vcc1=Vcc2=2.7 to 3.3V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(BCLK)=10MHz unless otherwise specified.

2. With one timer operated using fC32.

3. This indicates the memory in which the program to be executed exists.

4. Idet is dissipation current when the following bit is set to "1" (detection circuit enabled).

Idet4: VC27 bit in the VCR2 register

Idet3: VC26 bit in the VCR2 register

# VCC1=VCC2=3V

#### **Switching Characteristics**

#### (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 5.46 | Memory Expansion and Microprocessor Modes (for setting with no wait) |

|------------|----------------------------------------------------------------------|

|            | · · · · · · · · · · · · · · · · · · ·                                |

| Currente e l  | Deveryeter                                         |                 | Stan     | dard | Linit |

|---------------|----------------------------------------------------|-----------------|----------|------|-------|

| Symbol        | Parameter                                          |                 | Min.     | Max. | Unit  |

| td(BCLK-AD)   | Address Output Delay Time                          |                 |          | 30   | ns    |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)     |                 | 4        |      | ns    |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)       |                 | 0        |      | ns    |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)       |                 | (NOTE 2) |      | ns    |

| td(BCLK-CS)   | Chip Select Output Delay Time                      |                 |          | 30   | ns    |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK) |                 | 4        |      | ns    |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                       |                 |          | 25   | ns    |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                        |                 | -4       |      | ns    |

| td(BCLK-RD)   | RD Signal Output Delay Time                        | See Figure 5.12 |          | 30   | ns    |

| th(BCLK-RD)   | RD Signal Output Hold Time                         | Figure 5.12     | 0        |      | ns    |

| td(BCLK-WR)   | WR Signal Output Delay Time                        |                 |          | 30   | ns    |

| th(BCLK-WR)   | WR Signal Output Hold Time                         |                 | 0        |      | ns    |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)       |                 |          | 40   | ns    |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) (3)    |                 | 4        |      | ns    |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)         |                 | (NOTE 1) |      | ns    |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) (3)      |                 | (NOTE 2) |      | ns    |

| td(BCLK-HLDA) | HLDA Output Delay Time                             |                 |          | 40   | ns    |

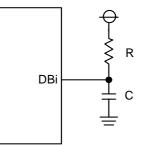

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 40[ns] \qquad \qquad f(BCLK) \text{ is } 12.5 \text{MHz or less.}$$

2. Calculated according to the BCLK frequency as follows:

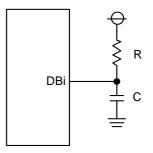

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in  $t = -CR X \ln (1 - VoL / Vcc2)$ by a circuit of the right figure. For example, when VoL = 0.2Vcc2, C = 30pF, R = 1k $\Omega$ , hold time of output "L" level is

t = -30pF X 1k  $\Omega$  X In(1-0.2Vcc2 / Vcc2)

= 6.7ns.

Figure 5.12 Ports P0 to P14 Measurement Circuit

# VCC1=VCC2=3V

#### Switching Characteristics

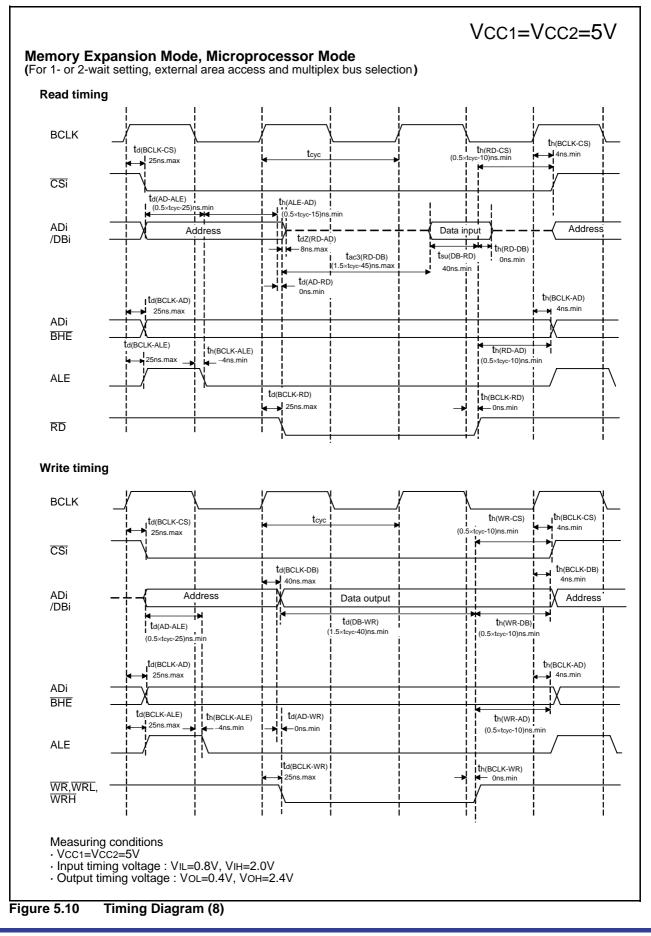

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 5.47 | Memory Expansion and Microprocessor Modes (for 1- to 3-wait setting and external |

|------------|----------------------------------------------------------------------------------|

|            | area access)                                                                     |

| Symbol        | Deremeter                                                | Stan               | dard     | Unit |    |

|---------------|----------------------------------------------------------|--------------------|----------|------|----|

| Symbol        | Parameter                                                | Min.               | Max.     | Unit |    |

| td(BCLK-AD)   | Address Output Delay Time                                |                    |          | 30   | ns |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)           |                    | 4        |      | ns |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)             |                    | 0        |      | ns |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)             |                    | (NOTE 2) |      | ns |

| td(BCLK-CS)   | Chip Select Output Delay Time                            |                    |          | 30   | ns |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)       |                    | 4        |      | ns |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                             |                    |          | 25   | ns |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                              |                    | -4       |      | ns |

| td(BCLK-RD)   | RD Signal Output Delay Time                              | See<br>Figure 5.12 |          | 30   | ns |

| th(BCLK-RD)   | RD Signal Output Hold Time                               |                    | 0        |      | ns |

| td(BCLK-WR)   | WR Signal Output Delay Time                              |                    |          | 30   | ns |

| th(BCLK-WR)   | WR Signal Output Hold Time                               |                    | 0        |      | ns |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)             |                    |          | 40   | ns |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) (3)          |                    | 4        |      | ns |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)               |                    | (NOTE 1) |      | ns |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) <sup>(3)</sup> |                    | (NOTE 2) |      | ns |

| td(BCLK-HLDA) | HLDA Output Delay Time                                   |                    |          | 40   | ns |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5)x10^9}{f(\text{BCLK})} - 40[\text{ns}]$

n is "1" for 1-wait setting, "2" for 2-wait setting and "3" for 3-wait setting. (BCLK) is 12.5MHz or less.

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \text{x10}^9}{f(\text{BCLK})} - 10[\text{ns}]$$

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in t = -CR X ln (1-VoL / VCc2) by a circuit of the right figure. For example, when VoL = 0.2Vcc2, C = 30pF, R = 1kΩ, hold time of output "L" level is

> $t = -30pF X 1k\Omega X ln(1-0.2Vcc2 / Vcc2)$ = 6.7ns.

Figure 5.15 Timing Diagram (3)

| Symbol  | Parameter                                                          | Measuring Condition |      | Unit |      |      |  |

|---------|--------------------------------------------------------------------|---------------------|------|------|------|------|--|

| Symbol  | Falanetei                                                          | measuring Condition | Min. | Тур. | Max. | Unit |  |

| td(P-R) | Time for Internal Power Supply Stabilization<br>During Powering-On | Vcc1=4.0V to 5.5V   |      |      | 2    | ms   |  |

| td(R-S) | STOP Release Time                                                  |                     |      |      | 150  | μS   |  |

| td(W-S) | Low Power Dissipation Mode Wait Mode<br>Release Time               |                     |      |      | 150  | μs   |  |

| Table 5.56 | Power Supply Circuit Timing Characteristics |  |

|------------|---------------------------------------------|--|

|------------|---------------------------------------------|--|

Figure 5.22 Power Supply Circuit Timing Diagram

# VCC1=VCC2=5V

| Symbol                                       | Parameter                                                                                                                |                                                                                                                                                  |                                      | Measuring Condition  | Standard |      |       | Unit |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|----------|------|-------|------|--|

| ,                                            |                                                                                                                          |                                                                                                                                                  | modeuring contaition                 | Min.                 | Тур.     | Max. | 01110 |      |  |

| Vон                                          | HIGH<br>Output<br>Voltage <sup>(2)</sup>                                                                                 | P6_0 to P6_7, P7_2 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P14                                                            | IOH=-5mA                             | Vcc1-2.0             |          | Vcc1 | v     |      |  |

|                                              | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P12_0 to P12_7, P13_0 to P13_7 |                                                                                                                                                  |                                      | IOH=-5mA             | Vcc2-2.0 |      | Vcc2  |      |  |

| VOH HIGH<br>Output<br>Voltage <sup>(2)</sup> |                                                                                                                          | P6_0 to P6_7, P7_2 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P14                                                            | P10_0 to P10_7,                      | ОН=-200μА            | Vcc1-0.3 |      | Vcc1  | N    |  |

|                                              |                                                                                                                          | P0_0 to P0_7, P1_0 to P1_7<br>P3_0 to P3_7, P4_0 to P4_7<br>P12_0 to P12_7, P13_0 to P                                                           | ', P5_0 to P5_7,                     | Юн=-200µА            | Vcc2-0.3 |      | Vcc2  |      |  |

| Vон                                          | HIGH Outpu                                                                                                               | t Voltage XOUT                                                                                                                                   | HIGHPOWER                            | IOH=-1mA             | Vcc1-2.0 |      | VCC1  | V    |  |

|                                              |                                                                                                                          |                                                                                                                                                  | LOWPOWER                             | IOH=-0.5mA           | Vcc1-2.0 |      | VCC1  | v    |  |

|                                              | HIGH Outpu                                                                                                               | t Voltage XCOUT                                                                                                                                  | HIGHPOWER                            | With no load applied |          | 2.5  |       |      |  |

|                                              |                                                                                                                          |                                                                                                                                                  | LOWPOWER                             | With no load applied |          | 1.6  |       | V    |  |

| Vol                                          | LOW<br>Output<br>Voltage <sup>(2)</sup>                                                                                  | P6_0 to P6_7, P7_0 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P14                                                            | P10 0 to P10 7,                      | IOL=5mA              |          |      | 2.0   | v    |  |

| . chage                                      |                                                                                                                          | P0_0 to P0_7, P1_0 to P1_7<br>P3_0 to P3_7, P4_0 to P4_7<br>P12_0 to P12_7, P13_0 to P                                                           | 7, P2_0 to P2_7,<br>7, P5_0 to P5_7, | IOL=5mA              |          |      | 2.0   |      |  |

| C                                            | LOW<br>Output<br>Voltage <sup>(2)</sup>                                                                                  | P6_0 to P6_7, P7_0 to P7_7<br>P8_6, P8_7, P9_0 to P9_7,<br>P11_0 to P11_7, P14_0, P14                                                            | P10_0 to P10_7,                      | IOL=200μA            |          |      | 0.45  | v    |  |

|                                              |                                                                                                                          | P0_0 to P0_7, P1_0 to P1_7<br>P3_0 to P3_7, P4_0 to P4_7<br>P12_0 to P12_7, P13_0 to P                                                           | 7, P5_0 to P5_7,                     | IOL=200μA            |          |      | 0.45  |      |  |

| Vol                                          | LOW Output                                                                                                               | Voltage XOUT                                                                                                                                     | HIGHPOWER                            | IOL=1mA              |          |      | 2.0   |      |  |

|                                              |                                                                                                                          |                                                                                                                                                  | LOWPOWER                             | IOL=0.5mA            |          |      | 2.0   | V    |  |

|                                              | LOW Output                                                                                                               | Voltage XCOUT                                                                                                                                    | HIGHPOWER                            | With no load applied |          | 0    |       |      |  |

|                                              |                                                                                                                          |                                                                                                                                                  | LOWPOWER                             | With no load applied |          | 0    |       | V    |  |

| Vt+-Vt-                                      | Hysteresis                                                                                                               | HOLD, RDY, TA0IN to TA4I<br>INT0 to INT5, NMI, ADTRG,<br>TA0OUT to TA4OUT, KI0 to<br>SCL0 to SCL2, SDA0 to SD                                    |                                      | 0.2                  |          | 1.0  | V     |      |  |

| Vt+-Vt-                                      | Hysteresis                                                                                                               |                                                                                                                                                  |                                      |                      | 0.2      |      | 2.5   | V    |  |

| Ін                                           | HIGH Input<br>Current <sup>(2)</sup>                                                                                     | P0_0 to P0_7, P1_0 to P1_7<br>P4_0 to P4_7, P5_0 to P5_7<br>P8_0 to P8_7, P9_0 to P9_<br>P11_0 to P11_7, P12_0 to P<br>P14_0, P14_1, XIN, RESET  | VI=5V                                |                      |          | 5.0  | μΑ    |      |  |

| lıL                                          | LOW Input<br>Current <sup>(2)</sup>                                                                                      | P0_0 to P0_7, P1_0 to P1_7<br>P4_0 to P4_7, P5_0 to P5_7<br>P8_0 to P8_7, P9_0 to P9_7<br>P11_0 to P11_7, P12_0 to P<br>P14_0, P14_1, XIN, RESET | VI=0V                                |                      |          | -5.0 | μA    |      |  |

| Rpullup                                      | Pull-Up<br>Resistance<br>(2)                                                                                             | P0_0 to P0_7, P1_0 to P1_7<br>P4_0 to P4_7, P5_0 to P5_7<br>P8_0 to P8_4, P8_6, P8_7, I<br>P11_0 to P11_7, P12_0 to P<br>P14_0, P14_1            | VI=0V                                | 30                   | 50       | 170  | kΩ    |      |  |

| Rfxin                                        | Feedback R                                                                                                               | esistance XIN                                                                                                                                    |                                      |                      |          | 1.5  |       | MΩ   |  |

| Rfxcin                                       | Feedback Resistance XCIN                                                                                                 |                                                                                                                                                  |                                      |                      |          | 15   |       | MΩ   |  |

| Vram                                         | RAM Retent                                                                                                               | ion Voltage                                                                                                                                      | At stop mode                         | 2.0                  |          |      | V     |      |  |

#### Table 5.57 Electrical Characteristics (1) (1)

NOTES:

1. Referenced to Vcc1=Vcc2=4.0 to 5.5V, Vss = 0V at Topr = -40 to 85°C / -40 to 125°C, f(BCLK)=24MHz unless otherwise specified. T version = -40 to 85°C, V version =-40 to 125°C.

2. There is no external connections for port P1\_0 to P1\_7, P4\_4 to P4\_7, P7\_2 to P7\_5 and P9\_1 in 80-pin version.

| REVISION HISTORY         M16C/62P Group (M16C/62P, M16C/62PT) Hardware M |              |           |                                                  |                                                                        |  |  |

|--------------------------------------------------------------------------|--------------|-----------|--------------------------------------------------|------------------------------------------------------------------------|--|--|

| Rev. Date                                                                |              |           | Description                                      |                                                                        |  |  |

| TXCV.                                                                    | Date         | Page      |                                                  | Summary                                                                |  |  |

|                                                                          |              | 33        | Table 5.4 A                                      | -D Conversion Characteristics is revised.                              |  |  |

|                                                                          |              |           | Table 5.5 D                                      | -A Conversion Characteristics revised.                                 |  |  |

|                                                                          |              | 34,74     | Table 5.6 to                                     | 5.7 and table 5.54 to 5.55 are revised.                                |  |  |

|                                                                          |              | 36        | Table 5.11                                       | is revised.                                                            |  |  |

|                                                                          |              | 38,55     | Table 5.14                                       | and 5.33 HLDA output deley time is deleted.                            |  |  |

|                                                                          |              | 41        | Figure 5.1 i                                     | s partly revised.                                                      |  |  |

|                                                                          |              | 41-43,    | Table 5.27                                       | to 5.29 and table 5.46 to 48 HLDA output deley time is added.          |  |  |

|                                                                          |              | 58-60     |                                                  |                                                                        |  |  |

|                                                                          |              | 44        | Figure 5.2                                       | Timing Diagram (1) XIN input is added.                                 |  |  |

|                                                                          |              | 47-48     | Figure 5.5 t                                     | to 5.6 Read timing $DB \rightarrow DBi$                                |  |  |

|                                                                          |              | 49-50     | Figure 5.7 t                                     | to 5.8 Write timing $DB \rightarrow DBi$                               |  |  |

|                                                                          |              | 52        | Figure 5.10                                      |                                                                        |  |  |

|                                                                          |              | 53        | Table 5.30                                       |                                                                        |  |  |

|                                                                          |              | 58        | -                                                | is partly revised.                                                     |  |  |

|                                                                          |              | 61        | -                                                | Timing Diagram (1) XIN input is added.                                 |  |  |

|                                                                          |              | 64-65     | 0                                                | to 5.16 Read timing $DB \rightarrow DBi$                               |  |  |

|                                                                          |              | 66-67     | -                                                | to 5.18 Write timing $DB \rightarrow DBi$                              |  |  |

|                                                                          |              | 69        | Figure 5.20                                      |                                                                        |  |  |

|                                                                          |              | 70-85     |                                                  | haracteristics (M16C/62PT) is added.                                   |  |  |

| 2.10                                                                     | Nov 07, 2003 | 8-9<br>23 | Table 1.5 to<br>Table 3.1 is                     | o 1.7 Product List is partly revised. Note 1 is deleted.<br>s revised. |  |  |

|                                                                          |              | 71        | Table 5.50                                       |                                                                        |  |  |

|                                                                          |              | 72        | Table 5.51                                       |                                                                        |  |  |

| 2.11                                                                     | Jan 06, 2004 | 16        |                                                  | $VCC1  VCC2 \rightarrow VCC1 > VCC2$                                   |  |  |

|                                                                          |              | 17-18     |                                                  | to 1.11 NOTE 1 VCC1 VCC2 $\rightarrow$ VCC1 > VCC2                     |  |  |

|                                                                          |              | 31        |                                                  | Power Supply Ripple Allowable Frequency Unit MHz $\rightarrow$ kHz     |  |  |

|                                                                          |              | 12        |                                                  | nd Figure 1.5 are added.                                               |  |  |

| 2.30                                                                     | Sep 01, 2004 | 18, 20    |                                                  | to 1.13 are revised.                                                   |  |  |

|                                                                          |              | 19,21     |                                                  | to 1.14 are revised.                                                   |  |  |

|                                                                          |              | 24        | -                                                | s partly revised.                                                      |  |  |

|                                                                          |              | 05        | Note 3 is ad                                     |                                                                        |  |  |

|                                                                          |              | 25        | Note 6 is ad                                     |                                                                        |  |  |

|                                                                          |              | 33        | Table 5.3 is                                     |                                                                        |  |  |

|                                                                          |              | 34        |                                                  | able 5.4 is added.                                                     |  |  |

|                                                                          |              | 34<br>35  |                                                  | 5.6 is partly revised.                                                 |  |  |

|                                                                          |              | - 30      | 5 Table 5.8 is revised.<br>Table 5.9 is revised. |                                                                        |  |  |

|                                                                          |              | 37        | 37 Table 5.11 is revised.                        |                                                                        |  |  |

|                                                                          |              | 57        |                                                  |                                                                        |  |  |