#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                           |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 10MHz                                                                         |

| Connectivity               | Host Interface (LPC), I <sup>2</sup> C, IrDA, SCI, X-Bus                      |

| Peripherals                | PWM, WDT                                                                      |

| Number of I/O              | 114                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 144-TQFP                                                                      |

| Supplier Device Package    | 144-TQFP (16x16)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2161bvt10v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 24.5 | External Clock Input Timing                              | 636 |

|-------------|----------------------------------------------------------|-----|

| Figure 24.6 | Timing of External Clock Output Stabilization Delay Time | 637 |

| Figure 24.7 | Subclock Input Timing                                    | 638 |

| Figure 24.8 | Processing for X1 and X2 Pins                            | 640 |

| Figure 24.9 | Note on Board Design of Oscillator Circuit Section       | 640 |

### Section 25 Power-Down Modes

| Figure 25.1 | Mode Transition Diagram                      | 647 |

|-------------|----------------------------------------------|-----|

| Figure 25.2 | Medium-Speed Mode Timing                     | 650 |

| Figure 25.3 | Application Example in Software Standby Mode | 652 |

| Figure 25.4 | Hardware Standby Mode Timing                 | 653 |

### Section 27 Electrical Characteristics

| Figure 27.1  | Darlington Pair Drive Circuit (Example)                    | 708 |

|--------------|------------------------------------------------------------|-----|

| Figure 27.2  | LED Drive Circuit (Example)                                | 709 |

| Figure 27.3  | Output Load Circuit                                        | 710 |

| Figure 27.4  | Connection of VCL Capacitor                                | 724 |

| Figure 27.5  | Connection of VCL Capacitor                                | 761 |

| Figure 27.6  | System Clock Timing                                        | 762 |

| Figure 27.7  | Oscillation Settling Timing                                | 762 |

| Figure 27.8  | Oscillation Setting Timing (Exiting Software Standby Mode) | 763 |

| Figure 27.9  | Reset Input Timing                                         | 764 |

| Figure 27.10 | Interrupt Input Timing                                     | 764 |

| Figure 27.11 | Basic Bus Timing (Two-State Access)                        | 765 |

| Figure 27.12 | Basic Bus Timing (Three-State Access)                      | 766 |

| Figure 27.13 | Basic Bus Timing (Three-State Access with One Wait State)  | 767 |

| Figure 27.14 | Burst ROM Access Timing (Two-State Access)                 | 768 |

| Figure 27.15 | Burst ROM Access Timing (One-State Access)                 | 769 |

| Figure 27.16 | I/O Port Input/Output Timing                               | 770 |

| Figure 27.17 | FRT Input/Output Timing                                    | 770 |

| Figure 27.18 | FRT Clock Input Timing                                     | 771 |

| Figure 27.19 | 8-Bit Timer Output Timing                                  | 771 |

| Figure 27.20 | 8-Bit Timer Clock Input Timing                             | 771 |

| Figure 27.21 | 8-Bit Timer Reset Input Timing                             | 771 |

| Figure 27.22 | PWM, PWMX Output Timing                                    | 772 |

| Figure 27.23 | SCK Clock Input Timing                                     | 772 |

| Figure 27.24 | SCI Input/Output Timing (Synchronous Mode)                 | 772 |

| Figure 27.25 | A/D Converter External Trigger Input Timing                | 772 |

| Figure 27.26 | WDT Output Timing (RESO)                                   | 773 |

| Figure 27.27 | Host Interface (XBS) Timing                                | 773 |

| Figure 27.28 | Keyboard Buffer Controller Timing                          | 774 |

Rev. 3.00 Mar 21, 2006 page xlvi of liv

# Tables

| Section 1  | Overview                                                        |    |

|------------|-----------------------------------------------------------------|----|

| Table 1.1  | Pin Functions of H8S/2140B, H8S/2141B, H8S/2145B, and H8S/2148B |    |

|            | in Each Operating Mode                                          | 7  |

| Table 1.2  | Pin Functions of H8S/2160B and H8S/2161B in Each Operating Mode | 12 |

| Table 1.3  | Pin Functions                                                   | 18 |

|            |                                                                 |    |

| Section 2  | CPU                                                             |    |

| Table 2.1  | Instruction Classification                                      | 40 |

| Table 2.2  | Operation Notation                                              | 41 |

| Table 2.3  | Data Transfer Instructions                                      | 42 |

| Table 2.4  | Arithmetic Operations Instructions (1)                          | 43 |

| Table 2.4  | Arithmetic Operations Instructions (2)                          | 44 |

| Table 2.5  | Logic Operations Instructions                                   | 45 |

| Table 2.6  | Shift Instructions                                              | 45 |

| Table 2.7  | Bit Manipulation Instructions (1)                               | 46 |

| Table 2.7  | Bit Manipulation Instructions (2)                               | 47 |

| Table 2.8  | Branch Instructions                                             | 48 |

| Table 2.9  | System Control Instructions                                     | 49 |

| Table 2.10 | Block Data Transfer Instructions                                | 50 |

| Table 2.11 | Addressing Modes                                                | 52 |

| Table 2.12 | Absolute Address Access Ranges                                  | 53 |

| Table 2.13 | Effective Address Calculation (1)                               | 55 |

| Table 2.13 | Effective Address Calculation (2)                               | 56 |

| Section 3  | MCU Operating Modes                                             |    |

| Table 3.1  | MCU Operating Mode Selection                                    | 63 |

| Table 3.2  | Pin Functions in Each Mode                                      | 70 |

|            |                                                                 |    |

| Section 4  | Exception Handling                                              |    |

| Table 4.1  | Exception Types and Priority                                    | 81 |

| Table 4.2  | Exception Handling Vector Table                                 | 82 |

| Table 4.3  | Status of CCR after Trap Instruction Exception Handling         | 85 |

| Section 5  | Interrupt Controller                                            |    |

| Table 5.1  | Pin Configuration                                               | 91 |

| Table 5.2  | Correspondence between Interrupt Source and ICR                 | 92 |

| Table 5.3  | Interrupt Sources, Vector Addresses, and Interrupt Priorities   | -  |

| Table 5.4  | Interrupt Control Modes                                         |    |

|            | ·····                                                           |    |

Rev. 3.00 Mar 21, 2006 page xlviii of liv

### **1.3.2** Pin Functions in Each Operating Mode

Table 1.1Pin Functions of H8S/2140B, H8S/2141B, H8S/2145B, and H8S/2148B in Each<br/>Operating Mode

|                     | Pin Name                  |                               |                              |                    |  |  |  |  |

|---------------------|---------------------------|-------------------------------|------------------------------|--------------------|--|--|--|--|

| Pin No.             | Extend                    | ed Modes                      | Single-Chip Modes            | Flash Memory       |  |  |  |  |

| FP-100B<br>TFP-100B | Mode 1                    | Mode 2, Mode 3<br>(EXPE = 1)  | Mode 2, Mode 3<br>(EXPE = 0) | Programmer<br>Mode |  |  |  |  |

| 1                   | RES                       | RES                           | RES                          | RES                |  |  |  |  |

| 2                   | XTAL                      | XTAL                          | XTAL                         | XTAL               |  |  |  |  |

| 3                   | EXTAL                     | EXTAL                         | EXTAL                        | EXTAL              |  |  |  |  |

| 4                   | VCCB                      | VCCB                          | VCCB                         | VCC                |  |  |  |  |

| 5                   | MD1                       | MD1                           | MD1                          | VSS                |  |  |  |  |

| 6                   | MD0                       | MD0                           | MD0                          | VSS                |  |  |  |  |

| 7                   | NMI                       | NMI                           | NMI                          | FA9                |  |  |  |  |

| 8                   | STBY                      | STBY                          | STBY                         | VCC                |  |  |  |  |

| 9                   | VCL                       | VCL                           | VCL                          | VCC                |  |  |  |  |

| 10 (B)              | PA7/CIN15/KIN15/<br>PS2CD | PA7/A23/CIN15/<br>KIN15/PS2CD | PA7/CIN15/KIN15/<br>PS2CD    | NC                 |  |  |  |  |

| 11 (B)              | PA6/CIN14/KIN14/<br>PS2CC | PA6/A22/CIN14/<br>KIN14/PS2CC | PA6/CIN14/KIN14/<br>PS2CC    | NC                 |  |  |  |  |

| 12 (N)              | P52/SCK0/SCL0             | P52/SCK0/SCL0                 | P52/SCK0/SCL0                | NC                 |  |  |  |  |

| 13                  | P51/RxD0                  | P51/RxD0                      | P51/RxD0                     | FA17               |  |  |  |  |

| 14                  | P50/TxD0                  | P50/TxD0                      | P50/TxD0                     | NC                 |  |  |  |  |

| 15                  | VSS                       | VSS                           | VSS                          | VSS                |  |  |  |  |

| 16 (N)              | P97/WAIT/SDA0             | P97/WAIT/SDA0                 | P97/SDA0                     | VCC                |  |  |  |  |

| 17                  | P96/ø/EXCL                | P96/ø/EXCL                    | P96/ø/EXCL                   | NC                 |  |  |  |  |

| 18                  | AS/IOS                    | AS/IOS                        | P95/CS1                      | FA16               |  |  |  |  |

| 19                  | HWR                       | HWR                           | P94/IOW                      | FA15               |  |  |  |  |

| 20 (B)              | PA5/CIN13/KIN13/<br>PS2BD | PA5/A21/CIN13/<br>KIN13/PS2BD | PA5/CIN13/KIN13/<br>PS2BD    | NC                 |  |  |  |  |

| 21 (B)              | PA4/CIN12/KIN12/<br>PS2BC | PA4/A20/CIN12/<br>KIN12/PS2BC | PA4/CIN12/KIN12/<br>PS2BC    | NC                 |  |  |  |  |

# Section 3 MCU Operating Modes

# 3.1 MCU Operating Mode Selection

This LSI has three operating modes (modes 1 to 3). The operating mode is determined by the setting of the mode pins (MD1 and MD0). Table 3.1 shows the MCU operating mode selection.

Table 3.1 lists the MCU operating modes.

| MCU<br>Operating<br>Mode | MD1 | MD0 | CPU<br>Operating<br>Mode | Description                                             | On-Chip<br>ROM |

|--------------------------|-----|-----|--------------------------|---------------------------------------------------------|----------------|

| 0                        | 0   | 0   | _                        | _                                                       | _              |

| 1                        | _   | 1   | Normal                   | Expanded mode with on-chip ROM disabled                 | Disabled       |

| 2                        | 1   | 0   | Advanced                 | Expanded mode with on-chip ROM enabled Single-chip mode | Enabled        |

| 3                        |     | 1   | Normal                   | Expanded mode with on-chip ROM enabled Single-chip mode |                |

Table 3.1

MCU Operating Mode Selection

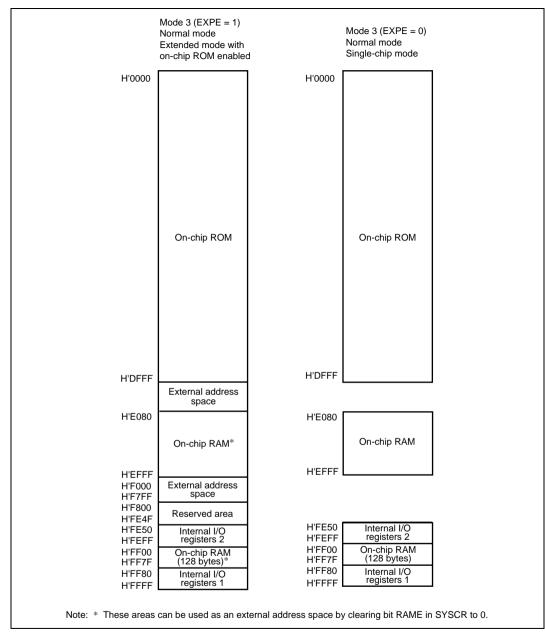

Mode 1 is an expanded mode that allows access to external memory and peripheral devices. With modes 2 and 3, operation begins in single-chip mode after reset release, but a transition can be made to external expansion mode by setting the EXPE bit in MDCR to 1.

Mode 0 cannot be used in this LSI. Thus, mode pins should be set to enable mode 1, 2 or 3 in normal program execution state. Mode pins should not be changed during operation.

# **3.2 Register Descriptions**

The following registers are related to the operating mode. For details on the bus control register (BCR), refer to section 6.3.1, Bus Control Register (BCR).

- Mode control register (MDCR)

- System control register (SYSCR)

- Serial timer control register (STCR)

Figure 3.10 Address Map for H8S/2148B (2)

Section 8 I/O Ports

### 8.4 Port 3

Port 3 is an 8-bit I/O port. Port 3 pins also function as a bidirectional data bus, XBS bidirectional data bus, and LPC input/output pins. Port 3 functions change according to the operating mode. Port 3 has the following registers.

- Port 3 data direction register (P3DDR)

- Port 3 data register (P3DR)

- Port 3 pull-up MOS control register (P3PCR)

### 8.4.1 Port 3 Data Direction Register (P3DDR)

P3DDR specifies input or output for the pins of port 3 on a bit-by-bit basis.

| Bit | Bit Name | Initial Value | R/W | Description                                                                             |

|-----|----------|---------------|-----|-----------------------------------------------------------------------------------------|

| 7   | P37DDR   | 0             | W   | Modes 1, 2, and 3 (EXPE = 1)                                                            |

| 6   | P36DDR   | 0             | W   | The input/output direction specified by P3DDR is                                        |

| 5   | P35DDR   | 0             | W   | <ul> <li>ignored, and pins automatically function as data</li> <li>I/O pins.</li> </ul> |

| 4   | P34DDR   | 0             | W   | Modes 2 and 3 (EXPE = 0)                                                                |

| 3   | P33DDR   | 0             | W   | The corresponding port 3 pins are output ports                                          |

| 2   | P32DDR   | 0             | W   | when P3DDR bits are set to 1, and input ports                                           |

| 1   | P31DDR   | 0             | W   | when cleared to 0.                                                                      |

| 0   | P30DDR   | 0             | W   |                                                                                         |

### P80/HA0/PME<sup>\*3</sup>

The pin function is switched as shown below according to the combination of the HI12E bit in SYSCR2, the PMEE bit in HICR0, and the P80DDR bit.

| PMEE         | 0 1                           |                |                             |                |  |  |  |

|--------------|-------------------------------|----------------|-----------------------------|----------------|--|--|--|

| HI12E        | (                             | )              | 1                           | 0*1            |  |  |  |

| P80DDR       | 0                             | 1              | —                           | 0*1            |  |  |  |

| Pin Function | P80 input pin                 | P80 output pin | HA0 input pin <sup>*2</sup> | PME output pin |  |  |  |

|              | PME input pin <sup>*2*3</sup> |                |                             |                |  |  |  |

Notes: 1. When bit PMEE is set to 1 in HICR0, bits HI12E and P80DDR should be cleared to 0.

- 2. The HA0 input pin can only be used in mode 2 or 3 (EXPE = 0).

- 3. Not supported by the H8S/2148B and H8S/2145B (5-V version).

### 8.10 Port 9

Port 9 is an 8-bit I/O port. Port 9 pins also function as external interrupt input pins, the A/D converter input pin, host interface (XBS) input pins, the IIC\_0 I/O pin, the subclock input pin, bus control signal I/O pins, and the system clock ( $\phi$ ) output pin. P97 is an NMOS push-pull output. SDA0 is an NMOS open-drain output, and has direct bus drive capability. Port 9 has the following registers.

- Port 9 data direction register (P9DDR)

- Port 9 data register (P9DR)

#### 8.10.2 Port 9 Data Register (P9DR)

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                |

|-----|----------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------|

| 7   | P97DR    | 0             | R/W | With the exception of P96, if a port 9 read is                                                                             |

| 6   | P96DR    | Undefined*    | R   | <ul> <li>performed while P9DDR bits are set to 1, the</li> <li>P9DR values are read directly, regardless of the</li> </ul> |

| 5   | P95DR    | 0             | R/W | actual pin states. If a port 9 read is performed                                                                           |

| 4   | P94DR    | 0             | R/W | while P9DDR bits are cleared to 0, the pin states                                                                          |

| 3   | P93DR    | 0             | R/W | — are read.<br>— For P96, the pin state is always read.                                                                    |

| 2   | P92DR    | 0             | R/W | - For F90, the pin state is always read.                                                                                   |

| 1   | P91DR    | 0             | R/W | —                                                                                                                          |

| 0   | P90DR    | 0             | R/W | —                                                                                                                          |

P9DR stores output data for the port 9 pins.

Note: \* The initial value of bit 6 is determined according to the P96 pin state.

#### 8.10.3 **Pin Functions**

#### • P97/WAIT/SDA0

The pin function is switched as shown below according to the combination of operating mode, the WMS1 bit in WSCR, the ICE bit in ICCR of IIC\_0, and the P97DDR bit.

| Operating<br>Mode | Ν                | /lodes 1, 2, 3    | 3 (EXPE = 1     | Mode                 | s 2, 3 (EXPI     | E = 0)            |                 |

|-------------------|------------------|-------------------|-----------------|----------------------|------------------|-------------------|-----------------|

| WMS1              | 0                |                   |                 | 1                    |                  | _                 |                 |

| ICE               | 0                |                   | 1               | _                    | 0 1              |                   | 1               |

| P97DDR            | 0                | 1                 | _               | _                    | 0                | 1                 | —               |

| Pin Function      | P97 input<br>pin | P97<br>output pin | SDA0 I/O<br>pin | WAIT<br>input<br>pin | P97 input<br>pin | P97<br>output pin | SDA0 I/O<br>pin |

Note: When this pin is set as the P97 output pin, it is an NMOS push-pull output. SDA0 is an NMOS open-drain output, and has direct bus drive capability.

### 11.7 Usage Notes

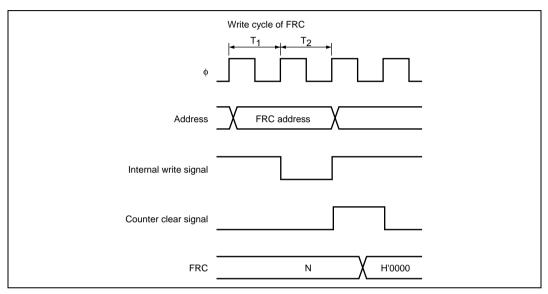

### 11.7.1 Conflict between FRC Write and Clear

If an internal counter clear signal is generated during the state after an FRC write cycle, the clear signal takes priority and the write is not performed. Figure 11.17 shows the timing for this type of conflict.

Figure 11.17 FRC Write-Clear Conflict

### 15.3.10 Keyboard Comparator Control Register (KBCOMP)

KBCOMP selects the functions of the SCI and A/D converter.

| Bit         | Bit Name                | Initial Value | R/W               | Description                                                                                                                      |

|-------------|-------------------------|---------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 7           | IrE                     | 0             | R/W               | IrDA Enable                                                                                                                      |

|             |                         |               |                   | Specifies SCI_2 I/O pins for either normal SCI or IrDA.                                                                          |

|             |                         |               |                   | 0: TxD2/IrTxD and RxD2/IrRxD pins function as TxD2<br>and RxD2 pins, respectively                                                |

|             |                         |               |                   | 1: TxD2/IrTxD and RxD2/IrRxD pins function as IrTxD<br>and IrRxD pins, respectively                                              |

| 6           | IrCKS2                  | 0             | R/W               | IrDA Clock Select 2 to 0                                                                                                         |

| 5<br>4      | IrCKS1<br>IrCKS0        | 0<br>0        | R/W<br>R/W        | These bits specify the high-level width of the clock pulse during IrTxD output pulse encoding when the IrDA function is enabled. |

|             |                         |               |                   | 000: B × 3/16 (B: Bit rate)                                                                                                      |

|             |                         |               |                   | 001: φ/2                                                                                                                         |

|             |                         |               |                   | 010: φ/4                                                                                                                         |

|             |                         |               |                   | 011: φ/8                                                                                                                         |

|             |                         |               |                   | 100:                                                                                                                             |

|             |                         |               |                   | 101:                                                                                                                             |

|             |                         |               |                   | 110: ф/64                                                                                                                        |

|             |                         |               |                   | 111: φ/128                                                                                                                       |

| 3           | KBADE                   | 0             | R/W               | Bits related to the A/D converter                                                                                                |

| 2<br>1<br>0 | KBCH2<br>KBCH1<br>KBCH0 | 0<br>0<br>0   | R/W<br>R/W<br>R/W | For details, refer to section 21.3.4, Keyboard Comparator Control Register (KBCOMP).                                             |

| Bit | Bit Name | Initial Value | R/W    | Description                                                                                                                                                                                                               |  |  |  |  |

|-----|----------|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3   | AL       | 0             | R/(W)* | Arbitration Lost Flag                                                                                                                                                                                                     |  |  |  |  |

|     |          |               |        | Indicates that arbitration was lost in master mode.                                                                                                                                                                       |  |  |  |  |

|     |          |               |        | [Setting conditions]                                                                                                                                                                                                      |  |  |  |  |

|     |          |               |        | When ALSL = 0                                                                                                                                                                                                             |  |  |  |  |

|     |          |               |        | • If the internal SDA and SDA pin disagree at the rise of SCL in master transmit mode                                                                                                                                     |  |  |  |  |

|     |          |               |        | <ul> <li>If the internal SCL line is high at the fall of SCL in<br/>master transmit mode</li> </ul>                                                                                                                       |  |  |  |  |

|     |          |               |        | When ALSL = 1                                                                                                                                                                                                             |  |  |  |  |

|     |          |               |        | • If the internal SDA and SDA pin disagree at the rise of SCL in master transmit mode                                                                                                                                     |  |  |  |  |

|     |          |               |        | <ul> <li>If the SDA pin is driven low by another device before<br/>the I<sup>2</sup>C bus interface drives the SDA pin low, after the<br/>start condition instruction was executed in master<br/>transmit mode</li> </ul> |  |  |  |  |

|     |          |               |        | [Clearing conditions]                                                                                                                                                                                                     |  |  |  |  |

|     |          |               |        | • When ICDR is written to (transmit mode) or read from (receive mode)                                                                                                                                                     |  |  |  |  |

|     |          |               |        | • When 0 is written in AL after reading AL = 1                                                                                                                                                                            |  |  |  |  |

| 2   | AAS      | 0             | R/(W)* | Slave Address Recognition Flag                                                                                                                                                                                            |  |  |  |  |

|     |          |               |        | In $I^2C$ bus format slave receive mode, this flag is set to 1 if<br>the first frame following a start condition matches bits SVA6<br>to SVA0 in SAR, or if the general call address (H'00) is<br>detected.               |  |  |  |  |

|     |          |               |        | [Setting condition]                                                                                                                                                                                                       |  |  |  |  |

|     |          |               |        | When the slave address or general call address (one frame including a $R/\overline{W}$ bit is H'00) is detected in slave receive mode and FS = 0 in SAR                                                                   |  |  |  |  |

|     |          |               |        | [Clearing conditions]                                                                                                                                                                                                     |  |  |  |  |

|     |          |               |        | • When ICDR is written to (transmit mode) or read from (receive mode)                                                                                                                                                     |  |  |  |  |

|     |          |               |        | • When 0 is written in AAS after reading AAS = 1                                                                                                                                                                          |  |  |  |  |

|     |          |               |        | In master mode                                                                                                                                                                                                            |  |  |  |  |

|                    |                                          |                 | Time Indication (at Maximum Transfer Rate) [ns]         |                                                      |                   |                    |                    |                    |                    |  |  |

|--------------------|------------------------------------------|-----------------|---------------------------------------------------------|------------------------------------------------------|-------------------|--------------------|--------------------|--------------------|--------------------|--|--|

| Item               | t <sub>cyc</sub><br>Indication           |                 | t <sub>s</sub> ,∕t <sub>sr</sub><br>Influence<br>(Max.) | I <sup>2</sup> C Bus<br>Specifi-<br>cation<br>(Min.) | φ =<br>5 MHz      | ф =<br>8 MHz       | φ =<br>10 MHz      | φ =<br>16 MHz      | φ =<br>20 MHz      |  |  |

| t <sub>sclho</sub> | 0.5 $t_{_{SCLO}}$ ( $t_{_{Sr}}$ )        | Standard mode   | -1000                                                   | 4000                                                 | 4000              | 4000               | 4000               | 4000               | 4000               |  |  |

|                    |                                          | High-speed mode | -300                                                    | 600                                                  | 950               | 950                | 950                | 950                | 950                |  |  |

| t <sub>SCLLO</sub> | 0.5 $t_{sclo}$ (- $t_{sf}$ )             | Standard mode   | -250                                                    | 4700                                                 | 4750              | 4750               | 4750               | 4750               | 4750               |  |  |

|                    |                                          | High-speed mode | -250                                                    | 1300                                                 | 1000*1            | 1000*1             | 1000*1             | 1000*1             | 1000*1             |  |  |

| t <sub>BUFO</sub>  | 0.5 $t_{_{SCLO}}$ -1 $t_{_{cyc}}$        | Standard mode   | -1000                                                   | 4700                                                 | 3800*1            | 3875 <sup>*1</sup> | 3900 <sup>*1</sup> | 3938 <sup>*1</sup> | 3950 <sup>*1</sup> |  |  |

|                    | (t <sub>sr</sub> )                       | High-speed mode | -300                                                    | 1300                                                 | 750 <sup>*1</sup> | 825 <sup>*1</sup>  | 850 <sup>*1</sup>  | 888 <sup>*1</sup>  | 900*1              |  |  |

| t <sub>staho</sub> | $0.5 t_{sclo} - 1 t_{cyc}$               | Standard mode   | -250                                                    | 4000                                                 | 4550              | 4625               | 4650               | 4688               | 4700               |  |  |

|                    | (-t <sub>sr</sub> )                      | High-speed mode | -250                                                    | 600                                                  | 800               | 875                | 900                | 938                | 950                |  |  |

| t <sub>staso</sub> | $1 t_{sclo} (-t_{sr})$                   | Standard mode   | -1000                                                   | 4700                                                 | 9000              | 9000               | 9000               | 9000               | 9000               |  |  |

|                    |                                          | High-speed mode | -300                                                    | 600                                                  | 2200              | 2200               | 2200               | 2200               | 2200               |  |  |

| t <sub>stoso</sub> | $0.5 t_{_{\rm SCLO}} + 2 t_{_{\rm cyc}}$ | Standard mode   | -1000                                                   | 4000                                                 | 4400              | 4250               | 4200               | 4125               | 4100               |  |  |

|                    | $(-t_{Sr})$                              | High-speed mode | -300                                                    | 600                                                  | 1350              | 1200               | 1150               | 1075               | 1050               |  |  |

| t <sub>sdaso</sub> | $1 t_{scllo}^{*3}$ –3 $t_{cyc}$          | Standard mode   | -1000                                                   | 250                                                  | 3100              | 3325               | 3400               | 3513               | 3550               |  |  |

| (master)           | (—t <sub>Sr</sub> )                      | High-speed mode | -300                                                    | 100                                                  | 400               | 625                | 700                | 813                | 850                |  |  |

| t <sub>sdaso</sub> | 1 t <sub>scll</sub> *3                   | Standard mode   | -1000                                                   | 250                                                  | 1300              | 2200               | 2500               | 2950               | 3100               |  |  |

| (slave)            | -12 t_cyc *2                             |                 |                                                         |                                                      |                   |                    |                    |                    |                    |  |  |

|                    | (—t <sub>sr</sub> )                      | High-speed mode | -300                                                    | 100                                                  | -1400*1           | -500*1             | -200*1             | 250                | 400                |  |  |

| t <sub>sdaho</sub> | 3 t <sub>cyc</sub>                       | Standard mode   | 0                                                       | 0                                                    | 600               | 375                | 300                | 188                | 150                |  |  |

|                    |                                          | High-speed mode | 0                                                       | 0                                                    | 600               | 375                | 300                | 188                | 150                |  |  |

### Table 16.11 I<sup>2</sup>C Bus Timing (with Maximum Influence of $t_{sr}/t_{sr}$ )

Notes: 1. Does not meet the I<sup>2</sup>C bus interface specification. Remedial action such as the following is necessary: (a) secure a start/stop condition issuance interval; (b) adjust the rise and fall times by means of a pull-up resistor and capacitive load; (c) reduce the transfer rate; (d) select slave devices whose input timing permits this output timing.

The values in the above table will vary depending on the settings of the IICX bit and bits CKS0 to CKS2. Depending on the frequency it may not be possible to achieve the maximum transfer rate; therefore, whether or not the  $l^2$ C bus interface specifications are met must be determined in accordance with the actual setting conditions.

- 2. Value when the IICX bit is set to 1. When the IICX bit is cleared to 0, the value is  $(t_{scll} 6t_{cyc})$ .

- 3. Calculated using the I<sup>2</sup>C bus specification values (standard mode: 4700 ns min.; high-speed mode: 1300 ns min.).

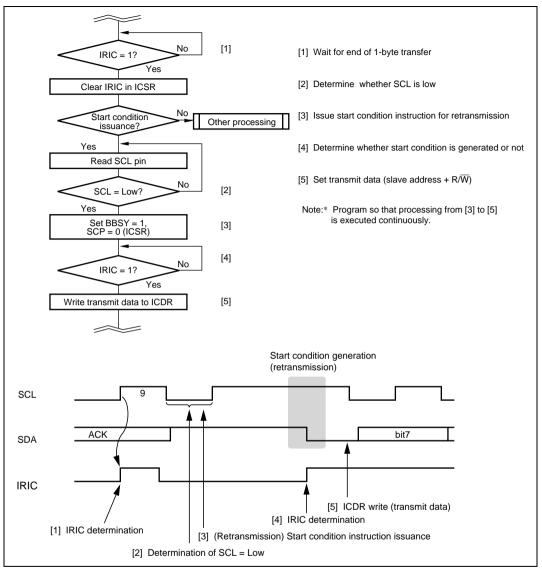

Figure 16.31 Flowchart for Start Condition Issuance Instruction for Retransmission and Timing

Note: This restriction on usage can be canceled by setting the FNC1 and FNC0 bits to 1 in ICXR.

### **19.5** Interrupt Sources

### 19.5.1 IBFI1 to IBFI3, and ERRI

The host interface has four interrupt requests for the slave processor (this LSI): IBF1 to IBF3, and ERRI. IBF11 to IBF13 are IDR receive complete interrupts for IDR1 to IDR3 and TWR, respectively. The ERRI interrupt indicates the occurrence of a special state such as an LPC reset, LPC shutdown, or transfer cycle abort. An interrupt request is enabled by setting the corresponding enable bit.

| Interrupt | Description                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|

| IBFI1     | When IBFIE1 is set to 1 and IDR1 reception is completed                                                                              |

| IBFI2     | When IBFIE2 is set to 1 and IDR2 reception is completed                                                                              |

| IBFI3     | When IBFIE3 is set to 1 and IDR3 reception is completed, or when TWRE and IBFIE3 are set to 1 and reception is completed up to TWR15 |

| ERRI      | When ERRIE is set to 1 and one of LRST, SDWN and ABRT is set to 1                                                                    |

Table 19.7

Receive Complete Interrupts and Error Interrupt

### 19.5.2 SMI, HIRQ1, HIRQ6, HIRQ9 to HIRQ12

The host interface can request seven kinds of host interrupt by means of SERIRQ. HIRQ1 and HIRQ12 are used on LPC channel 1 only, while SMI, HIRQ6, HIRQ9 to HIRQ11 can be requested from LPC channel 2 or 3.

There are two ways of clearing a host interrupt request.

When the IEDIR bit is cleared to 0 in SIRQCR0, host interrupt sources and LPC channels are all linked to the host interrupt request enable bits. When the OBF flag is cleared to 0 by a read of ODR or TWR15 by the host in the corresponding LPC channel, the corresponding host interrupt enable bit is automatically cleared to 0, and the host interrupt request is cleared.

When the IEDIR bit is set to 1 in SIRQCR0, LPC channel 2 and 3 interrupt requests are dependent only upon the host interrupt enable bits. The host interrupt enable bit is not cleared when OBF for channel 2 or 3 is cleared. Therefore, SMIE2, SMIE3A and SMIE3B, IRQ6E2 and IRQ6E3, IRQ9E2 and IRQ9E3, IRQ10E2 and IRQ10E3, and IRQ11E2 and IRQ11E3 lose their respective functional differences. In order to clear a host interrupt request, it is necessary to clear the host interrupt enable bit.

# Renesas

### 24.4 Bus Master Clock Select Circuit

The bus master clock select circuit selects a clock to supply the bus master with either the system clock ( $\phi$ ) or medium-speed clock ( $\phi/2$ ,  $\phi/4$ ,  $\phi/8$ ,  $\phi/16$ , or  $\phi/32$ ) by the SCK2 to SCK0 bits in SBYCR.

### 24.5 Subclock Input Circuit

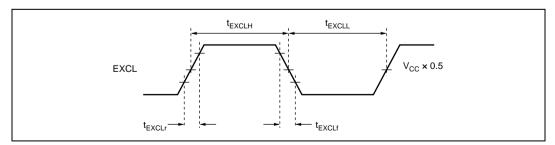

The subclock input circuit controls subclock input from the EXCL pin.

**Inputting the Subclock:** To use the subclock, a 32.768-kHz external clock should be input from the EXCL pin. At this time, the P96DDR bit in P9DDR should be cleared to 0, and the EXCLE bit in LPWRCR should be set to 1.

Subclock input conditions are shown in table 24.5. When the subclock is not used, subclock input should not be enabled.

### Table 24.5 Subclock Input Conditions

|                                       |                    | ,   | Vcc = 2.7 to | o 5.5 V |      | Measurement |

|---------------------------------------|--------------------|-----|--------------|---------|------|-------------|

| Item                                  | Symbol             | Min | Тур          | Max     | Unit | Condition   |

| Subclock input pulse width low level  | t <sub>excll</sub> | _   | 15.26        | —       | μs   | Figure 24.7 |

| Subclock input pulse width high level | t <sub>exclh</sub> | _   | 15.26        | —       | μs   |             |

| Subclock input rising time            | t <sub>EXCLr</sub> | _   | _            | 10      | ns   |             |

| Subclock input falling time           | $t_{_{EXCLf}}$     | —   | _            | 10      | ns   |             |

Figure 24.7 Subclock Input Timing

### 25.1.1 Standby Control Register (SBYCR)

SBYCR controls power-down modes.

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                                    |

|-----|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SSBY     | 0             | R/W | Software Standby                                                                                                                                                                                                                                                                               |

|     |          |               |     | Specifies the operating mode to be entered after executing the SLEEP instruction.                                                                                                                                                                                                              |

|     |          |               |     | When the SLEEP instruction is executed in high-speed mode or medium-speed mode:                                                                                                                                                                                                                |

|     |          |               |     | 0: Shifts to sleep mode                                                                                                                                                                                                                                                                        |

|     |          |               |     | 1: Shifts to software standby mode, subactive mode, or watch mode                                                                                                                                                                                                                              |

|     |          |               |     | When the SLEEP instruction is executed in subactive mode:                                                                                                                                                                                                                                      |

|     |          |               |     | 0: Shifts to subsleep mode                                                                                                                                                                                                                                                                     |

|     |          |               |     | 1: Shifts to watch mode or high-speed mode                                                                                                                                                                                                                                                     |

|     |          |               |     | Note that the SSBY bit is not changed even if a mode transition occurs by an interrupt.                                                                                                                                                                                                        |

| 6   | STS2     | 0             | R/W | Standby Timer Select 2 to 0                                                                                                                                                                                                                                                                    |

| 5   | STS1     | 0             | R/W | Selects the wait time for clock stabilization from clock                                                                                                                                                                                                                                       |

| 4   | STS0     | 0             | R/W | oscillation start when canceling software standby mode,<br>watch mode, or subactive mode. Select a wait time of 8 ms<br>(oscillation stabilization time) or more, depending on the<br>operating frequency. Table 25.1 shows the relationship<br>between the STS2 to STS0 values and wait time. |

|     |          |               |     | With an external clock, there are no specific wait requirements. Normally the minimum value is recommended.                                                                                                                                                                                    |

| 3   |          | 0             | R   | Reserved                                                                                                                                                                                                                                                                                       |

|     |          |               |     | This bit is always read as 0, and cannot be modified.                                                                                                                                                                                                                                          |

| Bit | Bit Name | Initial Value | R/W | Description                                                                                      |

|-----|----------|---------------|-----|--------------------------------------------------------------------------------------------------|

| 2   | SCK2     | 0             | R/W | System Clock Select 2 to 0                                                                       |

| 1   | SCK1     | 0             | R/W | Selects a clock for the bus master in high-speed mode or                                         |

| 0   | SCK0     | 0             | R/W | medium-speed mode.                                                                               |

|     |          |               |     | When making a transition to subactive mode or watch mode, SCK2 to SCK0 must be cleared to B'000. |

|     |          |               |     | 000: High-speed mode                                                                             |

|     |          |               |     | 001: Medium-speed clock: 2</td                                                                   |

|     |          |               |     | 010: Medium-speed clock:                                                                         |

|     |          |               |     | 011: Medium-speed clock:                                                                         |

|     |          |               |     | 100: Medium-speed clock:  \phi/16                                                                |

|     |          |               |     | 101: Medium-speed clock:                                                                         |

|     |          |               |     | 11X: —                                                                                           |

Legend:

X: Don't care

| STS2 | STS1 | STS0 | Wait Time     | 20 MHz | 10 MHz | 8 MHz | 6 MHz | 4 MHz | 2 MHz | Unit |

|------|------|------|---------------|--------|--------|-------|-------|-------|-------|------|

| 0    | 0    | 0    | 8192 states   | 0.4    | 0.8    | 1.0   | 1.3   | 2.0   | 4.1   | ms   |

| 0    | 0    | 1    | 16384 states  | 0.8    | 1.6    | 2.0   | 2.7   | 4.1   | 8.2   |      |

| 0    | 1    | 0    | 32768 states  | 2.0    | 3.3    | 4.1   | 5.5   | 8.2   | 16.4  | _    |

| 0    | 1    | 1    | 65536 states  | 4.1    | 6.6    | 8.2   | 10.9  | 16.4  | 32.8  |      |

| 1    | 0    | 0    | 131072 states | 8.2    | 13.1   | 16.4  | 21.8  | 32.8  | 65.5  |      |

| 1    | 0    | 1    | 262144 states | 16.4   | 26.2   | 32.8  | 43.6  | 65.6  | 131.2 |      |

| 1    | 1    | 0    | Reserved      | _      | _      | _     |       |       | _     |      |

| 1    | 1    | 1    | 16 states*    | 0.8    | 1.6    | 2.0   | 2.7   | 4.0   | 8.0   | μs   |

Shaded cells indicate the recommended specification.

Note: \* This setting cannot be made in the flash-memory version of this LSI.

| Register<br>Abbrevia-<br>tion | Reset       | High-<br>Speed/<br>Medium-<br>Speed | Watch | Sleep | Sub-<br>Active | Sub-<br>Sleep | Module<br>Stop | Software<br>Standby | Hardware<br>Standby | Module              |

|-------------------------------|-------------|-------------------------------------|-------|-------|----------------|---------------|----------------|---------------------|---------------------|---------------------|

| TCONRO                        | Initialized | —                                   | —     | —     | —              | —             | —              | —                   | Initialized         | Timer<br>connection |

| STR_2                         | Initialized | _                                   | _     | _     | _              | _             |                | —                   | Initialized         | XBS                 |

| TCONRS                        | Initialized | _                                   | _     | _     | _              | _             |                | —                   | Initialized         | Timer               |

| SEDGR                         | Initialized | _                                   | _     | _     | _              | _             | _              | _                   | Initialized         | connection          |

Notes: 1. Can be used on the H8S/2160B and H8S/2161B.

2. Not supported by the H8S/2148B and H8S/2145B (5-V version).

| Lower<br>Address | Register<br>Name | H8S/2140B, H8S/2141B,<br>H8S/2145B, H8S/2148B<br>Register Select Condition | H8S/2160B, H8S/2161B<br>Register Select Condition | Module<br>Name        |

|------------------|------------------|----------------------------------------------------------------------------|---------------------------------------------------|-----------------------|

| H'FE4E           | PCPIN (read)     | —                                                                          | No condition                                      | PORT                  |

|                  | PCDDR (write)    |                                                                            |                                                   |                       |

| H'FE4F           | PDPIN (read)     |                                                                            |                                                   |                       |

|                  | PDDDR (write)    |                                                                            |                                                   |                       |

| H'FE80           | HICR2            | MSTP2 = 0                                                                  | MSTP2 = 0                                         | XBS                   |

| H'FE81           | IDR_3            |                                                                            |                                                   |                       |

| H'FE82           | ODR_3            |                                                                            |                                                   |                       |

| H'FE83           | STR_3            |                                                                            |                                                   |                       |

| H'FE84           | IDR_4            |                                                                            |                                                   |                       |

| H'FE85           | ODR_4            |                                                                            |                                                   |                       |

| H'FE86           | STR_4            |                                                                            |                                                   |                       |

| H'FED4           | ICXR_0           | No condition                                                               | No condition                                      | IIC_0                 |

| H'FED5           | ICXR_1           |                                                                            |                                                   | IIC_1                 |

| H'FED8           | KBCRH_0          | MSTP2 = 0                                                                  | MSTP2 = 0                                         | Keyboard              |

| H'FED9           | KBCRL_0          |                                                                            |                                                   | buffer<br>controller  |

| H'FEDA           | KBBR_0           |                                                                            |                                                   | controller            |

| H'FEDC           | KBCRH_1          |                                                                            |                                                   |                       |

| H'FEDD           | KBCRL_1          |                                                                            |                                                   |                       |

| H'FEDE           | KBBR_1           |                                                                            |                                                   |                       |

| H'FEE0           | KBCRH_2          |                                                                            |                                                   |                       |

| H'FEE1           | KBCRL_2          |                                                                            |                                                   |                       |

| H'FEE2           | KBBR_2           |                                                                            |                                                   |                       |

| H'FEE4           | КВСОМР           | No condition                                                               | No condition                                      | IrDA/<br>expanded A/D |

| H'FEE6           | DDCSWR           | MSTP4 = 0                                                                  | MSTP4 = 0                                         | IIC_0                 |

| H'FEE8           | ICRA             | No condition                                                               | No condition                                      | INT                   |

| H'FEE9           | ICRB             | 1                                                                          |                                                   |                       |

| H'FEEA           | ICRC             | ]                                                                          |                                                   |                       |

| H'FEEB           | ISR              |                                                                            |                                                   |                       |

| H'FEEC           | ISCRH            |                                                                            |                                                   |                       |

| H'FEED           | ISCRL            |                                                                            |                                                   |                       |

| Section 27 Electrical Characteristics | s |

|---------------------------------------|---|

|---------------------------------------|---|

|                            |                                 |                                | Condition A<br>10 MHz                       |                                | Condition B<br>16 MHz        |                                | Condition C<br>20 MHz       |      | Test                |

|----------------------------|---------------------------------|--------------------------------|---------------------------------------------|--------------------------------|------------------------------|--------------------------------|-----------------------------|------|---------------------|

| ltem                       | Symbol                          | Min                            | Max                                         | Min                            | Max                          | Min                            | Max                         | Unit | Conditions          |

| Read data<br>access time 4 | t <sub>ACC4</sub>               | —                              | $2.5 	imes t_{_{cyc}} - 50$                 | —                              | $2.5 \times t_{_{cyc}} - 35$ | —                              | $2.5 	imes t_{_{cyc}} - 25$ | ns   | Figures<br>27.11 to |

| Read data<br>access time 5 | t <sub>ACC5</sub>               | _                              | $3.0 	imes t_{\scriptscriptstyle cyc} - 80$ | _                              | $3.0 \times t_{_{cyc}} - 55$ | _                              | $3.0 	imes t_{_{cyc}} - 40$ | ns   | 27.15               |

| HWR, LWR<br>delay time 1   | t <sub>wRD1</sub>               | —                              | 60                                          | —                              | 45                           | —                              | 30                          | ns   |                     |

| HWR, LWR<br>delay time 2   | $\mathbf{t}_{_{\mathrm{WRD2}}}$ | —                              | 60                                          | _                              | 45                           | _                              | 30                          | ns   |                     |

| HWR, LWR<br>pulse width 1  | t <sub>wsw1</sub>               | 1.0 ×<br>t <sub>cyc</sub> – 40 | _                                           | 1.0×<br>t <sub>cyc</sub> – 30  | _                            | 1.0 ×<br>t <sub>cyc</sub> – 20 | _                           | ns   |                     |

| HWR, LWR<br>pulse width 2  | t <sub>wsw2</sub>               | 1.5 ×<br>t <sub>cyc</sub> – 40 | _                                           | 1.5 ×<br>t <sub>cyc</sub> – 30 | _                            | 1.5 ×<br>t <sub>cyc</sub> – 20 | _                           | ns   |                     |

| Write data<br>delay time   | $\mathbf{t}_{_{\mathrm{WDD}}}$  | _                              | 60                                          | _                              | 45                           | _                              | 30                          | ns   |                     |

| Write data setup time      | $\mathbf{t}_{_{\mathrm{WDS}}}$  | 0                              | _                                           | 0                              | _                            | 0                              | _                           | ns   |                     |

| Write data<br>hold time    | $\mathbf{t}_{WDH}$              | 20                             |                                             | 15                             | _                            | 10                             | _                           | ns   |                     |

| WAIT setup<br>time         | t <sub>wrs</sub>                | 60                             |                                             | 45                             |                              | 30                             | —                           | ns   |                     |

| WAIT hold<br>time          | t <sub>wth</sub>                | 10                             | _                                           | 5                              | _                            | 5                              | _                           | ns   |                     |