Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Obsolete                                                        |

| Core Processor             | XCore                                                           |

| Core Size                  | 32-Bit 24-Core                                                  |

| Speed                      | 4000MIPS                                                        |

| Connectivity               | -                                                               |

| Peripherals                | <u>.</u>                                                        |

| Number of I/O              | 176                                                             |

| Program Memory Size        | 2MB (2M x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1M x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                    |

| Data Converters            | -                                                               |

| Oscillator Type            | External                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 374-LFBGA                                                       |

| Supplier Device Package    | 374-FBGA (18x18)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xlf232-1024-fb374-i40 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1   | xCORE Multicore Microcontrollers          |

|-----|-------------------------------------------|

| 2   | XLF232-1024-FB374 Features                |

| 3   | Pin Configuration                         |

| 4   | Signal Description                        |

| 5   | Example Application Diagram               |

| 6   | Product Overview                          |

| 7   | PLL                                       |

| 8   | Boot Procedure                            |

| 9   | Memory                                    |

| 10  | JTAG                                      |

| 11  | Board Integration                         |

| 12  | DC and Switching Characteristics          |

| 13  | Package Information                       |

| 14  | Ordering Information                      |

| App | endices                                   |

| A   | Configuration of the XLF232-1024-FB374 30 |

| В   | Processor Status Configuration            |

| С   | Tile Configuration                        |

| D   | Node Configuration                        |

| E   | JTAG, xSCOPE and Debugging                |

| F   | Schematics Design Check List              |

| G   | PCB Layout Design Check List              |

| Н   | Associated Design Documentation           |

| 1   | Related Documentation                     |

| J   | Revision History                          |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

# 4 Signal Description

This section lists the signals and I/O pins available on the XLF232-1024-FB374. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

- PD/PU: The IO pin has a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled. This resistor is designed to ensure defined logic input state for unconnected pins. It should not be used to pull external circuitry. Note that the resistors are highly non-linear and only a maximum pull current is specified in Section 12.2.

- ST: The IO pin has a Schmitt Trigger on its input.

- ▶ IOT: The IO pin is powered from VDDIOT (X1) or VDDIOT\_2 (X3), not VDDIO

- ▶ IO: the pin is powered from VDDIO

|          | Power pins (9)              |      |            |

|----------|-----------------------------|------|------------|

| Signal   | Function                    | Туре | Properties |

| GND      | Digital ground              | GND  |            |

| OTP_VCC  | OTP power supply            | PWR  |            |

| PLL_AGND | Analog ground for PLL       | PWR  |            |

| PLL_AVDD | Analog PLL power            | PWR  |            |

| VDD      | Digital tile power          | PWR  |            |

| VDD33    | Peripheral power            | PWR  |            |

| VDDIO    | Digital I/O power           | PWR  |            |

| VDDIOT   | Digital I/O power (top)     | PWR  |            |

| VDDIOT_2 | Digital I/O power (top, X3) | PWR  |            |

|        | JTAG pins (6)      |        |            |

|--------|--------------------|--------|------------|

| Signal | Function           | Туре   | Properties |

| RST_N  | Global reset input | Input  | IO, PU, ST |

| ТСК    | Test clock         | Input  | IO, PD, ST |

| TDI    | Test data input    | Input  | IO, PU     |

| TDO    | Test data output   | Output | IO, PD     |

| TMS    | Test mode select   | Input  | IO, PU     |

| TRST_N | Test reset input   | Input  | IO, PU, ST |

-XM()S

| X1D68       >         X1D69       >         X1D70       >         X2D00 | $x_{0}L2_{out}^{1}$ $x_{0}L2_{out}^{2}$ $x_{0}L2_{out}^{3}$ $x_{0}L2_{out}^{4}$                | 1A <sup>0</sup> | 4A <sup>0</sup><br>4A <sup>1</sup> | 8A <sup>0</sup> |                   | 32A <sup>16</sup><br>32A <sup>17</sup><br>32A <sup>18</sup><br>32A <sup>19</sup> | I/O<br>I/O<br>I/O<br>I/O | IO, PD<br>IO, PD<br>IO, PD |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|------------------------------------|-----------------|-------------------|----------------------------------------------------------------------------------|--------------------------|----------------------------|

| X1D68       >         X1D69       >         X1D70       >         X2D00 | X <sub>0</sub> L2 <sup>2</sup> <sub>out</sub><br>X <sub>0</sub> L2 <sup>3</sup> <sub>out</sub> | 1A <sup>0</sup> |                                    | 8A <sup>0</sup> |                   | 32A <sup>18</sup>                                                                | 1/0                      | IO, PD                     |

| X1D69       >         X1D70       >         X2D00                       | X <sub>0</sub> L2 <sup>3</sup><br>ut                                                           | 1A <sup>0</sup> |                                    | 8A <sup>0</sup> |                   |                                                                                  |                          |                            |

| X1D70 >><br>X2D00                                                       |                                                                                                | 1A <sup>0</sup> |                                    | 8A <sup>0</sup> |                   | 32A <sup>19</sup>                                                                | 1/0                      |                            |

| X2D00<br>X2D02<br>X2D03<br>X2D04<br>X2D05<br>X2D06                      |                                                                                                | 1A <sup>0</sup> |                                    | 8A <sup>0</sup> |                   |                                                                                  |                          | IO, PD                     |

| X2D03<br>X2D04<br>X2D05<br>X2D06                                        |                                                                                                |                 |                                    | 8A <sup>0</sup> |                   |                                                                                  | I/O                      | IO, PD                     |

| X2D04<br>X2D05<br>X2D06                                                 |                                                                                                |                 | 4A <sup>1</sup>                    |                 | 16A <sup>0</sup>  | 32A <sup>20</sup>                                                                | I/O                      | IO, PD                     |

| X2D05<br>X2D06                                                          |                                                                                                |                 |                                    | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup>                                                                | I/O                      | IO, PD                     |

| X2D06                                                                   |                                                                                                |                 | 4B <sup>0</sup>                    | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup>                                                                | I/O                      | IO, PD                     |

|                                                                         |                                                                                                |                 | 4B <sup>1</sup>                    | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup>                                                                | I/O                      | IO, PD                     |

| ⊢                                                                       |                                                                                                |                 | 4B <sup>2</sup>                    | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup>                                                                | I/O                      | IO, PD                     |

| X2D07                                                                   |                                                                                                |                 | 4B <sup>3</sup>                    | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup>                                                                | I/O                      | IO, PD                     |

| X2D08                                                                   |                                                                                                |                 | 4A <sup>2</sup>                    | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup>                                                                | I/O                      | IO, PD                     |

| X2D09                                                                   |                                                                                                |                 | 4A <sup>3</sup>                    | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup>                                                                | I/O                      | IO, PD                     |

| X2D11                                                                   |                                                                                                | 1D <sup>0</sup> |                                    |                 |                   |                                                                                  | I/O                      | IO, PD                     |

| X2D12                                                                   |                                                                                                | 1E <sup>0</sup> |                                    |                 |                   |                                                                                  | I/O                      | IO, PD                     |

| X2D13                                                                   |                                                                                                | 1F <sup>0</sup> |                                    |                 |                   |                                                                                  | I/O                      | IO, PD                     |

| X2D14                                                                   |                                                                                                |                 | 4C <sup>0</sup>                    | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup>                                                                | 1/0                      | IO, PD                     |

| X2D15                                                                   |                                                                                                |                 | 4C <sup>1</sup>                    | 8B <sup>1</sup> | 16A <sup>9</sup>  | 32A <sup>29</sup>                                                                | I/O                      | IO, PD                     |

|                                                                         | X <sub>2</sub> L4 <sup>4</sup>                                                                 |                 | 4D <sup>0</sup>                    | 8B <sup>2</sup> | 16A <sup>10</sup> | -                                                                                | I/O                      | IO, PD                     |

|                                                                         | $X_2L4_{in}^3$                                                                                 |                 | 4D <sup>1</sup>                    | 8B <sup>3</sup> | 16A <sup>11</sup> |                                                                                  | 1/0                      | IO, PD                     |

|                                                                         | X <sub>2</sub> L4 <sup>2</sup>                                                                 |                 | 4D <sup>2</sup>                    | 8B <sup>4</sup> | 16A <sup>12</sup> |                                                                                  | 1/0                      | IO, PD                     |

|                                                                         | X <sub>2</sub> L4 <sup>1</sup>                                                                 |                 | 4D <sup>3</sup>                    | 8B <sup>5</sup> | 16A <sup>13</sup> |                                                                                  | I/O                      | IO, PD                     |

| X2D20                                                                   | -2 - 10                                                                                        |                 | 4C <sup>2</sup>                    | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup>                                                                | 1/0                      | IO, PD                     |

| X2D21                                                                   |                                                                                                |                 | 4C <sup>3</sup>                    | 8B <sup>7</sup> | 16A <sup>15</sup> | 32A <sup>31</sup>                                                                | 1/0                      | IO, PD                     |

| X2D22                                                                   |                                                                                                | 1G <sup>0</sup> |                                    |                 |                   | -                                                                                | 1/0                      | IO, PD                     |

| X2D23                                                                   |                                                                                                | 1H <sup>0</sup> |                                    |                 |                   |                                                                                  | I/O                      | IO, PD                     |

|                                                                         | X <sub>2</sub> L7 <sup>0</sup>                                                                 | 110             |                                    |                 |                   |                                                                                  | I/O                      | IO, PD                     |

|                                                                         | $X_2L7_{out}^0$                                                                                | 1J <sup>0</sup> |                                    |                 |                   |                                                                                  | I/O                      | IO, PD                     |

|                                                                         | $X_2L7_{out}^3$                                                                                | .,              | 4E <sup>0</sup>                    | 8C <sup>0</sup> | 16B <sup>0</sup>  |                                                                                  | I/O                      | IO, PD                     |

|                                                                         | $X_2L7_{out}^4$                                                                                |                 | 4E <sup>1</sup>                    | 8C <sup>1</sup> | 16B <sup>1</sup>  |                                                                                  | I/O                      | IO, PD                     |

| X2D28                                                                   |                                                                                                |                 | 4F <sup>0</sup>                    | 8C <sup>2</sup> | 16B <sup>2</sup>  |                                                                                  | I/O                      | IO, PD                     |

| X2D29                                                                   |                                                                                                |                 | 4F <sup>1</sup>                    | 8C <sup>3</sup> | 16B <sup>3</sup>  |                                                                                  | I/O                      | IO, PD                     |

| X2D30                                                                   |                                                                                                |                 | 4F <sup>2</sup>                    | 8C <sup>4</sup> | 16B <sup>4</sup>  |                                                                                  | I/O                      | IO, PD                     |

| X2D31                                                                   |                                                                                                |                 | 4F <sup>3</sup>                    | 8C <sup>5</sup> | 16B <sup>5</sup>  |                                                                                  | I/O                      | IO, PD                     |

| X2D32                                                                   |                                                                                                |                 | 4E <sup>2</sup>                    | 8C <sup>6</sup> | 16B <sup>6</sup>  |                                                                                  | 1/0                      | IO, PD                     |

| X2D33                                                                   |                                                                                                |                 | 4E <sup>3</sup>                    | 8C <sup>7</sup> | 16B <sup>7</sup>  |                                                                                  | 1/0                      | IO, PD                     |

|                                                                         | X <sub>2</sub> L7 <sup>1</sup>                                                                 | 1K <sup>0</sup> |                                    |                 |                   |                                                                                  | 1/0                      | IO, PD                     |

|                                                                         | $X_2L7_{out}^2$<br>$X_2L7_{out}^2$                                                             | 1L <sup>0</sup> |                                    |                 |                   |                                                                                  | 1/0                      | IO, PD                     |

| X2D35 /                                                                 | out                                                                                            | 1M <sup>0</sup> |                                    | 8D <sup>0</sup> | 16B <sup>8</sup>  |                                                                                  | 1/0                      | IO, PD                     |

|                                                                         | X <sub>2</sub> L5 <sup>4</sup>                                                                 |                 |                                    | 00              |                   | 32A <sup>0</sup>                                                                 | 1/0                      | IO, PD                     |

|                                                                         | $X_2L5_{in}^3$<br>$X_2L5_{in}^3$                                                               |                 |                                    |                 |                   | 32A <sup>1</sup>                                                                 | 1/0<br>1/0               | IO, PD                     |

|                                                                         | $X_2L5_{in}^2$<br>$X_2L5_{in}^2$                                                               |                 |                                    |                 |                   | 32A <sup>2</sup>                                                                 | 1/0                      | IO, PD                     |

|                                                                         | $X_2L5_{in}^1$<br>$X_2L5_{in}^1$                                                               |                 |                                    |                 |                   | 32A <sup>3</sup>                                                                 | 1/0                      | IO, PD                     |

|                                                                         | ''2'''in                                                                                       |                 |                                    |                 |                   | 524                                                                              | 1/0                      | (continued)                |

-XMOS<sup>®</sup>-

(continued)

| X2D54 | X <sub>2</sub> L5 <sub>out</sub>               |                 |                 |                   | 32A <sup>3</sup>  | 1/0 | 10, PD  |

|-------|------------------------------------------------|-----------------|-----------------|-------------------|-------------------|-----|---------|

| X2D55 | X <sub>2</sub> L5 <sup>1</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>6</sup>  | I/0 | IO, PD  |

| X2D56 | X <sub>2</sub> L5 <sup>2</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>7</sup>  | I/O | IO, PD  |

| X2D57 | X <sub>2</sub> L5 <sup>3</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>8</sup>  | I/O | IO, PD  |

| X2D58 | X <sub>2</sub> L5 <sup>4</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>9</sup>  | I/O | IO, PD  |

| X2D61 | X <sub>2</sub> L6 <sup>4</sup> <sub>in</sub>   |                 |                 |                   | 32A <sup>10</sup> | I/O | IO, PD  |

| X2D62 | X <sub>2</sub> L6 <sup>3</sup> <sub>in</sub>   |                 |                 |                   | 32A <sup>11</sup> | I/O | IO, PD  |

| X2D63 | X <sub>2</sub> L6 <sup>2</sup> <sub>in</sub>   |                 |                 |                   | 32A <sup>12</sup> | I/O | IO, PD  |

| X2D64 | X <sub>2</sub> L6 <sup>1</sup> <sub>in</sub>   |                 |                 |                   | 32A <sup>13</sup> | I/O | IO, PD  |

| X2D65 | X <sub>2</sub> L6 <sup>0</sup> <sub>in</sub>   |                 |                 |                   | 32A <sup>14</sup> | I/O | IO, PD  |

| X2D66 | X <sub>2</sub> L6 <sup>0</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>15</sup> | I/O | IO, PD  |

| X2D67 | X <sub>2</sub> L6 <sup>1</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>16</sup> | I/O | IO, PD  |

| X2D68 | X <sub>2</sub> L6 <sup>2</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>17</sup> | I/O | IO, PD  |

| X2D69 | X <sub>2</sub> L6 <sup>3</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>18</sup> | I/O | IO, PD  |

| X2D70 | X <sub>2</sub> L6 <sup>4</sup> <sub>out</sub>  |                 |                 |                   | 32A <sup>19</sup> | I/O | IO, PD  |

| X3D00 | X <sub>2</sub> L7 <sup>2</sup> 1A <sup>0</sup> |                 |                 |                   |                   | I/0 | IO, PD  |

| X3D01 | X <sub>2</sub> L7 <sup>1</sup> 1B <sup>0</sup> |                 |                 |                   |                   | 1/0 | IO, PD  |

| X3D02 | X <sub>2</sub> L4 <sup>0</sup>                 | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | I/O | IO, PD  |

| X3D03 | X <sub>2</sub> L4 <sup>0</sup> <sub>out</sub>  | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup> | I/O | IO, PD  |

| X3D04 | X <sub>2</sub> L4 <sup>1</sup> <sub>out</sub>  | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | I/O | IO, PD  |

| X3D05 | X <sub>2</sub> L4 <sup>2</sup> <sub>out</sub>  | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | I/O | IO, PD  |

| X3D06 | X <sub>2</sub> L4 <sup>3</sup> <sub>out</sub>  | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | I/O | IO, PD  |

| X3D07 | X <sub>2</sub> L4 <sup>4</sup> <sub>out</sub>  | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | I/O | IO, PD  |

| X3D08 | X <sub>2</sub> L7 <sup>4</sup> <sub>in</sub>   | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O | IO, PD  |

| X3D09 | X <sub>2</sub> L7 <sup>3</sup> <sub>in</sub>   | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | I/O | IO, PD  |

| X3D10 | 1C <sup>0</sup>                                |                 |                 |                   |                   | I/O | IOT, PD |

| X3D11 | 1D <sup>0</sup>                                |                 |                 |                   |                   | I/O | IOT, PD |

| X3D12 | 1 E <sup>0</sup>                               |                 |                 |                   |                   | I/O | IO, PD  |

| X3D13 | 1 F <sup>0</sup>                               |                 |                 |                   |                   | I/O | IO, PD  |

| X3D14 |                                                | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | I/O | IO, PD  |

| X3D15 |                                                | 4C <sup>1</sup> | 8B1             | 16A <sup>9</sup>  | 32A <sup>29</sup> | I/O | IO, PD  |

| X3D20 |                                                | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | I/O | IO, PD  |

| X3D21 |                                                | 4C <sup>3</sup> | 8B <sup>7</sup> | 16A <sup>15</sup> | 32A <sup>31</sup> | I/O | IO, PD  |

| X3D23 | 1H <sup>0</sup>                                |                 |                 |                   |                   | I/O | IO, PD  |

| X3D24 | 110                                            |                 |                 |                   |                   | I/O | IO, PD  |

| X3D25 | 1J <sup>0</sup>                                |                 |                 |                   |                   | I/O | IO, PD  |

| X3D26 |                                                | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | I/O | IOT, PD |

| X3D27 |                                                | 4E <sup>1</sup> | 8C <sup>1</sup> | 16B <sup>1</sup>  |                   | I/O | IOT, PD |

| X3D28 |                                                | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | I/O | IOT, PD |

| X3D29 |                                                | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | I/O | IOT, PD |

| X3D30 |                                                | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | I/O | IOT, PD |

| X3D31 |                                                | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | I/O | IOT, PD |

|       |                                                |                 |                 |                   |                   |     |         |

XMOS<sup>®</sup>

Signal

X2D53

X2D54

Function

$X_2L5_{in}^0$

$X_2L5_{out}^0$

Туре

I/0

I/0

32A<sup>4</sup>

32A<sup>5</sup>

Properties

IO, PD

IO, PD

### XLF232-1024-FB374 Datasheet

| Signal | Function                                         | Туре | Properties |

|--------|--------------------------------------------------|------|------------|

| X3D32  | 4E <sup>2</sup> 8C <sup>6</sup> 16B <sup>6</sup> | I/0  | IOT, PD    |

| X3D33  | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup> | I/0  | IOT, PD    |

| X3D40  | 8D <sup>4</sup> 16B <sup>12</sup>                | I/0  | IOT, PD    |

| X3D41  | 8D <sup>5</sup> 16B <sup>13</sup>                | I/0  | IOT, PD    |

| X3D42  | 8D <sup>6</sup> 16B <sup>14</sup>                | I/0  | IOT, PD    |

| X3D43  | 8D <sup>7</sup> 16B <sup>15</sup>                | I/0  | IOT, PD    |

|         | System pins (4)     |       |            |

|---------|---------------------|-------|------------|

| Signal  | Function            | Туре  | Properties |

| CLK     | PLL reference clock | Input | IO, PD, ST |

| DEBUG_N | Multi-chip debug    | I/O   | IO, PU     |

| MODE0   | Boot mode select    | Input | PU         |

| MODE1   | Boot mode select    | Input | PU         |

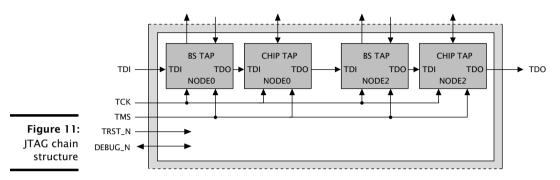

# 10 JTAG

The JTAG module can be used for loading programs, boundary scan testing, incircuit source-level debugging and programming the OTP memory.

The JTAG chain structure is illustrated in Figure 11. Directly after reset, two TAP controllers are present in the JTAG chain for each xCORE Tile: the boundary scan TAP and the chip TAP. The boundary scan TAP is a standard 1149.1 compliant TAP that can be used for boundary scan of the I/O pins. The chip TAP provides access into the xCORE Tile, switch and OTP for loading code and debugging.

The TRST\_N pin must be asserted low during and after power up for 100 ns. If JTAG is not required, the TRST\_N pin can be tied to ground to hold the JTAG module in reset.

The DEBUG\_N pin is used to synchronize the debugging of multiple xCORE Tiles. This pin can operate in both output and input mode. In output mode and when configured to do so, DEBUG\_N is driven low by the device when the processor hits a debug break point. Prior to this point the pin will be tri-stated. In input mode and when configured to do so, driving this pin low will put the xCORE Tile into debug mode. Software can set the behavior of the xCORE Tile based on this pin. This pin should have an external pull up of  $4K7-47K\Omega$  or left not connected in single core applications.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 12.

|              | Bit | 31  |      |   |   |   |   |   |   |   |    |      | De  | evice | Ide | ntifi | atio | n Re | egist | er |   |   |   |     |       |      |       |      |   |   | E | lit0 |

|--------------|-----|-----|------|---|---|---|---|---|---|---|----|------|-----|-------|-----|-------|------|------|-------|----|---|---|---|-----|-------|------|-------|------|---|---|---|------|

| Figure 12:   |     | Ver | sion |   |   |   |   |   |   |   | Pa | rt N | umb | er    |     |       |      |      |       |    |   |   |   | Man | ufact | ture | r Ide | ntit | y |   |   | 1    |

| IDCODE       | 0   | 0   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0    | 0   | 0     | 0   | 0     | 0    | 1    | 1     | 0  | 0 | 1 | 1 | 0   | 0     | 0    | 1     | 1    | 0 | 0 | 1 | 1    |

| return value |     | (   | 0    |   |   | ( | D |   |   | C | )  |      |     | (     | )   |       |      | e    | 5     |    |   | 6 | 5 |     |       |      | 3     |      |   | Э | 3 |      |

-XM()S

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 13. The OTP User ID field is read from bits [22:31] of the security register on xCORE Tile 0, *see* §9.1 (all zero on unprogrammed devices).

Figure 13: USERCODE return value

|         | Bit | 31 |   |   |      |      |    |   |   |   |   |     |      | ι | Jser | code | Reg | giste | r |   |   |       |      |       |     |   |   |   |   |   | В | it0 |

|---------|-----|----|---|---|------|------|----|---|---|---|---|-----|------|---|------|------|-----|-------|---|---|---|-------|------|-------|-----|---|---|---|---|---|---|-----|

| 3:<br>「 |     |    |   | 0 | TP U | lser | ID |   |   |   |   | Unu | ised |   |      |      |     |       |   |   |   | Silic | on I | Revis | ion |   |   |   |   |   |   |     |

| E       | 0   | 0  | 0 | 0 | 0    | 0    | 0  | 0 | 0 | 0 | 0 | 0   | 0    | 0 | 1    | 0    | 1   | 0     | 0 | 0 | 0 | 0     | 0    | 0     | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| e       |     |    | 0 |   |      | (    | )  |   |   | ( | ) |     |      | 2 | 2    |      |     | 8     | 3 |   |   | C     | )    |       |     | ( | ) |   |   | C | ) |     |

# 11 Board Integration

The device has the following power supply pins:

- ▶ VDD pins for the xCORE Tile

- ▶ VDDIO pins for the I/O lines

- ▶ PLL\_AVDD pins for the PLL

- OTP\_VCC pins for the OTP

Several pins of each type are provided to minimize the effect of inductance within the package, all of which must be connected. The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDD supply must ramp from 0V to its final value within 10 ms to ensure correct startup.

The VDDIO and OTP\_VCC supply must ramp to its final value before VDD reaches 0.4 V.

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $2.2 \Omega$  resistor and 100 nF multi-layer ceramic capacitor) is recommended on this pin.

The following ground pins are provided:

- PLL\_AGND for PLL\_AVDD

- ► GND for all other supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND (for example, 100nF 0402 for every other supply pin). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

RST\_N is an active-low asynchronous-assertion global reset signal. Following a reset, the PLL re-establishes lock after which the device boots up according to the boot mode (*see* §8). RST\_N and must be asserted low during and after power up for 100 ns.

#### 11.1 Land patterns and solder stencils

The package is a 374 ball Fine Ball Grid Array (FBGA) on a 0.8 mm pitch.

The land patterns and solder stencils will depend on the PCB manufacturing process. We recommend you design them with using the IPC specifications *"Generic Requirements for Surface Mount Design and Land Pattern Standards"* IPC-7351B. This standard aims to achieve desired targets of heel, toe and side fillets for solder-joints. The mechanical drawings in Section 13 specify the dimensions and tolerances.

#### 11.2 Ground and Thermal Vias

Vias next to each ground ball into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance.

#### 11.3 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they are stored below 30C and 60% RH. If devices have exceeded these values or an included moisture indicator card shows excessive levels of moisture, then the parts should be baked as appropriate before use. This is based on information from *Joint IPC/JEDEC Standard For Moisture/Reflow Sensitivity Classification For Nonhermetic Solid State Surface-Mount Devices* J-STD-020 Revision D.

$-X \Lambda ()S$

X009390,

# 12 DC and Switching Characteristics

| Symbol   | Parameter                                     | MIN   | ТҮР  | MAX   | UNITS | Notes |

|----------|-----------------------------------------------|-------|------|-------|-------|-------|

| VDD      | Tile DC supply voltage                        | 0.95  | 1.00 | 1.05  | V     |       |

| VDDIO    | I/O supply voltage                            | 2.30  | 3.30 | 3.60  | V     |       |

| VDDIOT_0 | I/O supply voltage                            | 2.25  | 3.30 | 3.60  | V     |       |

| VDDIOT_1 | I/O supply voltage                            | 2.25  | 3.30 | 3.60  | V     |       |

| USB_VDD  | USB tile DC supply voltage                    | 0.95  | 1.00 | 1.05  | V     |       |

| VDD33    | Peripheral supply                             | 3.135 | 3.30 | 3.465 | V     |       |

| PLL_AVDD | PLL analog supply                             | 0.95  | 1.00 | 1.05  | V     |       |

| CI       | xCORE Tile I/O load<br>capacitance            |       |      | 25    | pF    |       |

| Та       | Ambient operating<br>temperature (Commercial) | 0     |      | 70    | °C    |       |

|          | Ambient operating<br>temperature (Industrial) | -40   |      | 85    | °C    |       |

| Tj       | Junction temperature                          |       |      | 125   | °C    |       |

| Tstg     | Storage temperature                           | -65   |      | 150   | °C    |       |

#### 12.1 Operating Conditions

Figure 14: Operating conditions

#### 12.2 DC Characteristics, VDDIO=3V3

| Symbol | Parameter                                | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|------------------------------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage                       | 2.00  |     | 3.60 | V     | A     |

| V(IL)  | Input low voltage                        | -0.30 |     | 0.70 | V     | A     |

| V(OH)  | Output high voltage                      | 2.20  |     |      | V     | B, C  |

| V(OL)  | Output low voltage                       |       |     | 0.40 | V     | B, C  |

| I(PU)  | Internal pull-up current (Vin=0V)        | -100  |     |      | μA    | D     |

| I(PD)  | Internal pull-down current<br>(Vin=3.3V) |       |     | 100  | μA    | D     |

| I(LC)  | Input leakage current                    | -10   |     | 10   | μA    |       |

Figure 15: DC characteristics

A All pins except power supply pins.

B Pins X1D40, X1D41, X1D42, X1D43, X1D26, X1D27, X3D40, X3D41, X3D42, X3D43, X3D26, and X3D27 are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry. In order to pull the pin to the opposite state, a 4K7 resistor is recommended to overome the internal pull current.

More detailed power analysis can be found in the XS1-LF Power Consumption document.

| 12.6 Clock |

|------------|

|------------|

Figure 20: Clock

| Symbol | Parameter                 | MIN  | ТҮР | MAX | UNITS | Notes |

|--------|---------------------------|------|-----|-----|-------|-------|

| f      | Frequency                 | 3.25 | 25  | 100 | MHz   |       |

| SR     | Slew rate                 | 0.10 |     |     | V/ns  |       |

| TJ(LT) | Long term jitter (pk-pk)  |      |     | 2   | %     | А     |

| f(MAX) | Processor clock frequency |      |     | 500 | MHz   | В     |

A Percentage of CLK period.

B Assumes typical tile and I/O voltages with nominal activity.

Further details can be found in the XS1-LF Clock Frequency Control document,

#### 12.7 xCORE Tile I/O AC Characteristics

|                             | Symbol       | Parameter                                                           | MIN | ТҮР | MAX | UNITS | Notes |

|-----------------------------|--------------|---------------------------------------------------------------------|-----|-----|-----|-------|-------|

|                             | T(XOVALID)   | Input data valid window                                             | 8   |     |     | ns    |       |

| Figure 21:                  | T(XOINVALID) | Output data invalid window                                          | 9   |     |     | ns    |       |

| I/O AC char-<br>acteristics | T(XIFMAX)    | Rate at which data can be sampled with respect to an external clock |     |     | 60  | MHz   |       |

The input valid window parameter relates to the capability of the device to capture data input to the chip with respect to an external clock source. It is calculated as the sum of the input setup time and input hold time with respect to the external clock as measured at the pins. The output invalid window specifies the time for which an output is invalid with respect to the external clock. Note that these parameters are specified as a window rather than absolute numbers since the device provides functionality to delay the incoming clock with respect to the incoming data.

Information on interfacing to high-speed synchronous interfaces can be found in the XS1 Port I/O Timing document, X5821.

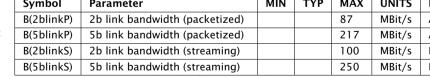

#### 12.8 xConnect Link Performance

|                                   | Symbol     | Parameter                      | MIN | ТҮР | MAX | UNITS  | Notes |

|-----------------------------------|------------|--------------------------------|-----|-----|-----|--------|-------|

|                                   | B(2blinkP) | 2b link bandwidth (packetized) |     |     | 87  | MBit/s | А, В  |

| Figure 22:<br>Link<br>performance | B(5blinkP) | 5b link bandwidth (packetized) |     |     | 217 | MBit/s | А, В  |

|                                   | B(2blinkS) | 2b link bandwidth (streaming)  |     |     | 100 | MBit/s | В     |

|                                   | B(5blinkS) | 5b link bandwidth (streaming)  |     |     | 250 | MBit/s | В     |

A Assumes 32-byte packet in 3-byte header mode. Actual performance depends on size of the header and payload.

B 7.5 ns symbol time.

-XMOS-

The asynchronous nature of links means that the relative phasing of CLK clocks is not important in a multi-clock system, providing each meets the required stability criteria.

| Symbol   | Parameter                     | MIN | TYP | MAX | UNITS | Notes |

|----------|-------------------------------|-----|-----|-----|-------|-------|

| f(TCK_D) | TCK frequency (debug)         |     |     | 18  | MHz   |       |

| f(TCK_B) | TCK frequency (boundary scan) |     |     | 10  | MHz   |       |

| T(SETUP) | TDO to TCK setup time         | 5   |     |     | ns    | А     |

| T(HOLD)  | TDO to TCK hold time          | 5   |     |     | ns    | А     |

| T(DELAY) | TCK to output delay           |     |     | 15  | ns    | В     |

## 12.9 JTAG Timing

Figure 23: JTAG timing

A Timing applies to TMS and TDI inputs.

B Timing applies to TDO output from negative edge of TCK.

All JTAG operations are synchronous to TCK apart from the global asynchronous reset TRST\_N.

| <b>0x13:</b><br>DGETREG<br>operand 1 | Bits | Perm | Init | Description              |

|--------------------------------------|------|------|------|--------------------------|

|                                      | 31:8 | RO   | -    | Reserved                 |

|                                      | 7:0  | DRW  |      | Thread number to be read |

## B.16 DGETREG operand 2: 0x14

Register number to be read by DGETREG

0x14: DGETREG operand 2

| Bits | Perm | Init | Description                |  |

|------|------|------|----------------------------|--|

| 31:5 | RO   | -    | Reserved                   |  |

| 4:0  | DRW  |      | Register number to be read |  |

#### **B.17** Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

| Bits  | Perm | Init | Description                                                                                                                                                                                                              |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 17:16 | DRW  |      | Number of the hardware breakpoint/watchpoint which caused<br>the interrupt (always 0 for =HOST= and =DCALL=). If multiple<br>breakpoints/watchpoints trigger at once, the lowest number is<br>taken.                     |

| 15:8  | DRW  |      | Number of thread which caused the debug interrupt (always 0 in the case of =HOST=).                                                                                                                                      |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                 |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point |

0x15: Debug interrupt type

## B.18 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

-XMOS-

#### B.22 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

| Bits  | Perm | Init | Description                                                                                                |  |

|-------|------|------|------------------------------------------------------------------------------------------------------------|--|

| 31:24 | RO   | -    | Reserved                                                                                                   |  |

| 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint t<br>be enabled individually for each thread. |  |

| 15:2  | RO   | -    | Reserved                                                                                                   |  |

| 1     | DRW  | 0    | When 0 break when PC == IBREAK_ADDR. When 1 = break when PC != IBREAK_ADDR.                                |  |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                              |  |

0x40 .. 0x43: Instruction breakpoint control

#### B.23 Data watchpoint address 1: 0x50 .. 0x53

This set of registers contains the first address for the four data watchpoints.

**0x50 .. 0x53:** Data watchpoint address 1

| Data<br>hpoint | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ress 1         | 31:0 | DRW  |      | Value.      |

#### B.24 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| Data<br>Chpoint | Bits | Perm | Init | Description |

|-----------------|------|------|------|-------------|

| dress 2         | 31:0 | DRW  |      | Value.      |

## B.25 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

-XMOS

XS2-LF32A-1024-FB374

|                                   | Bits  | Perm | Init | Description                                        |

|-----------------------------------|-------|------|------|----------------------------------------------------|

|                                   | 31:24 | CRO  |      | Processor ID of this XCore.                        |

| 0x00:                             | 23:16 | CRO  |      | Number of the node in which this XCore is located. |

| 0x00:<br>Device<br>identification | 15:8  | CRO  |      | XCore revision.                                    |

|                                   | 7:0   | CRO  |      | XCore version.                                     |

#### C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

| Bits  | Perm | Init | Description              |

|-------|------|------|--------------------------|

| 31:24 | CRO  |      | Number of channel ends.  |

| 23:16 | CRO  |      | Number of the locks.     |

| 15:8  | CRO  |      | Number of synchronisers. |

| 7:0   | RO   | -    | Reserved                 |

#### C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

0x01: xCORE Tile description 1

|      | Bits  | Perm | Init | Description             |

|------|-------|------|------|-------------------------|

| x02: | 31:16 | RO   | -    | Reserved                |

| Tile | 15:8  | CRO  |      | Number of clock blocks. |

| on 2 | 7:0   | CRO  |      | Number of timers.       |

## C.4 Control PSwitch permissions to debug registers: 0x04

-XMOS-

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

0x41: PC of logical core 1

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

### C.11 PC of logical core 2: 0x42

Value of the PC of logical core 2.

0x42: PC of logical core 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

## C.12 PC of logical core 3: 0x43

Value of the PC of logical core 3.

| 0x43:         |                  |      |      |             |

|---------------|------------------|------|------|-------------|

| PC of logical | <b>Bits</b> 31:0 | Perm | Init | Description |

| core 3        | 31:0             | CRO  |      | Value.      |

#### C.13 PC of logical core 4: 0x44

Value of the PC of logical core 4.

**0x44**: PC of logical core 4

| <b>0x44:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 4                  | 31:0 | CRO  |      | Value.      |

## C.14 PC of logical core 5: 0x45

Value of the PC of logical core 5.

**0x45:** PC of logical core 5

|   | Bits | Perm | Init | Description |

|---|------|------|------|-------------|

| ; | 31:0 | CRO  |      | Value.      |

Bits

31:0

### C.15 PC of logical core 6: 0x46

Value of the PC of logical core 6.

**0x46:** PC of logical core 6

Perm

Init

Description

CRO

Value.

## C.16 PC of logical core 7: 0x47

Value of the PC of logical core 7.

0x47 PC of logical core 7

| 0x47:<br>gical | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ore 7          | 31:0 | CRO  |      | Value.      |

## C.17 SR of logical core 0: 0x60

Value of the SR of logical core 0

**0x60:** SR of logical core 0

| <b>0x60:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 0                  | 31:0 | CRO  |      | Value.      |

## C.18 SR of logical core 1: 0x61

Value of the SR of logical core 1

**0x61** SR of logical core 1

| 61:<br>cal | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| e 1        | 31:0 | CRO  |      | Value.      |

## C.19 SR of logical core 2: 0x62

Value of the SR of logical core 2

|   | Bits  | Perm | Init | Description                                     |

|---|-------|------|------|-------------------------------------------------|

| Э | 31:28 | RW   | 0    | The direction for packets whose dimension is F. |

| 2 | 27:24 | RW   | 0    | The direction for packets whose dimension is E. |

| 2 | 23:20 | RW   | 0    | The direction for packets whose dimension is D. |

| 1 | 19:16 | RW   | 0    | The direction for packets whose dimension is C. |

| 1 | 15:12 | RW   | 0    | The direction for packets whose dimension is B. |

|   | 11:8  | RW   | 0    | The direction for packets whose dimension is A. |

|   | 7:4   | RW   | 0    | The direction for packets whose dimension is 9. |

|   | 3:0   | RW   | 0    | The direction for packets whose dimension is 8. |

**0x0D:** Directions 8-15

## D.12 DEBUG\_N configuration, tile 0: 0x10

Configures the behavior of the DEBUG\_N pin.

**0x10** DEBUG\_N con figuration tile 0

|                    | Bits | Perm | Init | Description                                                     |

|--------------------|------|------|------|-----------------------------------------------------------------|

| 1 <b>0:</b><br>on- | 31:2 | RO   | -    | Reserved                                                        |

| on,                | 1    | RW   | 0    | Set 1 to enable GlobalDebug to generate debug request to XCore. |

| 0                  | 0    | RW   | 0    | Set 1 to enable inDebug bit to drive GlobalDebug.               |

## D.13 DEBUG\_N configuration, tile 1: 0x11

Configures the behavior of the DEBUG\_N pin.

**0x11** DEBUG\_N con figuration tile 1

| _         | Bits | Perm | Init | Description                                                     |

|-----------|------|------|------|-----------------------------------------------------------------|

| 1:<br>0n- | 31:2 | RO   | -    | Reserved                                                        |

| on,       | 1    | RW   | 0    | Set 1 to enable GlobalDebug to generate debug request to XCore. |

| : 1       | 0    | RW   | 0    | Set 1 to enable inDebug bit to drive GlobalDebug.               |

### D.14 Debug source: 0x1F

Contains the source of the most recent debug event.

$\cdot X MOS$

TDO to pin 13 of the xSYS header

The RST\_N net should be open-drain, active-low, and have a pull-up to VDDIO.

#### E.3 Full xSYS header

For a full xSYS header you will need to connect the pins as discussed in Section E.2, and then connect a 2-wire xCONNECT Link to the xSYS header. The links can be found in the Signal description table (Section 4): they are labelled XL0, XL1, etc in the function column. The 2-wire link comprises two inputs and outputs, labelled  ${}^{1}_{out}$ ,  ${}^{0}_{out}$ ,  ${}^{0}_{in}$ , and  ${}^{1}_{in}$ . For example, if you choose to use XL0 for xSCOPE I/O, you need to connect up XL0 ${}^{1}_{out}$ , XL0 ${}^{0}_{out}$ , XL0 ${}^{1}_{in}$ , as follows:

- XL0<sup>1</sup><sub>out</sub> (X0D43) to pin 6 of the xSYS header with a 33R series resistor close to the device.

- XL0<sup>0</sup><sub>out</sub> (X0D42) to pin 10 of the xSYS header with a 33R series resistor close to the device.

- ▶ XL0<sup>0</sup><sub>in</sub> (X0D41) to pin 14 of the xSYS header.

- >  $XLO_{in}^{1}$  (X0D40) to pin 18 of the xSYS header.

# H Associated Design Documentation

| Document Title                                  | Information                               | Document Number |

|-------------------------------------------------|-------------------------------------------|-----------------|

| Estimating Power Consumption For XS1-LF Devices | Power consumption                         | X4271           |

| Programming XC on XMOS Devices                  | Timers, ports, clocks, cores and channels | X9577           |

| xTIMEcomposer User Guide                        | Compilers, assembler and linker/mapper    | X3766           |

|                                                 | Timing analyzer, xScope, debugger         |                 |

|                                                 | Flash and OTP programming utilities       |                 |

# I Related Documentation

| Document Title                                   | Information                         | Document Number |

|--------------------------------------------------|-------------------------------------|-----------------|

| The XMOS XS1 Architecture                        | ISA manual                          | X7879           |

| XS1 Port I/O Timing                              | Port timings                        | X5821           |

| xCONNECT Architecture                            | Link, switch and system information | X4249           |

| XS1-LF Link Performance and Design<br>Guidelines | Link timings                        | X2999           |

| XS1-LF Clock Frequency Control                   | Advanced clock control              | X1433           |

| XS1-L Active Power Conservation                  | Low-power mode during idle          | X7411           |

-XMOS°-

# J Revision History

| Date       | Description                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------|

| 2015-03-20 | Preliminary release                                                                                 |

| 2015-04-14 | Added RST to pins to be pulled hard, and removed reference to TCK from Errata                       |

|            | Removed TRST_N references in packages that have no TRST_N                                           |

|            | New diagram for boot from embedded flash showing ports                                              |

|            | Pull up requirements for shared clock and external resistor for QSPI                                |

| 2015-05-06 | Removed references to DEBUG_N                                                                       |

| 2015-07-09 | Updated electrical characteristics - Section 12                                                     |

| 2015-08-27 | Updated part marking and product code - Section 14                                                  |

| 2015-11-23 | Updated status of X2D04, X2D05, X2D06, X2D07 during boot - Section 8                                |

|            | Updated Schematics Design Checklist: GPIO for X2D04, X2D05, X2D06, X2D07<br>during boot - Section F |

| 2015-12-18 | Clarified connectivity of internal and external xCONNECT links - Sections 3 and 4                   |

|            | Made pin names canonical - Sections 3 and 4                                                         |

|            | Updated JTAG diagram - Section 10                                                                   |

|            | Removed references to 400MHz parts - Section 12                                                     |

| 2016-01-05 | Updated signal tables to use VDDIO - Section 4                                                      |

|            | Updated IDD value - Section 12                                                                      |

|            | Updated land pattern description - Section 11.1                                                     |

| 2016-04-20 | Typical internal pull-up and pull down current diagrams added - Section 12                          |

XMOS®

Copyright © 2016, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.