#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

E·XFI

| 2 0 0 0 0 0                     |                                                              |

|---------------------------------|--------------------------------------------------------------|

| Product Status                  | Active                                                       |

| Core Processor                  | MPC8xx                                                       |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 50MHz                                                        |

| Co-Processors/DSP               | Communications; CPM                                          |

| RAM Controllers                 | DRAM                                                         |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                   |

| SATA                            | · ·                                                          |

| USB                             |                                                              |

| Voltage - I/O                   | 3.3V                                                         |

| Operating Temperature           | -40°C ~ 100°C (TA)                                           |

| Security Features               | -                                                            |

| Package / Case                  | 357-BBGA                                                     |

| Supplier Device Package         | 357-PBGA (25x25)                                             |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc859dslcvr50a |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Features

- One serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multiple-master operation on the same bus

- One inter-integrated circuit (I<sup>2</sup>C) port

- Supports master and slave modes

- Multiple-master environment support

- Time slot assigner (TSA) (MPC859DSL does not have TSA.)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

- Allows dynamic changes

- On MPC866P and MPC866T, can be internally connected to six serial channels (four SCCs and two SMCs); on MPC859P and MPC859T, can be connected to three serial channels (one SCC and two SMCs).

- Parallel interface port (PIP)

- Centronics interface support

- Supports fast connection between compatible ports on MPC866/859 or MC68360

- PCMCIA interface

- Master (socket) interface, compliant with PCI Local Bus Specification (Rev 2.1)

- Supports one or two PCMCIA sockets whether ESAR functionality is enabled

- Eight memory or I/O windows supported

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two operate on data.

- Supports conditions: =  $\neq < >$

- Each watchpoint can generate a breakpoint internally

- Normal high and normal low power modes to conserve power

- 1.8 V core and 3.3 V I/O operation with 5-V TTL compatibility; refer to Table 6 for a listing of the 5-V tolerant pins.

- 357-pin plastic ball grid array (PBGA) package

- Operation up to 133 MHz

### Features

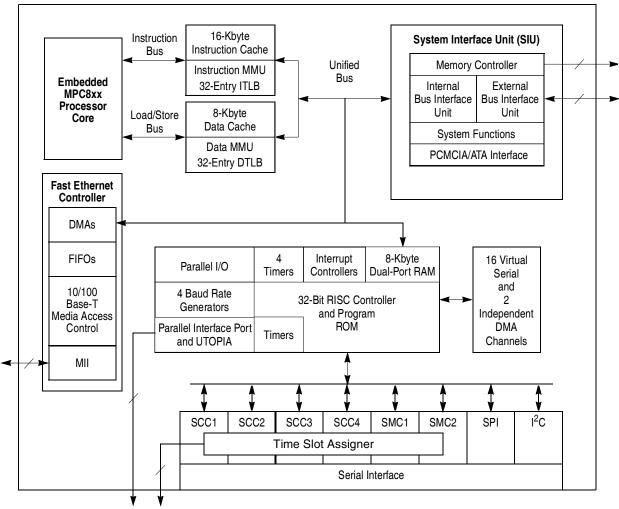

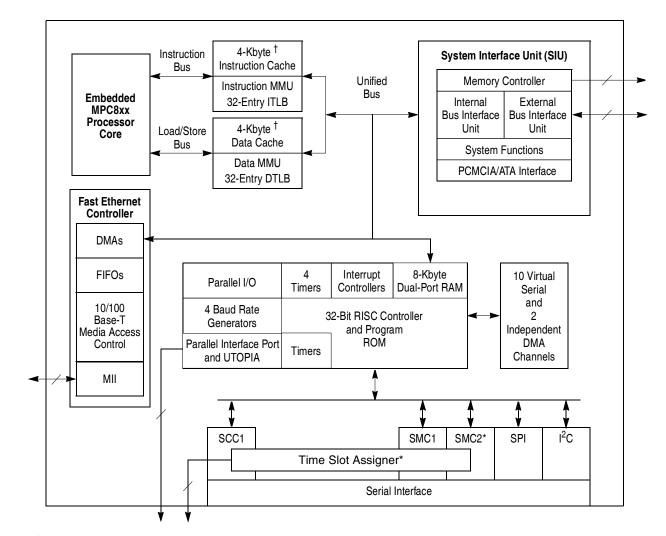

The MPC866/859 is comprised of three modules that each use a 32-bit internal bus: MPC8xx core, system integration unit (SIU), and communication processor module (CPM). The MPC866P block diagram is shown in Figure 1. The MPC859P/859T/859DSL block diagram is shown in Figure 2.

Figure 1. MPC866P Block Diagram

- <sup>†</sup> The MPC859P has a 16-Kbyte instruction cache and a 8-Kbyte data cache.

- \* The MPC859DSL does not contain SMC2 nor the time slot assigner, and provides eight SDMA controllers.

### Figure 2. MPC859P/859T/MPC859DSL Block Diagram

**Maximum Tolerated Ratings**

# 3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC866/859. Table 2 shows the maximum tolerated ratings, and Table 3 shows the operating temperatures.

| Rating                      | Symbol                            | Value                             | Unit |

|-----------------------------|-----------------------------------|-----------------------------------|------|

| Supply voltage <sup>1</sup> | VDDH                              | - 0.3 to 4.0                      | V    |

|                             | VDDL                              | - 0.3 to 2.0                      | V    |

|                             | VDDSYN                            | - 0.3 to 2.0                      | V    |

|                             | Difference between VDDL to VDDSYN | 100                               | mV   |

| Input voltage <sup>2</sup>  | V <sub>in</sub>                   | V <sub>in</sub> GND – 0.3 to VDDH |      |

| Storage temperature range   | T <sub>stg</sub>                  | -55 to +150                       | °C   |

### **Table 2. Maximum Tolerated Ratings**

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 6. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device. See page 15.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than VDDH. This restriction applies to power-up and normal operation (that is, if the MPC866/859 is unpowered, a voltage greater than 2.5 V must not be applied to its inputs).

|                                     | scruting rempere    |       |      |

|-------------------------------------|---------------------|-------|------|

| Rating                              | Symbol              | Value | Unit |

| Temperature <sup>1</sup> (standard) | T <sub>A(min)</sub> | 0     | °C   |

|                                     | T <sub>j(max)</sub> | 95    | °C   |

| Temperature (extended)              | T <sub>A(min)</sub> | -40   | °C   |

|                                     | T <sub>j(max)</sub> | 100   | °C   |

### **Table 3. Operating Temperatures**

Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

|      | Ohann sharia tia                                                                                                                                                          | 33    | MHz   | 40 I  | MHz   | 50 I  | MHz   | 66 I  | MHz   |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Num  | Characteristic                                                                                                                                                            | Min   | Max   | Min   | Мах   | Min   | Max   | Min   | Max   | Unit |

| B22b | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0, EBDF = 0<br>(MAX = 0.25 x B1 + 6.3)                                                           | 7.60  | 13.80 | 6.30  | 12.50 | 5.00  | 11.30 | 3.80  | 10.00 | ns   |

| B22c | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0, EBDF = 1<br>(MAX = 0.375 x B1 + 6.6)                                                          | 10.90 | 18.00 | 10.90 | 16.00 | 7.00  | 14.10 | 5.20  | 12.30 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated<br>GPCM read access, GPCM write<br>access ACS = 00, TRLX = 0 & CSNT =<br>0 (MAX = 0.00 x B1 + 8.00)                         | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 0<br>(MIN = 0.25 x B1 - 2.00)                                                               | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80  | _     | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 11, TRLX = 0<br>(MIN = 0.50 x B1 - 2.00)                                                               | 13.20 | —     | 10.50 | —     | 8.00  | —     | 5.60  | —     | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}(0:3)$<br>asserted (MAX = 0.00 x B1 + 9.00)                                                                         | —     | 9.00  | —     | 9.00  |       | 9.00  |       | 9.00  | ns   |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated (MAX = 0.00 x B1 + 9.00)                                                                                                    | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 1<br>(MIN = 1.25 x B1 - 2.00)                                                               | 35.90 | —     | 29.30 | —     | 23.00 | —     | 16.90 | _     | ns   |

| B27a | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 11, TRLX = 1<br>(MIN = 1.50 x B1 - 2.00)                                                               | 43.50 | —     | 35.50 | _     | 28.00 | _     | 20.70 | _     | ns   |

| B28  | CLKOUT rising edge to $\overline{WE}(0:3)$<br>negated GPCM write access CSNT =<br>0 (MAX = 0.00 x B1 + 9.00)                                                              | —     | 9.00  | —     | 9.00  | _     | 9.00  | —     | 9.00  | ns   |

| B28a | CLKOUT falling edge to $\overline{WE}(0:3)$<br>negated GPCM write access TRLX = 0,1, CSNT = 1, EBDF = 0 (MAX = 0.25 x B1 + 6.80)                                          | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80  | 10.50 | ns   |

| B28b | CLKOUT falling edge to $\overline{CS}$ negated<br>GPCM write access TRLX = 0,1,<br>CSNT = 1, ACS = 10 or ACS = 11,<br>EBDF = 0 (MAX = 0.25 x B1 + 6.80)                   | _     | 14.30 | _     | 13.00 | _     | 11.80 | _     | 10.50 | ns   |

| B28c | CLKOUT falling edge to $\overline{WE}(0:3)$<br>negated GPCM write access TRLX =<br>0, CSNT = 1 write access TRLX = 0,1,<br>CSNT = 1, EBDF = 1 (MAX = 0.375 x<br>B1 + 6.6) | 10.90 | 18.00 | 10.90 | 18.00 | 7.00  | 14.30 | 5.20  | 12.30 | ns   |

## Table 9. Bus Operation Timings (continued)

|      |                                                                                                                                                                                                                             | 33    | MHz   | 40 1  | MHz   | 50 I  | MHz   | 66 MHz |       |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                                                                              | Min   | Max   | Min   | Max   | Min   | Max   | Min    | Max   | Unit |

| B28d | CLKOUT falling edge to $\overline{CS}$ negated<br>GPCM write access TRLX = 0,1,<br>CSNT = 1, ACS = 10, or ACS = 11,<br>EBDF = 1 (MAX = 0.375 x B1 + 6.6)                                                                    | _     | 18.00 |       | 18.00 |       | 14.30 | _      | 12.30 | ns   |

| B29  | $\overline{WE}$ (0:3) negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, CSNT = 0,<br>EBDF = 0 (MIN = 0.25 x B1 - 2.00)                                                                                               | 5.60  | _     | 4.30  | —     | 3.00  | —     | 1.80   | —     | ns   |

| B29a | $\overline{\text{WE}}(0:3)$ negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 0,<br>CSNT = 1, EBDF = 0 (MIN = 0.50 x B1<br>- 2.00)                                                                            | 13.20 |       | 10.50 | _     | 8.00  | _     | 5.60   | _     | ns   |

| B29b | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3), High<br>Z GPCM write access, ACS = 00,<br>TRLX = 0,1 & CSNT = 0 (MIN = 0.25 x<br>B1-2.00)                                                                               | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80   | _     | ns   |

| B29c | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT<br>= 1, ACS = 10, or ACS = 11, EBDF = 0<br>(MIN = 0.50 x B1 - 2.00)                                                          | 13.20 |       | 10.50 | _     | 8.00  | _     | 5.60   | _     | ns   |

| B29d | $\overline{\text{WE}}$ (0:3) negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 1,<br>CSNT = 1, EBDF = 0 (MIN = 1.50 x B1<br>- 2.00)                                                                           | 43.50 | _     | 35.50 | _     | 28.00 | _     | 20.70  | _     | ns   |

| B29e | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT<br>= 1, ACS = 10, or ACS = 11, EBDF = 0<br>(MIN = 1.50 x B1 - 2.00)                                                          | 43.50 | _     | 35.50 | _     | 28.00 | _     | 20.70  | _     | ns   |

| B29f | $\overline{\text{WE}}$ (0:3) negated to D(0:31), DP(0:3)<br>High Z GPCM write access, TRLX = 0,<br>CSNT = 1, EBDF = 1 (MIN = 0.375 x<br>B1 - 6.30)                                                                          | 5.00  | _     | 3.00  | _     | 1.10  | _     | 0.00   | _     | ns   |

| B29g | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT<br>= 1 ACS = 10 or ACS = 11, EBDF = 1<br>(MIN = 0.375 x B1 - 6.30)                                                           | 5.00  | _     | 3.00  | _     | 1.10  | _     | 0.00   | _     | ns   |

| B29h | $\overline{\text{WE}}(0:3)$ negated to D(0:31), DP(0:3)<br>High Z GPCM write access, TRLX = 1,<br>CSNT = 1, EBDF = 1 (MIN = 0.375 x<br>B1 - 3.30)                                                                           | 38.40 | _     | 31.10 | _     | 24.20 | _     | 17.50  | _     | ns   |

| B29i | $      \overline{\text{CS}} \text{ negated to D(0:31), DP(0:3) High-Z}       GPCM write access, TRLX = 1, CSNT       = 1, ACS = 10 or ACS = 11, EBDF = 1       (MIN = 0.375 x B1 - 3.30)                                  $ | 38.40 | _     | 31.10 | _     | 24.20 | _     | 17.50  | _     | ns   |

## Table 9. Bus Operation Timings (continued)

| Niumo | Okovertevistis                                                                                                                                                          | 33    | MHz   | 40    | MHz   | 50 I  | MHz   | 66   | MHz   | l l mit |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|-------|---------|

| Num   | Characteristic                                                                                                                                                          | Min   | Max   | Min   | Мах   | Min   | Max   | Min  | Мах   | Unit    |

| B31d  | CLKOUT falling edge to $\overline{CS}$ valid, as<br>requested by control bit CST1 in the<br>corresponding word in the UPM EBDF<br>= 1 (MAX = 0.375 x B1 + 6.6)          | 13.30 | 18.00 | 11.30 | 16.00 | 9.40  | 14.10 | 7.60 | 12.30 | ns      |

| B32   | CLKOUT falling edge to $\overline{BS}$ valid, as<br>requested by control bit BST4 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 6.00)                   | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50 | 6.00  | ns      |

| B32a  | CLKOUT falling edge to $\overline{\text{BS}}$ valid, as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF<br>= 0 (MAX = 0.25 x B1 + 6.80)  | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80 | 10.50 | ns      |

| B32b  | CLKOUT rising edge to $\overline{BS}$ valid, as<br>requested by control bit BST2 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 8.00)                    | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50 | 8.00  | ns      |

| B32c  | CLKOUT rising edge to $\overline{BS}$ valid, as<br>requested by control bit BST3 in the<br>corresponding word in the UPM (MAX<br>= 0.25 x B1 + 6.80)                    | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80 | 10.50 | ns      |

| B32d  | CLKOUT falling edge to $\overline{\text{BS}}$ valid- as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF<br>= 1 (MAX = 0.375 x B1 + 6.60) | 13.30 | 18.00 | 11.30 | 16.00 | 9.40  | 14.10 | 7.60 | 12.30 | ns      |

| B33   | CLKOUT falling edge to $\overline{\text{GPL}}$ valid, as<br>requested by control bit GxT4 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 6.00)           | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50 | 6.00  | ns      |

| B33a  | CLKOUT rising edge to $\overline{\text{GPL}}$ valid, as<br>requested by control bit GxT3 in the<br>corresponding word in the UPM (MAX<br>= 0.25 x B1 + 6.80)            | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80 | 10.50 | ns      |

| B34   | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid, as requested by control bit CST4 in the corresponding word in the UPM (MIN = 0.25 x B1 - 2.00)             | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80 | _     | ns      |

| B34a  | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{CS}$ valid, as requested by control bit<br>CST1 in the corresponding word in the<br>UPM (MIN = 0.50 x B1 - 2.00)    | 13.20 | _     | 10.50 | _     | 8.00  | _     | 5.60 | _     | ns      |

| B34b  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid, as requested by CST2 in the corresponding word in UPM (MIN = 0.75 x B1 - 2.00)                             | 20.70 | _     | 16.70 |       | 13.00 |       | 9.40 | _     | ns      |

## Table 9. Bus Operation Timings (continued)

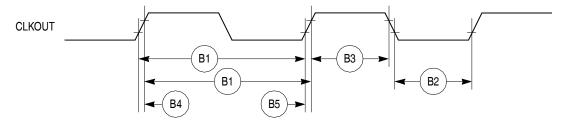

Figure 6 shows the timing for the external clock.

Figure 6. External Clock Timing

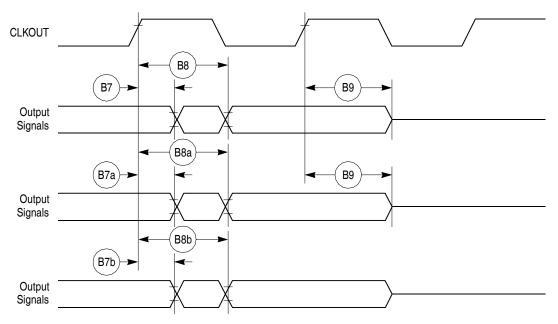

Figure 7 shows the timing for the synchronous output signals.

Figure 7. Synchronous Output Signals Timing

Figure 8 shows the timing for the synchronous active pull-up and open-drain output signals.

Figure 8. Synchronous Active Pull-Up Resistor and Open-Drain Output Signals Timing

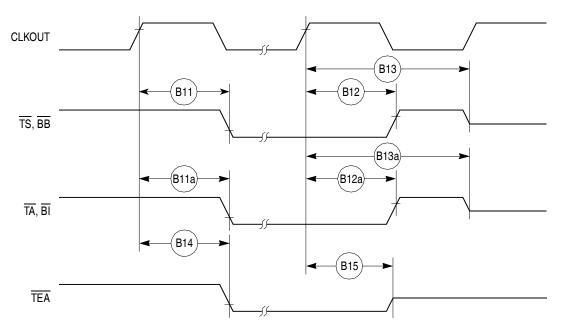

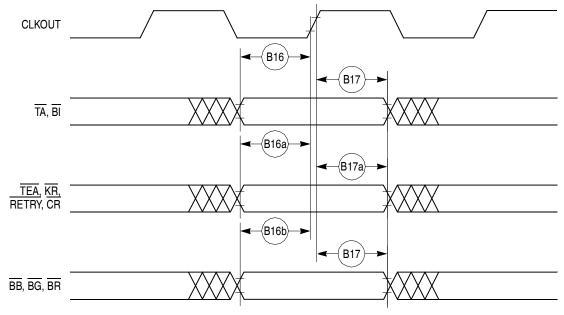

Figure 9 shows the timing for the synchronous input signals.

Figure 9. Synchronous Input Signals Timing

Figure 12 through Figure 15 show the timing for the external bus read controlled by various GPCM factors.

Figure 12. External Bus Read Timing (GPCM Controlled—ACS = 00)

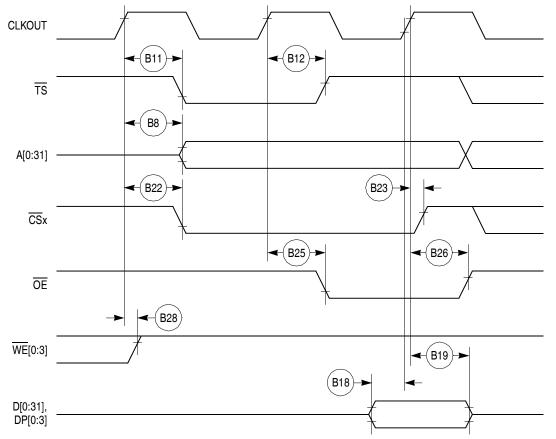

Figure 28. PCMCIA Access Cycles Timing External Bus Write

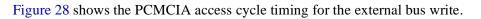

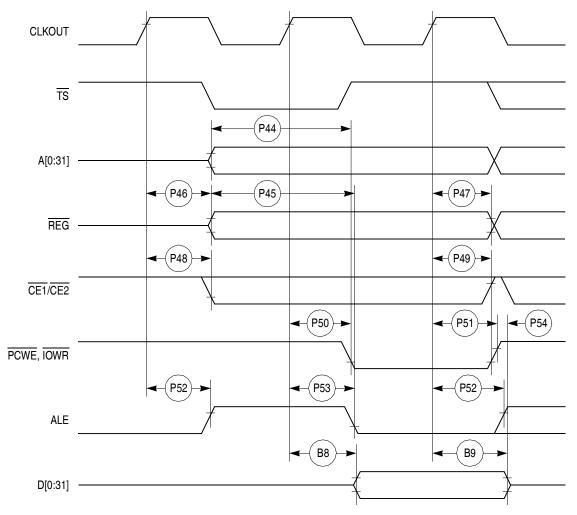

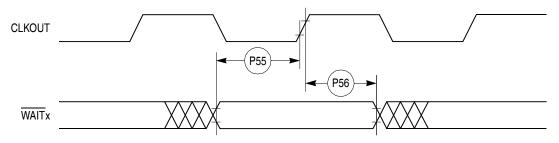

Figure 29 shows the PCMCIA WAIT signals detection timing.

Figure 29. PCMCIA WAIT Signals Detection Timing

MPC866/MPC859 Hardware Specifications, Rev. 2

**CPM Electrical Characteristics**

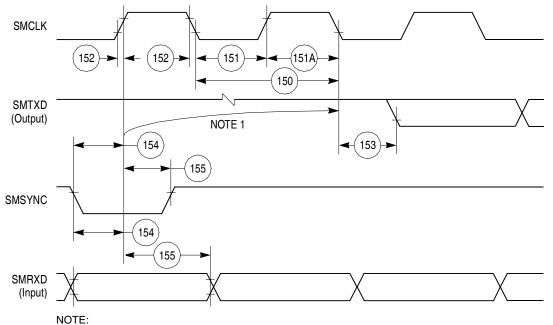

Figure 54. SI Receive Timing with Double-Speed Clocking (DSC = 1)

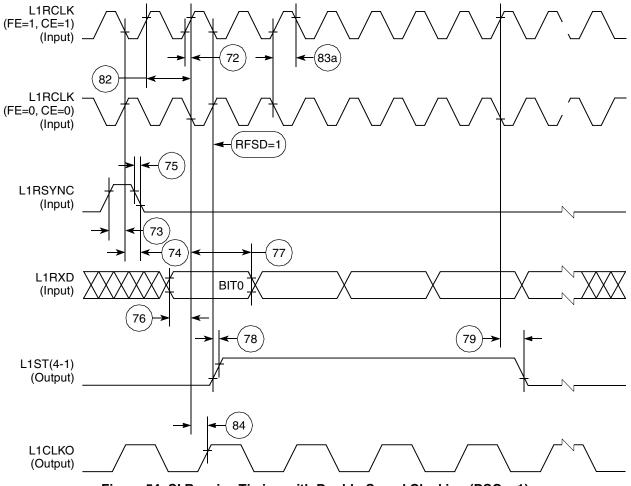

## 12.7 SCC in NMSI Mode Electrical Specifications

Table 22 shows the NMSI external clock timings.

| Num | Characteristic                                       | All Frequencie | Unit  |      |

|-----|------------------------------------------------------|----------------|-------|------|

| Num | Characteristic                                       | Min            | Max   | Unit |

| 100 | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK      | -     | ns   |

| 101 | RCLK1 and TCLK1 width low                            | 1/SYNCCLK +5   | —     | ns   |

| 102 | RCLK1 and TCLK1 rise/fall time                       | _              | 15.00 | ns   |

| 103 | TXD1 active delay (from TCLK1 falling edge)          | 0.00           | 50.00 | ns   |

| 104 | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00           | 50.00 | ns   |

| 105 | CTS1 setup time to TCLK1 rising edge                 | 5.00           | _     | ns   |

| 106 | RXD1 setup time to RCLK1 rising edge                 | 5.00           | —     | ns   |

| 107 | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00           | _     | ns   |

| 108 | CD1 setup time to RCLK1 rising edge                  | 5.00           | —     | ns   |

### Table 22. NMSI External Clock Timings

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

Table 23 shows the NMSI internal clock timings.

### Table 23. NMSI Internal Clock Timings

| Num   | Characteristic                                       | All Fr | Unit      |      |

|-------|------------------------------------------------------|--------|-----------|------|

| Nulli | Characteristic                                       | Min    | Max       | Onit |

| 100   | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00   | SYNCCLK/3 | MHz  |

| 102   | RCLK1 and TCLK1 rise/fall time                       |        | —         | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00   | 30.00     | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00   | 30.00     | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 40.00  | _         | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 40.00  | _         | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00   | _         | ns   |

| 108   | CD1 setup time to RCLK1 rising edge                  | 40.00  | _         | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

Figure 60. HDLC Bus Timing Diagram

## **12.8 Ethernet Electrical Specifications**

Table 24 shows the Ethernet timings as shown in Figure 61 through Figure 65.Table 24. Ethernet Timing

| Num | Characteristic                                                  | All Freq | uencies | Unit |

|-----|-----------------------------------------------------------------|----------|---------|------|

| Num | Characteristic                                                  | Min      | Max     | Unit |

| 120 | CLSN width high                                                 | 40       |         | ns   |

| 121 | RCLK1 rise/fall time                                            | _        | 15      | ns   |

| 122 | RCLK1 width low                                                 | 40       | _       | ns   |

| 123 | RCLK1 clock period <sup>1</sup>                                 | 80       | 120     | ns   |

| 124 | RXD1 setup time                                                 | 20       | _       | ns   |

| 125 | RXD1 hold time                                                  | 5        | _       | ns   |

| 126 | RENA active delay (from RCLK1 rising edge of the last data bit) | 10       | _       | ns   |

| 127 | RENA width low                                                  | 100      | _       | ns   |

| 128 | TCLK1 rise/fall time                                            | _        | 15      | ns   |

| 129 | TCLK1 width low                                                 | 40       | _       | ns   |

| 130 | TCLK1 clock period <sup>1</sup>                                 | 99       | 101     | ns   |

| 131 | TXD1 active delay (from TCLK1 rising edge)                      | —        | 50      | ns   |

| 132 | TXD1 inactive delay (from TCLK1 rising edge)                    | 6.5      | 50      | ns   |

| 133 | TENA active delay (from TCLK1 rising edge)                      | 10       | 50      | ns   |

MPC866/MPC859 Hardware Specifications, Rev. 2

### **CPM Electrical Characteristics**

| Num                 | Characteristic                               | All Freq | uencies | Unit |

|---------------------|----------------------------------------------|----------|---------|------|

| Nulli               | Characteristic                               | Min      | Мах     | Unit |

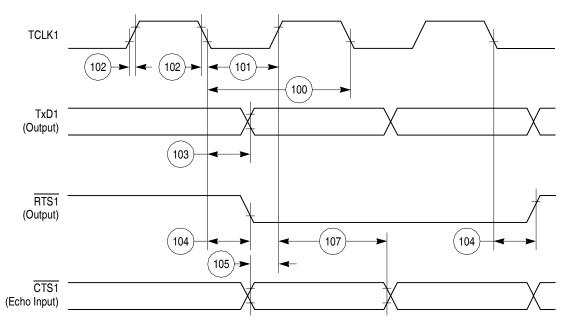

| 150                 | SMCLK clock period <sup>1</sup>              | 100      | _       | ns   |

| 151                 | SMCLK width low                              | 50       | _       | ns   |

| 151A                | SMCLK width high                             | 50       | _       | ns   |

| 152                 | SMCLK rise/fall time                         | —        | 15      | ns   |

| 153                 | SMTXD active delay (from SMCLK falling edge) | 10       | 50      | ns   |

| 154                 | SMRXD/SMSYNC setup time                      | 20       | —       | ns   |

| 155                 | RXD1/SMSYNC hold time                        | 5        | _       | ns   |

| <sup>1</sup> Svnc ( | CLK must be at least twice as fast as SMCLK. | •        |         | •    |

### Table 25. SMC Transparent Timing

Sync CLK must be at least twice as fast as SMCLK.

1. This delay is equal to an integer number of character-length clocks.

### Figure 66. SMC Transparent Timing Diagram

### **CPM Electrical Characteristics**

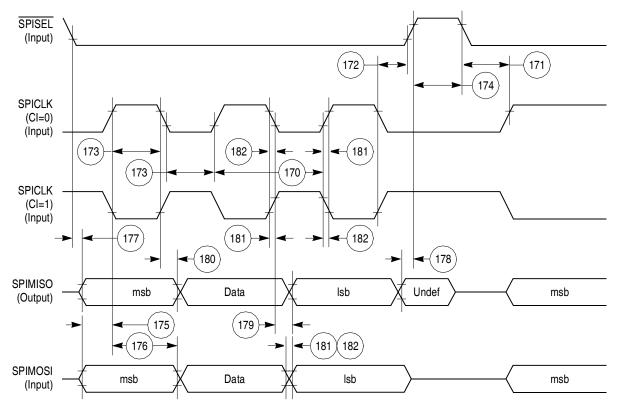

Figure 69. SPI Slave (CP = 0) Timing Diagram

Table 28 shows the  $I^2C$  (SCL < 100 kHz) timings.

Table 28. I<sup>2</sup>C Timing (SCL < 100 kHz)

| Num | Characteristic                            | All Freq | uencies | Unit |

|-----|-------------------------------------------|----------|---------|------|

| Num | Characteristic                            | Min      | Max     | Unit |

| 200 | SCL clock frequency (slave)               | 0        | 100     | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100     | kHz  |

| 202 | Bus free time between transmissions       | 4.7      |         | μs   |

| 203 | Low period of SCL                         | 4.7      | _       | μs   |

| 204 | High period of SCL                        | 4.0      | _       | μs   |

| 205 | Start condition setup time                | 4.7      |         | μs   |

| 206 | Start condition hold time                 | 4.0      | _       | μs   |

| 207 | Data hold time                            | 0        | _       | μs   |

| 208 | Data setup time                           | 250      | _       | ns   |

| 209 | SDL/SCL rise time                         | —        | 1       | μs   |

| 210 | SDL/SCL fall time                         | —        | 300     | ns   |

| 211 | Stop condition setup time                 | 4.7      | —       | μs   |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

## Table 29 shows the $I^2C$ (SCL > 100 kHz) timings.

Table 29.  $I^2C$  Timing (SCL > 100 kHz)

| Num | Characteristic                            | Expression | All Freq        | Unit          |      |

|-----|-------------------------------------------|------------|-----------------|---------------|------|

| num | Characteristic                            | Expression | Min             | Мах           | Unit |

| 200 | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz   |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz   |

| 202 | Bus free time between transmissions       | _          | 1/(2.2 * fSCL)  | _             | s    |

| 203 | Low period of SCL                         | _          | 1/(2.2 * fSCL)  | _             | s    |

| 204 | High period of SCL                        | —          | 1/(2.2 * fSCL)  | _             | s    |

| 205 | Start condition setup time                | —          | 1/(2.2 * fSCL)  | _             | s    |

| 206 | Start condition hold time                 | —          | 1/(2.2 * fSCL)  | _             | s    |

| 207 | Data hold time                            | —          | 0               | _             | s    |

| 208 | Data setup time                           | —          | 1/(40 * fSCL)   | _             | s    |

| 209 | SDL/SCL rise time                         | —          | —               | 1/(10 * fSCL) | s    |

| 210 | SDL/SCL fall time                         | —          | —               | 1/(33 * fSCL) | s    |

| 211 | Stop condition setup time                 | —          | 1/2(2.2 * fSCL) |               | s    |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

Mechanical Data and Ordering Information

# **15 Mechanical Data and Ordering Information**

Table 37 shows information on the MPC866/859 derivative devices.

Table 37. MPC866/859 Derivatives

| Device    | Number<br>of      | Ethernet    | Multi-Channel | ATM Support       | Cache Size  |          |  |  |  |

|-----------|-------------------|-------------|---------------|-------------------|-------------|----------|--|--|--|

| Device    | SCCs <sup>1</sup> | Support     | HDLC Support  |                   | Instruction | Data     |  |  |  |

| MPC866T   | 4                 | 10/100 Mbps | Yes           | Yes               | 4 Kbyte     | 4 Kbytes |  |  |  |

| MPC866P   | 4                 | 10/100 Mbps | Yes           | Yes               | 16 Kbyte    | 8 Kbytes |  |  |  |

| MPC859T   | 1 (SCC1)          | 10/100 Mbps | Yes           | Yes               | 4 Kbyte     | 4 Kbytes |  |  |  |

| MPC859DSL | 1 (SCC1)          | 10/100 Mbps | No            | Up to 4 addresses | 4 Kbyte     | 4 Kbytes |  |  |  |

<sup>1</sup> Serial communications controller (SCC).

Table 38 identifies the packages and operating frequencies orderable for the MPC866/859 derivative devices.

Table 38. MPC866/859 Package/Frequency Orderable

| Package Type                  | Temperature (Tj) | Frequency (MHz) | Order Number                                                         |  |  |  |  |

|-------------------------------|------------------|-----------------|----------------------------------------------------------------------|--|--|--|--|

| Plastic ball grid array       | 0° to 95°C       | 50              | MPC859DSLZP50A                                                       |  |  |  |  |

| (ZP suffix)<br>Non lead free  |                  | 66              | MPC859DSLZP66A                                                       |  |  |  |  |

|                               |                  | 100             | MPC859PZP100A<br>MPC859TZP100A<br>MPC866PZP100A<br>MPC866TZP100A     |  |  |  |  |

|                               |                  | 133             | MPC859PZP133A<br>MPC859TZP133A<br>MPC866PZP133A<br>MPC866TZP133A     |  |  |  |  |

| Plastic ball grid array       | –40° to 100°C    | 50              | MPC859DSLCZP50A                                                      |  |  |  |  |

| (CZP suffix)<br>Non lead free |                  | 66              | MPC859DSLCZP66A                                                      |  |  |  |  |

|                               |                  | 100             | MPC859PCZP100A<br>MPC859TCZP100A<br>MPC866PCZP100A<br>MPC866TCZP100A |  |  |  |  |

Mechanical Data and Ordering Information

## **15.1 Pin Assignments**

Figure 78 shows the top view pinout of the PBGA package. For additional information, see the *MPC866 PowerQUICC Family User's Manual*.

| <i>(</i>  |           |           |           |            |                        |            |            |            |            |            |            |            |                   |            |                        |              |               |              |        |

|-----------|-----------|-----------|-----------|------------|------------------------|------------|------------|------------|------------|------------|------------|------------|-------------------|------------|------------------------|--------------|---------------|--------------|--------|

|           | O<br>PD10 | O<br>PD8  | O<br>PD3  |            |                        | O<br>D4    | ()<br>D1   | ()<br>D2   | )<br>D3    | ()<br>D5   |            | ()<br>D6   | ()<br>D7          | )<br>D29   | O<br>DP2               |              |               |              | w      |

| O<br>PD14 | O<br>PD13 | O<br>PD9  | O<br>PD6  | O<br>M_Tx_ |                        | 0<br>5 D13 | ()<br>D27  | )<br>D10   | ()<br>D14  | )<br>D18   | 〇<br>D20   | 〇<br>D24   | )<br>D28          | O<br>DP1   | O<br>DP3               | O<br>DP0     | )<br>N/C \    |              | v<br>1 |

| O<br>PA0  | O<br>PB14 | O<br>PD15 | O<br>PD4  | O<br>PD5   |                        | ()<br>D8   | ()<br>D23  | 〇<br>D11   | 〇<br>D16   | )<br>D19   | 〇<br>D21   | 〇<br>D26   | )<br>D30          | O<br>IPA5  | O<br>IPA4              | O<br>IPA2    | ⊖<br>N/C      |              | U      |

| O<br>PA1  | O<br>PC5  | O<br>PC4  | O<br>PD11 | O<br>PD7   |                        | )<br>H D12 | ()<br>D17  | O<br>D9    | ()<br>D15  | )<br>D22   | )<br>D25   | )<br>D31   | O<br>IPA6         |            | O<br>IPA1              | O<br>IPA7    | ⊖<br>N/C      |              | T      |

| O<br>PC6  | 0<br>PA2  | ⊖<br>₽B15 | O<br>PD12 | 0          |                        | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0                 | O<br>VDDH  |                        |              |               |              | R      |

| O<br>PA4  | O<br>PB17 | O<br>PA3  |           | $\bigcirc$ | $\left( \circ \right)$ | )<br>GND   | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | GND               | 0          |                        |              |               | C<br>ET XTAL | Ρ      |

| O<br>PB19 | O<br>PA5  | )<br>PB18 | O<br>PB16 | $\bigcirc$ | 0                      | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$        | 0          |                        |              |               |              | Ν      |

| O<br>PA7  | 0<br>PC8  | )<br>PA6  | O<br>PC7  | $\bigcirc$ | 0                      | $\bigcirc$        | $\bigcirc$ |                        | BADDR28      |               | O<br>R29 VDD | M      |

| O<br>PB22 | O<br>PC9  | )<br>PA8  | O<br>PB20 | $\bigcirc$ | 0                      | $\bigcirc$        | 0          | О<br>ОР0               |              | O<br>OP1      |              | L      |

| O<br>PC10 | 0<br>PA9  | O<br>PB23 | O<br>PB21 | $\bigcirc$ | 0                      | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | )<br>GND   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$        | 0          |                        | 0<br>30 IPB6 |               |              | к      |

| O<br>PC11 | O<br>PB24 | )<br>PA10 | O<br>PB25 | $\bigcirc$ | 0                      | $\bigcirc$        | 0          | O<br>IPB5              | O<br>IPB1    | O<br>IPB2     | O            | J      |

|           |           |           | О<br>тск  | $\bigcirc$ | 0                      | $\bigcirc$ | 0                 | 0          | O<br>M_COL             |              | O<br>IPB0     | O<br>IPB7    | н      |

|           | О<br>тмs  | O<br>TDO  | O<br>PA11 | $\bigcirc$ | 0                      | GND        | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | O<br>GND          | $\bigcirc$ |                        |              | O<br>IPB4     | O<br>IPB3    | G      |

| O<br>PB26 | O<br>PC12 | )<br>PA12 |           | $\bigcirc$ |                        |            | 0          | 0          | 0          | 0          | 0          | 0          |                   |            |                        | ⊖<br>⊤s      |               |              | F      |

| O<br>PB27 | O<br>PC13 | )<br>PA13 | O<br>PB29 | $\bigcirc$ | 0                      | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0                 | 0          | $\bigcirc$<br>CS3      | O<br>BI      | $\bigcirc$ BG |              | Е      |

| O<br>PB28 | O<br>PC14 | O<br>PA14 | O<br>PC15 | ()<br>A8   | O<br>N/C               | ⊖<br>N/C   | ()<br>A15  | ()<br>A19  | ()<br>A25  | ()<br>A18  |            |            | ⊖<br>N/C          |            | $\bigcirc$<br>CS2      |              |               |              | D      |

| O<br>PB30 | O<br>PA15 | O<br>PB31 | ()<br>A3  | ()<br>A9   | ()<br>A12              | ()<br>A16  | ()<br>A20  | )<br>A24   | ()<br>A26  |            |            |            |                   |            | $\frac{\bigcirc}{CS7}$ |              | ⊖<br>TA       |              | С      |

| ()<br>A0  | ()<br>A1  | ()<br>A4  | ()<br>A6  | ()<br>A10  | ()<br>A13              | ()<br>A17  | ()<br>A21  | ()<br>A23  | ()<br>A22  | O<br>TSIZO |            | O<br>M_CRS | $\bigcirc$<br>WE2 |            | $\frac{\bigcirc}{CS5}$ |              |               |              | В      |

|           | ()<br>A2  | ()<br>A5  | ()<br>A7  | ()<br>A11  | ()<br>A14              | ()<br>A27  | ()<br>A29  | )<br>A30   | ()<br>A28  | )<br>A31   |            | BSA2       |                   |            |                        |              |               |              | A      |

| 19        | 18        | 17        | 16        | 15         | 14                     | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6                 | 5          | 4                      | 3            | 2             | 1            |        |

NOTE: This is the top view of the device.

Figure 78. Pinout of the PBGA Package

# **16 Document Revision History**

Table 40 lists significant changes between revisions of this document.

### Table 40. Document Revision History

| Revision<br>Number | Date      | Substantive Changes                                                                                                                                                         |

|--------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | 5/2002    | Initial revision                                                                                                                                                            |

| 1                  | 11/2002   | Added the 5-V tolerant pins, new package dimensions, and other changes.                                                                                                     |

| 1.1                | 4/2003    | Added the Spec. B1d and changed spec. B1a. Added the Note Solder sphere composition for MPC866XZP, MPC859DSLZP, and MPC859TZP is 62%Sn 36%Pb 2%Ag to Figure 15-79.          |

| 1.2                | 4/2003    | Added the MPC859P.                                                                                                                                                          |

| 1.3                | 5/2003    | Changed the SPI Master Timing Specs. 162 and 164.                                                                                                                           |

| 1.4                | 7-8/2003  | <ul> <li>Added TxClav and RxClav to PB15 and PC15. Changed B28a through B28d and B29b to show that TRLX can be 0 or 1.</li> <li>Added nontechnical reformatting.</li> </ul> |

| 1.5                | 3/14/2005 | Updated document template.                                                                                                                                                  |

| 2                  | 2/10/2006 | Updated orderable parts table.                                                                                                                                              |