#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XE

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Active                                                      |

| Core Processor                  | MPC8xx                                                      |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 50MHz                                                       |

| Co-Processors/DSP               | Communications; CPM                                         |

| RAM Controllers                 | DRAM                                                        |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                  |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 3.3V                                                        |

| Operating Temperature           | 0°C ~ 95°C (TA)                                             |

| Security Features               | -                                                           |

| Package / Case                  | 357-BBGA                                                    |

| Supplier Device Package         | 357-PBGA (25x25)                                            |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc859dslzp50a |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- ATM port-to-port switching capability without the need for RAM-based microcode

- Simultaneous MII (10/100Base-T) and UTOPIA (half-duplex) capability

- Optional statistical cell counters per PHY

- UTOPIA level 2 compliant interface with added FIFO buffering to reduce the total cell transmission time. (The earlier UTOPIA level 1 specification is also supported.)

- Multi-PHY support on the MPC866, MPC859P, and MPC859T

- Four PHY support on the MPC866/859

- Parameter RAM for both SPI and I<sup>2</sup>C can be relocated without RAM-based microcode

- Supports full-duplex UTOPIA both master (ATM side) and slave (PHY side) operation using a 'split' bus

- AAL2/VBR functionality is ROM-resident.

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- Thirty-two address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to page mode/EDO/SDRAM, SRAM, EPROMs, flash EPROMs, and other memory devices.

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes–256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers cascadable to be two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Fast Ethernet controller (FEC)

- Simultaneous MII (10/100Base-T) and UTOPIA operation when using the UTOPIA multiplexed bus

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer and time base from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

#### Features

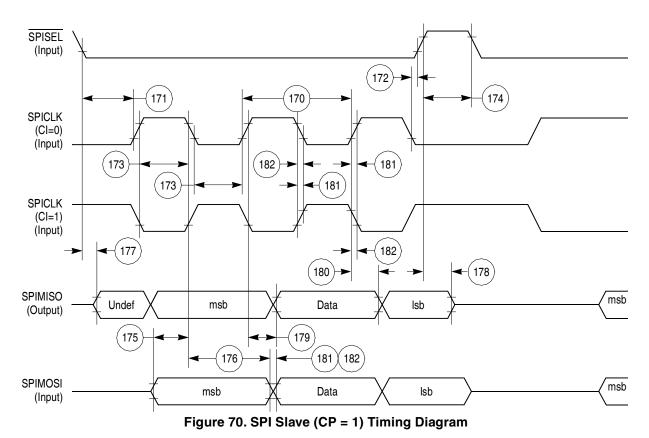

- One serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multiple-master operation on the same bus

- One inter-integrated circuit (I<sup>2</sup>C) port

- Supports master and slave modes

- Multiple-master environment support

- Time slot assigner (TSA) (MPC859DSL does not have TSA.)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

- Allows dynamic changes

- On MPC866P and MPC866T, can be internally connected to six serial channels (four SCCs and two SMCs); on MPC859P and MPC859T, can be connected to three serial channels (one SCC and two SMCs).

- Parallel interface port (PIP)

- Centronics interface support

- Supports fast connection between compatible ports on MPC866/859 or MC68360

- PCMCIA interface

- Master (socket) interface, compliant with PCI Local Bus Specification (Rev 2.1)

- Supports one or two PCMCIA sockets whether ESAR functionality is enabled

- Eight memory or I/O windows supported

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two operate on data.

- Supports conditions:  $= \neq < >$

- Each watchpoint can generate a breakpoint internally

- Normal high and normal low power modes to conserve power

- 1.8 V core and 3.3 V I/O operation with 5-V TTL compatibility; refer to Table 6 for a listing of the 5-V tolerant pins.

- 357-pin plastic ball grid array (PBGA) package

- Operation up to 133 MHz

| Characteristic                                                                                                                                                                                               | Symbol          | Min        | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|------|------|

| Input low voltage                                                                                                                                                                                            | VIL             | GND        | 0.8  | V    |

| EXTAL, EXTCLK input high voltage                                                                                                                                                                             | VIHC            | 0.7*(VDDH) | VDDH | V    |

| Input leakage current, Vin = 5.5V (except TMS, $\overline{\text{TRST}}$ , DSCK and DSDI pins) for 5 Volts Tolerant Pins <sup>2</sup>                                                                         | l <sub>in</sub> | —          | 100  | μA   |

| Input leakage current, Vin = VDDH (except TMS, TRST, DSCK, and DSDI)                                                                                                                                         | l <sub>in</sub> | _          | 10   | μA   |

| Input leakage current, Vin = 0 V (except TMS, $\overline{\text{TRST}}$ , DSCK and DSDI pins)                                                                                                                 | l <sub>in</sub> | —          | 10   | μA   |

| Input capacitance <sup>3</sup>                                                                                                                                                                               | C <sub>in</sub> | —          | 20   | pF   |

| Output high voltage, IOH = $-2.0$ mA,<br>except XTAL, and Open drain pins                                                                                                                                    | VOH             | 2.4        | _    | V    |

| Output low voltage<br>• IOL = 2.0 mA (CLKOUT)<br>• IOL = 3.2 mA <sup>4</sup><br>• IOL = 5.3 mA <sup>5</sup><br>• IOL = 7.0 mA (TXD1/PA14, TXD2/PA12)<br>• IOL = 8.9 mA (TS, TA, TEA, BI, BB, HRESET, SRESET) | VOL             | _          | 0.5  | V    |

#### Table 6. DC Electrical Specifications (continued)

<sup>1</sup> The difference between VDDL and VDDSYN can not be more than 100 m V.

<sup>2</sup> The signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], TDI, TDO, TCK, TRST\_B, TMS, MII\_TXEN, MII\_MDIO are 5 V tolerant.

<sup>3</sup> Input capacitance is periodically sampled.

<sup>4</sup> A(0:31), TSIZ0/REG, TSIZ1, D(0:31), DP(0:3)/IRQ(3:6), RD/WR, BURST, RSV/IRQ2, IP\_B(0:1)/IWP(0:1)/VFLS(0:1), IP\_B2/IOIS16\_B/AT2, IP\_B3/IWP2/VF2, IP\_B4/LWP0/VF0, IP\_B5/LWP1/VF1, IP\_B6/DSDI/AT0, IP\_B7/PTR/AT3, RXD1 /PA15, RXD2/PA13, L1TXDB/PA11, L1RXDB/PA10, L1TXDA/PA9, L1RXDA/PA8, TIN1/L1RCLKA/BRGO1/CLK1/PA7, BRGCLK1/TOUT1/CLK2/PA6, TIN2/L1TCLKA/BRGO2/CLK3/PA5, TOUT2/CLK4/PA4, TIN3/BRGO3/CLK5/PA3, BRGCLK2/L1RCLKB/TOUT3/CLK6/PA2, TIN4/BRGO4/CLK7/PA1, L1TCLKB/TOUT4/CLK8/PA0, REJCT1/SPISEL/PB31, SPICLK/PB30, SPIMOSI/PB29, BRGO4/SPIMISO/PB28, BRGO1/I2CSDA/PB27, BRGO2/I2CSCL/PB26, SMTXD1/PB25, SMRXD1/PB24, SMSYN1/SDACK1/PB23, SMSYN2/SDACK2/PB22, SMTXD2/L1CLKOB/PB21, SMRXD2/L1CLKOA/PB20, L1ST1/RTS1/PB19, L1ST2/RTS2/PB18, L1ST3/L1RQB/PB17, L1ST4/L1RQA/PB16, BRGO3/PB15, RSTRT1/PB14, L1ST1/RTS1/DREQ0/PC15, L1ST2/RTS2/DREQ1/PC14, L1ST3/L1RQB/PC13, L1ST4/L1RQA/PC12, CTS1/PC11, TGATE1/CD1/PC10, CTS2/PC9, TGATE2/CD2/PC8, CTS3/SDACK2/L1TSYNCB/PC7, CD3/L1RSYNCB/PC6, CTS4/SDACK1/L1TSYNCA/PC5, CD4/L1RSYNCA/PC4, PD15/L1TSYNCA, PD14/L1RSYNCA, PD13/L1TSYNCB, PD12/L1RSYNCB, PD11/RXD3, PD10/TXD3, PD9/RXD4, PD8/TXD4, PD5/REJECT2, PD6/RTS4, PD7/RTS3, PD4/REJECT3, PD3, MII\_MDC, MII\_TX\_ER, MII\_EN, MII\_MDIO, MII\_TXD[0:3].

<sup>5</sup> BDIP/GPL\_B(5), BR, BG, FRZ/IRQ6, CS(0:5), CS(6)/CE(1)\_B, CS(7)/CE(2)\_B, WE0/BS\_B0/IORD, WE1/BS\_B1/IOWR, WE2/BS\_B2/PCOE, WE3/BS\_B3/PCWE, BS\_A(0:3), GPL\_A0/GPL\_B0, OE/GPL\_A1/GPL\_B1, GPL\_A(2:3)/GPL\_B(2:3)/CS(2:3), UPWAITA/GPL\_A4, UPWAITB/GPL\_B4, GPL\_A5, ALE\_A, CE1\_A, CE2\_A, ALE\_B/DSCK/AT1, OP(0:1), OP2/MODCK1/STS, OP3/MODCK2/DSDO, BADDR(28:30).

This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of 6" are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{DD}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins. For more information, please refer to Section 14.4.3, Clock Synthesizer Power (VDDSYN, VSSSYN, VSSSYN1), in the *MPC866 User's Manual*.

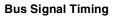

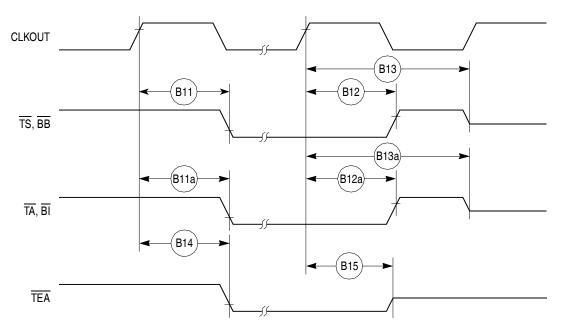

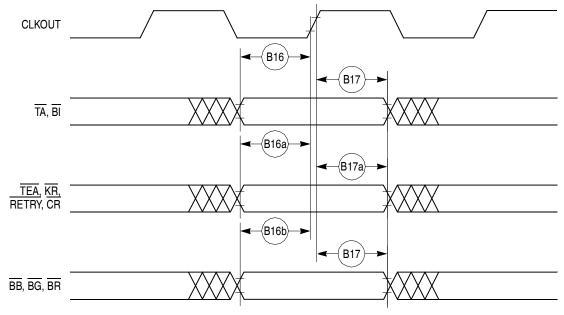

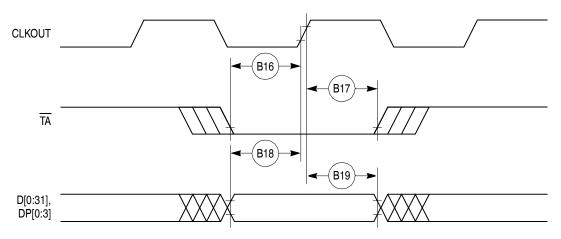

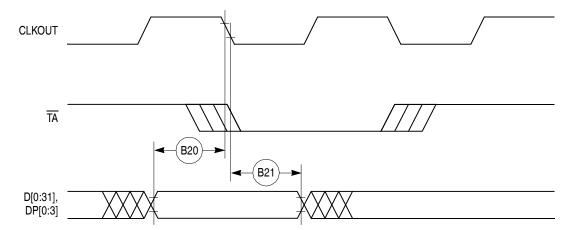

# 10 Bus Signal Timing

The maximum bus speed supported by the MPC866/859 is 66 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC866/859 used at 100 MHz must be configured for a 50-MHz bus). Table 7 and Table 8 show the frequency ranges for standard part frequencies.

Table 7. Frequency Ranges for Standard Part Frequencies (1:1 Bus Mode)

| Part Freq | 50 M | ИНz | 66 MHz |       |  |  |

|-----------|------|-----|--------|-------|--|--|

|           | Min  | Мах | Min    | Мах   |  |  |

| Core      | 40   | 50  | 40     | 66.67 |  |  |

| Bus       | 40   | 50  | 40     | 66.67 |  |  |

Table 8. Frequency Ranges for Standard Part Frequencies (2:1 Bus Mode)

| Part<br>Freq | 50 I | MHz | 66 MHz |       | 6 MHz 100 MHz |     | 66 MHz 100 MHz 133 MHz |        | MHz |

|--------------|------|-----|--------|-------|---------------|-----|------------------------|--------|-----|

|              | Min  | Мах | Min    | Мах   | Min           | Max | Min                    | Max    |     |

| Core         | 40   | 50  | 40     | 66.67 | 40            | 100 | 40                     | 133.34 |     |

| Bus          | 20   | 25  | 20     | 33.33 | 20            | 50  | 20                     | 66.67  |     |

Table 9 shows the timings for the MPC866/859 at 33, 40, 50, and 66 MHz bus operation. The timing for the MPC866/859 bus shown in this table assumes a 50-pF load for maximum delays and a 0-pF load for minimum delays. CLKOUT assumes a 100-pF load maximum delay.

Table 9. Bus Operation Timings

| Num | Characteristic                       | 33 MHz |      | 40 MHz |      | 50 MHz |      | 66 MHz |      | Unit |

|-----|--------------------------------------|--------|------|--------|------|--------|------|--------|------|------|

|     | Characteristic                       | Min    | Max  | Min    | Мах  | Min    | Max  | Min    | Max  | onn  |

| B1  | Bus Period (CLKOUT) See Table 7      |        | _    |        | —    | —      | —    |        | —    | ns   |

| B1a | EXTCLK to CLKOUT phase skew          | - 2    | +2   | - 2    | +2   | - 2    | +2   | - 2    | +2   | ns   |

| B1b | CLKOUT frequency jitter peak-to-peak |        | 1    |        | 1    | —      | 1    | _      | 1    | ns   |

| B1c | Frequency jitter on EXTCLK           |        | 0.50 |        | 0.50 | —      | 0.50 |        | 0.50 | %    |

| Niumo | Okovertevistis                                                                                                                                                          | 33    | MHz   | 40    | MHz   | 50 I  | MHz   | 66 MHz |       | l l mit |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|---------|

| Num   | Characteristic                                                                                                                                                          | Min   | Max   | Min   | Мах   | Min   | Max   | Min    | Мах   | Unit    |

| B31d  | CLKOUT falling edge to $\overline{CS}$ valid, as<br>requested by control bit CST1 in the<br>corresponding word in the UPM EBDF<br>= 1 (MAX = 0.375 x B1 + 6.6)          | 13.30 | 18.00 | 11.30 | 16.00 | 9.40  | 14.10 | 7.60   | 12.30 | ns      |

| B32   | CLKOUT falling edge to $\overline{BS}$ valid, as<br>requested by control bit BST4 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 6.00)                   | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50   | 6.00  | ns      |

| B32a  | CLKOUT falling edge to $\overline{\text{BS}}$ valid, as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF<br>= 0 (MAX = 0.25 x B1 + 6.80)  | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80   | 10.50 | ns      |

| B32b  | CLKOUT rising edge to $\overline{BS}$ valid, as<br>requested by control bit BST2 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 8.00)                    | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50   | 8.00  | ns      |

| B32c  | CLKOUT rising edge to $\overline{BS}$ valid, as<br>requested by control bit BST3 in the<br>corresponding word in the UPM (MAX<br>= 0.25 x B1 + 6.80)                    | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80   | 10.50 | ns      |

| B32d  | CLKOUT falling edge to $\overline{\text{BS}}$ valid- as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF<br>= 1 (MAX = 0.375 x B1 + 6.60) | 13.30 | 18.00 | 11.30 | 16.00 | 9.40  | 14.10 | 7.60   | 12.30 | ns      |

| B33   | CLKOUT falling edge to $\overline{\text{GPL}}$ valid, as<br>requested by control bit GxT4 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 6.00)           | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50   | 6.00  | ns      |

| B33a  | CLKOUT rising edge to $\overline{\text{GPL}}$ valid, as<br>requested by control bit GxT3 in the<br>corresponding word in the UPM (MAX<br>= 0.25 x B1 + 6.80)            | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80   | 10.50 | ns      |

| B34   | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid, as requested by control bit CST4 in the corresponding word in the UPM (MIN = 0.25 x B1 - 2.00)             | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80   | _     | ns      |

| B34a  | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{CS}$ valid, as requested by control bit<br>CST1 in the corresponding word in the<br>UPM (MIN = 0.50 x B1 - 2.00)    | 13.20 | _     | 10.50 | _     | 8.00  | _     | 5.60   | _     | ns      |

| B34b  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid, as requested by CST2 in the corresponding word in UPM (MIN = 0.75 x B1 - 2.00)                             | 20.70 | _     | 16.70 |       | 13.00 |       | 9.40   | _     | ns      |

# Table 9. Bus Operation Timings (continued)

Figure 6 shows the timing for the external clock.

Figure 6. External Clock Timing

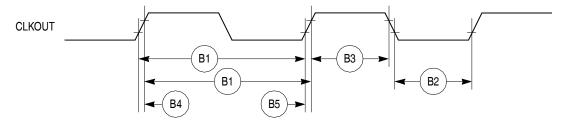

Figure 7 shows the timing for the synchronous output signals.

Figure 7. Synchronous Output Signals Timing

Figure 8 shows the timing for the synchronous active pull-up and open-drain output signals.

Figure 8. Synchronous Active Pull-Up Resistor and Open-Drain Output Signals Timing

Figure 9 shows the timing for the synchronous input signals.

Figure 9. Synchronous Input Signals Timing

Figure 10 shows normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 10. Input Data Timing in Normal Case

Figure 11 shows the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Figure 11. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

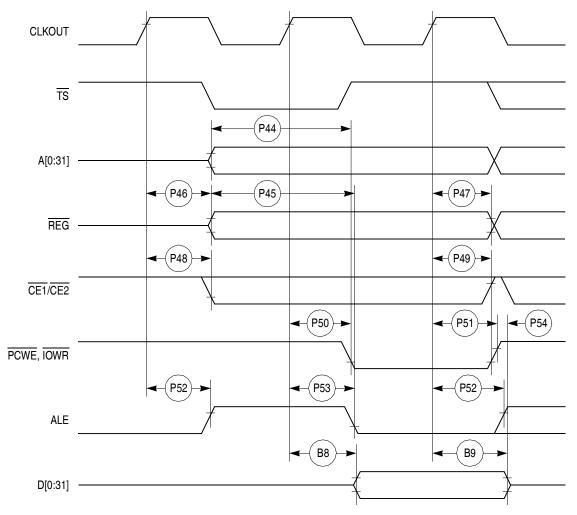

Figure 16 through Figure 18 show the timing for the external bus write controlled by various GPCM factors.

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

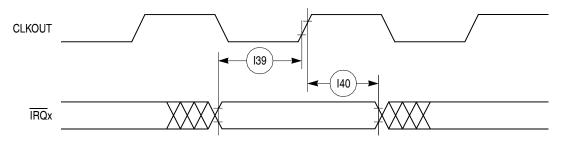

Figure 25 shows the interrupt detection timing for the external level-sensitive lines.

Figure 25. Interrupt Detection Timing for External Level Sensitive Lines

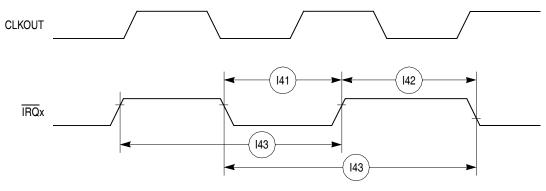

Figure 26 shows the interrupt detection timing for the external edge-sensitive lines.

Figure 26. Interrupt Detection Timing for External Edge Sensitive Lines

Table 11 shows the PCMCIA timing for the MPC866/859.

Table 11. PCMCIA Timing

| Num | Characteristic                                                                                               | 33 I  | ИНz   | 40 1  | MHz   | 50 I  | ЛНz   | 66 MHz |       | Unit |

|-----|--------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num | onardotenstie                                                                                                | Min   | Мах   | Min   | Max   | Min   | Мах   | Min    | Max   | Onit |

| P44 | A(0:31), $\overline{\text{REG}}$ valid to PCMCIA<br>Strobe asserted <sup>1</sup> (MIN = 0.75 x B1<br>- 2.00) | 20.70 | _     | 16.70 | _     | 13.00 | _     | 9.40   | _     | ns   |

| P45 | A(0:31), $\overline{\text{REG}}$ valid to ALE<br>negation <sup>1</sup> (MIN = 1.00 x B1 - 2.00)              | 28.30 | _     | 23.00 | _     | 18.00 |       | 13.20  | _     | ns   |

| P46 | CLKOUT to $\overline{\text{REG}}$ valid (MAX = 0.25 x B1 + 8.00)                                             | 7.60  | 15.60 | 6.30  | 14.30 | 5.00  | 13.00 | 3.80   | 11.80 | ns   |

| P47 | CLKOUT to $\overline{\text{REG}}$ invalid (MIN = 0.25 x B1 + 1.00)                                           | 8.60  | _     | 7.30  | _     | 6.00  | _     | 4.80   | _     | ns   |

| P48 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ asserted<br>(MAX = 0.25 x B1 + 8.00)                           | 7.60  | 15.60 | 6.30  | 14.30 | 5.00  | 13.00 | 3.80   | 11.80 | ns   |

| P49 | CLKOUT to $\overline{CE1}$ , $\overline{CE2}$ negated<br>(MAX = 0.25 x B1 + 8.00)                            | 7.60  | 15.60 | 6.30  | 14.30 | 5.00  | 13.00 | 3.80   | 11.80 | ns   |

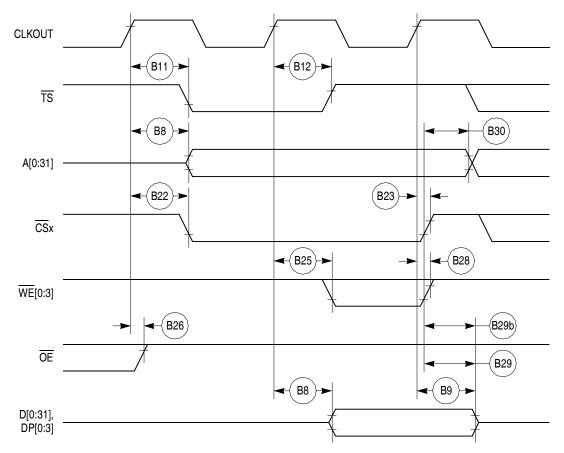

Figure 28. PCMCIA Access Cycles Timing External Bus Write

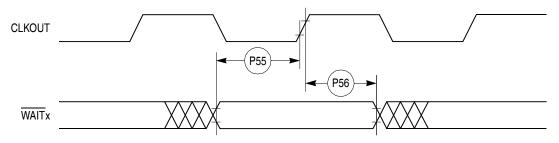

Figure 29 shows the PCMCIA WAIT signals detection timing.

Figure 29. PCMCIA WAIT Signals Detection Timing

MPC866/MPC859 Hardware Specifications, Rev. 2

Table 14 shows the reset timing for the MPC866/859.

Table 14. Reset Timing

|     | Ok ann charlistia                                                                                                                               | 33 N   | /Hz   | 40 N   | /Hz   | 50 N   | /Hz   | 66 MHz |       | 11   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| Num | Characteristic                                                                                                                                  | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| R69 | CLKOUT to $\overline{\text{HRESET}}$ high impedance<br>(MAX = 0.00 x B1 + 20.00)                                                                |        | 20.00 |        | 20.00 |        | 20.00 |        | 20.00 | ns   |

| R70 | CLKOUT to $\overline{\text{SRESET}}$ high impedance<br>(MAX = 0.00 x B1 + 20.00)                                                                | —      | 20.00 | —      | 20.00 | —      | 20.00 | —      | 20.00 | ns   |

| R71 | RSTCONF pulse width (MIN = 17.00 x<br>B1)                                                                                                       | 515.20 | —     | 425.00 | —     | 340.00 | —     | 257.60 | —     | ns   |

| R72 | —                                                                                                                                               | —      | —     | _      |       | _      |       | _      | _     | —    |

| R73 | Configuration data to HRESET rising<br>edge setup time (MIN = 15.00 x B1 +<br>50.00)                                                            | 504.50 | _     | 425.00 | _     | 350.00 | _     | 277.30 | —     | ns   |

| R74 | Configuration data to $\overrightarrow{\text{RSTCONF}}$ rising<br>edge setup time (MIN = 0.00 x B1 +<br>350.00)                                 | 350.00 |       | 350.00 |       | 350.00 |       | 350.00 |       | ns   |

| R75 | Configuration data hold time after<br>RSTCONF negation (MIN = 0.00 x B1 +<br>0.00)                                                              | 0.00   |       | 0.00   |       | 0.00   |       | 0.00   |       | ns   |

| R76 | Configuration data hold time after<br>HRESET negation (MIN = 0.00 x B1 +<br>0.00)                                                               | 0.00   |       | 0.00   |       | 0.00   |       | 0.00   |       | ns   |

| R77 | HRESET and RSTCONF asserted to<br>data out drive (MAX = 0.00 x B1 +<br>25.00)                                                                   |        | 25.00 |        | 25.00 |        | 25.00 | _      | 25.00 | ns   |

| R78 | RSTCONF negated to data out high<br>impedance (MAX = 0.00 x B1 + 25.00)                                                                         |        | 25.00 |        | 25.00 |        | 25.00 |        | 25.00 | ns   |

| R79 | CLKOUT of last rising edge before chip<br>three-states $\overrightarrow{\text{HRESET}}$ to data out high<br>impedance (MAX = 0.00 x B1 + 25.00) |        | 25.00 | _      | 25.00 | _      | 25.00 | _      | 25.00 | ns   |

| R80 | DSDI, DSCK setup (MIN = 3.00 x B1)                                                                                                              | 90.90  | —     | 75.00  | _     | 60.00  | _     | 45.50  | _     | ns   |

| R81 | DSDI, DSCK hold time (MIN = 0.00 x B1<br>+ 0.00)                                                                                                | 0.00   | —     | 0.00   | _     | 0.00   |       | 0.00   | _     | ns   |

| R82 | SRESET negated to CLKOUT rising<br>edge for DSDI and DSCK sample (MIN<br>= 8.00 x B1)                                                           | 242.40 |       | 200.00 | —     | 160.00 | —     | 121.20 | —     | ns   |

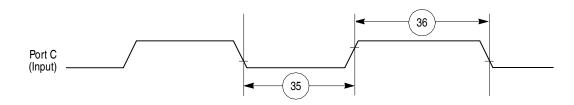

Figure 46. Port C Interrupt Detection Timing

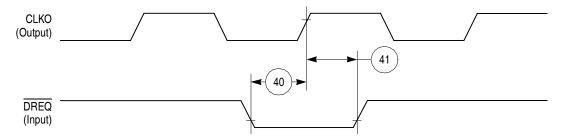

# **12.3 IDMA Controller AC Electrical Specifications**

Table 18 shows the IDMA controller timings as shown in Figure 47 through Figure 50.

| Num | Characteristic                                                                | All Free | llmit |      |

|-----|-------------------------------------------------------------------------------|----------|-------|------|

| Num | Characteristic                                                                | Min      | Max   | Unit |

| 40  | DREQ setup time to clock high                                                 | 7        | _     | ns   |

| 41  | DREQ hold time from clock high                                                | 3        |       | ns   |

| 42  | SDACK assertion delay from clock high                                         |          | 12    | ns   |

| 43  | SDACK negation delay from clock low                                           |          | 12    | ns   |

| 44  | SDACK negation delay from TA low                                              |          | 20    | ns   |

| 45  | SDACK negation delay from clock high                                          | _        | 15    | ns   |

| 46  | TA assertion to falling edge of the clock setup time (applies to external TA) | 7        | _     | ns   |

## Table 18. IDMA Controller Timing

Figure 47. IDMA External Requests Timing Diagram

**CPM Electrical Characteristics**

# **12.5 Timer AC Electrical Specifications**

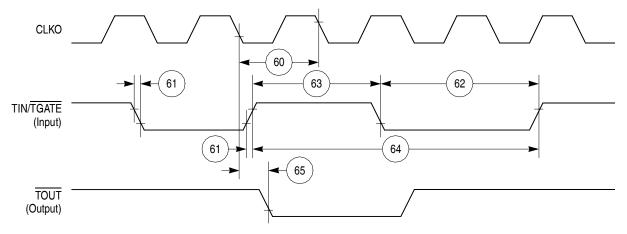

Table 20 shows the general-purpose timer timings as shown in Figure 52.

## Table 20. Timer Timing

| Num | Characteristic               |     | All Frequencies |      |  |  |

|-----|------------------------------|-----|-----------------|------|--|--|

| Num | Characteristic               | Min | Max             | Unit |  |  |

| 61  | TIN/TGATE rise and fall time | 10  |                 | ns   |  |  |

| 62  | TIN/TGATE low time           | 1   | _               | clk  |  |  |

| 63  | TIN/TGATE high time          | 2   | _               | clk  |  |  |

| 64  | TIN/TGATE cycle time         | 3   | _               | clk  |  |  |

| 65  | CLKO low to TOUT valid       | 3   | 25              | ns   |  |  |

Figure 52. CPM General-Purpose Timers Timing Diagram

# **12.6 Serial Interface AC Electrical Specifications**

Table 21 shows the serial interface timings as shown in Figure 53 through Figure 57.

# Table 21. SI Timing

| Num   | Characteristic                                         | All F  | requencies  | Unit |

|-------|--------------------------------------------------------|--------|-------------|------|

| Nulli | Characteristic                                         | Min    | Мах         | Unit |

| 70    | L1RCLK, L1TCLK frequency (DSC = 0) <sup>1, 2</sup>     | —      | SYNCCLK/2.5 | MHz  |

| 71    | L1RCLK, L1TCLK width low (DSC = 0) $^{2}$              | P + 10 | _           | ns   |

| 71a   | L1RCLK, L1TCLK width high (DSC = 0) $^{3}$             | P + 10 | _           | ns   |

| 72    | L1TXD, L1ST(1–4), L1RQ, L1CLKO rise/fall time          | —      | 15.00       | ns   |

| 73    | L1RSYNC, L1TSYNC valid to L1CLK edge (SYNC setup time) | 20.00  | _           | ns   |

#### **CPM Electrical Characteristics**

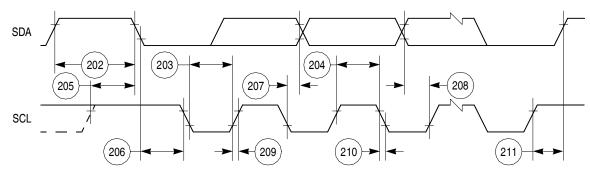

# 12.12I<sup>2</sup>C AC Electrical Specifications

## **UTOPIA AC Electrical Specifications**

Figure 71 shows the  $I^2C$  bus timing.

Figure 71. I<sup>2</sup>C Bus Timing Diagram

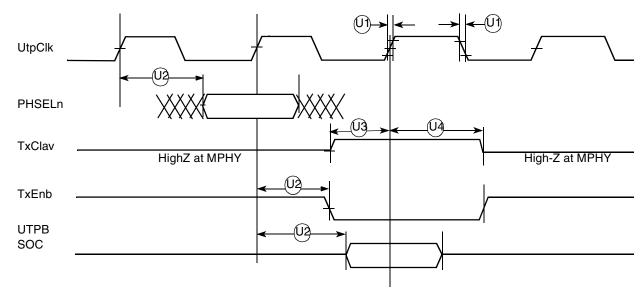

# **13 UTOPIA AC Electrical Specifications**

Table 30 through Table 32 show the AC electrical specifications for the UTOPIA interface.

| Num | Signal Characteristic                                                                                    | Direction | Min | Max | Unit |

|-----|----------------------------------------------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (Internal clock option)                                                            | Output    | —   | 4   | ns   |

|     | Duty cycle                                                                                               |           | 50  | 50  | %    |

|     | Frequency                                                                                                |           | _   | 33  | MHz  |

| U2  | UTPB, SOC, RxEnb, TxEnb, RxAddr, and TxAddr-active delay (and PHREQ and PHSEL active delay in MPHY mode) | Output    | 2   | 16  | ns   |

| U3  | UTPB, SOC, Rxclav and Txclav setup time                                                                  | Input     | 4   | —   | ns   |

| U4  | UTPB, SOC, Rxclav and Txclav hold time                                                                   | Input     | 1   | _   | ns   |

## Table 30. UTOPIA Master (Muxed Mode) Electrical Specifications

## Table 31. UTOPIA Master (Split Bus Mode) Electrical Specifications

| Num | Signal Characteristic                                                                               | Direction | Min | Max | Unit |

|-----|-----------------------------------------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (Internal clock option)                                                       | Output    | _   | 4   | ns   |

|     | Duty cycle                                                                                          |           | 50  | 50  | %    |

|     | Frequency                                                                                           |           | _   | 33  | MHz  |

| U2  | UTPB, SOC, RxEnb, TxEnb, RxAddr and TxAddr active delay (PHREQ and PHSEL active delay in MPHY mode) | Output    | 2   | 16  | ns   |

| U3  | UTPB_Aux, SOC_Aux, Rxclav, and Txclav setup time                                                    | Input     | 4   | _   | ns   |

| U4  | UTPB_Aux, SOC_Aux, Rxclav, and Txclav hold time                                                     | Input     | 1   |     | ns   |

### **FEC Electrical Characteristics**

Figure 73 shows signal timings during UTOPIA transmit operations.

Figure 73. UTOPIA Transmit Timing

# **14 FEC Electrical Characteristics**

This section provides the AC electrical specifications for the fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Also, MII signals use TTL signal levels compatible with devices operating at either 5.0 or 3.3 V.

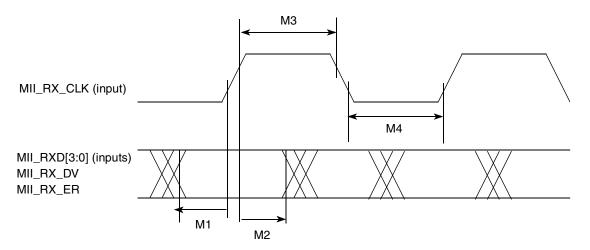

# 14.1 MII Receive Signal Timing (MII\_RXD [3:0], MII\_RX\_DV, MII\_RX\_ER, MII\_RX\_CLK)

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency -1%. Table 33 shows the timings for MII receive signal.

| Num | Characteristic                                         | Min | Max | Unit              |

|-----|--------------------------------------------------------|-----|-----|-------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                |

| MЗ  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK period |

## Table 33. MII Receive Signal Timing

Figure 74 shows the timings for MII receive signal.

Figure 74. MII Receive Signal Timing Diagram

# 14.2 MII Transmit Signal Timing (MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER, MII\_TX\_CLK)

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency - 1%.

Table 34 shows information on the MII transmit signal timing.

| Table 34. | MII | Transmit | Signal | Timing |

|-----------|-----|----------|--------|--------|

|-----------|-----|----------|--------|--------|

| Num | Characteristic                                           | Min | Max | Unit              |

|-----|----------------------------------------------------------|-----|-----|-------------------|

| M5  | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER invalid | 5   | _   | ns                |

| M6  | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER valid   | —   | 25  | _                 |

| M7  | MII_TX_CLK pulse width high                              | 35% | 65% | MII_TX_CLK period |

| M8  | MII_TX_CLK pulse width low                               | 35% | 65% | MII_TX_CLK period |

Mechanical Data and Ordering Information

| Plastic ball grid array   | 0° to 95°C    | 50  | MPC859DSLVR50A  |  |  |

|---------------------------|---------------|-----|-----------------|--|--|

| (VR suffix)<br>Lead free  |               | 66  | MPC859DSLVR66A  |  |  |

|                           |               | 100 | MPC859PVR100A   |  |  |

|                           |               |     | MPC859TVR100A   |  |  |

|                           |               |     | MPC866PVR100A   |  |  |

|                           |               |     | MPC866TVR100A   |  |  |

|                           |               | 133 | MPC859PVR133A   |  |  |

|                           |               |     | MPC859TVR133A   |  |  |

|                           |               |     | MPC866PVR133A   |  |  |

|                           |               |     | MPC866TVR133A   |  |  |

| Plastic ball grid array   | –40° to 100°C | 50  | MPC859DSLCVR50A |  |  |

| (CVR suffix)<br>Lead free |               | 66  | MPC859DSLCVR66A |  |  |

|                           |               | 100 | MPC859PCVR100A  |  |  |

|                           |               |     | MPC859TCVR100A  |  |  |

|                           |               |     | MPC866PCVR100A  |  |  |

|                           |               |     | MPC866TCVR100A  |  |  |

# Table 38. MPC866/859 Package/Frequency Orderable (continued)

# Table 39. Pin Assignments (continued)

| Name                                                                          | Pin Number | Туре                                    |

|-------------------------------------------------------------------------------|------------|-----------------------------------------|

| PB25<br>RXADDR3 <sup>2</sup><br>SMTXD1                                        | J16        | Bidirectional<br>(Optional: Open-drain) |

| PB24<br>TXADDR3 <sup>2</sup><br>SMRXD1                                        | J18        | Bidirectional<br>(Optional: Open-drain) |

| PB23<br>TXADDR2 <sup>2</sup><br>SDACK1<br>SMSYN1                              | K17        | Bidirectional<br>(Optional: Open-drain) |

| PB22<br>TXADDR4 <sup>2</sup><br>SDACK2<br>SMSYN2                              | L19        | Bidirectional<br>(Optional: Open-drain) |

| PB21<br>SMTXD2<br>L1CLKOB<br>PHSEL1 <sup>1</sup><br>TXADDR1 <sup>2</sup>      | K16        | Bidirectional<br>(Optional: Open-drain) |

| PB20<br>SMRXD2<br>L1CLKOA<br>PHSEL0 <sup>1</sup><br>TXADDR0 <sup>2</sup>      | L16        | Bidirectional<br>(Optional: Open-drain) |

| PB19<br>RTS1<br>L1ST1                                                         | N19        | Bidirectional<br>(Optional: Open-drain) |

| PB18<br>RXADDR4 <sup>2</sup><br>RTS2<br>L1ST2                                 | N17        | Bidirectional<br>(Optional: Open-drain) |

| PB17<br>L1RQb<br>L1ST3<br>RTS3<br>PHREQ1 <sup>1</sup><br>RXADDR1 <sup>2</sup> | P18        | Bidirectional<br>(Optional: Open-drain) |