### NXP USA Inc. - MPC859DSLZP66A Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 66MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 357-BBGA                                                               |

| Supplier Device Package         | 357-PBGA (25x25)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc859dslzp66a |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- ATM port-to-port switching capability without the need for RAM-based microcode

- Simultaneous MII (10/100Base-T) and UTOPIA (half-duplex) capability

- Optional statistical cell counters per PHY

- UTOPIA level 2 compliant interface with added FIFO buffering to reduce the total cell transmission time. (The earlier UTOPIA level 1 specification is also supported.)

- Multi-PHY support on the MPC866, MPC859P, and MPC859T

- Four PHY support on the MPC866/859

- Parameter RAM for both SPI and I<sup>2</sup>C can be relocated without RAM-based microcode

- Supports full-duplex UTOPIA both master (ATM side) and slave (PHY side) operation using a 'split' bus

- AAL2/VBR functionality is ROM-resident.

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- Thirty-two address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to page mode/EDO/SDRAM, SRAM, EPROMs, flash EPROMs, and other memory devices.

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, and one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbytes–256 Mbytes)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers cascadable to be two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Fast Ethernet controller (FEC)

- Simultaneous MII (10/100Base-T) and UTOPIA operation when using the UTOPIA multiplexed bus

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer and time base from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- Twelve port pins with interrupt capability

- The MPC866P and MPC866T have 23 internal interrupt sources; the MPC859P, MPC859T, and MPC859DSL have 20 internal interrupt sources.

- Programmable priority between SCCs (MPC866P and MPC866T)

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8-Kbytes of dual-port RAM

- MPC866P and MPC866T have 16 serial DMA (SDMA) channels; MPC859P, MPC859T, and MPC859DSL have 10 serial DMA (SDMA) channels.

- Three parallel I/O registers with open-drain capability

- Four baud rate generators

- Independent (can be connected to any SCC or SMC)

- Allow changes during operation

- Autobaud support option

- MPC866P and MPC866T have four SCCs (serial communication controller); MPC859P, MPC859T, and MPC859DSL have one SCC; and SCC1 on MPC859DSL supports Ethernet only.

- Serial ATM capability on all SCCs

- Optional UTOPIA port on SCC4

- Ethernet/IEEE 802.3 optional on SCC1–4, supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC)

- Two SMCs (serial management channels) (MPC859DSL has one SMC (SMC1) for UART.)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division multiplexed (TDM) channels

#### MPC866/MPC859 Hardware Specifications, Rev. 2

# **4** Thermal Characteristics

Table 4 shows the thermal characteristics for the MPC866/859.

#### Table 4. MPC866/859 Thermal Resistance Data

| Rating                               | Env                  | Environment             |                      |    | Unit |

|--------------------------------------|----------------------|-------------------------|----------------------|----|------|

| Junction-to-ambient <sup>1</sup>     | Natural Convection   | Single-layer board (1s) | $R_{\theta JA}^2$    | 37 | °C/W |

|                                      |                      | Four-layer board (2s2p) | $R_{\theta JMA}^{3}$ | 23 |      |

|                                      | Airflow (200 ft/min) | Single-layer board (1s) | $R_{\theta JMA}^{3}$ | 30 |      |

|                                      |                      | Four-layer board (2s2p) | $R_{\theta JMA}^{3}$ | 19 |      |

| Junction-to-board <sup>4</sup>       |                      |                         | $R_{\theta JB}$      | 13 |      |

| Junction-to-case 5                   |                      |                         | R <sub>θJC</sub>     | 6  |      |

| Junction-to-package top <sup>6</sup> | Natural Convection   |                         | $\Psi_{JT}$          | 2  |      |

|                                      | Airflow (200 ft/min) |                         | $\Psi_{JT}$          | 2  |      |

<sup>1</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated value from the junction to the exposed pad without contact resistance.

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and junction temperature per JEDEC JESD51-2.

| Characteristic                                                                                                                                                                                               | Symbol          | Min        | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|------|------|

| Input low voltage                                                                                                                                                                                            | VIL             | GND        | 0.8  | V    |

| EXTAL, EXTCLK input high voltage                                                                                                                                                                             | VIHC            | 0.7*(VDDH) | VDDH | V    |

| Input leakage current, Vin = 5.5V (except TMS, $\overline{\text{TRST}}$ , DSCK and DSDI pins) for 5 Volts Tolerant Pins <sup>2</sup>                                                                         | l <sub>in</sub> | —          | 100  | μA   |

| Input leakage current, Vin = VDDH (except TMS, TRST, DSCK, and DSDI)                                                                                                                                         | l <sub>in</sub> | _          | 10   | μA   |

| Input leakage current, Vin = 0 V (except TMS, $\overline{\text{TRST}}$ , DSCK and DSDI pins)                                                                                                                 | l <sub>in</sub> | —          | 10   | μA   |

| Input capacitance <sup>3</sup>                                                                                                                                                                               | C <sub>in</sub> | —          | 20   | pF   |

| Output high voltage, IOH = $-2.0$ mA,<br>except XTAL, and Open drain pins                                                                                                                                    | VOH             | 2.4        | _    | V    |

| Output low voltage<br>• IOL = 2.0 mA (CLKOUT)<br>• IOL = 3.2 mA <sup>4</sup><br>• IOL = 5.3 mA <sup>5</sup><br>• IOL = 7.0 mA (TXD1/PA14, TXD2/PA12)<br>• IOL = 8.9 mA (TS, TA, TEA, BI, BB, HRESET, SRESET) | VOL             | _          | 0.5  | V    |

#### Table 6. DC Electrical Specifications (continued)

<sup>1</sup> The difference between VDDL and VDDSYN can not be more than 100 m V.

<sup>2</sup> The signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], TDI, TDO, TCK, TRST\_B, TMS, MII\_TXEN, MII\_MDIO are 5 V tolerant.

<sup>3</sup> Input capacitance is periodically sampled.

<sup>4</sup> A(0:31), TSIZ0/REG, TSIZ1, D(0:31), DP(0:3)/IRQ(3:6), RD/WR, BURST, RSV/IRQ2, IP\_B(0:1)/IWP(0:1)/VFLS(0:1), IP\_B2/IOIS16\_B/AT2, IP\_B3/IWP2/VF2, IP\_B4/LWP0/VF0, IP\_B5/LWP1/VF1, IP\_B6/DSDI/AT0, IP\_B7/PTR/AT3, RXD1 /PA15, RXD2/PA13, L1TXDB/PA11, L1RXDB/PA10, L1TXDA/PA9, L1RXDA/PA8, TIN1/L1RCLKA/BRGO1/CLK1/PA7, BRGCLK1/TOUT1/CLK2/PA6, TIN2/L1TCLKA/BRGO2/CLK3/PA5, TOUT2/CLK4/PA4, TIN3/BRGO3/CLK5/PA3, BRGCLK2/L1RCLKB/TOUT3/CLK6/PA2, TIN4/BRGO4/CLK7/PA1, L1TCLKB/TOUT4/CLK8/PA0, REJCT1/SPISEL/PB31, SPICLK/PB30, SPIMOSI/PB29, BRGO4/SPIMISO/PB28, BRGO1/I2CSDA/PB27, BRGO2/I2CSCL/PB26, SMTXD1/PB25, SMRXD1/PB24, SMSYN1/SDACK1/PB23, SMSYN2/SDACK2/PB22, SMTXD2/L1CLKOB/PB21, SMRXD2/L1CLKOA/PB20, L1ST1/RTS1/PB19, L1ST2/RTS2/PB18, L1ST3/L1RQB/PB17, L1ST4/L1RQA/PB16, BRGO3/PB15, RSTRT1/PB14, L1ST1/RTS1/DREQ0/PC15, L1ST2/RTS2/DREQ1/PC14, L1ST3/L1RQB/PC13, L1ST4/L1RQA/PC12, CTS1/PC11, TGATE1/CD1/PC10, CTS2/PC9, TGATE2/CD2/PC8, CTS3/SDACK2/L1TSYNCB/PC7, CD3/L1RSYNCB/PC6, CTS4/SDACK1/L1TSYNCA/PC5, CD4/L1RSYNCA/PC4, PD15/L1TSYNCA, PD14/L1RSYNCA, PD13/L1TSYNCB, PD12/L1RSYNCB, PD11/RXD3, PD10/TXD3, PD9/RXD4, PD8/TXD4, PD5/REJECT2, PD6/RTS4, PD7/RTS3, PD4/REJECT3, PD3, MII\_MDC, MII\_TX\_ER, MII\_EN, MII\_MDIO, MII\_TXD[0:3].

<sup>5</sup> BDIP/GPL\_B(5), BR, BG, FRZ/IRQ6, CS(0:5), CS(6)/CE(1)\_B, CS(7)/CE(2)\_B, WE0/BS\_B0/IORD, WE1/BS\_B1/IOWR, WE2/BS\_B2/PCOE, WE3/BS\_B3/PCWE, BS\_A(0:3), GPL\_A0/GPL\_B0, OE/GPL\_A1/GPL\_B1, GPL\_A(2:3)/GPL\_B(2:3)/CS(2:3), UPWAITA/GPL\_A4, UPWAITB/GPL\_B4, GPL\_A5, ALE\_A, CE1\_A, CE2\_A, ALE\_B/DSCK/AT1, OP(0:1), OP2/MODCK1/STS, OP3/MODCK2/DSDO, BADDR(28:30).

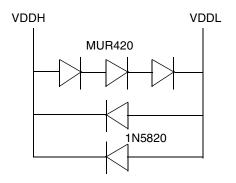

# 8 Power Supply and Power Sequencing

This section provides design considerations for the MPC866/859 power supply. The MPC866/859 has a core voltage (VDDL) and PLL voltage (VDDSYN) that operates at a lower voltage than the I/O voltage VDDH. The I/O section of the MPC866/859 is supplied with 3.3 V across VDDH and  $V_{SS}$  (GND).

Signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], TDI, TDO, TCK, TRST\_B, TMS, MII\_TXEN, and MII\_MDIO are 5-V tolerant. All inputs cannot be more than 2.5 V greater than VDDH. In addition, 5-V tolerant pins cannot exceed 5.5 V and the remaining input pins cannot exceed 3.465 V. This restriction applies to power up/down and normal operation.

One consequence of multiple power supplies is that when power is initially applied the voltage rails ramp up at different rates. The rates depend on the nature of the power supply, the type of load on each power supply, and the manner in which different voltages are derived. The following restrictions apply:

- VDDL must not exceed VDDH during power up and power down.

- VDDL must not exceed 1.9 V and VDDH must not exceed 3.465 V.

These cautions are necessary for the long term reliability of the part. If they are violated, the electrostatic discharge (ESD) protection diodes are forward-biased and excessive current can flow through these diodes. If the system power supply design does not control the voltage sequencing, the circuit shown in Figure 4 can be added to meet these requirements. The MUR420 Schottky diodes control the maximum potential difference between the external bus and core power supplies on powerup and the 1N5820 diodes regulate the maximum potential difference on powerdown.

Figure 4. Example Voltage Sequencing Circuit

# 9 Layout Practices

Each  $V_{DD}$  pin on the MPC866/859 should be provided with a low-impedance path to the board's supply. Furthermore, each GND pin should be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1  $\mu$ F bypass capacitors located as close as possible to the four sides of the package. Each board designed should be characterized and additional appropriate decoupling capacitors should be used if required. The capacitor leads and associated printed-circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than 1/2" per capacitor lead. At a minimum, a four-layer board employing two inner layers as  $V_{DD}$  and GND planes should be used.

All output pins on the MPC866/859 have fast rise and fall times. Printed-circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times.

| Num  | Chavastavistia                                                                                                                                                                | 33   | MHz   | 40   | 40 MHz 50 MHz |      |       | IHz 66 MHz |       |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|---------------|------|-------|------------|-------|------|

| Num  | Characteristic                                                                                                                                                                | Min  | Max   | Min  | Max           | Min  | Max   | Min        | Мах   | Unit |

| B12a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ negation (when<br>driven by the memory controller or<br>PCMCIA interface) (MAX = 0.00 x B1 +<br>9.00)                             | 2.50 | 9.00  | 2.50 | 9.00          | 2.50 | 9.00  | 2.50       | 9.00  | ns   |

| B13  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ High-Z (MIN = 0.25 x B1)                                                                                                          | 7.60 | 21.60 | 6.30 | 20.30         | 5.00 | 19.00 | 3.80       | 14.00 | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ High-Z (when driven<br>by the memory controller or PCMCIA<br>interface) (MIN = 0.00 x B1 + 2.5)                                   | 2.50 | 15.00 | 2.50 | 15.00         | 2.50 | 15.00 | 2.50       | 15.00 | ns   |

| B14  | CLKOUT to TEA assertion (MAX = 0.00 x B1 + 9.00)                                                                                                                              | 2.50 | 9.00  | 2.50 | 9.00          | 2.50 | 9.00  | 2.50       | 9.00  | ns   |

| B15  | CLKOUT to $\overline{\text{TEA}}$ High-Z (MIN = 0.00 x B1 + 2.50)                                                                                                             | 2.50 | 15.00 | 2.50 | 15.00         | 2.50 | 15.00 | 2.50       | 15.00 | ns   |

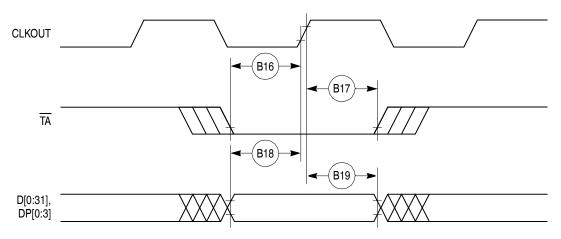

| B16  | $\overline{TA}$ , $\overline{BI}$ valid to CLKOUT (setup time)<br>(MIN = 0.00 x B1 + 6.00)                                                                                    | 6.00 | -     | 6.00 | —             | 6.00 | —     | 6.00       | —     | ns   |

| B16a | TEA, KR, RETRY, CR valid to CLKOUT<br>(setup time) (MIN = 0.00 x B1 + 4.5)                                                                                                    | 4.50 | _     | 4.50 | _             | 4.50 | _     | 4.50       | —     | ns   |

| B16b | $\overline{\text{BB}}$ , $\overline{\text{BG}}$ , $\overline{\text{BR}}$ , valid to CLKOUT (setup time) <sup>2</sup> (4 MIN = 0.00 x B1 + 0.00 )                              | 4.00 | —     | 4.00 | —             | 4.00 | _     | 4.00       | —     | ns   |

| B17  | CLKOUT to $\overline{TA}$ , $\overline{TEA}$ , $\overline{BI}$ , $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ valid (hold time) (MIN = 0.00 x B1 + 1.00 <sup>3</sup> ) | 1.00 | —     | 1.00 | _             | 1.00 | —     | 2.00       | _     | ns   |

| B17a | CLKOUT to $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid (hold time) (MIN = 0.00 x B1 + 2.00)                                              | 2.00 | —     | 2.00 | —             | 2.00 | _     | 2.00       | —     | ns   |

| B18  | D(0:31), DP(0:3) valid to CLKOUT<br>rising edge (setup time) $^{4}$ (MIN = 0.00<br>x B1 + 6.00)                                                                               | 6.00 | _     | 6.00 | _             | 6.00 | —     | 6.00       | —     | ns   |

| B19  | CLKOUT rising edge to D(0:31),<br>DP(0:3) valid (hold time) $^{4}$ (MIN = 0.00<br>x B1 + 1.00 $^{5}$ )                                                                        | 1.00 | _     | 1.00 | _             | 1.00 | _     | 2.00       | _     | ns   |

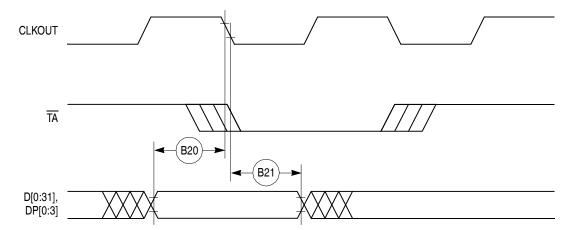

| B20  | D(0:31), DP(0:3) valid to CLKOUT<br>falling edge (setup time) $^{6}$ (MIN = 0.00<br>x B1 + 4.00)                                                                              | 4.00 | —     | 4.00 | —             | 4.00 | —     | 4.00       | —     | ns   |

| B21  | CLKOUT falling edge to D(0:31),<br>DP(0:3) valid (hold Time) $^{6}$ (MIN = 0.00<br>x B1 + 2.00)                                                                               | 2.00 | —     | 2.00 | —             | 2.00 | —     | 2.00       | —     | ns   |

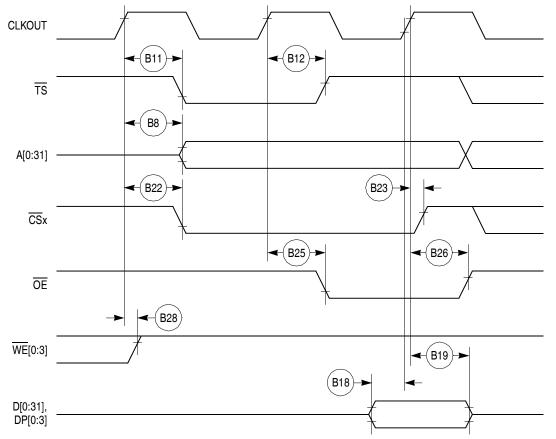

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted<br>GPCM ACS = 00 (MAX = 0.25 x B1 + 6.3)                                                                                       | 7.60 | 13.80 | 6.30 | 12.50         | 5.00 | 11.30 | 3.80       | 10.00 | ns   |

| B22a | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0 (MAX = 0.00 x B1 + 8.00)                                                                           |      | 8.00  | —    | 8.00          |      | 8.00  | —          | 8.00  | ns   |

# Table 9. Bus Operation Timings (continued)

|      |                                                                                                                                                                                                                                                              | 33    | MHz   | 40 1  | MHz   | 50 I  | MHz   | 66 I  | MHz   |      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Num  | Characteristic                                                                                                                                                                                                                                               | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| B28d | CLKOUT falling edge to $\overline{CS}$ negated<br>GPCM write access TRLX = 0,1,<br>CSNT = 1, ACS = 10, or ACS = 11,<br>EBDF = 1 (MAX = 0.375 x B1 + 6.6)                                                                                                     | _     | 18.00 |       | 18.00 |       | 14.30 | _     | 12.30 | ns   |

| B29  | $\overline{WE}$ (0:3) negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, CSNT = 0,<br>EBDF = 0 (MIN = 0.25 x B1 - 2.00)                                                                                                                                | 5.60  | _     | 4.30  | —     | 3.00  | —     | 1.80  | —     | ns   |

| B29a | $\overline{\text{WE}}(0:3)$ negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 0,<br>CSNT = 1, EBDF = 0 (MIN = 0.50 x B1<br>- 2.00)                                                                                                             | 13.20 |       | 10.50 | _     | 8.00  | _     | 5.60  | _     | ns   |

| B29b | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3), High<br>Z GPCM write access, ACS = 00,<br>TRLX = 0,1 & CSNT = 0 (MIN = 0.25 x<br>B1-2.00)                                                                                                                | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80  | _     | ns   |

| B29c | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT<br>= 1, ACS = 10, or ACS = 11, EBDF = 0<br>(MIN = 0.50 x B1 - 2.00)                                                                                           | 13.20 |       | 10.50 | _     | 8.00  | _     | 5.60  | _     | ns   |

| B29d | $\overline{\text{WE}}$ (0:3) negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 1,<br>CSNT = 1, EBDF = 0 (MIN = 1.50 x B1<br>- 2.00)                                                                                                            | 43.50 | _     | 35.50 | _     | 28.00 | _     | 20.70 | _     | ns   |

| B29e | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT<br>= 1, ACS = 10, or ACS = 11, EBDF = 0<br>(MIN = 1.50 x B1 - 2.00)                                                                                           | 43.50 | _     | 35.50 | _     | 28.00 | _     | 20.70 | _     | ns   |

| B29f | $\overline{\text{WE}}$ (0:3) negated to D(0:31), DP(0:3)<br>High Z GPCM write access, TRLX = 0,<br>CSNT = 1, EBDF = 1 (MIN = 0.375 x<br>B1 - 6.30)                                                                                                           | 5.00  | _     | 3.00  | _     | 1.10  | _     | 0.00  | _     | ns   |

| B29g | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 0, CSNT<br>= 1 ACS = 10 or ACS = 11, EBDF = 1<br>(MIN = 0.375 x B1 - 6.30)                                                                                            | 5.00  | _     | 3.00  | _     | 1.10  | _     | 0.00  | _     | ns   |

| B29h | $\overline{\text{WE}}(0:3)$ negated to D(0:31), DP(0:3)<br>High Z GPCM write access, TRLX = 1,<br>CSNT = 1, EBDF = 1 (MIN = 0.375 x<br>B1 - 3.30)                                                                                                            | 38.40 | _     | 31.10 | _     | 24.20 | _     | 17.50 | _     | ns   |

| B29i | $      \overline{\text{CS}} \text{ negated to D(0:31), DP(0:3) High-Z} \\       \text{GPCM write access, TRLX = 1, CSNT} \\       = 1, ACS = 10 \text{ or ACS = 11, EBDF = 1} \\        (MIN = 0.375 \text{ x B1} - 3.30)                                  $ | 38.40 | _     | 31.10 | _     | 24.20 | _     | 17.50 | _     | ns   |

# Table 9. Bus Operation Timings (continued)

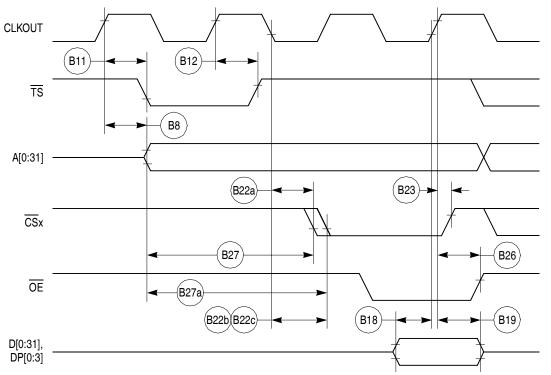

Figure 10 shows normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 10. Input Data Timing in Normal Case

Figure 11 shows the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Figure 11. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

Figure 12 through Figure 15 show the timing for the external bus read controlled by various GPCM factors.

Figure 12. External Bus Read Timing (GPCM Controlled—ACS = 00)

Figure 15. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10, ACS = 11)

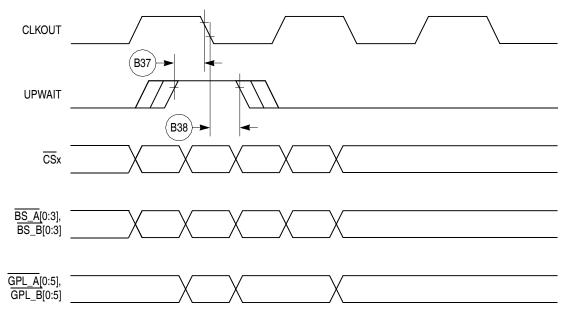

Figure 20 shows the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Figure 20. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

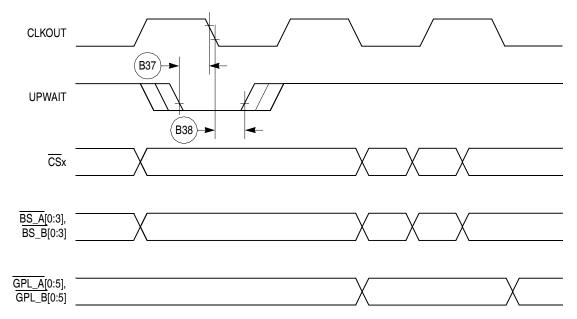

Figure 21 shows the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

Figure 21. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

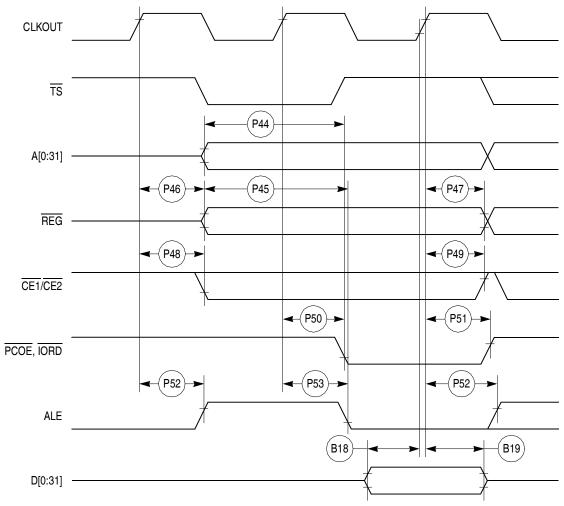

Figure 27 shows the PCMCIA access cycle timing for the external bus read.

Figure 27. PCMCIA Access Cycles Timing External Bus Read

**CPM Electrical Characteristics**

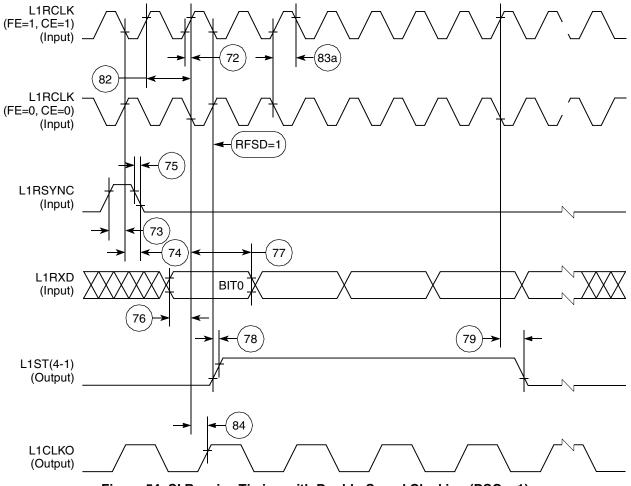

Figure 54. SI Receive Timing with Double-Speed Clocking (DSC = 1)

#### **CPM Electrical Characteristics**

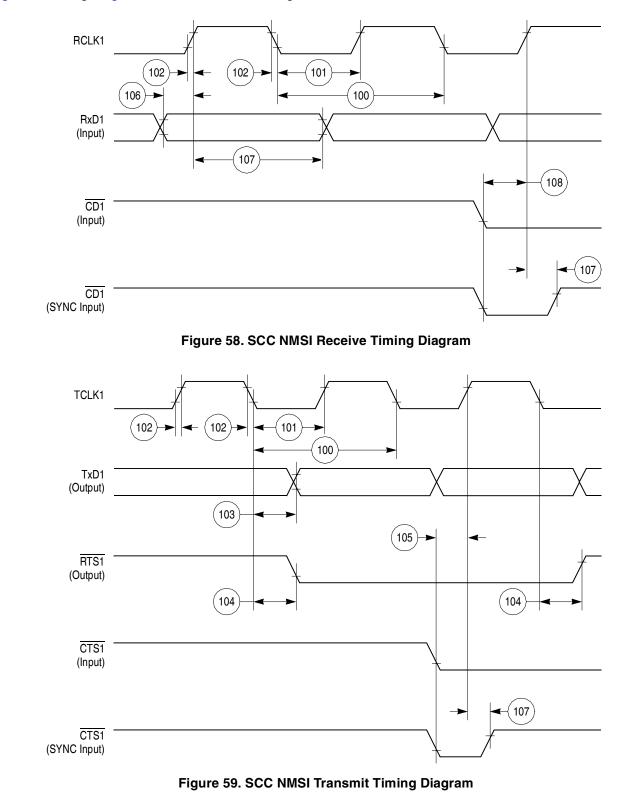

Figure 58 through Figure 60 show the NMSI timings.

MPC866/MPC859 Hardware Specifications, Rev. 2

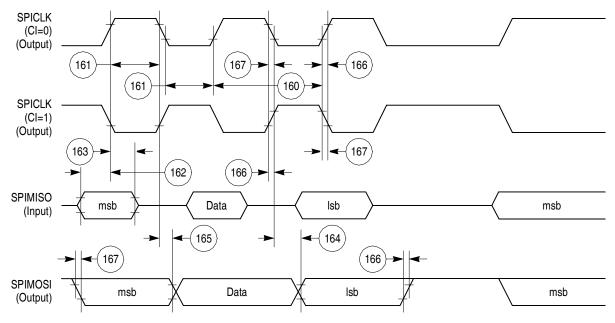

# **12.10SPI Master AC Electrical Specifications**

Table 26 shows the SPI master timings as shown in Figure 67 and Figure 68.

## Table 26. SPI Master Timing

| Num | Characteristic                      | All Freq | Unit |                  |

|-----|-------------------------------------|----------|------|------------------|

| Num |                                     |          | Max  | Onit             |

| 160 | MASTER cycle time                   | 4        | 1024 | t <sub>cyc</sub> |

| 161 | MASTER clock (SCK) high or low time | 2        | 512  | t <sub>cyc</sub> |

| 162 | MASTER data setup time (inputs)     | 15       | _    | ns               |

| 163 | Master data hold time (inputs)      | 0        | _    | ns               |

| 164 | Master data valid (after SCK edge)  | _        | 10   | ns               |

| 165 | Master data hold time (outputs)     | 0        | _    | ns               |

| 166 | Rise time output                    | _        | 15   | ns               |

| 167 | Fall time output                    | _        | 15   | ns               |

Figure 67. SPI Master (CP = 0) Timing Diagram

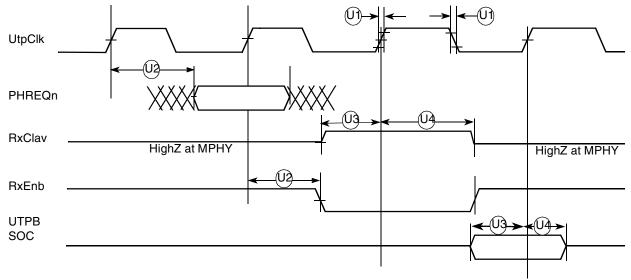

| Num | Signal Characteristic                                            | Direction | Min | Max | Unit |

|-----|------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (external clock option)                    | Input     |     | 4   | ns   |

|     | Duty cycle                                                       |           | 40  | 60  | %    |

|     | Frequency                                                        |           | _   | 33  | MHz  |

| U2  | UTPB, SOC, Rxclav and Txclav active delay                        | Output    | 2   | 16  | ns   |

| U3  | UTPB_AUX, SOC_Aux, RxEnb, TxEnb, RxAddr, and TxAddr setup time   | Input     | 4   | —   | ns   |

| U4  | UTPB_AUX, SOC_Aux, RxEnb, TxEnb, RxAddr, and TxAddr<br>hold time | Input     | 1   | _   | ns   |

Table 32. UTOPIA Slave (Split Bus Mode) Electrical Specifications

Figure 72 shows signal timings during UTOPIA receive operations.

Figure 72. UTOPIA Receive Timing

| Table 39. Pin Assignments | (continued) |

|---------------------------|-------------|

|---------------------------|-------------|

| Name                                                      | Pin Number | Туре                     |

|-----------------------------------------------------------|------------|--------------------------|

| UPWAITB<br>GPL_B4                                         | B1         | Bidirectional            |

| GPL_A5                                                    | D3         | Output                   |

| PORESET                                                   | R2         | Input                    |

| RSTCONF                                                   | P3         | Input                    |

| HRESET                                                    | N4         | Open-drain               |

| SRESET                                                    | P2         | Open-drain               |

| XTAL                                                      | P1         | Analog Output            |

| EXTAL                                                     | N1         | Analog Input (3.3V only) |

| CLKOUT                                                    | W3         | Output                   |

| EXTCLK                                                    | N2         | Input (3.3V only)        |

| TEXP                                                      | N3         | Output                   |

| ALE_A<br>MII-TXD1                                         | К2         | Output                   |

| CE1_A<br>MII-TXD2                                         | B3         | Output                   |

| CE2_A<br>MII-TXD3                                         | A3         | Output                   |

| WAIT_A<br>SOC_Split <sup>2</sup>                          | R3         | Input                    |

| WAIT_B                                                    | R4         | Input                    |

| IP_A0<br>UTPB_Split0 <sup>2</sup><br>MII-RXD3             | Т5         | Input                    |

| IP_A1<br>UTPB_Split1 <sup>2</sup><br>MII-RXD2             | T4         | Input                    |

| IP_A2<br>IOIS16_A<br>UTPB_Split2 <sup>2</sup><br>MII-RXD1 | U3         | Input                    |

| IP_A3<br>UTPB_Split3 <sup>2</sup><br>MII-RXD0             | W2         | Input                    |

| IP_A4<br>UTPB_Split4 <sup>2</sup><br>MII-RXCLK            | U4         | Input                    |

#### Mechanical Data and Ordering Information

| Name                                           | Pin Number | Туре                         |

|------------------------------------------------|------------|------------------------------|

| IP_A5<br>UTPB_Split5 <sup>2</sup><br>MII-RXERR | U5         | Input                        |

| IP_A6<br>UTPB_Split6 <sup>2</sup><br>MII-TXERR | Тб         | Input                        |

| IP_A7<br>UTPB_Split7 <sup>2</sup><br>MII-RXDV  | Т3         | Input                        |

| ALE_B<br>DSCK/AT1                              | J1         | Bidirectional<br>Three-state |

| IP_B[0:1]<br>IWP[0:1]<br>VFLS[0:1]             | H2, J3     | Bidirectional                |

| IP_B2<br>IOIS16_B<br>AT2                       | J2         | Bidirectional<br>Three-state |

| IP_B3<br>IWP2<br>VF2                           | G1         | Bidirectional                |

| IP_B4<br>LWP0<br>VF0                           | G2         | Bidirectional                |

| IP_B5<br>LWP1<br>VF1                           | J4         | Bidirectional                |

| IP_B6<br>DSDI<br>AT0                           | КЗ         | Bidirectional<br>Three-state |

| IP_B7<br>PTR<br>AT3                            | H1         | Bidirectional<br>Three-state |

| OP0<br>MII-TXD0<br>UtpClk_Split <sup>2</sup>   | L4         | Bidirectional                |

| OP1                                            | L2         | Output                       |

| OP2<br>MODCK1<br>STS                           | L1         | Bidirectional                |

# Table 39. Pin Assignments (continued)

#### Mechanical Data and Ordering Information

| Name                                | Pin Number | Туре          |

|-------------------------------------|------------|---------------|

| PD9<br>RXD4<br>MII-TXD0<br>UTPCLK   | V17        | Bidirectional |

| PD8<br>TXD4<br>MII-MDC<br>MII-RXCLK | W17        | Bidirectional |

| PD7<br>RTS3<br>MII-RXERR<br>UTPB4   | T15        | Bidirectional |

| PD6<br>RTS4<br>MII-RXDV<br>UTPB5    | V16        | Bidirectional |

| PD5<br>REJECT2<br>MII-TXD3<br>UTPB6 | U15        | Bidirectional |

| PD4<br>REJECT3<br>MII-TXD2<br>UTPB7 | U16        | Bidirectional |

| PD3<br>REJECT4<br>MII-TXD1<br>SOC   | W16        | Bidirectional |

| TMS                                 | G18        | Input         |

| TDI<br>DSDI                         | H17        | Input         |

| TCK<br>DSCK                         | H16        | Input         |

| TRST                                | G19        | Input         |

| TDO<br>DSDO                         | G17        | Output        |

| MII_CRS                             | B7         | Input         |

| MII_MDIO                            | H18        | Bidirectional |

| MII_TXEN                            | V15        | Output        |

# Table 39. Pin Assignments (continued)

#### Mechanical Data and Ordering Information

# Table 39. Pin Assignments (continued)

| Name    | Pin Number                                                                                                                                                                                                                                                                                                                                                                      | Туре                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| MII_COL | H4                                                                                                                                                                                                                                                                                                                                                                              | Input                  |

| VSSSYN1 | V1                                                                                                                                                                                                                                                                                                                                                                              | PLL analog VDD and GND |

| VSSSYN  | U1                                                                                                                                                                                                                                                                                                                                                                              | Power                  |

| VDDSYN  | T1                                                                                                                                                                                                                                                                                                                                                                              | Power                  |

| GND     | F6, F7, F8, F9, F10, F11, F12, F13, F14, G6, G7, G8, G9, G10, G11, G12, G13, G14, H6, H7, H8, H9, H10, H11, H12, H13, H14, J6, J7, J8, J9, J10, J11, J12, J13, J14, K6, K7, K8, K9, K10, K11, K12, K13, K14, L6, L7, L8, L9, L10, L11, L12, L13, L14, M6, M7, M8, M9, M10, M11, M12, M13, M14, N6, N7, N8, N9, N10, N11, N12, N13, N14, P6, P7, P8, P9, P10, P11, P12, P13, P14 | Power                  |

| VDDL    | A8, M1, W8, H19, F4, F16, P4, P16, R1                                                                                                                                                                                                                                                                                                                                           | Power                  |

| VDDH    | E5, E6, E7, E8, E9, E10, E11, E12, E13, E14, E15, F5, F15, G5, G15, H5, H15, J5, J15, K5, K15, L5, L15, M5, M15, N5, N15, P5, P15, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, T14                                                                                                                                                                                        | Power                  |

| N/C     | D6, D13, D14, U2, V2, T2                                                                                                                                                                                                                                                                                                                                                        | No-connect             |

<sup>1</sup> Classic SAR mode only

<sup>2</sup> ESAR mode only