#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Active                                                     |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                     |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 100MHz                                                     |

| Co-Processors/DSP               | Communications; CPM                                        |

| RAM Controllers                 | DRAM                                                       |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                 |

| SATA                            |                                                            |

| USB                             | -                                                          |

| Voltage - I/O                   | 3.3V                                                       |

| Operating Temperature           | 0°C ~ 95°C (TA)                                            |

| Security Features               | -                                                          |

| Package / Case                  | 357-BBGA                                                   |

| Supplier Device Package         | 357-PBGA (25x25)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc859tvr100a |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Features

- One serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multiple-master operation on the same bus

- One inter-integrated circuit (I<sup>2</sup>C) port

- Supports master and slave modes

- Multiple-master environment support

- Time slot assigner (TSA) (MPC859DSL does not have TSA.)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user-defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, and clocking

- Allows dynamic changes

- On MPC866P and MPC866T, can be internally connected to six serial channels (four SCCs and two SMCs); on MPC859P and MPC859T, can be connected to three serial channels (one SCC and two SMCs).

- Parallel interface port (PIP)

- Centronics interface support

- Supports fast connection between compatible ports on MPC866/859 or MC68360

- PCMCIA interface

- Master (socket) interface, compliant with PCI Local Bus Specification (Rev 2.1)

- Supports one or two PCMCIA sockets whether ESAR functionality is enabled

- Eight memory or I/O windows supported

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two operate on data.

- Supports conditions: =  $\neq < >$

- Each watchpoint can generate a breakpoint internally

- Normal high and normal low power modes to conserve power

- 1.8 V core and 3.3 V I/O operation with 5-V TTL compatibility; refer to Table 6 for a listing of the 5-V tolerant pins.

- 357-pin plastic ball grid array (PBGA) package

- Operation up to 133 MHz

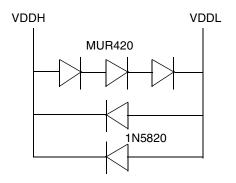

# 8 Power Supply and Power Sequencing

This section provides design considerations for the MPC866/859 power supply. The MPC866/859 has a core voltage (VDDL) and PLL voltage (VDDSYN) that operates at a lower voltage than the I/O voltage VDDH. The I/O section of the MPC866/859 is supplied with 3.3 V across VDDH and  $V_{SS}$  (GND).

Signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], TDI, TDO, TCK, TRST\_B, TMS, MII\_TXEN, and MII\_MDIO are 5-V tolerant. All inputs cannot be more than 2.5 V greater than VDDH. In addition, 5-V tolerant pins cannot exceed 5.5 V and the remaining input pins cannot exceed 3.465 V. This restriction applies to power up/down and normal operation.

One consequence of multiple power supplies is that when power is initially applied the voltage rails ramp up at different rates. The rates depend on the nature of the power supply, the type of load on each power supply, and the manner in which different voltages are derived. The following restrictions apply:

- VDDL must not exceed VDDH during power up and power down.

- VDDL must not exceed 1.9 V and VDDH must not exceed 3.465 V.

These cautions are necessary for the long term reliability of the part. If they are violated, the electrostatic discharge (ESD) protection diodes are forward-biased and excessive current can flow through these diodes. If the system power supply design does not control the voltage sequencing, the circuit shown in Figure 4 can be added to meet these requirements. The MUR420 Schottky diodes control the maximum potential difference between the external bus and core power supplies on powerup and the 1N5820 diodes regulate the maximum potential difference on powerdown.

Figure 4. Example Voltage Sequencing Circuit

# 9 Layout Practices

Each  $V_{DD}$  pin on the MPC866/859 should be provided with a low-impedance path to the board's supply. Furthermore, each GND pin should be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1  $\mu$ F bypass capacitors located as close as possible to the four sides of the package. Each board designed should be characterized and additional appropriate decoupling capacitors should be used if required. The capacitor leads and associated printed-circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than 1/2" per capacitor lead. At a minimum, a four-layer board employing two inner layers as  $V_{DD}$  and GND planes should be used.

All output pins on the MPC866/859 have fast rise and fall times. Printed-circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times.

| Num  | Ohavastavistia                                                                                                                                                   | 33   | MHz   | 40   | MHz   | 50 I | MHz   | 66 MHz |       | 11   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                   | Min  | Max   | Min  | Мах   | Min  | Max   | Min    | Мах   | Unit |

| B1d  | CLKOUT phase jitter peak-to-peak for OSCLK $\geq$ 15 MHz                                                                                                         |      | 4     |      | 4     |      | 4     |        | 4     | ns   |

|      | CLKOUT phase jitter peak-to-peak<br>for OSCLK < 15 MHz                                                                                                           | _    | 5     |      | 5     | _    | 5     |        | 5     | ns   |

| B2   | CLKOUT pulse width low (MIN = 0.4 x<br>B1, MAX = 0.6 x B1)                                                                                                       | 12.1 | 18.2  | 10.0 | 15.0  | 8.0  | 12.0  | 6.1    | 9.1   | ns   |

| B3   | CLKOUT pulse width high (MIN = $0.4 \text{ x}$<br>B1, MAX = $0.6 \text{ x}$ B1)                                                                                  | 12.1 | 18.2  | 10.0 | 15.0  | 8.0  | 12.0  | 6.1    | 9.1   | ns   |

| B4   | CLKOUT rise time                                                                                                                                                 |      | 4.00  |      | 4.00  | -    | 4.00  |        | 4.00  | ns   |

| B5   | CLKOUT fall time                                                                                                                                                 | _    | 4.00  | _    | 4.00  | _    | 4.00  | _      | 4.00  | ns   |

| B7   | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3)<br>output hold (MIN = 0.25 x B1)                                                              | 7.60 |       | 6.30 |       | 5.00 |       | 3.80   |       | ns   |

| B7a  | CLKOUT to TSIZ(0:1), $\overline{\text{REG}}$ , $\overline{\text{RSV}}$ ,<br>AT(0:3), $\overline{\text{BDIP}}$ , PTR output hold (MIN = 0.25 x B1)                | 7.60 | _     | 6.30 | _     | 5.00 | _     | 3.80   | _     | ns   |

| B7b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , FRZ, VFLS(0:1),<br>VF(0:2), IWP(0:2), LWP(0:1), $\overline{STS}$<br>output hold (MIN = 0.25 x B1)                  | 7.60 | —     | 6.30 | _     | 5.00 | —     | 3.80   | _     | ns   |

| B8   | CLKOUT to A(0:31), BADDR(28:30)<br>RD/WR, BURST, D(0:31), DP(0:3),<br>valid (MAX = 0.25 x B1 + 6.3)                                                              | _    | 13.80 |      | 12.50 | _    | 11.30 |        | 10.00 | ns   |

| B8a  | CLKOUT to TSIZ(0:1), REG, RSV,<br>AT(0:3), BDIP, PTR valid (MAX = 0.25<br>x B1 + 6.3)                                                                            |      | 13.80 |      | 12.50 |      | 11.30 |        | 10.00 | ns   |

| B8b  | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , VFLS(0:1),<br>VF(0:2), IWP(0:2), FRZ, LWP(0:1),<br>STS valid <sup>4</sup> (MAX = 0.25 x B1 + 6.3)                  |      | 13.80 |      | 12.50 |      | 11.30 |        | 10.00 | ns   |

| B9   | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3),<br>TSIZ(0:1), REG, RSV, AT(0:3), PTR<br>High-Z (MAX = 0.25 x B1 + 6.3)                       | 7.60 | 13.80 | 6.30 | 12.50 | 5.00 | 11.30 | 3.80   | 10.00 | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion (MAX = 0.25 x B1 + 6.0)                                                                                    | 7.60 | 13.60 | 6.30 | 12.30 | 5.00 | 11.00 | 3.80   | 9.80  | ns   |

| B11a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ assertion (when<br>driven by the memory controller or<br>PCMCIA interface) (MAX = 0.00 x B1 +<br>9.30 <sup>1</sup> ) | 2.50 | 9.30  | 2.50 | 9.30  | 2.50 | 9.30  | 2.50   | 9.80  | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation (MAX = 0.25 x B1 + 4.8)                                                                                     | 7.60 | 12.30 | 6.30 | 11.00 | 5.00 | 9.80  | 3.80   | 8.50  | ns   |

| Num  | Chavastavistia                                                                                                                                                                | 33   | MHz   | 40   | MHz   | 50   | MHz   | 66   | MHz   | Unit |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|-------|------|-------|------|

| Num  | Characteristic                                                                                                                                                                | Min  | Max   | Min  | Max   | Min  | Max   | Min  | Мах   | Unit |

| B12a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ negation (when<br>driven by the memory controller or<br>PCMCIA interface) (MAX = 0.00 x B1 +<br>9.00)                             | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00  | ns   |

| B13  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ High-Z (MIN = 0.25 x B1)                                                                                                          | 7.60 | 21.60 | 6.30 | 20.30 | 5.00 | 19.00 | 3.80 | 14.00 | ns   |

| B13a | CLKOUT to $\overline{TA}$ , $\overline{BI}$ High-Z (when driven<br>by the memory controller or PCMCIA<br>interface) (MIN = 0.00 x B1 + 2.5)                                   | 2.50 | 15.00 | 2.50 | 15.00 | 2.50 | 15.00 | 2.50 | 15.00 | ns   |

| B14  | CLKOUT to TEA assertion (MAX = 0.00 x B1 + 9.00)                                                                                                                              | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00  | 2.50 | 9.00  | ns   |

| B15  | CLKOUT to $\overline{\text{TEA}}$ High-Z (MIN = 0.00 x B1 + 2.50)                                                                                                             | 2.50 | 15.00 | 2.50 | 15.00 | 2.50 | 15.00 | 2.50 | 15.00 | ns   |

| B16  | $\overline{TA}$ , $\overline{BI}$ valid to CLKOUT (setup time)<br>(MIN = 0.00 x B1 + 6.00)                                                                                    | 6.00 | -     | 6.00 | —     | 6.00 | —     | 6.00 | —     | ns   |

| B16a | TEA, KR, RETRY, CR valid to CLKOUT<br>(setup time) (MIN = 0.00 x B1 + 4.5)                                                                                                    | 4.50 | _     | 4.50 | _     | 4.50 | _     | 4.50 | —     | ns   |

| B16b | $\overline{\text{BB}}$ , $\overline{\text{BG}}$ , $\overline{\text{BR}}$ , valid to CLKOUT (setup time) <sup>2</sup> (4 MIN = 0.00 x B1 + 0.00 )                              | 4.00 | —     | 4.00 | —     | 4.00 | _     | 4.00 | —     | ns   |

| B17  | CLKOUT to $\overline{TA}$ , $\overline{TEA}$ , $\overline{BI}$ , $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ valid (hold time) (MIN = 0.00 x B1 + 1.00 <sup>3</sup> ) | 1.00 | —     | 1.00 | _     | 1.00 | —     | 2.00 | _     | ns   |

| B17a | CLKOUT to $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid (hold time) (MIN = 0.00 x B1 + 2.00)                                              | 2.00 | —     | 2.00 | —     | 2.00 | _     | 2.00 | —     | ns   |

| B18  | D(0:31), DP(0:3) valid to CLKOUT<br>rising edge (setup time) $^{4}$ (MIN = 0.00<br>x B1 + 6.00)                                                                               | 6.00 | _     | 6.00 | _     | 6.00 | —     | 6.00 | —     | ns   |

| B19  | CLKOUT rising edge to D(0:31),<br>DP(0:3) valid (hold time) $^{4}$ (MIN = 0.00<br>x B1 + 1.00 $^{5}$ )                                                                        | 1.00 | _     | 1.00 | _     | 1.00 | _     | 2.00 | _     | ns   |

| B20  | D(0:31), DP(0:3) valid to CLKOUT<br>falling edge (setup time) $^{6}$ (MIN = 0.00<br>x B1 + 4.00)                                                                              | 4.00 | —     | 4.00 | —     | 4.00 | —     | 4.00 | —     | ns   |

| B21  | CLKOUT falling edge to D(0:31),<br>DP(0:3) valid (hold Time) $^{6}$ (MIN = 0.00<br>x B1 + 2.00)                                                                               | 2.00 | —     | 2.00 | —     | 2.00 | —     | 2.00 | —     | ns   |

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted<br>GPCM ACS = 00 (MAX = 0.25 x B1 + 6.3)                                                                                       | 7.60 | 13.80 | 6.30 | 12.50 | 5.00 | 11.30 | 3.80 | 10.00 | ns   |

| B22a | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0 (MAX = 0.00 x B1 + 8.00)                                                                           |      | 8.00  |      | 8.00  |      | 8.00  |      | 8.00  | ns   |

|      | Ohann sharia tia                                                                                                                                                          | 33    | MHz   | 40 I  | MHz   | 50 I  | MHz   | 66 MHz |       |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                            | Min   | Max   | Min   | Мах   | Min   | Max   | Min    | Max   | Unit |

| B22b | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0, EBDF = 0<br>(MAX = 0.25 x B1 + 6.3)                                                           | 7.60  | 13.80 | 6.30  | 12.50 | 5.00  | 11.30 | 3.80   | 10.00 | ns   |

| B22c | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0, EBDF = 1<br>(MAX = 0.375 x B1 + 6.6)                                                          | 10.90 | 18.00 | 10.90 | 16.00 | 7.00  | 14.10 | 5.20   | 12.30 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated<br>GPCM read access, GPCM write<br>access ACS = 00, TRLX = 0 & CSNT =<br>0 (MAX = 0.00 x B1 + 8.00)                         | 2.00  | 8.00  | 2.00  | 8.00  | 2.00  | 8.00  | 2.00   | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 0<br>(MIN = 0.25 x B1 - 2.00)                                                               | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80   | _     | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 11, TRLX = 0<br>(MIN = 0.50 x B1 - 2.00)                                                               | 13.20 | —     | 10.50 | —     | 8.00  | —     | 5.60   | —     | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}(0:3)$<br>asserted (MAX = 0.00 x B1 + 9.00)                                                                         | —     | 9.00  | —     | 9.00  |       | 9.00  |        | 9.00  | ns   |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated (MAX = 0.00 x B1 + 9.00)                                                                                                    | 2.00  | 9.00  | 2.00  | 9.00  | 2.00  | 9.00  | 2.00   | 9.00  | ns   |

| B27  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 1<br>(MIN = 1.25 x B1 - 2.00)                                                               | 35.90 | _     | 29.30 | —     | 23.00 | —     | 16.90  | _     | ns   |

| B27a | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 11, TRLX = 1<br>(MIN = 1.50 x B1 - 2.00)                                                               | 43.50 | —     | 35.50 | _     | 28.00 | _     | 20.70  | _     | ns   |

| B28  | CLKOUT rising edge to $\overline{WE}(0:3)$<br>negated GPCM write access CSNT =<br>0 (MAX = 0.00 x B1 + 9.00)                                                              | —     | 9.00  | —     | 9.00  | _     | 9.00  | —      | 9.00  | ns   |

| B28a | CLKOUT falling edge to $\overline{WE}(0:3)$<br>negated GPCM write access TRLX = 0,1, CSNT = 1, EBDF = 0 (MAX = 0.25 x B1 + 6.80)                                          | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80   | 10.50 | ns   |

| B28b | CLKOUT falling edge to $\overline{CS}$ negated<br>GPCM write access TRLX = 0,1,<br>CSNT = 1, ACS = 10 or ACS = 11,<br>EBDF = 0 (MAX = 0.25 x B1 + 6.80)                   | _     | 14.30 | _     | 13.00 | _     | 11.80 | _      | 10.50 | ns   |

| B28c | CLKOUT falling edge to $\overline{WE}(0:3)$<br>negated GPCM write access TRLX =<br>0, CSNT = 1 write access TRLX = 0,1,<br>CSNT = 1, EBDF = 1 (MAX = 0.375 x<br>B1 + 6.6) | 10.90 | 18.00 | 10.90 | 18.00 | 7.00  | 14.30 | 5.20   | 12.30 | ns   |

| Niumo | Characteristic                                                                                                                                                          | 33    | MHz   | 40    | MHz   | MHz 50 MHz |       |      | 66 MHz |      |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------------|-------|------|--------|------|

| Num   | Characteristic                                                                                                                                                          | Min   | Max   | Min   | Мах   | Min        | Max   | Min  | Мах    | Unit |

| B31d  | CLKOUT falling edge to $\overline{CS}$ valid, as<br>requested by control bit CST1 in the<br>corresponding word in the UPM EBDF<br>= 1 (MAX = 0.375 x B1 + 6.6)          | 13.30 | 18.00 | 11.30 | 16.00 | 9.40       | 14.10 | 7.60 | 12.30  | ns   |

| B32   | CLKOUT falling edge to $\overline{BS}$ valid, as<br>requested by control bit BST4 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 6.00)                   | 1.50  | 6.00  | 1.50  | 6.00  | 1.50       | 6.00  | 1.50 | 6.00   | ns   |

| B32a  | CLKOUT falling edge to $\overline{\text{BS}}$ valid, as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF<br>= 0 (MAX = 0.25 x B1 + 6.80)  | 7.60  | 14.30 | 6.30  | 13.00 | 5.00       | 11.80 | 3.80 | 10.50  | ns   |

| B32b  | CLKOUT rising edge to $\overline{BS}$ valid, as<br>requested by control bit BST2 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 8.00)                    | 1.50  | 8.00  | 1.50  | 8.00  | 1.50       | 8.00  | 1.50 | 8.00   | ns   |

| B32c  | CLKOUT rising edge to $\overline{BS}$ valid, as<br>requested by control bit BST3 in the<br>corresponding word in the UPM (MAX<br>= 0.25 x B1 + 6.80)                    | 7.60  | 14.30 | 6.30  | 13.00 | 5.00       | 11.80 | 3.80 | 10.50  | ns   |

| B32d  | CLKOUT falling edge to $\overline{\text{BS}}$ valid- as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF<br>= 1 (MAX = 0.375 x B1 + 6.60) | 13.30 | 18.00 | 11.30 | 16.00 | 9.40       | 14.10 | 7.60 | 12.30  | ns   |

| B33   | CLKOUT falling edge to $\overline{\text{GPL}}$ valid, as<br>requested by control bit GxT4 in the<br>corresponding word in the UPM (MAX<br>= 0.00 x B1 + 6.00)           | 1.50  | 6.00  | 1.50  | 6.00  | 1.50       | 6.00  | 1.50 | 6.00   | ns   |

| B33a  | CLKOUT rising edge to $\overline{\text{GPL}}$ valid, as<br>requested by control bit GxT3 in the<br>corresponding word in the UPM (MAX<br>= 0.25 x B1 + 6.80)            | 7.60  | 14.30 | 6.30  | 13.00 | 5.00       | 11.80 | 3.80 | 10.50  | ns   |

| B34   | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid, as requested by control bit CST4 in the corresponding word in the UPM (MIN = 0.25 x B1 - 2.00)             | 5.60  | _     | 4.30  | _     | 3.00       | _     | 1.80 | _      | ns   |

| B34a  | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{CS}$ valid, as requested by control bit<br>CST1 in the corresponding word in the<br>UPM (MIN = 0.50 x B1 - 2.00)    | 13.20 | _     | 10.50 | _     | 8.00       | _     | 5.60 | _      | ns   |

| B34b  | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid, as requested by CST2 in the corresponding word in UPM (MIN = 0.75 x B1 - 2.00)                             | 20.70 | _     | 16.70 |       | 13.00      |       | 9.40 | _      | ns   |

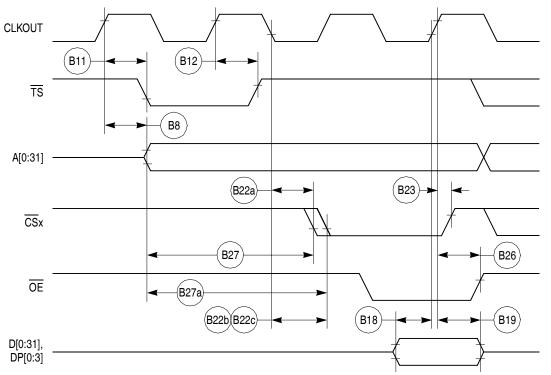

Figure 15. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10, ACS = 11)

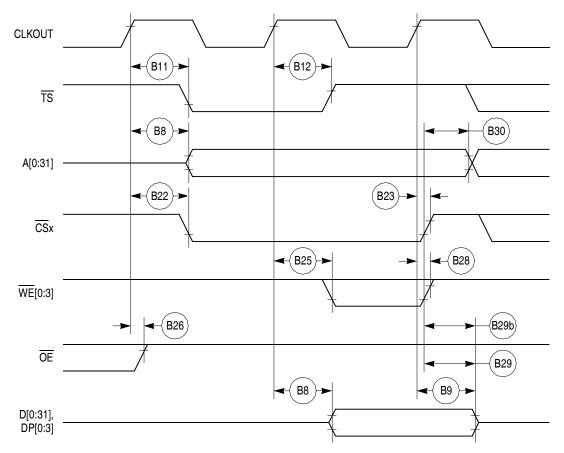

Figure 16 through Figure 18 show the timing for the external bus write controlled by various GPCM factors.

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 0)

Table 12 shows the PCMCIA port timing for the MPC866/859.

| Num | Characteristic                                                  | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-----|-----------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

|     | Gharacteristic                                                  | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

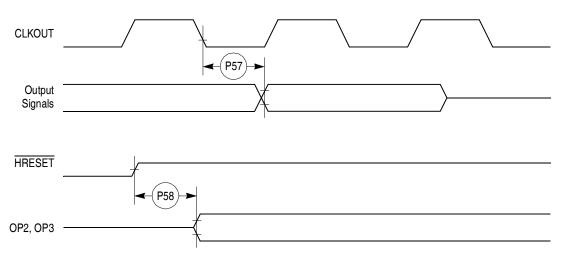

| P57 | CLKOUT to OPx, valid (MAX = 0.00 x B1<br>+ 19.00)               | _      | 19.00 | _      | 19.00 | _      | 19.00 | —      | 19.00 | ns   |

| P58 | HRESET negated to OPx drive $^{1}$ (MIN = 0.75 x B1 + 3.00)     | 25.70  |       | 21.70  |       | 18.00  |       | 14.40  |       | ns   |

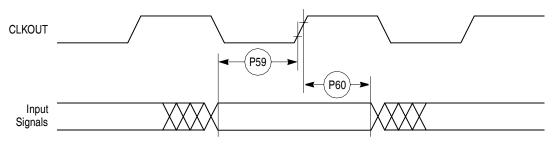

| P59 | IP_Xx valid to CLKOUT rising edge (MIN<br>= 0.00 x B1 + 5.00)   | 5.00   | _     | 5.00   | _     | 5.00   | _     | 5.00   | _     | ns   |

| P60 | CLKOUT rising edge to IP_Xx invalid<br>(MIN = 0.00 x B1 + 1.00) | 1.00   |       | 1.00   |       | 1.00   |       | 1.00   |       | ns   |

Table 12. PCMCIA Port Timing

OP2 and OP3 only.

1

Figure 30 shows the PCMCIA output port timing for the MPC866/859.

## Figure 30. PCMCIA Output Port Timing

Figure 31 shows the PCMCIA output port timing for the MPC866/859.

Figure 31. PCMCIA Input Port Timing

MPC866/MPC859 Hardware Specifications, Rev. 2

**CPM Electrical Characteristics**

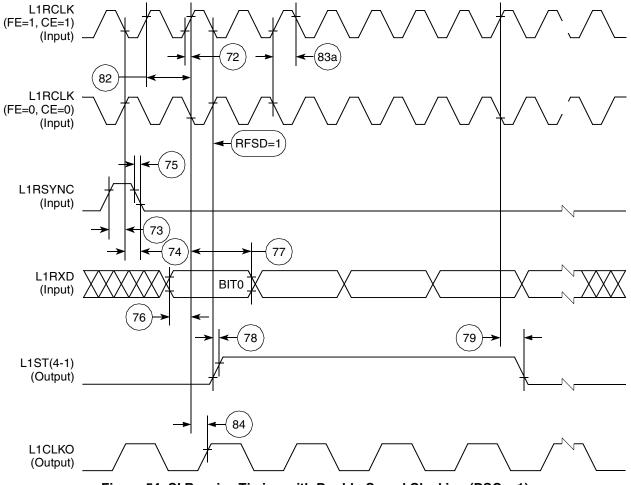

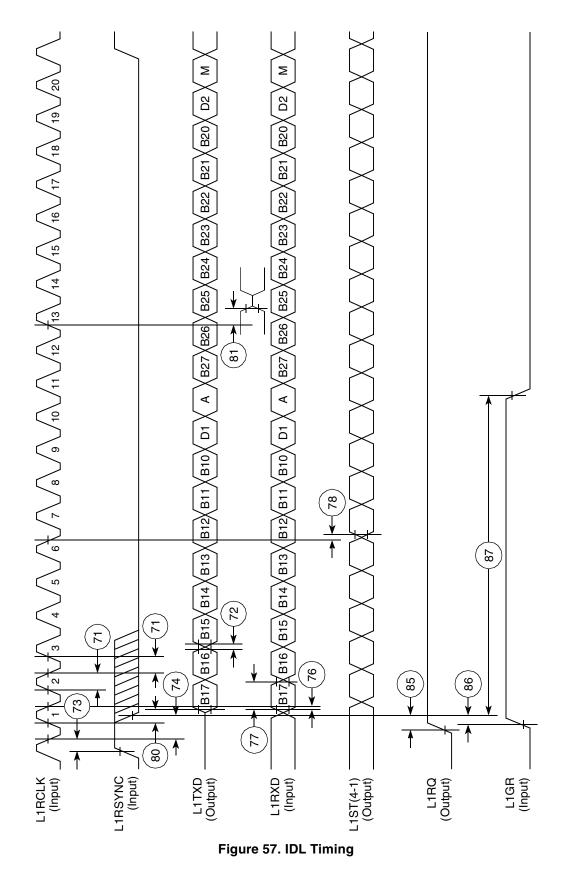

Figure 54. SI Receive Timing with Double-Speed Clocking (DSC = 1)

#### **CPM Electrical Characteristics**

MPC866/MPC859 Hardware Specifications, Rev. 2

# 12.7 SCC in NMSI Mode Electrical Specifications

Table 22 shows the NMSI external clock timings.

| Num | Characteristic                                       | All Frequencie | Unit  |      |

|-----|------------------------------------------------------|----------------|-------|------|

| Num | Characteristic                                       | Min            | Max   | Unit |

| 100 | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK      | -     | ns   |

| 101 | RCLK1 and TCLK1 width low                            | 1/SYNCCLK +5   | —     | ns   |

| 102 | RCLK1 and TCLK1 rise/fall time                       | _              | 15.00 | ns   |

| 103 | TXD1 active delay (from TCLK1 falling edge)          | 0.00           | 50.00 | ns   |

| 104 | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00           | 50.00 | ns   |

| 105 | CTS1 setup time to TCLK1 rising edge                 | 5.00           | _     | ns   |

| 106 | RXD1 setup time to RCLK1 rising edge                 | 5.00           | —     | ns   |

| 107 | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00           | _     | ns   |

| 108 | CD1 setup time to RCLK1 rising edge                  | 5.00           | —     | ns   |

## Table 22. NMSI External Clock Timings

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

Table 23 shows the NMSI internal clock timings.

## Table 23. NMSI Internal Clock Timings

| Num   | Characteristic                                       | All Fr | Unit      |      |

|-------|------------------------------------------------------|--------|-----------|------|

| Nulli | Characteristic                                       | Min    | Max       | Onit |

| 100   | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00   | SYNCCLK/3 | MHz  |

| 102   | RCLK1 and TCLK1 rise/fall time                       |        | _         | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00   | 30.00     | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00   | 30.00     | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 40.00  | _         | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 40.00  | _         | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00   | _         | ns   |

| 108   | CD1 setup time to RCLK1 rising edge                  | 40.00  | _         | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

## **CPM Electrical Characteristics**

| Num                 | Characteristic                               | All Freq | Unit |      |  |

|---------------------|----------------------------------------------|----------|------|------|--|

| Nulli               | Characteristic                               | Min      | Мах  | onit |  |

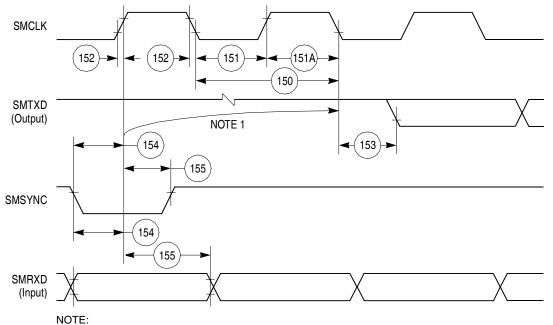

| 150                 | SMCLK clock period <sup>1</sup>              | 100      | _    | ns   |  |

| 151                 | SMCLK width low                              | 50       | _    | ns   |  |

| 151A                | SMCLK width high                             | 50       | _    | ns   |  |

| 152                 | SMCLK rise/fall time                         | —        | 15   | ns   |  |

| 153                 | SMTXD active delay (from SMCLK falling edge) | 10       | 50   | ns   |  |

| 154                 | SMRXD/SMSYNC setup time                      | 20       | —    | ns   |  |

| 155                 | RXD1/SMSYNC hold time                        | 5        | _    | ns   |  |

| <sup>1</sup> Svnc ( | CLK must be at least twice as fast as SMCLK. | •        |      | •    |  |

# Table 25. SMC Transparent Timing

Sync CLK must be at least twice as fast as SMCLK.

1. This delay is equal to an integer number of character-length clocks.

## Figure 66. SMC Transparent Timing Diagram

#### **CPM Electrical Characteristics**

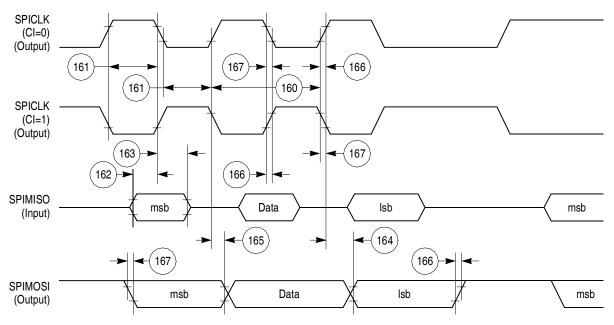

Figure 68. SPI Master (CP = 1) Timing Diagram

# **12.11SPI Slave AC Electrical Specifications**

Table 27 shows the SPI slave timings as shown in Figure 69 and Figure 70.

| Num   | Characteristic                                              | All Freq | Unit |                  |

|-------|-------------------------------------------------------------|----------|------|------------------|

| Nulli | Characteristic                                              | Min      | Max  | Omt              |

| 170   | Slave cycle time                                            | 2        | _    | t <sub>cyc</sub> |

| 171   | Slave enable lead time                                      | 15       | _    | ns               |

| 172   | Slave enable lag time                                       | 15       | _    | ns               |

| 173   | Slave clock (SPICLK) high or low time                       | 1        | _    | t <sub>cyc</sub> |

| 174   | Slave sequential transfer delay (does not require deselect) | 1        | _    | t <sub>cyc</sub> |

| 175   | Slave data setup time (inputs)                              | 20       | _    | ns               |

| 176   | Slave data hold time (inputs)                               | 20       | _    | ns               |

| 177   | Slave access time                                           | _        | 50   | ns               |

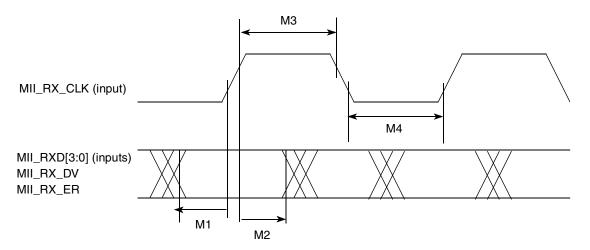

Figure 74. MII Receive Signal Timing Diagram

# 14.2 MII Transmit Signal Timing (MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER, MII\_TX\_CLK)

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency - 1%.

Table 34 shows information on the MII transmit signal timing.

| Table 34. | MII | Transmit | Signal | Timing |

|-----------|-----|----------|--------|--------|

|-----------|-----|----------|--------|--------|

| Num | Characteristic                                           | Min | Max | Unit              |

|-----|----------------------------------------------------------|-----|-----|-------------------|

| M5  | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER invalid | 5   | _   | ns                |

| M6  | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER valid   | —   | 25  | _                 |

| M7  | MII_TX_CLK pulse width high                              | 35% | 65% | MII_TX_CLK period |

| M8  | MII_TX_CLK pulse width low                               | 35% | 65% | MII_TX_CLK period |

#### **FEC Electrical Characteristics**

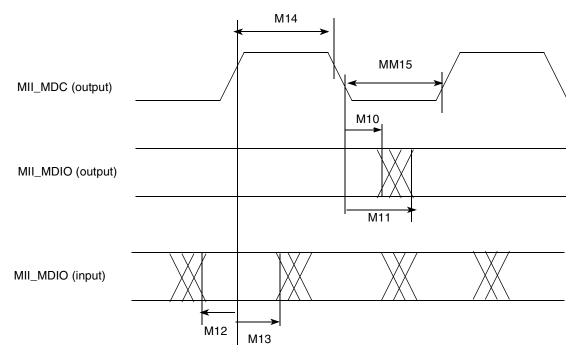

| Num | Characteristic                               | Min | Max | Unit           |

|-----|----------------------------------------------|-----|-----|----------------|

| M13 | MII_MDIO (input) to MII_MDC rising edge hold | 0   | —   | ns             |

| M14 | MII_MDC pulse width high                     | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low                      | 40% | 60% | MII_MDC period |

Figure 77 shows the MII serial management channel timing diagram.

Figure 77. MII Serial Management Channel Timing Diagram

Mechanical Data and Ordering Information

# **15.1 Pin Assignments**

Figure 78 shows the top view pinout of the PBGA package. For additional information, see the *MPC866 PowerQUICC Family User's Manual*.

| <i>(</i>  |           |           |           |            |                        |            |            |            |            |            |            |            |                   |            |                        |              |               |              |        |

|-----------|-----------|-----------|-----------|------------|------------------------|------------|------------|------------|------------|------------|------------|------------|-------------------|------------|------------------------|--------------|---------------|--------------|--------|

|           | O<br>PD10 | O<br>PD8  | O<br>PD3  |            |                        | O<br>D4    | ()<br>D1   | ()<br>D2   | )<br>D3    | ()<br>D5   |            | ()<br>D6   | ()<br>D7          | )<br>D29   | O<br>DP2               |              |               |              | w      |

| O<br>PD14 | O<br>PD13 | O<br>PD9  | O<br>PD6  | O<br>M_Tx_ |                        | 0<br>5 D13 | ()<br>D27  | 〇<br>D10   | ()<br>D14  | )<br>D18   | 〇<br>D20   | 〇<br>D24   | ()<br>D28         | O<br>DP1   | O<br>DP3               | O<br>DP0     | )<br>N/C \    |              | v<br>1 |

| O<br>PA0  | 〇<br>PB14 | O<br>PD15 | O<br>PD4  | O<br>PD5   |                        | ()<br>D8   | ()<br>D23  | 〇<br>D11   | 〇<br>D16   | )<br>D19   | 〇<br>D21   | 〇<br>D26   | )<br>D30          | O<br>IPA5  | O<br>IPA4              | O<br>IPA2    | ⊖<br>N/C      |              | U      |

| O<br>PA1  | O<br>PC5  | O<br>PC4  | O<br>PD11 | O<br>PD7   |                        | )<br>H D12 | ()<br>D17  | O<br>D9    | ()<br>D15  | )<br>D22   | )<br>D25   | )<br>D31   | O<br>IPA6         |            | O<br>IPA1              | O<br>IPA7    | ⊖<br>N/C      |              | T      |

| O<br>PC6  | 0<br>PA2  | ⊖<br>₽B15 | O<br>PD12 | 0          |                        | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0                 | O<br>VDDH  |                        |              |               |              | R      |

| O<br>PA4  | O<br>PB17 | O<br>PA3  |           | $\bigcirc$ | $\left( \circ \right)$ | )<br>GND   | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |                   | 0          |                        |              |               | C<br>ET XTAL | Ρ      |

| O<br>PB19 | O<br>PA5  | )<br>PB18 | O<br>PB16 | $\bigcirc$ | 0                      | $\bigcirc$ | 0          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 0                 | 0          |                        |              |               |              | Ν      |

| O<br>PA7  | 0<br>PC8  | )<br>PA6  | O<br>PC7  | $\bigcirc$ | 0                      | $\bigcirc$        | $\bigcirc$ |                        | BADDR28      |               | O<br>R29 VDD | M      |

| O<br>PB22 | O<br>PC9  | )<br>PA8  | O<br>PB20 | $\bigcirc$ | 0                      | $\bigcirc$        | 0          | О<br>ОР0               |              | O<br>OP1      |              | L      |

| O<br>PC10 | 0<br>PA9  | O<br>PB23 | O<br>PB21 | $\bigcirc$ | 0                      | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | )<br>GND   | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$        | 0          |                        | 0<br>30 IPB6 |               |              | к      |

| O<br>PC11 | O<br>PB24 | )<br>PA10 | O<br>PB25 | $\bigcirc$ | 0                      | $\bigcirc$        | 0          | O<br>IPB5              | O<br>IPB1    | O<br>IPB2     | O            | J      |

|           |           |           | О<br>тск  | $\bigcirc$ | 0                      | $\bigcirc$ | 0                 | 0          | O<br>M_COL             |              | O<br>IPB0     | O<br>IPB7    | н      |

|           | О<br>тмs  | O<br>TDO  | O<br>PA11 | $\bigcirc$ | 0                      | GND        | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | O<br>GND          | $\bigcirc$ |                        |              | O<br>IPB4     | O<br>IPB3    | G      |

| O<br>PB26 | O<br>PC12 | )<br>PA12 |           | $\bigcirc$ |                        |            | 0          | 0          | 0          | 0          | 0          | 0          |                   |            |                        | ⊖<br>⊤s      |               |              | F      |

| O<br>PB27 | O<br>PC13 | )<br>PA13 | O<br>PB29 | $\bigcirc$ | 0                      | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0                 | 0          | $\bigcirc$<br>CS3      | O<br>BI      | $\bigcirc$ BG |              | Е      |

| O<br>PB28 | O<br>PC14 | O<br>PA14 | O<br>PC15 | ()<br>A8   | O<br>N/C               | ⊖<br>N/C   | ()<br>A15  | ()<br>A19  | ()<br>A25  | ()<br>A18  |            |            | ⊖<br>N/C          |            | $\bigcirc$<br>CS2      |              |               |              | D      |

| O<br>PB30 | O<br>PA15 | O<br>PB31 | ()<br>A3  | ()<br>A9   | ()<br>A12              | ()<br>A16  | ()<br>A20  | )<br>A24   | ()<br>A26  |            |            |            |                   |            | $\frac{\bigcirc}{CS7}$ |              | ⊖<br>TA       |              | С      |

| ()<br>A0  | ()<br>A1  | ()<br>A4  | ()<br>A6  | ()<br>A10  | ()<br>A13              | ()<br>A17  | ()<br>A21  | ()<br>A23  | ()<br>A22  | O<br>TSIZO |            | O<br>M_CRS | $\bigcirc$<br>WE2 |            | $\frac{\bigcirc}{CS5}$ |              |               |              | В      |

|           | ()<br>A2  | ()<br>A5  | ()<br>A7  | ()<br>A11  | ()<br>A14              | ()<br>A27  | ()<br>A29  | )<br>A30   | ()<br>A28  | )<br>A31   |            | BSA2       |                   |            |                        |              |               |              | A      |

| 19        | 18        | 17        | 16        | 15         | 14                     | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6                 | 5          | 4                      | 3            | 2             | 1            |        |

NOTE: This is the top view of the device.

Figure 78. Pinout of the PBGA Package

## Mechanical Data and Ordering Information

| Table 39 | Pin | Assignments | (continued) |

|----------|-----|-------------|-------------|

|----------|-----|-------------|-------------|

| Name                                  | Pin Number | Туре          |

|---------------------------------------|------------|---------------|

| PC7<br>CTS3<br>L1TSYNCB<br>SDACK2     | M16        | Bidirectional |

| PC6<br>CD3<br>L1RSYNCB                | R19        | Bidirectional |

| PC5<br>CTS4<br>L1TSYNCA<br>SDACK1     | Т18        | Bidirectional |

| PC4<br>CD4<br>L1RSYNCA                | T17        | Bidirectional |

| PD15<br>L1TSYNCA<br>MII-RXD3<br>UTPB0 | U17        | Bidirectional |

| PD14<br>L1RSYNCA<br>MII-RXD2<br>UTPB1 | V19        | Bidirectional |

| PD13<br>L1TSYNCB<br>MII-RXD1<br>UTPB2 | V18        | Bidirectional |

| PD12<br>L1RSYNCB<br>MII-MDC<br>UTPB3  | R16        | Bidirectional |

| PD11<br>RXD3<br>MII-TXERR<br>RXENB    | T16        | Bidirectional |

| PD10<br>TXD3<br>MII-RXD0<br>TXENB     | W18        | Bidirectional |

# **16 Document Revision History**

Table 40 lists significant changes between revisions of this document.

#### Table 40. Document Revision History

| Revision<br>Number | Date      | Substantive Changes                                                                                                                                                         |

|--------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                  | 5/2002    | Initial revision                                                                                                                                                            |

| 1                  | 11/2002   | Added the 5-V tolerant pins, new package dimensions, and other changes.                                                                                                     |

| 1.1                | 4/2003    | Added the Spec. B1d and changed spec. B1a. Added the Note Solder sphere composition for MPC866XZP, MPC859DSLZP, and MPC859TZP is 62%Sn 36%Pb 2%Ag to Figure 15-79.          |

| 1.2                | 4/2003    | Added the MPC859P.                                                                                                                                                          |

| 1.3                | 5/2003    | Changed the SPI Master Timing Specs. 162 and 164.                                                                                                                           |

| 1.4                | 7-8/2003  | <ul> <li>Added TxClav and RxClav to PB15 and PC15. Changed B28a through B28d and B29b to show that TRLX can be 0 or 1.</li> <li>Added nontechnical reformatting.</li> </ul> |

| 1.5                | 3/14/2005 | Updated document template.                                                                                                                                                  |

| 2                  | 2/10/2006 | Updated orderable parts table.                                                                                                                                              |

#### How to Reach Us:

Home Page: www.freescale.com

email: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-0047 Japan 0120 191014 +81 3 3440 3569 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@ hibbertgroup.com

MPC866EC Rev. 2 2/2006 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The described product contains a PowerPC processor core. The PowerPC name is a trademark of IBM Corp. and used under license. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006.