Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                              |

| Core Processor                  | MPC8xx                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 100MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                            |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                       |

| Security Features               | -                                                                     |

| Package / Case                  | 357-BBGA                                                              |

| Supplier Device Package         | 357-PBGA (25x25)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc859tzp100a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

13

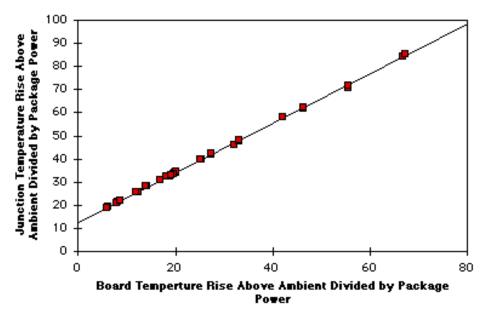

Figure 3. Effect of Board Temperature Rise on Thermal Behavior

If the board temperature is known, an estimate of the junction temperature in the environment can be made using the following equation:

$$T_J = T_B + (R_{\theta JB} \times P_D)$$

where:

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W)

$T_B$  = board temperature °C

$P_D$  = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and vias attaching the thermal balls to the ground plane.

### 7.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two-resistor model can be used with the thermal simulation of the application [2], or a more accurate and complex model of the package can be used in the thermal simulation.

**Table 9. Bus Operation Timings (continued)**

| Num  | Characteristic                                                                                                   | 33   | MHz   | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|------|------------------------------------------------------------------------------------------------------------------|------|-------|--------|-------|--------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                   | Min  | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| B12a | CLKOUT to TA, BI negation (when driven by the memory controller or PCMCIA interface) (MAX = 0.00 x B1 + 9.00)    | 2.50 | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | ns   |

| B13  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ High-Z (MIN = 0.25 x B1)                                             | 7.60 | 21.60 | 6.30   | 20.30 | 5.00   | 19.00 | 3.80   | 14.00 | ns   |

| B13a | CLKOUT to TA, BI High-Z (when driven<br>by the memory controller or PCMCIA<br>interface) (MIN = 0.00 x B1 + 2.5) | 2.50 | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | ns   |

| B14  | CLKOUT to TEA assertion (MAX = 0.00 x B1 + 9.00)                                                                 | 2.50 | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | ns   |

| B15  | CLKOUT to TEA High-Z (MIN = 0.00 x B1 + 2.50)                                                                    | 2.50 | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | ns   |

| B16  | TA, BI valid to CLKOUT (setup time)<br>(MIN = 0.00 x B1 + 6.00)                                                  | 6.00 | _     | 6.00   | _     | 6.00   | _     | 6.00   | _     | ns   |

| B16a | TEA, KR, RETRY, CR valid to CLKOUT (setup time) (MIN = 0.00 x B1 + 4.5)                                          | 4.50 | _     | 4.50   | _     | 4.50   | _     | 4.50   | _     | ns   |

| B16b | BB, BG, BR, valid to CLKOUT (setup time) <sup>2</sup> (4 MIN = 0.00 x B1 + 0.00)                                 | 4.00 | _     | 4.00   | _     | 4.00   | _     | 4.00   | _     | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time) (MIN = 0.00 x B1 + 1.00 <sup>3</sup> )                       | 1.00 | _     | 1.00   | _     | 1.00   | _     | 2.00   | _     | ns   |

| B17a | CLKOUT to $\overline{KR}$ , $\overline{RETRY}$ , $\overline{CR}$ valid (hold time) (MIN = 0.00 x B1 + 2.00)      | 2.00 | _     | 2.00   | _     | 2.00   | _     | 2.00   | _     | ns   |

| B18  | D(0:31), DP(0:3) valid to CLKOUT rising edge (setup time) <sup>4</sup> (MIN = 0.00 x B1 + 6.00)                  | 6.00 | _     | 6.00   | _     | 6.00   | _     | 6.00   | _     | ns   |

| B19  | CLKOUT rising edge to D(0:31),<br>DP(0:3) valid (hold time) $^4$ (MIN = 0.00 x B1 + 1.00 $^5$ )                  | 1.00 | _     | 1.00   | _     | 1.00   | _     | 2.00   | _     | ns   |

| B20  | D(0:31), DP(0:3) valid to CLKOUT falling edge (setup time) $^{6}$ (MIN = 0.00 x B1 + 4.00)                       | 4.00 | _     | 4.00   | _     | 4.00   | _     | 4.00   | _     | ns   |

| B21  | CLKOUT falling edge to D(0:31),<br>DP(0:3) valid (hold Time) <sup>6</sup> (MIN = 0.00<br>x B1 + 2.00)            | 2.00 | _     | 2.00   | _     | 2.00   | _     | 2.00   | _     | ns   |

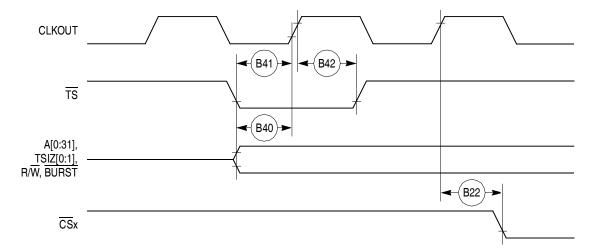

| B22  | CLKOUT rising edge to $\overline{\text{CS}}$ asserted GPCM ACS = 00 (MAX = 0.25 x B1 + 6.3)                      | 7.60 | 13.80 | 6.30   | 12.50 | 5.00   | 11.30 | 3.80   | 10.00 | ns   |

| B22a | CLKOUT falling edge to $\overline{\text{CS}}$ asserted GPCM ACS = 10, TRLX = 0 (MAX = 0.00 x B1 + 8.00)          | _    | 8.00  | _      | 8.00  | _      | 8.00  | _      | 8.00  | ns   |

### **Table 9. Bus Operation Timings (continued)**

| Nivers | Ohawaatawiatia                                                                                                                                                                                                                   | 33 I  | ИНz   | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------|-------|--------|-------|--------|-------|------|--|

| Num    | Characteristic                                                                                                                                                                                                                   | Min   | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |  |

| B30    | CS, WE(0:3) negated to A(0:31),<br>BADDR(28:30) invalid GPCM write<br>access <sup>7</sup> (MIN = 0.25 x B1 – 2.00)                                                                                                               | 5.60  | _     | 4.30   | _     | 3.00   | _     | 1.80   |       | ns   |  |

| B30a   | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM, write access, TRLX = 0, CSNT = 1, CS negated to A(0:31) invalid GPCM write access TRLX = 0, CSNT = 1 ACS = 10, or ACS == 11, EBDF = 0 (MIN = 0.50 x B1 - 2.00)            | 13.20 | _     | 10.50  |       | 8.00   |       | 5.60   | 1     | ns   |  |

| B30b   | WE(0:3) negated to A(0:31) invalid GPCM BADDR(28:30) invalid GPCM write access, TRLX = 1, CSNT = 1. CS negated to A(0:31) invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10, or ACS == 11 EBDF = 0 (MIN = 1.50 x B1 - 2.00) | 43.50 | _     | 35.50  | _     | 28.00  | _     | 20.70  | ı     | ns   |  |

| B30c   | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access, TRLX = 0, CSNT = 1. CS negated to A(0:31) invalid GPCM write access, TRLX = 0, CSNT = 1 ACS = 10, ACS == 11, EBDF = 1 (MIN = 0.375 x B1 - 3.00)              | 8.40  | _     | 6.40   | _     | 4.50   | _     | 2.70   | ı     | ns   |  |

| B30d   | WE(0:3) negated to A(0:31), BADDR(28:30) invalid GPCM write access TRLX = 1, CSNT = 1, CS negated to A(0:31) invalid GPCM write access TRLX = 1, CSNT = 1, ACS = 10 or 11, EBDF = 1                                              | 38.67 | _     | 31.38  | _     | 24.50  | _     | 17.83  | _     | ns   |  |

| B31    | CLKOUT falling edge to CS valid, as requested by control bit CST4 in the corresponding word in the UPM (MAX = 0.00 X B1 + 6.00)                                                                                                  | 1.50  | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | ns   |  |

| B31a   | CLKOUT falling edge to CS valid, as requested by control bit CST1 in the corresponding word in the UPM (MAX = 0.25 x B1 + 6.80)                                                                                                  | 7.60  | 14.30 | 6.30   | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |  |

| B31b   | CLKOUT rising edge to $\overline{\text{CS}}$ valid, as requested by control bit CST2 in the corresponding word in the UPM (MAX = 0.00 x B1 + 8.00)                                                                               | 1.50  | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | ns   |  |

| B31c   | CLKOUT rising edge to $\overline{\text{CS}}$ valid, as requested by control bit CST3 in the corresponding word in the UPM (MAX = 0.25 x B1 + 6.30)                                                                               | 7.60  | 13.80 | 6.30   | 12.50 | 5.00   | 11.30 | 3.80   | 10.00 | ns   |  |

**Table 9. Bus Operation Timings (continued)**

| Nivers | Ohawaatawiatia                                                                                                                                                     | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | 11   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| Num    | Characteristic                                                                                                                                                     | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| B31d   | CLKOUT falling edge to $\overline{\text{CS}}$ valid, as requested by control bit CST1 in the corresponding word in the UPM EBDF = 1 (MAX = 0.375 x B1 + 6.6)       | 13.30  | 18.00 | 11.30  | 16.00 | 9.40   | 14.10 | 7.60   | 12.30 | ns   |

| B32    | CLKOUT falling edge to BS valid, as requested by control bit BST4 in the corresponding word in the UPM (MAX = 0.00 x B1 + 6.00)                                    | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | ns   |

| B32a   | CLKOUT falling edge to BS valid, as requested by control bit BST1 in the corresponding word in the UPM, EBDF = 0 (MAX = 0.25 x B1 + 6.80)                          | 7.60   | 14.30 | 6.30   | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |

| B32b   | CLKOUT rising edge to BS valid, as requested by control bit BST2 in the corresponding word in the UPM (MAX = 0.00 x B1 + 8.00)                                     | 1.50   | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | ns   |

| B32c   | CLKOUT rising edge to BS valid, as requested by control bit BST3 in the corresponding word in the UPM (MAX = 0.25 x B1 + 6.80)                                     | 7.60   | 14.30 | 6.30   | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |

| B32d   | CLKOUT falling edge to BS valid- as requested by control bit BST1 in the corresponding word in the UPM, EBDF = 1 (MAX = 0.375 x B1 + 6.60)                         | 13.30  | 18.00 | 11.30  | 16.00 | 9.40   | 14.10 | 7.60   | 12.30 | ns   |

| B33    | CLKOUT falling edge to GPL valid, as requested by control bit GxT4 in the corresponding word in the UPM (MAX = 0.00 x B1 + 6.00)                                   | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | ns   |

| B33a   | CLKOUT rising edge to GPL valid, as requested by control bit GxT3 in the corresponding word in the UPM (MAX = 0.25 x B1 + 6.80)                                    | 7.60   | 14.30 | 6.30   | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |

| B34    | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid, as requested by control bit CST4 in the corresponding word in the UPM (MIN = 0.25 x B1 - 2.00) | 5.60   | _     | 4.30   | _     | 3.00   | _     | 1.80   | _     | ns   |

| B34a   | A(0:31), BADDR(28:30), and D(0:31) to $\overline{\text{CS}}$ valid, as requested by control bit CST1 in the corresponding word in the UPM (MIN = 0.50 x B1 - 2.00) | 13.20  | _     | 10.50  | _     | 8.00   | _     | 5.60   | _     | ns   |

| B34b   | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid, as requested by CST2 in the corresponding word in UPM (MIN = 0.75 x B1 $-$ 2.00)                      | 20.70  | _     | 16.70  | _     | 13.00  | _     | 9.40   | _     | ns   |

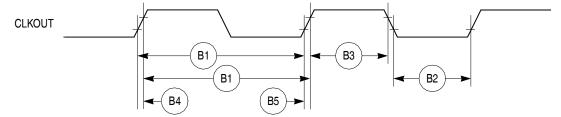

Figure 6 shows the timing for the external clock.

Figure 6. External Clock Timing

Figure 7 shows the timing for the synchronous output signals.

Figure 7. Synchronous Output Signals Timing

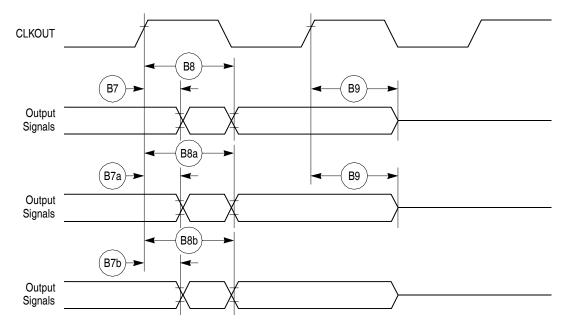

Figure 12 through Figure 15 show the timing for the external bus read controlled by various GPCM factors.

Figure 12. External Bus Read Timing (GPCM Controlled—ACS = 00)

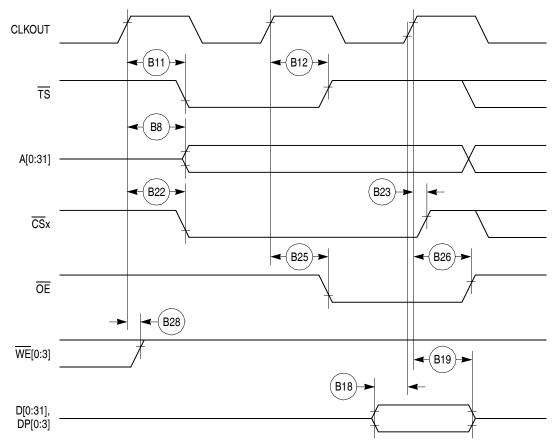

Figure 22 shows the timing for the synchronous external master access controlled by the GPCM.

Figure 22. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

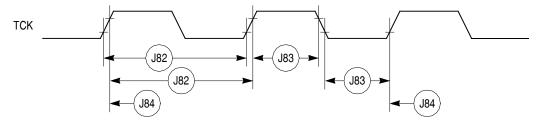

Figure 37. JTAG Test Clock Input Timing

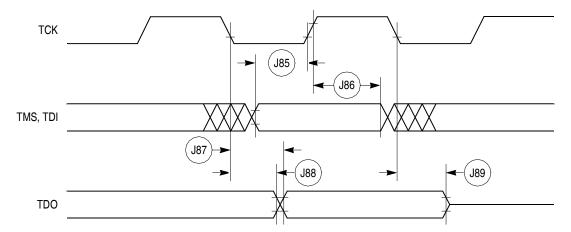

Figure 38. JTAG Test Access Port Timing Diagram

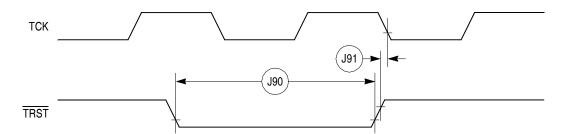

Figure 39. JTAG TRST Timing Diagram

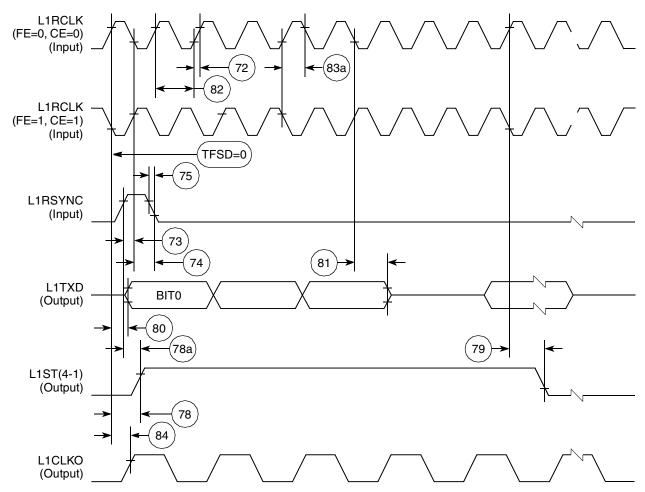

Figure 56. SI Transmit Timing with Double Speed Clocking (DSC = 1)

#### **CPM Electrical Characteristics**

Figure 57. IDL Timing

MPC866/MPC859 Hardware Specifications, Rev. 2

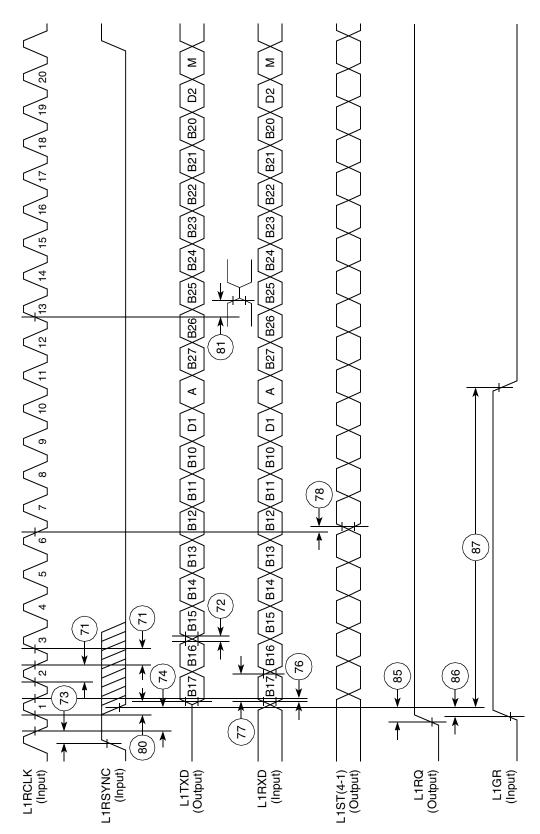

Figure 60. HDLC Bus Timing Diagram

# 12.8 Ethernet Electrical Specifications

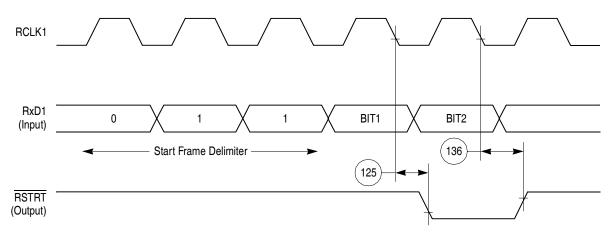

Table 24 shows the Ethernet timings as shown in Figure 61 through Figure 65.

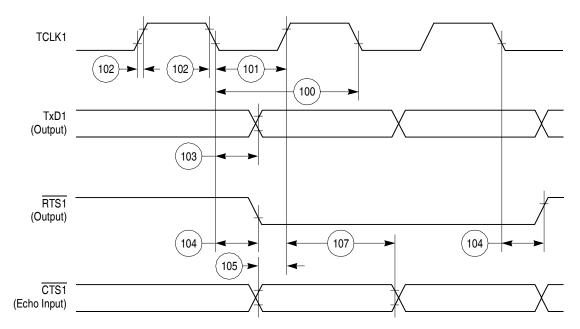

**Table 24. Ethernet Timing**

| Num | Chavastavistis                                                  | All Freq | uencies | Unit  |

|-----|-----------------------------------------------------------------|----------|---------|-------|

| Num | Characteristic                                                  | Min      | Max     | Oilit |

| 120 | CLSN width high                                                 | 40       | _       | ns    |

| 121 | RCLK1 rise/fall time                                            | _        | 15      | ns    |

| 122 | RCLK1 width low                                                 | 40       | _       | ns    |

| 123 | RCLK1 clock period <sup>1</sup>                                 | 80       | 120     | ns    |

| 124 | RXD1 setup time                                                 | 20       | _       | ns    |

| 125 | RXD1 hold time                                                  | 5        | _       | ns    |

| 126 | RENA active delay (from RCLK1 rising edge of the last data bit) | 10       | _       | ns    |

| 127 | RENA width low                                                  | 100      | _       | ns    |

| 128 | TCLK1 rise/fall time                                            | _        | 15      | ns    |

| 129 | TCLK1 width low                                                 | 40       | _       | ns    |

| 130 | TCLK1 clock period <sup>1</sup>                                 | 99       | 101     | ns    |

| 131 | TXD1 active delay (from TCLK1 rising edge)                      | _        | 50      | ns    |

| 132 | TXD1 inactive delay (from TCLK1 rising edge)                    | 6.5      | 50      | ns    |

| 133 | TENA active delay (from TCLK1 rising edge)                      | 10       | 50      | ns    |

#### Notes:

- 1. Transmit clock invert (TCI) bit in GSMR is set.

- If RENA is deasserted before TENA, or RENA is not asserted at all during transmit, then the CSL bit is set in the buffer descriptor at the end of the frame transmission.

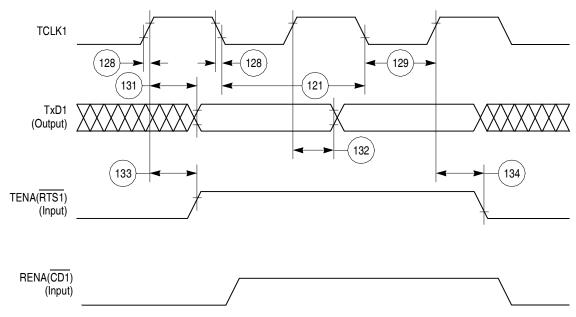

Figure 63. Ethernet Transmit Timing Diagram

Figure 64. CAM Interface Receive Start Timing Diagram

Figure 65. CAM Interface REJECT Timing Diagram

## 12.9 SMC Transparent AC Electrical Specifications

Table 25 shows the SMC transparent timings as shown in Figure 66.

MPC866/MPC859 Hardware Specifications, Rev. 2

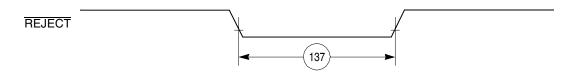

# 12.10SPI Master AC Electrical Specifications

Table 26 shows the SPI master timings as shown in Figure 67 and Figure 68.

**Table 26. SPI Master Timing**

| Num   | Characteristic                      | All Freq | Unit |                  |

|-------|-------------------------------------|----------|------|------------------|

| Nulli | Characteristic                      | Min      | Max  | Oilit            |

| 160   | MASTER cycle time                   | 4        | 1024 | t <sub>cyc</sub> |

| 161   | MASTER clock (SCK) high or low time | 2        | 512  | t <sub>cyc</sub> |

| 162   | MASTER data setup time (inputs)     | 15       | _    | ns               |

| 163   | Master data hold time (inputs)      | 0        | _    | ns               |

| 164   | Master data valid (after SCK edge)  | _        | 10   | ns               |

| 165   | Master data hold time (outputs)     | 0        | _    | ns               |

| 166   | Rise time output                    | _        | 15   | ns               |

| 167   | Fall time output                    | _        | 15   | ns               |

Figure 67. SPI Master (CP = 0) Timing Diagram

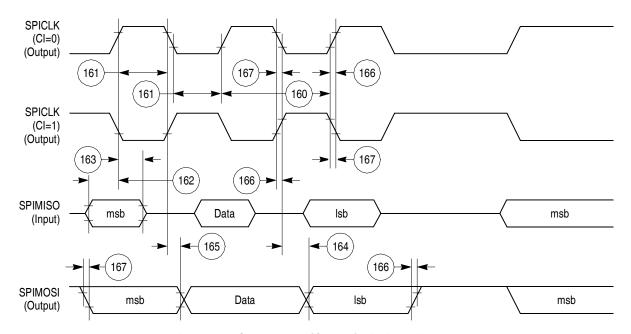

Table 28 shows the  $I^2C$  (SCL < 100 kHz) timings.

Table 28. I<sup>2</sup>C Timing (SCL < 100 kHz)

| Num   | Characteristic                            | All Freq | All Frequencies |      |  |  |

|-------|-------------------------------------------|----------|-----------------|------|--|--|

| Nulli | Characteristic                            | Min      | Max             | Unit |  |  |

| 200   | SCL clock frequency (slave)               | 0        | 100             | kHz  |  |  |

| 200   | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100             | kHz  |  |  |

| 202   | Bus free time between transmissions       | 4.7      | _               | μs   |  |  |

| 203   | Low period of SCL                         | 4.7      | _               | μs   |  |  |

| 204   | High period of SCL                        | 4.0      | _               | μs   |  |  |

| 205   | Start condition setup time                | 4.7      | _               | μs   |  |  |

| 206   | Start condition hold time                 | 4.0      | _               | μs   |  |  |

| 207   | Data hold time                            | 0        | _               | μs   |  |  |

| 208   | Data setup time                           | 250      | _               | ns   |  |  |

| 209   | SDL/SCL rise time                         | _        | 1               | μs   |  |  |

| 210   | SDL/SCL fall time                         | _        | 300             | ns   |  |  |

| 211   | Stop condition setup time                 | 4.7      | _               | μs   |  |  |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

Table 29 shows the  $I^2C$  (SCL > 100 kHz) timings.

Table 29.  $I^2C$  Timing (SCL > 100 kHz)

| Num   | Characteristic                            | Expression | All Freq        | Unit          |      |

|-------|-------------------------------------------|------------|-----------------|---------------|------|

| Nulli | Characteristic                            | Expression | Min             | Max           | Onit |

| 200   | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz   |

| 200   | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz   |

| 202   | Bus free time between transmissions       | _          | 1/(2.2 * fSCL)  | _             | S    |

| 203   | Low period of SCL                         | _          | 1/(2.2 * fSCL)  | _             | S    |

| 204   | High period of SCL                        | _          | 1/(2.2 * fSCL)  | _             | S    |

| 205   | Start condition setup time                | _          | 1/(2.2 * fSCL)  | _             | S    |

| 206   | Start condition hold time                 | _          | 1/(2.2 * fSCL)  | _             | s    |

| 207   | Data hold time                            | _          | 0               | _             | s    |

| 208   | Data setup time                           | _          | 1/(40 * fSCL)   | _             | S    |

| 209   | SDL/SCL rise time                         | _          | _               | 1/(10 * fSCL) | S    |

| 210   | SDL/SCL fall time                         | _          | _               | 1/(33 * fSCL) | S    |

| 211   | Stop condition setup time                 | _          | 1/2(2.2 * fSCL) | _             | S    |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

### MPC866/MPC859 Hardware Specifications, Rev. 2

### **UTOPIA AC Electrical Specifications**

Figure 71 shows the I<sup>2</sup>C bus timing.

Figure 71. I<sup>2</sup>C Bus Timing Diagram

# 13 UTOPIA AC Electrical Specifications

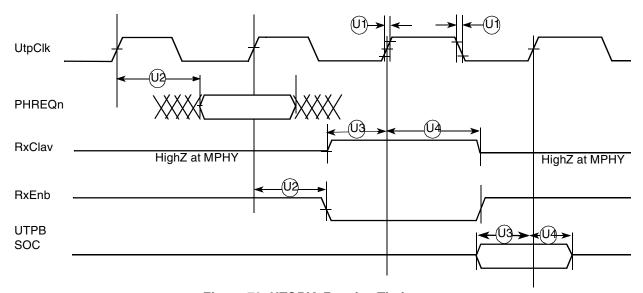

Table 30 through Table 32 show the AC electrical specifications for the UTOPIA interface.

Table 30. UTOPIA Master (Muxed Mode) Electrical Specifications

| Num | Signal Characteristic                                                                                    | Direction | Min | Max | Unit |

|-----|----------------------------------------------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (Internal clock option)                                                            | Output    | _   | 4   | ns   |

|     | Duty cycle                                                                                               |           | 50  | 50  | %    |

|     | Frequency                                                                                                |           | _   | 33  | MHz  |

| U2  | UTPB, SOC, RxEnb, TxEnb, RxAddr, and TxAddr-active delay (and PHREQ and PHSEL active delay in MPHY mode) | Output    | 2   | 16  | ns   |

| U3  | UTPB, SOC, Rxclav and Txclav setup time                                                                  | Input     | 4   | _   | ns   |

| U4  | UTPB, SOC, Rxclav and Txclav hold time                                                                   | Input     | 1   | _   | ns   |

Table 31. UTOPIA Master (Split Bus Mode) Electrical Specifications

| Num | Signal Characteristic                                                                               | Direction | Min | Max | Unit |

|-----|-----------------------------------------------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (Internal clock option)                                                       | Output    | _   | 4   | ns   |

|     | Duty cycle                                                                                          |           | 50  | 50  | %    |

|     | Frequency                                                                                           |           |     | 33  | MHz  |

| U2  | UTPB, SOC, RxEnb, TxEnb, RxAddr and TxAddr active delay (PHREQ and PHSEL active delay in MPHY mode) | Output    | 2   | 16  | ns   |

| U3  | UTPB_Aux, SOC_Aux, Rxclav, and Txclav setup time                                                    | Input     | 4   | _   | ns   |

| U4  | UTPB_Aux, SOC_Aux, Rxclav, and Txclav hold time                                                     | Input     | 1   | _   | ns   |

| Table 32. UTOPI | 4 Slave | (Split | Bus Mo | ode) Elec | ctrical S | pecifications |

|-----------------|---------|--------|--------|-----------|-----------|---------------|

|-----------------|---------|--------|--------|-----------|-----------|---------------|

| Num | Signal Characteristic                                          | Direction | Min | Max | Unit |

|-----|----------------------------------------------------------------|-----------|-----|-----|------|

| U1  | UtpClk rise/fall time (external clock option)                  | Input     | _   | 4   | ns   |

|     | Duty cycle                                                     |           | 40  | 60  | %    |

|     | Frequency                                                      |           | _   | 33  | MHz  |

| U2  | UTPB, SOC, Rxclav and Txclav active delay                      | Output    | 2   | 16  | ns   |

| U3  | UTPB_AUX, SOC_Aux, RxEnb, TxEnb, RxAddr, and TxAddr setup time | Input     | 4   | _   | ns   |

| U4  | UTPB_AUX, SOC_Aux, RxEnb, TxEnb, RxAddr, and TxAddr hold time  | Input     | 1   | _   | ns   |

Figure 72 shows signal timings during UTOPIA receive operations.

Figure 72. UTOPIA Receive Timing

MPC866/MPC859 Hardware Specifications, Rev. 2 73 Freescale Semiconductor

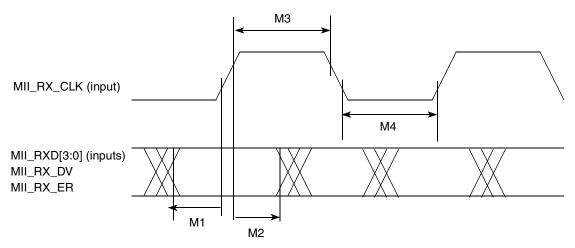

Figure 74. MII Receive Signal Timing Diagram

# 14.2 MII Transmit Signal Timing (MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER, MII\_TX\_CLK)

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency -1%.

Table 34 shows information on the MII transmit signal timing.

Num Characteristic Min Unit Max M5 MII\_TX\_CLK to MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER 5 ns invalid M6 MII\_TX\_CLK to MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER 25 valid М7 MII\_TX\_CLK pulse width high MII\_TX\_CLK period 35% 65% MII\_TX\_CLK pulse width low MII\_TX\_CLK period **M8** 35% 65%

**Table 34. MII Transmit Signal Timing**

### **Mechanical Data and Ordering Information**

### Table 39. Pin Assignments (continued)

| Name                                             | Pin Number | Туре                     |

|--------------------------------------------------|------------|--------------------------|

| UPWAITB<br>GPL_B4                                | B1         | Bidirectional            |

| GPL_A5                                           | D3         | Output                   |

| PORESET                                          | R2         | Input                    |

| RSTCONF                                          | P3         | Input                    |

| HRESET                                           | N4         | Open-drain               |

| SRESET                                           | P2         | Open-drain               |

| XTAL                                             | P1         | Analog Output            |

| EXTAL                                            | N1         | Analog Input (3.3V only) |

| CLKOUT                                           | W3         | Output                   |

| EXTCLK                                           | N2         | Input (3.3V only)        |

| TEXP                                             | N3         | Output                   |

| ALE_A<br>MII-TXD1                                | K2         | Output                   |

| CE1_A<br>MII-TXD2                                | B3         | Output                   |

| CE2_A<br>MII-TXD3                                | A3         | Output                   |

| WAIT_A<br>SOC_Split <sup>2</sup>                 | R3         | Input                    |

| WAIT_B                                           | R4         | Input                    |

| IP_A0<br>UTPB_Split0 <sup>2</sup><br>MII-RXD3    | T5         | Input                    |

| IP_A1<br>UTPB_Split1 <sup>2</sup><br>MII-RXD2    | T4         | Input                    |

| IP_A2 IOIS16_A UTPB_Split2 <sup>2</sup> MII-RXD1 | U3         | Input                    |

| IP_A3<br>UTPB_Split3 <sup>2</sup><br>MII-RXD0    | W2         | Input                    |

| IP_A4<br>UTPB_Split4 <sup>2</sup><br>MII-RXCLK   | U4         | Input                    |

**Mechanical Data and Ordering Information**

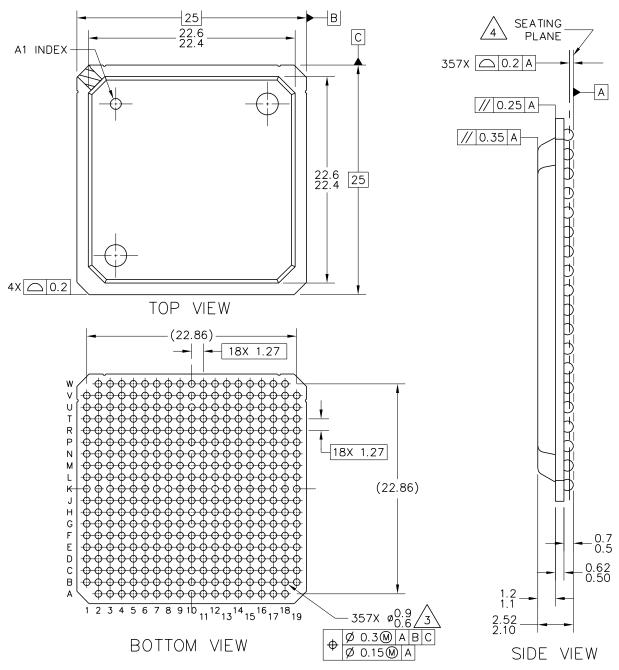

### 15.2 Mechanical Dimensions of the PBGA Package

For more information on the printed-circuit board layout of the PBGA package, including thermal via design and suggested pad layout, please refer to *Plastic Ball Grid Array Application Note* (order number: AN1231/D) available from your local Freescale sales office. Figure 79 shows the mechanical dimensions of the PBGA package.

**Note:** Solder sphere composition for MPC866XZP, MPC859PZP, MPC859DSLZP, and MPC859TZP is 62%Sn 36%Pb 2%Ag

Figure 79. Mechanical Dimensions and Bottom Surface Nomenclature of the PBGA Package

### THIS PAGE INTENTIONALLY LEFT BLANK