Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                         |

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 34                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 12K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x12b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

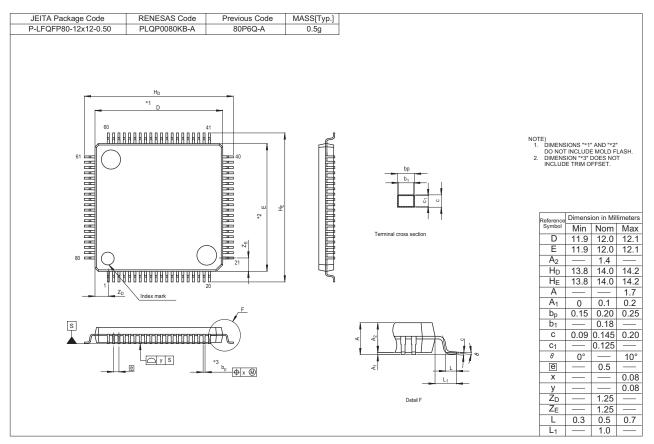

| Package / Case             | 48-LQFP                                                                          |

| Supplier Device Package    | 48-LQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52103bdfl-30 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1.1 Outline of Specifications (2 / 5)

| Classification        | Module/Function                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low power consumption | Low power consumption facilities               | Module stop function     Four low power consumption modes     Sleep mode, all-module clock stop mode, software standby mode, and deep software standby mode                                                                                                                                                                                                                                                                                                             |

|                       | Function for lower operating power consumption | Operating power control modes [Chip versions A and C] High-speed operating mode, middle-speed operating mode 1A, middle-speed operating mode 1B, low-speed operating mode 1, low-speed operating mode 2 [Chip version B] High-speed operating mode, middle-speed operating mode 1A, middle-speed operating mode 1B, middle-speed operating mode 2A, middle-speed operating mode 2B, low-speed operating mode 1, low-speed operating mode 2                              |

| Interrupt             | Interrupt controller (ICUb)                    | <ul> <li>Interrupt vectors: 167</li> <li>External interrupts: 9 (NMI, IRQ0 to IRQ7 pins)</li> <li>Non-maskable interrupts: 6 (the NMI pin, oscillation stop detection interrupt, voltage monitoring 1 interrupt, voltage monitoring 2 interrupt, WDT interrupt, and IWDT interrupt)</li> <li>16 levels specifiable for the order of priority</li> </ul>                                                                                                                 |

| External bus external | nsion                                          | The external address space can be divided into four areas (CS0 to CS3), each with independent control of access settings. Capacity of each area: 16 Mbytes (CS0 to CS3) A chip-select signal (CS0# to CS3#) can be output for each area. Each area is specifiable as an 8-bit or 16-bit bus space The data arrangement in each area is selectable as little or big endian (only for data). Bus format: Separate bus, multiplex bus  Wait control  Write buffer facility |

| DMA                   | DMA controller (DMACA)                         | <ul> <li>4 channels</li> <li>Three transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Software trigger, external interrupts, and interrupt requests from peripheral functions</li> </ul>                                                                                                                                                                                                                                 |

|                       | Data transfer controller (DTCa)                | <ul> <li>Three transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Interrupts</li> <li>Chain transfer function</li> </ul>                                                                                                                                                                                                                                                                                                 |

| I/O ports             | General I/O ports                              | 145-pin/144-pin/100-pin/80-pin/69-pin/64-pin/48-pin  • I/O: 122/122/84/64/48/48/34  • Input: 1/1/1/1/1/1  • Pull-up resistors: 122/122/84/64/48/48/34  • Open-drain outputs: 76/76/54/44/35/35/26  • 5-V tolerance:4/4/4/4/2/2*1/2                                                                                                                                                                                                                                      |

| Event link controll   | er (ELC)                                       | <ul> <li>Event signals of 59 types can be directly connected to the module</li> <li>Operations of timer modules are selectable at event input</li> <li>Capable of event link operation for ports B and E</li> </ul>                                                                                                                                                                                                                                                     |

| Multi-function nin    | controller (MPC)                               | Capable of selecting input/output function from multiple pins                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 1.1 Outline of Specifications (3 / 5)

| Classification | Module/Function                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| īmers          | 16-bit timer pulse unit<br>(TPUa)         | <ul> <li>(16 bits x 6 channels) x 1 unit</li> <li>Maximum of 16 pulse-input/output possible</li> <li>Select from among seven or eight counter-input clock signals for each channel</li> <li>Supports the input capture/output compare function</li> <li>Output of PWM waveforms in up to 15 phases in PWM mode</li> <li>Support for buffered operation, phase-counting mode (two-phase encoder input) and cascade-connected operation (32 bits x 2 channels) depending on the channel.</li> <li>Capable of generating conversion start triggers for the A/D converters</li> <li>Signals from the input capture pins are input via a digital filter</li> <li>Clock frequency measuring method<br/>(Products with 144 or more pins incorporate a TPU.)</li> </ul> |

|                | Multi-function timer pulse unit 2 (MTU2a) | <ul> <li>(16 bits × 6 channels) × 1 unit</li> <li>Up to 16 pulse-input/output lines and three pulse-input lines are available with six 16-bit timer channels</li> <li>Select from among eight or seven counter-input clock signals for each channel (PCLK/1, PCLK/4, PCLK/16, PCLK/64, PCLK/256, PCLK/1024, MTCLKA, MTCLKB, MTCLKC, MTCLKD) other than channel 5, for which only four signals are available.</li> <li>Input capture function</li> <li>21 output compare/input capture registers</li> <li>Pulse output mode</li> <li>Complementary PWM output mode</li> <li>Reset synchronous PWM mode</li> <li>Phase-counting mode</li> <li>Generation of triggers for A/D converter conversion</li> </ul>                                                      |

|                | Port output enable 2 (POE2a)              | Controls the high-impedance state of the MTU's waveform output pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | 8-bit timer (TMR)                         | <ul> <li>(8 bits × 2 channels) × 2 units</li> <li>Select from among seven internal clock signals (PCLK1, PCLK/2, PCLK/8, PCLK/32, PCLK/64, PCLK/1024, PCLK/8192) and one external clock signal</li> <li>Capable of output of pulse trains with desired duty cycles or of PWM signals</li> <li>The 2 channels of each unit can be cascaded to create a 16-bit timer</li> <li>Capable of generating baud-rate clocks for SCI5, SCI6, and SCI12</li> </ul>                                                                                                                                                                                                                                                                                                         |

|                | Compare match timer (CMT)                 | <ul> <li>(16 bits × 2 channels) × 2 units</li> <li>Select from among four clock signals (PCLK/8, PCLK/32, PCLK/128, PCLK/512)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | Watchdog timer (WDTA)                     | <ul> <li>14 bits × 1 channel</li> <li>Select from among six counter-input clock signals (PCLK/4, PCLK/64, PCLK/128, PCLK/512, PCLK/2048, PCLK/8192)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                | Independent watchdog timer (IWDTa)        | <ul> <li>14 bits × 1 channel</li> <li>Counter-input clock: IWDT-dedicated on-chip oscillator<br/>Frequency divided by 1, 16, 32, 64, 128, or 256</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | Realtime clock (RTCb)                     | <ul> <li>Clock source: Sub-clock</li> <li>Time/calendar</li> <li>Interrupt sources: Alarm interrupt, periodic interrupt, and carry interrupt</li> <li>Time-capture facility for three values</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 1.2 Comparison of Functions for Different Packages

|                            |                                        | RX210 Group                                           |                               |                                                                 |                                                                   |                                     |  |  |  |

|----------------------------|----------------------------------------|-------------------------------------------------------|-------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------|--|--|--|

| Module/Function            | ons                                    | 144, 145 Pins                                         | 100 Pins                      | 80 Pins                                                         | 64, 69 Pins                                                       | 48 Pins                             |  |  |  |

| External bus               | External bus width                     | 16                                                    | 16 bits                       |                                                                 | Not supported                                                     |                                     |  |  |  |

| Interrupt                  | External interrupts                    | NMI, IRQ0 to IRQ7                                     |                               |                                                                 | NMI, IRQ0 to<br>IRQ2, IRQ4 to<br>IRQ7                             | NMI, IRQ0,<br>IRQ1, IRQ4 to<br>IRQ7 |  |  |  |

| DMA                        | DMA controller                         |                                                       | DMAC3)                        |                                                                 |                                                                   |                                     |  |  |  |

|                            | Data transfer controller               | Supported                                             |                               |                                                                 |                                                                   |                                     |  |  |  |

| Timers                     | 16-bit timer pulse unit                | 6 channels<br>(TPU0 to<br>TPU5)                       |                               | Not su                                                          | upported                                                          |                                     |  |  |  |

|                            | Multi-function timer pulse unit 2      | 6 channels (MTU0 to MTU5)                             |                               |                                                                 |                                                                   |                                     |  |  |  |

|                            | Port output enable 2                   |                                                       | POE                           | # to POE3#, PO                                                  | OE8#                                                              |                                     |  |  |  |

|                            | 8-bit timer                            |                                                       | 2 (                           | channels × 2 un                                                 | its                                                               |                                     |  |  |  |

|                            | Compare match timer                    |                                                       | 2 (                           | channels x 2 un                                                 | its                                                               |                                     |  |  |  |

|                            | Realtime clock                         |                                                       | Suppo                         | orted                                                           |                                                                   | Not supported                       |  |  |  |

|                            | Watchdog timer                         |                                                       |                               | Supported                                                       |                                                                   |                                     |  |  |  |

| Independent watchdog timer |                                        | Supported                                             |                               |                                                                 |                                                                   |                                     |  |  |  |

| Communication functions    | Serial communications interface (SCIc) | 12 channels 6 channels (SCI0 to 11) (SCI0, 1, 5, 6, 8 |                               |                                                                 | 5 channels<br>(SCI1, 5, 6, 8, 9)                                  | 4 channels<br>(SCI1, 5, 6, 8)       |  |  |  |

|                            | Serial communications interface (SCId) | 1 channel (SCI12)                                     |                               |                                                                 |                                                                   |                                     |  |  |  |

|                            | I <sup>2</sup> C bus interface         | 1 channel                                             |                               |                                                                 |                                                                   |                                     |  |  |  |

|                            | Serial peripheral interface            |                                                       |                               | 1 channel                                                       |                                                                   |                                     |  |  |  |

| 12-bit A/D converter       |                                        |                                                       | annels<br>o AN015)            | 12 channels<br>(AN000 to<br>AN004, AN006,<br>AN008 to<br>AN013) | 8 channels<br>(AN000 to<br>AN002,<br>AN006,<br>AN009 to<br>AN012) |                                     |  |  |  |

| Temperature ser            | nsor                                   |                                                       |                               | Supported                                                       |                                                                   |                                     |  |  |  |

| D/A converter              |                                        |                                                       | 2 chai                        | nnels                                                           |                                                                   | Not supported                       |  |  |  |

| CRC calculator             |                                        |                                                       |                               | Supported                                                       |                                                                   |                                     |  |  |  |

| Event link contro          | oller                                  | Supported                                             |                               |                                                                 |                                                                   |                                     |  |  |  |

| Comparator A               |                                        | 2 channels                                            |                               |                                                                 |                                                                   |                                     |  |  |  |

| Comparator B               |                                        |                                                       |                               | 2 channels                                                      |                                                                   |                                     |  |  |  |

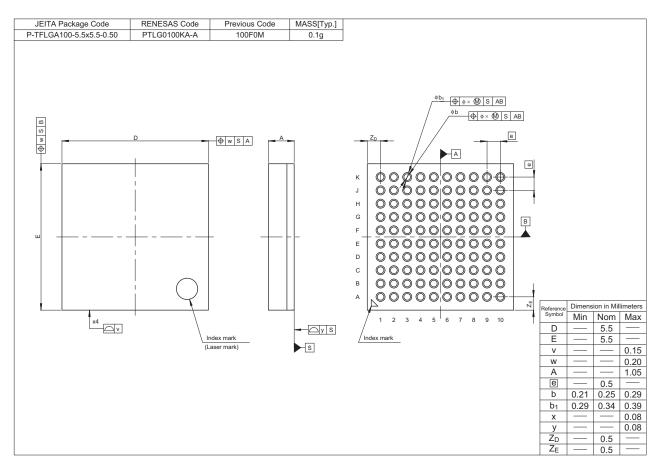

| Packages                   |                                        | 145-pin TFLGA<br>144-pin LQFP                         | 100-pin TFLGA<br>100-pin LQFP | 80-pin LQFP                                                     | 69-pin WLBGA<br>64-pin TFLGA<br>64-pin LQFP                       | 48-pin LQFP                         |  |  |  |

Table 1.8 Pin Functions (4 / 4)

| Classifications     | Pin Name             | I/O   | Description                                                                                                                               |

|---------------------|----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Analog power supply | AVCC0                | Input | Analog voltage supply pin for the 12-bit A/D converter. Connect this pin to VCC if the 12-bit A/D converter is not to be used.            |

|                     | AVSS0                | Input | Analog ground pin for the 12-bit A/D converter. Connect this pin to VSS if the 12-bit A/D converter is not to be used.                    |

|                     | VREFH0               | Input | Analog reference voltage supply pin for the 12-bit A/D converter.  Connect this pin to VCC if the 12-bit A/D converter is not to be used. |

|                     | VREFL0               | Input | Analog reference ground pin for the 12-bit A/D converter. Connect this pin to VSS if the 12-bit A/D converter is not to be used.          |

|                     | VREFH                | Input | Analog voltage supply pin for the D/A converter. Connect this pin to VCC if the D/A converter is not to be used.                          |

|                     | VREFL                | Input | Analog ground pin for the D/A converter. Connect this pin to VSS if the D/A converter is not to be used.                                  |

| I/O ports           | P00 to P03, P05, P07 | I/O   | 6-bit input/output pins.                                                                                                                  |

|                     | P12 to P17           | I/O   | 6-bit input/output pins.                                                                                                                  |

|                     | P20 to P27           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | P30 to P37           | I/O   | 8-bit input/output pins. (P35 input pin)                                                                                                  |

|                     | P40 to P47           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | P50 to P56           | I/O   | 7-bit input/output pins.                                                                                                                  |

|                     | P60 to P67           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | P70 to P77           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | P80 to P83, P86, P87 | I/O   | 6-bit input/output pins.                                                                                                                  |

|                     | P90 to P93           | I/O   | 4-bit input/output pins.                                                                                                                  |

|                     | PA0 to PA7           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | PB0 to PB7           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | PC0 to PC7           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | PD0 to PD7           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | PE0 to PE7           | I/O   | 8-bit input/output pins.                                                                                                                  |

|                     | PF5                  | I/O   | 1-bit input/output pin.                                                                                                                   |

|                     | PH0 to PH3           | I/O   | 4-bit input/output pins.                                                                                                                  |

|                     | PJ1, PJ3, PJ5        | I/O   | 3-bit input/output pins.                                                                                                                  |

|                     | PK2 to PK5           | I/O   | 4-bit input/output pins.                                                                                                                  |

|                     | PL0, PL1             | I/O   | 2-bit input/output pins.                                                                                                                  |

Table 1.9 List of Pins and Pin Functions (145-Pin TFLGA) (4 / 4)

| Pin | Power Supply, Clock, |          |                     | Timers                                | Communications              |        |

|-----|----------------------|----------|---------------------|---------------------------------------|-----------------------------|--------|

| No. | System Control       | I/O Port | <b>External Bus</b> | (MTU, TMR, POE)                       | (SCIc, SCId, RSPI, RIIC)    | Others |

| M11 |                      | PC0      | A16                 | MTIOC3C/TCLKC                         | CTS5#/RTS5#/SS5#/<br>SSLA1  |        |

| M12 |                      | PC1      | A17                 | MTIOC3A/TCLKD                         | SCK5/SSLA2                  |        |

| M13 |                      | PL1      |                     |                                       |                             |        |

| N1  |                      | P21      |                     | MTIOC1B/TMCI0/<br>TIOCA3              | RXD0/SMISO0/SSCL0           |        |

| N2  |                      | P20      |                     | MTIOC1A/TMRI0/<br>TIOCB3              | TXD0/SMOSI0/SSDA0           |        |

| N3  |                      | P87      |                     | TIOCA2                                |                             |        |

| N4  |                      | P14      |                     | MTIOC3A/MTCLKA/<br>TMRI2/TIOCB5/TCLKA | CTS1#/RTS1#/SS1#            | IRQ4   |

| N5  |                      | PH2      |                     | TMRI0                                 |                             | IRQ1   |

| N6  |                      | PH1      |                     | TMO0                                  |                             | IRQ0   |

| N7  |                      | P55      | WAIT#               | MTIOC4D/TMO3                          |                             |        |

| N8  | VSS                  |          |                     |                                       |                             |        |

| N9  |                      | PC7      | A23/CS0#            | MTIOC3A/TMO2/<br>MTCLKB               | TXD8/SMOSI8/SSDA8/<br>MISOA | CACREF |

| N10 |                      | P82      |                     | MTIOC4A                               | TXD10/SMOSI10/SSDA10        |        |

| N11 |                      | PC3      | A19                 | MTIOC4D/TCLKB                         | TXD5/SMOSI5/SSDA5           |        |

| N12 |                      | P75      |                     |                                       | SCK11                       |        |

| N13 |                      | P74      |                     |                                       | CTS11#/RTS11#/SS11#         |        |

Note: • Pin names to which –DS is appended are for pins that can be used to trigger release from deep software standby mode.

Note: • Leave the NC pin open.

Table 1.10 List of Pins and Pin Functions (144-Pin LQFP) (2 / 4)

| Pin<br>No. | Power Supply, Clock,<br>System Control | I/O Port | External Bus    | Timers<br>(MTU, TMR, POE)              | Communications<br>(SCIc, SCId, RSPI, RIIC)               | Others                  |

|------------|----------------------------------------|----------|-----------------|----------------------------------------|----------------------------------------------------------|-------------------------|

| 40         |                                        | P16      |                 | MTIOC3C/MTIOC3D/<br>TMO2/TIOCB1/TCLKC  | TXD1/SMOSI1/SSDA1/<br>MOSIA/SCL-DS/RXD3/<br>SMISO3/SSCL3 | IRQ6/RTCOUT/<br>ADTRG0# |

| 41         |                                        | P86      |                 | TIOCA0                                 |                                                          |                         |

| 42         |                                        | P15      |                 | MTIOC0B/MTCLKB/<br>TMCI2/TIOCB2/TCLKB  | RXD1/SMISO1/SSCL1/<br>SCK3                               | IRQ5                    |

| 43         |                                        | P14      |                 | MTIOC3A/MTCLKA/<br>TMRI2/TIOCB5/TCLKA  | CTS1#/RTS1#/SS1#                                         | IRQ4                    |

| 44         |                                        | P13      |                 | MTIOC0B/TMO3/<br>TIOCA5                | SDA/TXD2/SMOSI2/<br>SSDA2                                | IRQ3                    |

| 45         |                                        | P12      |                 | TMCI1                                  | SCL/RXD2/SMISO2/<br>SSCL2                                | IRQ2                    |

| 46         |                                        | PH3      |                 | TMCI0                                  |                                                          |                         |

| 47         |                                        | PH2      |                 | TMRI0                                  |                                                          | IRQ1                    |

| 48         |                                        | PH1      |                 | TMO0                                   |                                                          | IRQ0                    |

| 49         |                                        | PH0      |                 |                                        |                                                          | CACREF                  |

| 50         |                                        | P56      |                 | MTIOC3C/TIOCA1                         |                                                          |                         |

| 51         |                                        | P55      | WAIT#           | MTIOC4D/TMO3                           |                                                          |                         |

| 52         |                                        | P54      | ALE             | MTIOC4B/TMCI1                          | CTS2#/RTS2#/SS2#                                         |                         |

| 53         | BCLK                                   | P53      |                 |                                        |                                                          |                         |

| 54         |                                        | P52      | RD#             |                                        | RXD2/SMISO2/SSCL2                                        |                         |

| 55         |                                        | P51      | WR1#/BC1#/WAIT# |                                        | SCK2                                                     |                         |

| 56         |                                        | P50      | WR0#/WR#        |                                        | TXD2/SMOSI2/SSDA2                                        |                         |

| 57         | VSS                                    |          |                 |                                        |                                                          |                         |

| 58         |                                        | P83      |                 | MTIOC4C                                | CTS10#/RTS10#                                            |                         |

| 59         | VCC                                    |          |                 |                                        |                                                          |                         |

| 60         |                                        | PC7      | A23/CS0#        | MTIOC3A/TMO2/<br>MTCLKB                | TXD8/SMOSI8/SSDA8/<br>MISOA                              | CACREF                  |

| 61         |                                        | PC6      | A22/CS1#        | MTIOC3C/MTCLKA/<br>TMCl2               | RXD8/SMISO8/SSCL8/<br>MOSIA                              |                         |

| 62         |                                        | PC5      | A21/CS2#/WAIT#  | MTIOC3B/MTCLKD/<br>TMRI2               | SCK8/RSPCKA                                              |                         |

| 63         |                                        | P82      |                 | MTIOC4A                                | TXD10/SMOSI10/SSDA10                                     |                         |

| 64         |                                        | P81      |                 | MTIOC3D                                | RXD10/SMISO10/SSCL10                                     |                         |

| 65         |                                        | P80      |                 | MTIOC3B                                | SCK10                                                    |                         |

| 66         |                                        | PC4      | A20/CS3#        | MTIOC3D/MTCLKC/<br>TMCI1/POE0#         | SCK5/CTS8#/RTS8#/<br>SS8#/SSLA0                          |                         |

| 67         |                                        | PC3      | A19             | MTIOC4D/TCLKB                          | TXD5/SMOSI5/SSDA5                                        |                         |

| 68         |                                        | P77      |                 |                                        | TXD11/SMOSI11/SSDA11                                     | <u> </u>                |

| 69         |                                        | P76      |                 |                                        | RXD11/SMISO11/SSCL11                                     | <u> </u>                |

| 70         |                                        | PC2      | A18             | MTIOC4B/TCLKA                          | RXD5/SMISO5/SSCL5/<br>ISSLA3                             |                         |

| 71         |                                        | P75      |                 |                                        | SCK11                                                    |                         |

| 72         |                                        | P74      |                 |                                        | CTS11#/RTS11#/SS11#                                      |                         |

| 73         |                                        | PC1      | A17             | MTIOC3A/TCLKD                          | SCK5/SSLA2                                               |                         |

| 74         |                                        | PL1      |                 |                                        |                                                          |                         |

| 75         |                                        | PC0      | A16             | MTIOC3C/TCLKC                          | CTS5#/RTS5#/SS5#/<br>SSLA1                               |                         |

| 76         |                                        | PL0      |                 |                                        |                                                          |                         |

| 77         |                                        | P73      |                 |                                        |                                                          |                         |

| 78         |                                        | PB7      | A15             | MTIOC3B/TIOCB5                         | TXD9/SMOSI9/SSDA9                                        |                         |

| 79         |                                        | PB6      | A14             | MTIOC3D/TIOCA5                         | RXD9/SMISO9/SSCL9                                        |                         |

| 80         |                                        | PB5      | A13             | MTIOC2A/MTIOC1B/<br>TMRI1/POE1#/TIOCB4 | SCK9                                                     |                         |

RX210 Group 4. I/O Registers

• Longword-size I/O registers

MOV.L #SFR\_ADDR, R1 MOV.L #SFR\_DATA, [R1] CMP [R1].L, R1 ;; Next process

If multiple registers are written to and a subsequent instruction should be executed after the write operations are entirely completed, only read the I/O register that was last written to and execute the operation using the value; it is not necessary to read or execute operation for all the registers that were written to.

# (3) Number of Access Cycles to I/O Registers

For numbers of clock cycles for access to I/O registers, see Table 4.1, List of I/O Registers (Address Order). The number of access cycles to I/O registers is obtained by following equation.\*1

Number of access cycles to I/O registers = Number of bus cycles for internal main bus 1 +

Number of divided clock synchronization cycles +

Number of bus cycles for internal peripheral bus 1 to 6

The number of bus cycles of internal peripheral bus 1 to 6 differs according to the register to be accessed.

When peripheral functions connected to internal peripheral bus 2 to 6 or registers for the external bus control unit (except for bus error related registers) are accessed, the number of divided clock synchronization cycles is added.

The number of divided clock synchronization cycles differs depending on the frequency ratio between ICLK and PCLK (or FCLK, BCLK) or bus access timing.

In the peripheral function unit, when the frequency ratio of ICLK is equal to or greater than that of PCLK (or FCLK), the sum of the number of bus cycles for internal main bus 1 and the number of the divided clock synchronization cycles will be one cycle of PCLK (or FCLK) at a maximum. Therefore, one PCLK (or FCLK) has been added to the number of access cycles shown in Table 4.1.

When the frequency ratio of ICLK is lower than that of PCLK (or FCLK), the subsequent bus access is started from the ICLK cycle following the completion of the access to the peripheral functions. Therefore, the access cycles are described on an ICLK basis.

In the external bus control unit, the sum of the number of bus cycles for internal main bus 1 and the number of divided clock synchronization cycles will be one cycle of BCLK at a maximum. Therefore, one BCLK is added to the number of access cycles shown in Table 4.1.

Note 1. This applies to the number of cycles when the access from the CPU does not conflict with the instruction fetching to the external memory or bus access from the different bus master (DMAC or DTC).

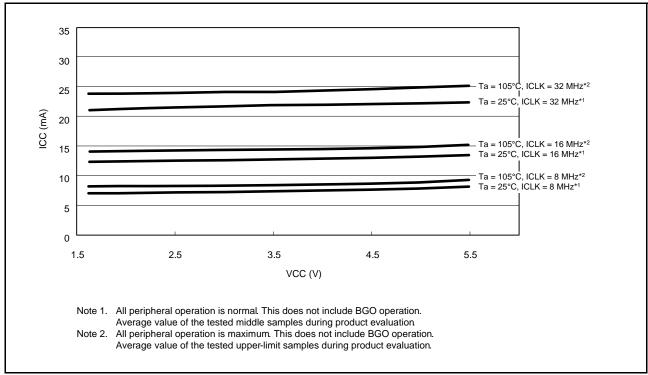

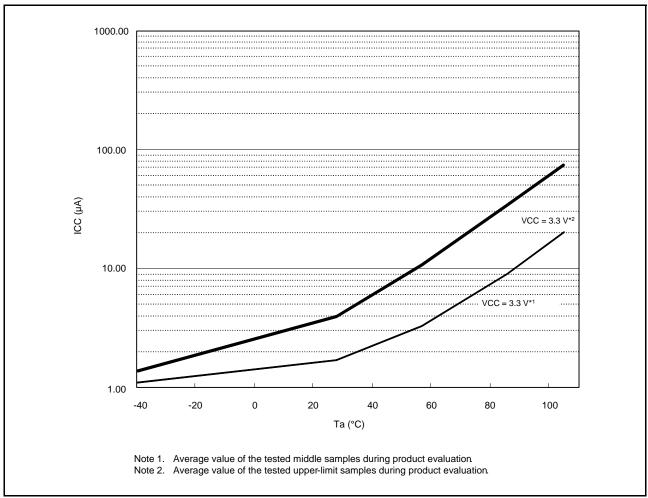

Figure 5.37 Voltage Dependency in Middle-Speed Operating Modes 2A and 2B (Reference Data) for Chip Version B with 512 Kbytes or Less of Flash Memory and 144 and 145 Pins

Figure 5.38 Voltage Dependency in Low-Speed Operating Mode 1 (Reference Data) for Chip Version B with 512 Kbytes or Less of Flash Memory and 144 and 145 Pins

RX210 Group 5. Electrical Characteristics

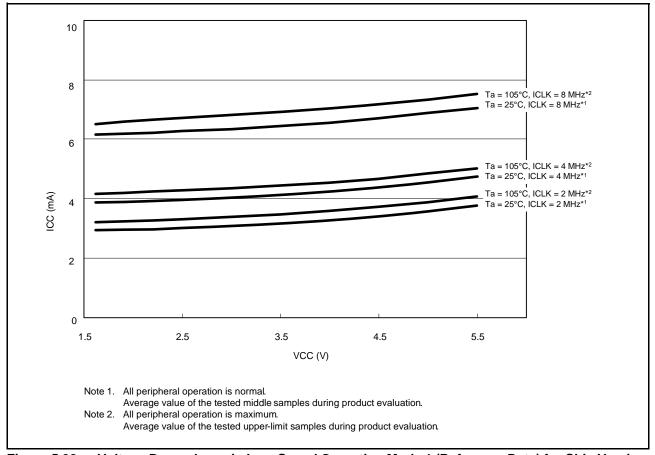

Figure 5.41 Temperature Dependency in Software Standby Mode (SOFTCUT[2:0] Bits = 110b)

(Reference Data) for Chip Version B with 512 Kbytes or Less of Flash Memory and 144 and 145 Pins

Table 5.44 Clock Timing

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

| Item                                            |                                                                     | Symbol                 | Min.   | Тур.              | Max.   | Unit        | Test<br>Conditions   |

|-------------------------------------------------|---------------------------------------------------------------------|------------------------|--------|-------------------|--------|-------------|----------------------|

| EXTAL external clock input cycle time           |                                                                     | t <sub>EXcyc</sub>     | 50     | _                 | _      | ns          | Figure 5.60          |

| EXTAL external clock input high pulse width     | 1                                                                   | t <sub>EXH</sub>       | 20     | _                 | _      | ns          |                      |

| EXTAL external clock input low pulse width      |                                                                     | t <sub>EXL</sub>       | 20     | _                 | _      | ns          |                      |

| EXTAL external clock rising time                |                                                                     | t <sub>EXr</sub>       | _      | _                 | 5      | ns          |                      |

| EXTAL external clock falling time               |                                                                     | t <sub>EXf</sub>       | _      | _                 | 5      | ns          |                      |

| EXTAL external clock input wait time*1          |                                                                     | t <sub>EXWT</sub>      | 1      | _                 |        | ms          |                      |

| Main clock oscillator oscillation frequency*2   |                                                                     | f <sub>MAIN</sub>      | 1      | _                 | 20     | MHz         |                      |

| Main clock oscillation stabilization time (crys | stal)* <sup>2</sup>                                                 | t <sub>MAINOSC</sub>   | _      | 3                 | _      | ms          | Figure 5.61          |

| Main clock oscillation stabilization time (cera | amic resonator)*2                                                   | t <sub>MAINOSC</sub>   | _      | 50                |        | μs          |                      |

| Main clock oscillation stabilization wait time  | (crystal)*2                                                         | t <sub>MAINOSCWT</sub> | _      | 6                 | _      | ms          |                      |

| Main clock oscillation stabilization wait time  | (ceramic resonator)*2                                               | t <sub>MAINOSCWT</sub> | _      | 100               |        | μs          |                      |

| LOCO clock cycle time                           |                                                                     | t <sub>cyc</sub>       | 7.27   | 8                 | 8.89   | μs          |                      |

| LOCO clock oscillation frequency*6              | f <sub>LOCO</sub>                                                   | 112.5                  | 125    | 137.5             | kHz    |             |                      |

| LOCO clock oscillation stabilization wait tim   | t <sub>LOCOWT</sub>                                                 | _                      | _      | 20                | μs     | Figure 5.62 |                      |

| HOCO clock oscillation frequency*7              | f <sub>HOCO</sub>                                                   | 31.680                 | 32     | 32.320            | MHz    | Ta = 0 to   |                      |

|                                                 |                                                                     | 36.495                 | 36.864 | 37.233            |        | 50°C        |                      |

|                                                 |                                                                     |                        | 39.600 | 40                | 40.400 |             |                      |

|                                                 |                                                                     |                        | 49.500 | 50                | 50.500 |             |                      |

|                                                 |                                                                     |                        | 31.520 | 32                | 32.480 |             | Ta = -40 to<br>105°C |

|                                                 |                                                                     |                        | 36.311 | 36.864            | 37.417 |             | 103 C                |

|                                                 |                                                                     |                        | 39.400 | 40                | 40.600 |             |                      |

|                                                 |                                                                     |                        | 49.250 | 50                | 50.750 |             | Fig. 5.00            |

| HOCO clock oscillation stabilization time 1     |                                                                     | t <sub>HOCO1</sub>     | _      |                   | 300    | μs          | Figure 5.63          |

| HOCO clock oscillation stabilization time 2     |                                                                     | t <sub>HOCO2</sub>     | _      |                   | 175    | μs          | Figure 5.64          |

| HOCO clock oscillation stabilization wait tim   |                                                                     | t <sub>HOCOWT</sub>    | _      | _                 | 350    | μs          | Figure 5.64          |

| HOCO clock power supply stabilization time      | 9                                                                   | tHOCOP                 | _      | _                 | 350    | μs          | Figure 5.65          |

| PLL input frequency                             |                                                                     | f <sub>PLLIN</sub>     | 4      | _                 | 12.5   | MHz         |                      |

| PLL circuit oscillation frequency               |                                                                     | f <sub>PLL</sub>       | 50     | _                 | 100    | MHz         |                      |

| PLL clock oscillation stabilization time        | PLL operation started after main clock                              | t <sub>PLL1</sub>      | _      | _                 | 500    | μs          | Figure 5.66          |

| PLL clock oscillation stabilization wait time   | oscillation has settled                                             | t <sub>PLLWT1</sub>    | 1.5    | 1                 | 1      | ms          |                      |

| PLL clock oscillation stabilization time*4      | PLL operation started                                               | t <sub>PLL2</sub>      | _      | 3.5* <sup>3</sup> | ı      | ms          | Figure 5.67          |

| PLL clock oscillation stabilization wait time*4 | before main clock oscillation has settled                           | t <sub>PLLWT2</sub>    | _      | 7                 |        | ms          |                      |

| PLL clock power supply stabilization time (for  | PLL clock power supply stabilization time (for chip version B only) |                        |        | _                 | 30     | μs          | Figure 5.68          |

| Sub-clock oscillator oscillation frequency      |                                                                     | f <sub>SUB</sub>       | _      | 32.768            | _      | kHz         |                      |

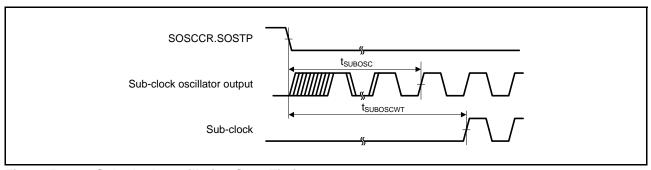

| Sub-clock oscillation stabilization time*5      |                                                                     | t <sub>SUBOSC</sub>    | 2      | _                 | _      | S           | Figure 5.69          |

| Sub-clock oscillation stabilization wait time*  | 5                                                                   | t <sub>SUBOSCWT</sub>  | 4      | _                 | _      | S           |                      |

Note 1. The time interval from the time P36 and P37 are configured for input and the main clock oscillator stopping bit (MOSCCR.MOSTP) is set to 0 (operating) until the clock becomes available.

RX210 Group 5. Electrical Characteristics

Figure 5.69 Sub-clock Oscillation Start Timing

|      | lt                        | tem    |                      | Symbol                           | Min. | Max. | Unit*1            | Test Conditions                             |  |

|------|---------------------------|--------|----------------------|----------------------------------|------|------|-------------------|---------------------------------------------|--|

| RSPI | MOSI and MISO rise/       | Output |                      | t <sub>Dr,</sub> t <sub>Df</sub> | _    | 20   | ns                | C = 30 pF                                   |  |

|      | fall time                 | Input  |                      | ,                                | _    | 1    | μs                | Figure 5.92 to<br>Figure 5.97               |  |

|      | SSL rise/fall time        | Output |                      | t <sub>SSLr,</sub>               | _    | 20   | ns                | 1 iguio 0.07                                |  |

|      |                           | Input  |                      | t <sub>SSLf</sub>                | _    | 1    | μs                |                                             |  |

|      | Slave access time         |        | 2.7 V ≤ VCC ≤ 5.5 V  | t <sub>SA</sub>                  | _    | 6    | t <sub>Pcyc</sub> | C = 30 pF<br>Figure 5.96 and<br>Figure 5.97 |  |

|      |                           |        | 1.8 V ≤ VCC < 2.7 V  |                                  | _    | 7    |                   |                                             |  |

|      |                           |        | 1.62 V ≤ VCC < 1.8 V |                                  | _    | 7    |                   | 1 19410 0.07                                |  |

|      | Slave output release time |        | 2.7 V ≤ VCC ≤ 5.5 V  | t <sub>REL</sub>                 | _    | 5    | t <sub>Pcyc</sub> |                                             |  |

|      |                           |        | 1.8 V ≤ VCC < 2.7 V  |                                  | _    | 6    |                   |                                             |  |

|      |                           |        | 1.62 V ≤ VCC < 1.8 V |                                  | _    | 6    |                   |                                             |  |

Note 1.  $t_{Pcyc}$ : PCLK cycle

# [768 Kbytes/1 Mbyte of flash memory or 144/145 pins]

# Table 5.57 Timing of On-Chip Peripheral Modules (3)

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V, T<sub>a</sub> = -40 to +105°C When high-drive output is selected by the drive capacity register

| ·    | Item                         |                            |                      |                     | Min.                                                                      | Max.                  | Unit*1 | Test Conditions |  |

|------|------------------------------|----------------------------|----------------------|---------------------|---------------------------------------------------------------------------|-----------------------|--------|-----------------|--|

| RSPI | RSPCK clock cycle            | Master                     |                      | t <sub>SPcyc</sub>  | 2                                                                         | 4096 t <sub>Pcy</sub> |        | C = 30pF        |  |

|      |                              | Slave                      |                      |                     | 8                                                                         | 4096                  |        | Figure 5.91     |  |

|      | RSPCK clock high pulse width | Master                     | 2.7 V ≤ VCC ≤ 5.5 V  | t <sub>SPCKWH</sub> | (t <sub>SPcyc</sub> - t <sub>SPCKr</sub> - t <sub>SPCKf</sub> )/2 - 3     | _                     | ns     |                 |  |

|      |                              |                            | 1.8 V ≤ VCC < 2.7 V  |                     | $(t_{SPCyc} - t_{SPCKr} - t_{SPCKf})/2 - 3$                               | 1                     |        |                 |  |

|      |                              |                            | 1.62 V ≤ VCC < 1.8 V |                     | $(t_{SPcyc} - t_{SPCKr} - t_{SPCKf})/2 - 10$                              | 1                     |        |                 |  |

|      |                              | Slave                      |                      |                     | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2      | 1                     |        |                 |  |

|      | RSPCK clock low pulse width  | Master 2.7 V ≤ VCC ≤ 5.5 V |                      | t <sub>SPCKWL</sub> | $(t_{SPcyc} - t_{SPCKr} - t_{SPCKf})/2 - 3$                               | 1                     | ns     |                 |  |

|      |                              |                            | 1.8 V ≤ VCC < 2.7 V  | ,                   | $(t_{SPcyc} - t_{SPCKr} - t_{SPCKf})/2 - 3$                               | -                     |        |                 |  |

|      |                              |                            | 1.62 V ≤ VCC < 1.8 V |                     | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 10 | -                     |        |                 |  |

|      |                              | Slave                      |                      |                     | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2      | -                     |        |                 |  |

|      | RSPCK clock rise/fall        | Output                     | 2.7 V ≤ VCC ≤ 5.5 V  | t <sub>SPCKr,</sub> | _                                                                         | 10                    | ns     |                 |  |

|      | time                         |                            | 1.8 V ≤ VCC < 2.7 V  | tSPCKf              | _                                                                         | - 15<br>- 20          |        |                 |  |

|      |                              |                            | 1.62 V ≤ VCC < 1.8 V |                     | _                                                                         |                       |        |                 |  |

|      |                              | Input                      | Input                |                     | _                                                                         | 1                     | μs     |                 |  |

RX210 Group 5. Electrical Characteristics

## Differential nonlinearity error (DNL)

Differential nonlinearity error is the difference between 1-LSB width based on the ideal A/D conversion characteristics and the width of the actually output code.

#### Offset error

Offset error is the difference between a transition point of the ideal first output code and the actual first output code.

### Full-scale error

Full-scale error is the difference between a transition point of the ideal last output code and the actual last output code.

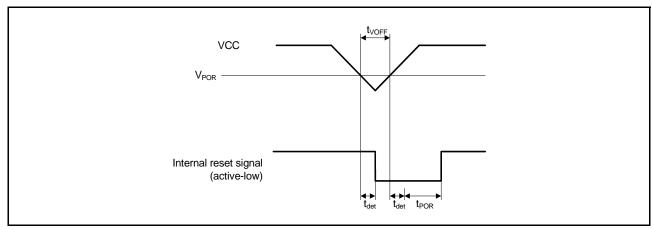

Figure 5.103 Voltage Detection Reset Timing

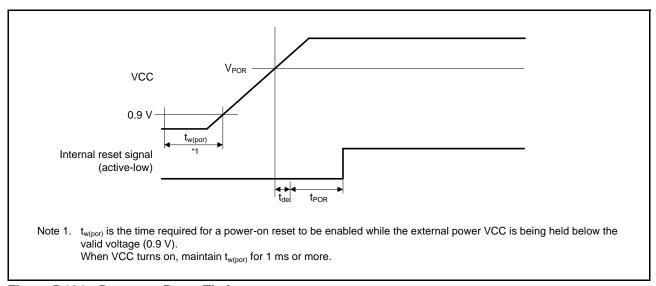

Figure 5.104 Power-on Reset Timing

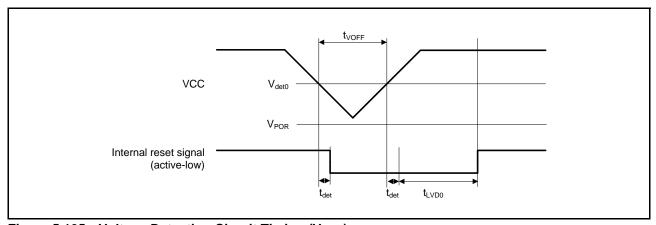

Figure 5.105 Voltage Detection Circuit Timing (V<sub>det0</sub>)

[Chip version B]

ROM (Flash Memory for Code Storage) Characteristics (6) : middle-speed operating modes 1B and 2B **Table 5.79**

Conditions: VCC = AVCC0 = 1.62 to 3.6 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation:  $T_a = -40$  to +105°C

| Item                                               |                                                                              | Symbol                                           | FCLK | = 4 MH | Z                                                |      | FCLK = | 32 MHz*1                                                                                                  | Unit  |

|----------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|------|--------|--------------------------------------------------|------|--------|-----------------------------------------------------------------------------------------------------------|-------|

| пеш                                                |                                                                              | Symbol                                           | Min. | Тур.   | Max.                                             | Min. | Тур.   | Max.                                                                                                      | Offic |

| Programming time                                   | 2 bytes                                                                      | t <sub>P2</sub>                                  | _    | 0.25   | 5.0                                              | _    | 0.21   | 2.8                                                                                                       | ms    |

| when N <sub>PEC</sub> ≤ 100 times                  | 8 bytes                                                                      | t <sub>P8</sub>                                  | _    | 0.25   | 5.3                                              | _    | 0.21   | 3.0                                                                                                       |       |

|                                                    | 128 bytes                                                                    | t <sub>P128</sub>                                | _    | 0.92   | 14.0                                             | _    | 0.65   | 8.3                                                                                                       |       |

| Programming time                                   | 2 bytes                                                                      | t <sub>P2</sub>                                  | _    | 0.31   | 6.2                                              | _    | 0.26   | 3.5                                                                                                       | ms    |

| when N <sub>PEC</sub> > 100 times                  | 8 bytes                                                                      | t <sub>P8</sub>                                  | _    | 0.31   | 6.6                                              | _    | 0.26   | 3.7                                                                                                       |       |

|                                                    | 128 bytes                                                                    | t <sub>P128</sub>                                | _    | 1.09   | 17.5                                             | _    | 0.77   | 10.0                                                                                                      |       |

| Erasure time when N <sub>PEC</sub> ≤ 100 times     | 2 Kbytes                                                                     | t <sub>E2K</sub>                                 | _    | 21.0   | 113.7                                            | _    | 18.5   | 46                                                                                                        | ms    |

| Erasure time when N <sub>PEC</sub> > 100 times     | 2 Kbytes                                                                     | t <sub>E2K</sub>                                 |      | 25.6   | 220.6                                            | _    | 22.5   | 90 (1000 times ≥<br>N <sub>PEC</sub> > 100 times),<br>98 (10000 times ≥<br>N <sub>PEC</sub> > 1000 times) | ms    |

|                                                    | Suspend delay time during programming (in programming/erasure priority mode) |                                                  | _    | _      | 1.7                                              | _    | _      | 1.6                                                                                                       | ms    |

| First suspend delay time programming (in suspend   | •                                                                            | t <sub>SPSD1</sub>                               | _    | _      | 220                                              | _    | _      | 120                                                                                                       | μs    |

| Second suspend delay ti programming (in suspend    | •                                                                            | t <sub>SPSD2</sub>                               | _    | _      | 1.7                                              | _    | _      | 1.6                                                                                                       | ms    |

| Suspend delay time durin (in programming/erasure   |                                                                              | t <sub>SED</sub>                                 | _    |        | 1.7                                              | _    | _      | 1.6                                                                                                       | ms    |

| First suspend delay time (in suspend priority mode |                                                                              | t <sub>SESD1</sub>                               | _    | _      | 220                                              | _    | _      | 120                                                                                                       | μs    |

|                                                    | Second suspend delay time during erasing (in suspend priority mode)          |                                                  | _    |        | 1.7                                              | _    | _      | 1.6                                                                                                       | ms    |

| FCU reset time                                     | t <sub>FCUR</sub>                                                            | 20 µs or<br>longer and<br>FCLK × 6<br>or greater | _    | _      | 20 µs or<br>longer and<br>FCLK × 6<br>or greater | _    | _      | μs                                                                                                        |       |

Note 1. The operating frequency is 20 MHz (max.) when the voltage is in the range from 1.62 V to less than 1.8 V.

[Chip version B]

**Table 5.84**

E2 DataFlash Characteristics (5): high-speed operating mode, middle-speed operating modes 1A and 2A

Conditions:  $VCC = AVCC0 = 2.7 \text{ to } 5.5 \text{ V}, VREFH = VREFH0 = AVCC0}, VSS = AVSS0 = VREFL = VREFL0 = 0 \text{ V}$ Temperature range for the programming/erasure operation:  $T_a = -40 \text{ to } +105^{\circ}\text{C}$

| Itom                                                          | Item                                                                     |                     | FCLK | ( = 4 MHz |      | FCLK | FCLK = 32 MHz |      |      |  |

|---------------------------------------------------------------|--------------------------------------------------------------------------|---------------------|------|-----------|------|------|---------------|------|------|--|

| item                                                          |                                                                          | Symbol              | Min. | Тур.      | Max. | Min. | Тур.          | Max. | Unit |  |

| Programming time                                              | 2 bytes                                                                  | t <sub>DP2</sub>    | _    | 0.19      | 4.4  | _    | 0.13          | 2.0  | ms   |  |

| when N <sub>DPEC</sub> ≤ 100 times                            | 8 bytes                                                                  | t <sub>DP8</sub>    | _    | 0.24      | 5.1  | _    | 0.13          | 2.2  |      |  |

| Programming time                                              | 2 bytes                                                                  | t <sub>DP2</sub>    | _    | 0.25      | 6.4  | _    | 0.17          | 3.0  | ms   |  |

| when N <sub>DPEC</sub> > 100 times                            | 8 bytes                                                                  | t <sub>DP8</sub>    | _    | 0.32      | 7.5  | _    | 0.18          | 3.2  |      |  |

| Erasure time<br>when N <sub>DPEC</sub> ≤ 100 times            | 128 bytes                                                                | t <sub>DE128</sub>  | _    | 3.3       | 27.1 | _    | 2.5           | 8    | ms   |  |

| Erasure time when N <sub>DPEC</sub> > 100 times               | 128 bytes                                                                | t <sub>DE128</sub>  | _    | 4.0       | 45.1 | _    | 3.0           | 12   | ms   |  |

| Blank check time                                              | 2 bytes                                                                  | t <sub>DBC2</sub>   | _    | _         | 98   | _    | _             | 35   | μs   |  |

| _                                                             | 2 Kbytes                                                                 | t <sub>DBC2K</sub>  |      |           | 16   | _    | _             | 2.5  | ms   |  |

| Suspend delay time during pr<br>(in programming/erasure prio  | 0                                                                        | t <sub>DSPD</sub>   | _    | _         | 0.9  | _    | _             | 0.8  | ms   |  |

| First suspend delay time during programming (in suspend price | U                                                                        | t <sub>DSPSD1</sub> | _    | _         | 220  | _    | _             | 120  | μs   |  |

| Second suspend delay time of programming (in suspend prior    | •                                                                        | t <sub>DSPSD2</sub> | _    | _         | 0.9  | _    | _             | 0.8  | ms   |  |

| . ,                                                           | Suspend delay time during erasing (in programming/erasure priority mode) |                     | _    | _         | 0.9  | _    | _             | 0.8  | ms   |  |

| First suspend delay time durin (in suspend priority mode)     | First suspend delay time during erasing (in suspend priority mode)       |                     | _    | _         | 220  | _    | _             | 120  | μs   |  |

| Second suspend delay time of (in suspend priority mode)       | luring erasing                                                           | t <sub>DSESD2</sub> | _    | _         | 0.9  | _    | _             | 0.8  | ms   |  |

[Chip version B]

E2 DataFlash Characteristics (6) : middle-speed operating modes 1B and 2B **Table 5.85**

Conditions: VCC = AVCC0 = 1.62 to 3.6 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation:  $T_a = -40$  to +105°C

| Item                                                                         |                     | Symbol -            | FCLK = 4 MHz |      |      | FCLK = 32 MHz*1 |      |      | I India |

|------------------------------------------------------------------------------|---------------------|---------------------|--------------|------|------|-----------------|------|------|---------|

|                                                                              |                     |                     | Min.         | Тур. | Max. | Min.            | Тур. | Max. | - Unit  |

| Programming time when N <sub>DPEC</sub> ≤ 100 times                          | 2 bytes             | t <sub>DP2</sub>    | _            | 0.28 | 5.1  | _               | 0.20 | 2.8  | ms      |

|                                                                              | 8 bytes             | t <sub>DP8</sub>    | _            | 0.32 | 6.0  | _               | 0.22 | 3.2  |         |

| Programming time when N <sub>DPEC</sub> > 100 times                          | 2 bytes             | t <sub>DP2</sub>    | _            | 0.36 | 7.6  | _               | 0.25 | 4.2  | ms      |

|                                                                              | 8 bytes             | t <sub>DP8</sub>    | _            | 0.40 | 8.8  | _               | 0.28 | 4.5  |         |

| Erasure time when N <sub>DPEC</sub> ≤ 100 times                              | 128 bytes           | t <sub>DE128</sub>  | _            | 4.8  | 32.4 | _               | 4.1  | 12   | ms      |

| Erasure time when N <sub>DPEC</sub> > 100 times                              | 128 bytes           | t <sub>DE128</sub>  | _            | 5.8  | 51.4 | _               | 4.9  | 17   | ms      |

| Blank check time                                                             | 2 bytes             | t <sub>DBC2</sub>   | _            | _    | 110  | _               | _    | 40   | μs      |

|                                                                              | 2 Kbytes            | t <sub>DBC2K</sub>  | _            | _    | 16.3 | _               | _    | 2.6  | ms      |

| Suspend delay time during programming (in programming/erasure priority mode) |                     | t <sub>DSPD</sub>   | _            | _    | 1.7  | _               | _    | 1.6  | ms      |

| First suspend delay time during programming (in suspend priority mode)       |                     | t <sub>DSPSD1</sub> | _            | _    | 220  | _               | _    | 120  | μs      |

| Second suspend delay time during programming (in suspend priority mode)      |                     | t <sub>DSPSD2</sub> | _            | _    | 1.7  | _               | _    | 1.6  | ms      |

| Suspend delay time during erasing (in programming/erasure priority mode)     |                     | t <sub>DSED</sub>   | _            | _    | 1.7  | _               | _    | 1.6  | ms      |

| First suspend delay time during erasing (in suspend priority mode)           |                     | t <sub>DSESD1</sub> | _            | _    | 220  | _               | _    | 120  | μs      |