Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 64                                                                               |

| Program Memory Size        | 96KB (96K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 5.5V                                                                     |

| Data Converters            | A/D 14x12b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52104bdff-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification        | Module/Function                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low power consumption | Low power consumption<br>facilities            | <ul> <li>Module stop function</li> <li>Four low power consumption modes</li> <li>Sleep mode, all-module clock stop mode, software standby mode, and deep software standby mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

|                       | Function for lower operating power consumption | <ul> <li>Operating power control modes         [Chip versions A and C]         High-speed operating mode, middle-speed operating mode 1A, middle-speed operating mode 1B, low-speed operating mode 1, low-speed operating mode 2         [Chip version B]         High-speed operating mode, middle-speed operating mode 1A, middle-speed operating mode 1B, middle-speed operating mode 2A, middle-speed operating mode 2B, low-speed operating mode 1, low-speed operating mode 2     </li> </ul>                                                      |

| Interrupt             | Interrupt controller (ICUb)                    | <ul> <li>Interrupt vectors: 167</li> <li>External interrupts: 9 (NMI, IRQ0 to IRQ7 pins)</li> <li>Non-maskable interrupts: 6 (the NMI pin, oscillation stop detection interrupt, voltage monitoring 1 interrupt, voltage monitoring 2 interrupt, WDT interrupt, and IWDT interrupt)</li> <li>16 levels specifiable for the order of priority</li> </ul>                                                                                                                                                                                                  |

| External bus exte     | nsion                                          | <ul> <li>The external address space can be divided into four areas (CS0 to CS3), each with independent control of access settings.</li> <li>Capacity of each area: 16 Mbytes (CS0 to CS3)</li> <li>A chip-select signal (CS0# to CS3#) can be output for each area.</li> <li>Each area is specifiable as an 8-bit or 16-bit bus space</li> <li>The data arrangement in each area is selectable as little or big endian (only for data).</li> <li>Bus format: Separate bus, multiplex bus</li> <li>Wait control</li> <li>Write buffer facility</li> </ul> |

| DMA                   | DMA controller (DMACA)                         | <ul> <li>4 channels</li> <li>Three transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Software trigger, external interrupts, and interrupt requests from peripheral functions</li> </ul>                                                                                                                                                                                                                                                                                                                  |

|                       | Data transfer controller<br>(DTCa)             | <ul> <li>Three transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Interrupts</li> <li>Chain transfer function</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  |

| I/O ports             | General I/O ports                              | 145-pin/144-pin/100-pin/80-pin/69-pin/64-pin/48-pin<br>• I/O: 122/122/84/64/48/48/34<br>• Input: 1/1/1/1/1/1<br>• Pull-up resistors: 122/122/84/64/48/48/34<br>• Open-drain outputs: 76/76/54/44/35/35/26<br>• 5-V tolerance:4/4/4/4/2/2*1/2                                                                                                                                                                                                                                                                                                             |

| Event link controll   | er (ELC)                                       | <ul> <li>Event signals of 59 types can be directly connected to the module</li> <li>Operations of timer modules are selectable at event input</li> <li>Capable of event link operation for ports B and E</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

| Multi-function pin    | controller (MPC)                               | Capable of selecting input/output function from multiple pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Table 1.1 Outline of Specifications (2 / 5)

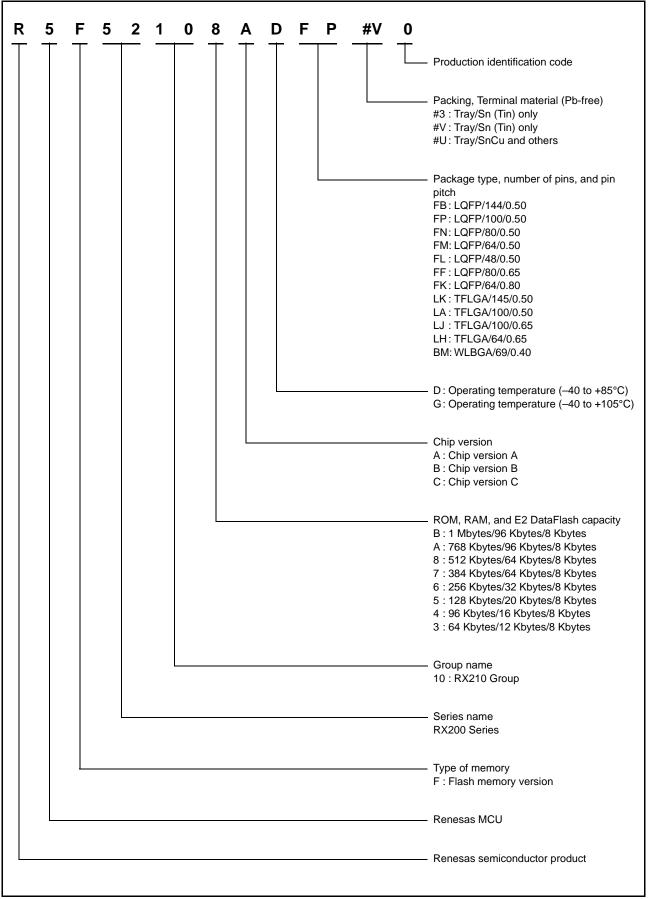

Figure 1.1 How to Read the Product Part No., Memory Capacity, and Package Type

RENESAS

| Pin | Power Supply, Clock, |          |              | Timers                                | Communications              |        |

|-----|----------------------|----------|--------------|---------------------------------------|-----------------------------|--------|

| No. | System Control       | I/O Port | External Bus | (MTU, TMR, POE)                       | (SCIc, SCId, RSPI, RIIC)    | Others |

| M11 |                      | PC0      | A16          | MTIOC3C/TCLKC                         | CTS5#/RTS5#/SS5#/<br>SSLA1  |        |

| M12 |                      | PC1      | A17          | MTIOC3A/TCLKD                         | SCK5/SSLA2                  |        |

| M13 |                      | PL1      |              |                                       |                             |        |

| N1  |                      | P21      |              | MTIOC1B/TMCI0/<br>TIOCA3              | RXD0/SMISO0/SSCL0           |        |

| N2  |                      | P20      |              | MTIOC1A/TMRI0/<br>TIOCB3              | TXD0/SMOSI0/SSDA0           |        |

| N3  |                      | P87      |              | TIOCA2                                |                             |        |

| N4  |                      | P14      |              | MTIOC3A/MTCLKA/<br>TMRI2/TIOCB5/TCLKA | CTS1#/RTS1#/SS1#            | IRQ4   |

| N5  |                      | PH2      |              | TMRI0                                 |                             | IRQ1   |

| N6  |                      | PH1      |              | TMO0                                  |                             | IRQ0   |

| N7  |                      | P55      | WAIT#        | MTIOC4D/TMO3                          |                             |        |

| N8  | VSS                  |          |              |                                       |                             |        |

| N9  |                      | PC7      | A23/CS0#     | MTIOC3A/TMO2/<br>MTCLKB               | TXD8/SMOSI8/SSDA8/<br>MISOA | CACREF |

| N10 |                      | P82      |              | MTIOC4A                               | TXD10/SMOSI10/SSDA10        |        |

| N11 |                      | PC3      | A19          | MTIOC4D/TCLKB                         | TXD5/SMOSI5/SSDA5           |        |

| N12 |                      | P75      |              |                                       | SCK11                       |        |

| N13 |                      | P74      |              |                                       | CTS11#/RTS11#/SS11#         |        |

Table 1.9

List of Pins and Pin Functions (145-Pin TFLGA) (4 / 4)

Note: • Pin names to which –DS is appended are for pins that can be used to trigger release from deep software standby mode. Note: • Leave the NC pin open.

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | External Bus | Timers<br>(MTU, TMR, POE)       | Communications<br>(SCIc, SCId, RSPI,<br>RIIC) | Others                   |

|------------|-------------------------------------------|----------|--------------|---------------------------------|-----------------------------------------------|--------------------------|

| E6         |                                           | PA2      | A2           |                                 | RXD5/SMISO5/SSCL5/<br>SSLA3                   |                          |

| E7         |                                           | PA6      | A6           | MTIC5V/MTCLKB/<br>TMCI3/POE2#   | CTS5#/RTS5#/SS5#/<br>MOSIA                    |                          |

| E8         |                                           | PA4      | A4           | MTIC5U/MTCLKA/<br>TMRI0         | TXD5/SMOSI5/SSDA5/<br>SSLA0                   | IRQ5-DS/CVREFB           |

| E9         |                                           | PA5      | A5           |                                 | RSPCKA                                        |                          |

| E10        |                                           | PA3      | A3           | MTIOC0D/MTCLKD                  | RXD5/SMISO5/SSCL5                             | IRQ6-DS/CMPB1            |

| F1         | EXTAL                                     | P36      |              |                                 |                                               |                          |

| F2         | VCC                                       |          |              |                                 |                                               |                          |

| F3         |                                           | P35      |              |                                 |                                               | NMI                      |

| F4         |                                           | P32      |              | MTIOC0C/TMO3                    | TXD6/SMOSI6/SSDA6                             | IRQ2-DS/RTCOUT<br>RTCIC2 |

| F5         |                                           | P12      |              | TMCI1                           | SCL                                           | IRQ2                     |

| F6         |                                           | PB3      | A11          | MTIOC0A/MTIOC4A/<br>TMO0/POE3#  | SCK6                                          |                          |

| F7         |                                           | PB2      | A10          |                                 | CTS6#/RTS6#/SS6#                              |                          |

| F8         |                                           | PB0      | A8           | MTIC5W                          | RXD6/SMISO6/SSCL6/<br>RSPCKA                  |                          |

| F9         |                                           | PA7      | A7           |                                 | MISOA                                         |                          |

| F10        | VSS                                       |          |              |                                 |                                               |                          |

| G1         |                                           | P33      |              | MTIOC0D/TMRI3/<br>POE3#         | RXD6/SMISO6/SSCL6                             | IRQ3-DS                  |

| G2         |                                           | P31      |              | MTIOC4D/TMCI2                   | CTS1#/RTS1#/SS1#                              | IRQ1-DS/RTCIC1           |

| G3         |                                           | P30      |              | MTIOC4B/TMRI3/<br>POE8#         | RXD1/SMISO1/SSCL1                             | IRQ0-DS/RTCIC0           |

| G4         |                                           | P27      | CS3#         | MTIOC2B/TMCI3                   | SCK1                                          |                          |

| G5         | BCLK                                      | P53      |              |                                 |                                               |                          |

| G6         |                                           | P52      | RD#          |                                 |                                               |                          |

| G7         |                                           | PB5      | A13          | MTIOC2A/MTIOC1B/<br>TMRI1/POE1# | SCK9                                          |                          |

| G8         |                                           | PB4      | A12          |                                 | CTS9#/RTS9#/SS9#                              |                          |

| G9         |                                           | PB1      | A9           | MTIOC0C/MTIOC4C/<br>TMCI0       | TXD6/SMOSI6/SSDA6                             | IRQ4-DS                  |

| G10        | VCC                                       |          |              |                                 |                                               |                          |

| H1         |                                           | P26      | CS2#         | MTIOC2A/TMO1                    | TXD1/SMOSI1/SSDA1                             |                          |

| H2         |                                           | P25      | CS1#         | MTIOC4C/MTCLKB                  |                                               | ADTRG0#                  |

| H3         |                                           | P16      |              | MTIOC3C/MTIOC3D/<br>TMO2        | TXD1/SMOSI1/SSDA1/<br>MOSIA/SCL-DS            | IRQ6/RTCOUT/<br>ADTRG0#  |

| H4         |                                           | P15      |              | MTIOC0B/MTCLKB/<br>TMCI2        | RXD1/SMISO1/SSCL1                             | IRQ5                     |

| H5         |                                           | P55      | WAIT#        | MTIOC4D/TMO3                    |                                               |                          |

| H6         |                                           | P54      | ALE          | MTIOC4B/TMCI1                   |                                               |                          |

| H7         |                                           | PC7      | A23/CS0#     | MTIOC3A/TMO2/<br>MTCLKB         | TXD8/SMOSI8/SSDA8/<br>MISOA                   | CACREF                   |

| H8         |                                           | PC6      | A22/CS1#     | MTIOC3C/MTCLKA/<br>TMCI2        | RXD8/SMISO8/SSCL8/<br>MOSIA                   |                          |

| H9         |                                           | PB6      | A14          | MTIOC3D                         | RXD9/SMISO9/SSCL9                             |                          |

| H10        |                                           | PB7      | A15          | MTIOC3B                         | TXD9/SMOSI9/SSDA9                             |                          |

| J1         |                                           | P24      | CS0#         | MTIOC4A/MTCLKA/<br>TMRI1        |                                               |                          |

| J2         |                                           | P21      |              | MTIOC1B/TMCI0                   | RXD0/SMISO0/SSCL0                             |                          |

|            |                                           | P17      |              | MTIOC3A/MTIOC3B/                | SCK1/MISOA/                                   | IRQ7                     |

### Table 1.11 List of Pins and Pin Functions (100-Pin TFLGA) (2 / 3)

| Pin<br>No. | Power Supply,<br>Clock, System<br>Control | I/O Port | External Bus | Timers<br>(MTU, TMR, POE)      | Communications<br>(SCIc, SCId, RSPI,<br>RIIC) | Others                    |

|------------|-------------------------------------------|----------|--------------|--------------------------------|-----------------------------------------------|---------------------------|

| 1          | VREFH                                     | WO FOIL  | External Bus |                                | KIIC)                                         | Others                    |

| 2          | VREFI                                     | P03      |              |                                |                                               | DA0                       |

| 3          | VREFL                                     | FU3      |              |                                |                                               | DAU                       |

| 4          | VILLE                                     | PJ3      |              | MTIOC3C                        | CTS6#/RTS6#/SS6#                              |                           |

| 5          | VCL                                       | FJ3      |              | MINUCSC                        | C130#/R130#/330#                              |                           |

| 6          | VCL                                       | PJ1      |              | MTIOC3A                        |                                               |                           |

| 7          | MD                                        | 151      |              | WHOOSA                         |                                               | FINED                     |

| 8          | XCIN                                      |          |              |                                |                                               | TINED                     |

| 9          | XCOUT                                     |          |              |                                |                                               |                           |

| 10         | RES#                                      |          |              |                                |                                               |                           |

| 10         | XTAL                                      | P37      |              |                                |                                               |                           |

| 12         | VSS                                       | 107      |              |                                |                                               |                           |

| 13         | EXTAL                                     | P36      |              |                                |                                               |                           |

| 14         | VCC                                       | 1.00     |              |                                |                                               |                           |

| 15         |                                           | P35      |              |                                |                                               | NMI                       |

| 16         |                                           | P34      |              | MTIOC0A/TMCI3/                 | SCK6                                          | IRQ4                      |

|            |                                           |          |              | POE2#                          |                                               |                           |

| 17         |                                           | P33      |              | MTIOC0D/TMRI3/<br>POE3#        | RXD6/SMISO6/SSCL6                             | IRQ3-DS                   |

| 18         |                                           | P32      |              | MTIOC0C/TMO3                   | TXD6/SMOSI6/SSDA6                             | IRQ2-DS/RTCOUT/<br>RTCIC2 |

| 19         |                                           | P31      |              | MTIOC4D/TMCI2                  | CTS1#/RTS1#/SS1#                              | IRQ1-DS/RTCIC1            |

| 20         |                                           | P30      |              | MTIOC4B/TMRI3/<br>POE8#        | RXD1/SMISO1/SSCL1                             | IRQ0-DS/RTCIC0            |

| 21         |                                           | P27      | CS3#         | MTIOC2B/TMCI3                  | SCK1                                          |                           |

| 22         |                                           | P26      | CS2#         | MTIOC2A/TMO1                   | TXD1/SMOSI1/SSDA1                             |                           |

| 23         |                                           | P25      | CS1#         | MTIOC4C/MTCLKB                 |                                               | ADTRG0#                   |

| 24         |                                           | P24      | CS0#         | MTIOC4A/MTCLKA/<br>TMRI1       |                                               |                           |

| 25         |                                           | P23      |              | MTIOC3D/MTCLKD                 | CTS0#/RTS0#/SS0#                              |                           |

| 26         |                                           | P22      |              | MTIOC3B/MTCLKC/<br>TMO0        | SCK0                                          |                           |

| 27         |                                           | P21      |              | MTIOC1B/TMCI0                  | RXD0/SMISO0/SSCL0                             |                           |

| 28         |                                           | P20      |              | MTIOC1A/TMRI0                  | TXD0/SMOSI0/SSDA0                             |                           |

| 29         |                                           | P17      |              | MTIOC3A/MTIOC3B/<br>TMO1/POE8# | SCK1/MISOA/<br>SDA-DS                         | IRQ7                      |

| 30         |                                           | P16      |              | MTIOC3C/MTIOC3D/<br>TMO2       | TXD1/SMOSI1/SSDA1/<br>MOSIA/SCL-DS            | IRQ6/RTCOUT/<br>ADTRG0#   |

| 31         |                                           | P15      |              | MTIOC0B/MTCLKB/<br>TMCl2       | RXD1/SMISO1/SSCL1                             | IRQ5                      |

| 32         |                                           | P14      |              | MTIOC3A/MTCLKA/<br>TMRI2       | CTS1#/RTS1#/SS1#                              | IRQ4                      |

| 33         |                                           | P13      |              | MTIOC0B/TMO3                   | SDA                                           | IRQ3                      |

| 34         |                                           | P12      |              | TMCI1                          | SCL                                           | IRQ2                      |

| 35         |                                           | PH3      |              | TMCI0                          |                                               |                           |

| 36         |                                           | PH2      |              | TMRI0                          |                                               | IRQ1                      |

| 37         |                                           | PH1      |              | TMO0                           |                                               | IRQ0                      |

| 38         |                                           | PH0      |              |                                |                                               | CACREF                    |

| 39         |                                           | P55      | WAIT#        | MTIOC4D/TMO3                   |                                               |                           |

| 40         |                                           | P54      | ALE          | MTIOC4B/TMCI1                  |                                               |                           |

| 41         | BCLK                                      | P53      |              |                                |                                               |                           |

### Table 1.12 List of Pins and Pin Functions (100-Pin LQFP) (1 / 3)

# 2.1 General-Purpose Registers (R0 to R15)

This CPU has sixteen general-purpose registers (R0 to R15). R1 to R15 can be used as data registers or address registers. R0, a general-purpose register, also functions as the stack pointer (SP). The stack pointer is switched to operate as the interrupt stack pointer (ISP) or user stack pointer (USP) by the value of the stack pointer select bit (U) in the processor status word (PSW).

# 2.2 Control Registers

# (1) Interrupt Stack Pointer (ISP)/User Stack Pointer (USP)

The stack pointer (SP) can be either of two types, the interrupt stack pointer (ISP) or the user stack pointer (USP). Whether the stack pointer operates as the ISP or USP depends on the value of the stack pointer select bit (U) in the processor status word (PSW).

Set the ISP or USP to a multiple of four, as this reduces the numbers of cycles required to execute interrupt sequences and instructions entailing stack manipulation.

### (2) Interrupt Table Register (INTB)

The interrupt table register (INTB) specifies the address where the relocatable vector table starts.

### (3) Program Counter (PC)

The program counter (PC) indicates the address of the instruction being executed.

### (4) Processor Status Word (PSW)

The processor status word (PSW) indicates the results of instruction execution or the state of the CPU.

### (5) Backup PC (BPC)

The backup PC (BPC) is provided to speed up response to interrupts. After a fast interrupt has been generated, the contents of the program counter (PC) are saved in the BPC register.

### (6) Backup PSW (BPSW)

The backup PSW (BPSW) is provided to speed up response to interrupts.

After a fast interrupt has been generated, the contents of the processor status word (PSW) are saved in the BPSW. The allocation of bits in the BPSW corresponds to that in the PSW.

### (7) Fast Interrupt Vector Register (FINTV)

The fast interrupt vector register (FINTV) is provided to speed up response to interrupts. The FINTV register specifies a branch destination address when a fast interrupt has been generated.

# 2.3 Register Associated with DSP Instructions

### (1) Accumulator (ACC)

The accumulator (ACC) is a 64-bit register used for DSP instructions. The accumulator is also used for the multiply and multiply-and-accumulate instructions; EMUL, EMULU, MUL, and RMPA, in which case the prior value in the accumulator is modified by execution of the instruction.

Use the MVTACHI and MVTACLO instructions for writing to the accumulator. The MVTACHI and MVTACLO instructions write data to the higher-order 32 bits (bits 63 to 32) and the lower-order 32 bits (bits 31 to 0), respectively. Use the MVFACHI and MVFACMI instructions for reading data from the accumulator. The MVFACHI and MVFACMI instructions read data from the higher-order 32 bits (bits 63 to 32) and the middle 32 bits (bits 47 to 16), respectively.

# [Chip version B with 256 Kbytes or less of flash memory and 48 to 100 pins]

# Table 5.12DC Characteristics (11)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|                  | ltem                      |                       |                                                      |               |                 | Тур. | Max. | Unit | Test<br>Conditions |

|------------------|---------------------------|-----------------------|------------------------------------------------------|---------------|-----------------|------|------|------|--------------------|

| Supply current*1 | High-speed operating mode | Normal operating mode | No peripheral operation* <sup>2</sup>                | ICLK = 50 MHz | I <sub>CC</sub> | 7.2  | _    | mA   |                    |

|                  |                           |                       | All peripheral<br>operation:<br>Normal* <sup>3</sup> | ICLK = 50 MHz |                 | 23.5 | _    |      |                    |

|                  |                           |                       | All peripheral operation: Max.* <sup>3</sup>         | ICLK = 50 MHz |                 | _    | 45   |      |                    |

|                  |                           | Sleep mode            | No peripheral operation                              | ICLK = 50 MHz |                 | 4.3  |      |      |                    |

|                  |                           |                       | All peripheral operation: Normal                     | ICLK = 50 MHz |                 | 12   | _    |      |                    |

|                  |                           | All-module clock st   | top mode                                             | ICLK = 50 MHz |                 | 3.7  |      |      |                    |

|                  |                           | Increase during BC    | GO operation*4                                       |               |                 | 20   |      |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

Note 3. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are ICLK divided by 2.

Note 4. This is the increase if data is programmed to or erasing from the ROM or E2 DataFlash during program execution.

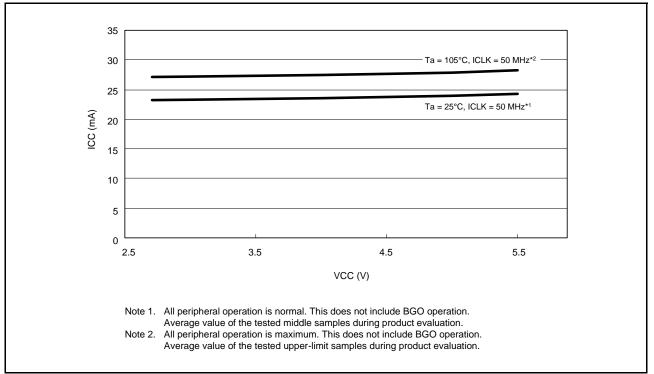

Figure 5.17 Voltage Dependency in High-Speed Operating Mode (Reference Data) for Chip Version B with 256 Kbytes or Less of Flash Memory and 48 to 100 Pins

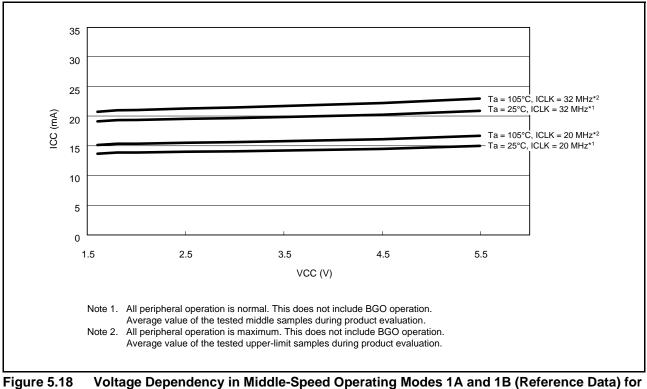

Chip Version B with 256 Kbytes or Less of Flash Memory and 48 to 100 Pins

RENESAS

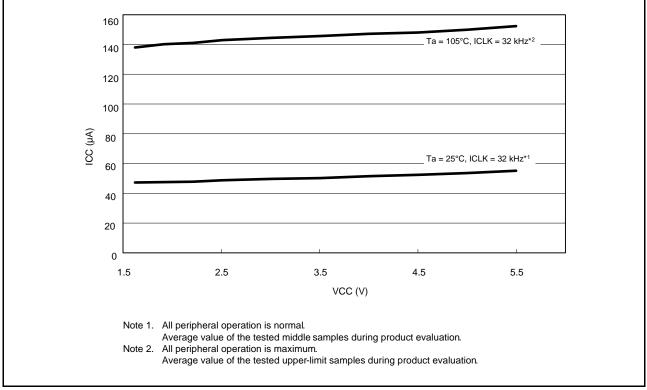

Figure 5.21 Voltage Dependency in Low-Speed Operating Mode 2 (Reference Data) for Chip Version B with 256 Kbytes or Less of Flash Memory and 48 to 100 Pins

# [Chip version B with 768 Kbytes/1 Mbyte of flash memory and 100 to 145 pins]

### Table 5.16DC Characteristics (15)

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|                                              |                              | Item                              |                                                      |                 | Symbol          | Тур. | Max. | Unit | Test<br>Condition |

|----------------------------------------------|------------------------------|-----------------------------------|------------------------------------------------------|-----------------|-----------------|------|------|------|-------------------|

| Supply                                       | Middle-speed                 | Normal                            | No peripheral                                        | ICLK = 32 MHz*2 | I <sub>CC</sub> | 5.6  | _    | mA   |                   |

| current*1                                    | operating modes<br>1A and 1B | operating mode                    | operation                                            | ICLK = 20 MHz*3 |                 | 4.6  | _    |      |                   |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz*4 |                 | 25.5 | _    |      |                   |

|                                              |                              |                                   | operation:<br>Normal                                 | ICLK = 20 MHz*5 |                 | 17.6 | _    |      |                   |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz*4 |                 | _    | 35   |      |                   |

|                                              |                              |                                   | operation: Max.                                      | ICLK = 20 MHz*5 |                 | _    |      |      |                   |

|                                              |                              | Sleep mode                        | No peripheral                                        | ICLK = 32 MHz   |                 | 3.4  | _    |      |                   |

|                                              |                              |                                   | operation                                            | ICLK = 20 MHz   |                 | 3.3  | _    |      |                   |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz   |                 | 13.4 | _    |      |                   |

|                                              |                              |                                   | operation:<br>Normal                                 | ICLK = 20 MHz   |                 | 10.2 | _    |      |                   |

|                                              |                              | All-module clock s                | stop mode                                            | ICLK = 32 MHz   |                 | 3    | _    |      |                   |

|                                              |                              |                                   |                                                      | ICLK = 20 MHz   |                 | 3    | _    |      |                   |

|                                              |                              | Increase during Middle-speed oper |                                                      | rating mode 1A  |                 | 23   | _    |      |                   |

|                                              |                              | BGO operation*6                   | Middle-speed ope                                     | rating mode 1B  |                 | 20   | _    |      |                   |

| Middle-speed<br>operating modes<br>2A and 2B | Normal                       | No peripheral                     | ICLK = 32 MHz                                        |                 | 5.1             | _    |      |      |                   |

|                                              | operating mode               | operation*2                       | ICLK = 16 MHz                                        |                 | 3.5             | _    |      |      |                   |

|                                              |                              |                                   | ICLK = 8 MHz                                         |                 | 2.7             | _    |      |      |                   |

|                                              |                              |                                   | All peripheral<br>operation:<br>Normal* <sup>4</sup> | ICLK = 32 MHz   |                 | 25   | _    |      |                   |

|                                              |                              |                                   |                                                      | ICLK = 16 MHz   |                 | 14   | _    |      |                   |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 | 8.5  | _    |      |                   |

|                                              |                              |                                   | All peripheral operation: Max.*4                     | ICLK = 32 MHz   |                 | _    | 34   |      |                   |

|                                              |                              |                                   |                                                      | ICLK = 16 MHz   |                 | _    | _    |      |                   |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 | _    | _    |      |                   |

|                                              |                              | Sleep mode                        | No peripheral                                        | ICLK = 32 MHz   |                 | 2.9  | _    |      |                   |

|                                              |                              |                                   | operation                                            | ICLK = 16 MHz   |                 | 2.5  | _    |      |                   |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 | 2.2  | _    |      |                   |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz   |                 | 13   | _    |      |                   |

|                                              |                              |                                   | operation:<br>Normal                                 | ICLK = 16 MHz   |                 | 8.2  | _    |      |                   |

|                                              |                              |                                   | Normai                                               | ICLK = 8 MHz    |                 | 5.8  | _    |      |                   |

|                                              | All-module clock s           | stop mode                         | ICLK = 32 MHz                                        |                 | 2.5             | _    |      |      |                   |

|                                              |                              |                                   | ICLK = 16 MHz                                        |                 | 2.2             | _    |      |      |                   |

|                                              |                              |                                   | ICLK = 8 MHz                                         |                 | 2.1             | _    |      |      |                   |

|                                              |                              | Increase during                   | Middle-speed ope                                     | rating mode 1A  |                 | 23   | —    |      |                   |

|                                              |                              | BGO operation*6                   | Middle-speed ope                                     | rating mode 1B  |                 | 20   | _    |      |                   |

# [Chip version B with 512 Kbytes or less of flash memory and 144 and 145 pins]

### Table 5.18DC Characteristics (17)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|                  | Item                      |                       |                                                |               |                 | Тур. | Max. | Unit | Test<br>Conditions |

|------------------|---------------------------|-----------------------|------------------------------------------------|---------------|-----------------|------|------|------|--------------------|

| Supply current*1 | High-speed operating mode | Normal operating mode | No peripheral operation* <sup>2</sup>          | ICLK = 50 MHz | I <sub>CC</sub> | 7.2  | —    | mA   |                    |

|                  |                           |                       | All peripheral operation: Normal* <sup>3</sup> | ICLK = 50 MHz |                 | 25.9 | —    |      |                    |

|                  |                           |                       | All peripheral operation: Max.* <sup>3</sup>   | ICLK = 50 MHz |                 |      | 45   |      |                    |

|                  |                           | Sleep mode            | No peripheral operation                        | ICLK = 50 MHz |                 | 4.3  | —    |      |                    |

|                  |                           |                       | All peripheral operation: Normal               | ICLK = 50 MHz |                 | 13   | —    |      |                    |

|                  |                           | All-module clock st   | top mode                                       |               |                 | 3.7  | —    |      |                    |

|                  |                           | Increase during BC    | GO operation*4                                 |               |                 | 21   | _    |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

Note 3. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are ICLK divided by 2.

Note 4. This is the increase if data is programmed to or erasing from the ROM or E2 DataFlash during program execution.

### [Chip version B with 512 Kbytes or less of flash memory and 144 and 145 pins]

### Table 5.19DC Characteristics (18)

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|                                              |                              | Item                              |                                                      |                 | Symbol          | Тур. | Max. | Unit | Test<br>Conditions |

|----------------------------------------------|------------------------------|-----------------------------------|------------------------------------------------------|-----------------|-----------------|------|------|------|--------------------|

| Supply                                       | Middle-speed                 | Normal                            | No peripheral                                        | ICLK = 32 MHz*2 | I <sub>CC</sub> | 5.3  | —    | mA   |                    |

| current*1                                    | operating modes<br>1A and 1B | operating mode                    | operation                                            | ICLK = 20 MHz*3 |                 | 4.6  | —    |      |                    |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz*4 |                 | 22.3 | —    |      |                    |

|                                              |                              |                                   | operation:<br>Normal                                 | ICLK = 20 MHz*5 |                 | 15.6 | —    |      |                    |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz*4 |                 | _    | 35   |      |                    |

|                                              |                              |                                   | operation: Max.                                      | ICLK = 20 MHz*5 |                 | _    | —    |      |                    |

|                                              |                              | ope<br>All                        | No peripheral                                        | ICLK = 32 MHz   |                 | 3.4  | —    |      |                    |

|                                              |                              |                                   | operation                                            | ICLK = 20 MHz   |                 | 3.3  | —    |      |                    |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz   |                 | 12.8 | —    |      |                    |

|                                              |                              |                                   | operation:<br>Normal                                 | ICLK = 20 MHz   |                 | 9.8  | —    |      |                    |

|                                              |                              | All-module clock stop mode        |                                                      | ICLK = 32 MHz   |                 | 3    | _    |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 20 MHz   |                 | 3    | —    |      |                    |

|                                              |                              | Increase during Middle-speed oper |                                                      | rating mode 1A  |                 | 21   | _    |      |                    |

|                                              |                              | BGO operation*6                   | Middle-speed ope                                     | rating mode 1B  |                 | 19   | —    |      |                    |

| Middle-speed<br>operating modes<br>2A and 2B |                              | No peripheral                     | ICLK = 32 MHz                                        |                 | 4.7             | —    |      |      |                    |

|                                              |                              | operation*2                       | ICLK = 16 MHz                                        |                 | 3.4             | —    |      |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 | 2.7  | —    |      |                    |

|                                              |                              |                                   | All peripheral<br>operation:<br>Normal* <sup>4</sup> | ICLK = 32 MHz*3 |                 | 21.7 | —    |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 16 MHz*3 |                 | 12.3 | —    |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 | 7.6  | —    |      |                    |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz*3 |                 |      | 34   |      |                    |

|                                              |                              |                                   | operation: Max.*4                                    | ICLK = 16 MHz*3 |                 |      | —    |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 |      | —    |      |                    |

|                                              |                              | Sleep mode                        | No peripheral                                        | ICLK = 32 MHz   |                 | 2.9  | —    |      |                    |

|                                              |                              |                                   | operation                                            | ICLK = 16 MHz   |                 | 2.5  | —    |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 | 2.2  | —    |      |                    |

|                                              |                              |                                   | All peripheral                                       | ICLK = 32 MHz   |                 | 12.3 | —    |      |                    |

|                                              |                              |                                   | operation:<br>Normal                                 | ICLK = 16 MHz   | 7.              | 7.8  | —    |      |                    |

|                                              |                              | Norman                            | ICLK = 8 MHz                                         | 5               | 5.6             | —    |      |      |                    |

|                                              |                              | All-module clock                  | stop mode                                            | ICLK = 32 MHz   |                 | 2.5  | —    |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 16 MHz   |                 | 2.2  | —    |      |                    |

|                                              |                              |                                   |                                                      | ICLK = 8 MHz    |                 | 2.1  | —    |      |                    |

|                                              |                              | Increase during                   | Middle-speed ope                                     | rating mode 1A  |                 | 21   | _    |      |                    |

|                                              |                              | BGO operation*6                   | Middle-speed ope                                     | rating mode 1B  |                 | 19   | —    |      |                    |

# 5.3.3 Timing of Recovery from Low Power Consumption Modes

[Chip versions A and C]

### Table 5.46 Timing of Recovery from Low Power Consumption Modes

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|                                                  | Item                                                |                                                 | Symbol              | Min.            | Тур. | Max. | Unit | Test<br>Conditions |

|--------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|---------------------|-----------------|------|------|------|--------------------|

| Recovery time<br>after                           | Crystal resonator connected to                      | Main clock oscillator<br>operating              | t <sub>SBYMC</sub>  | _               | 3    | —    | ms   | Figure 5.72        |

| cancellation of<br>software<br>standby mode      | main clock<br>oscillator* <sup>2</sup>              | Main clock oscillator and PLL circuit operating | t <sub>SBYPC</sub>  | —               | 3.5  | —    | ms   |                    |

| (flash memory,<br>HOCO power                     | External clock<br>input to main                     | Main clock oscillator<br>operating              | t <sub>SBYEX</sub>  | 10              |      | —    | μs   | -                  |

| supplied)<br>(SOFTCUT[2:0]<br>bits = 000b)*1     | clock oscillator                                    | Main clock oscillator and PLL circuit operating | t <sub>SBYPE</sub>  | 0.5             |      |      | ms   |                    |

| 0000)                                            | Sub-clock oscillato                                 | or operating                                    | t <sub>SBYSC</sub>  | 2* <sup>3</sup> |      | —    | S    |                    |

|                                                  | HOCO clock oscill                                   | ator operating                                  | t <sub>SBYHO</sub>  | _               |      | 500  | μs   |                    |

|                                                  | LOCO clock oscilla                                  | ator operating                                  | t <sub>SBYLO</sub>  | _               | —    | 90   | μs   |                    |

| Recovery time<br>after                           | Crystal resonator connected to                      | Main clock oscillator<br>operating              | t <sub>SBYMC</sub>  | —               | 3    | —    | ms   | Figure 5.72        |

| cancellation of<br>software<br>standby mode      | main clock<br>oscillator*2                          | Main clock oscillator and PLL circuit operating | t <sub>SBYPC</sub>  | —               | 3.5  | —    | ms   |                    |

| (flash memory power supplied,                    | External clock<br>input to main<br>clock oscillator | Main clock oscillator<br>operating              | t <sub>SBYEX</sub>  | 40              | _    | —    | μs   |                    |

| HOCO power<br>not supplied)<br>(SOFTCUT[2:0]     |                                                     | Main clock oscillator and PLL circuit operating | t <sub>SBYPE</sub>  | 0.5             | —    | —    | ms   |                    |

| bits = $110b$ )* <sup>1</sup>                    | Sub-clock oscillato                                 | t <sub>SBYSC</sub>                              | 2* <sup>3</sup>     | —               | _    | S    |      |                    |

|                                                  | HOCO clock oscill                                   | ator operating                                  | t <sub>SBYHO</sub>  | _               |      | 1.2  | ms   |                    |

|                                                  | LOCO clock oscilla                                  | ator operating                                  | t <sub>SBYLO</sub>  | _               | —    | 90   | μs   |                    |

| Recovery time<br>after                           | Crystal resonator connected to                      | Main clock oscillator<br>operating              | t <sub>SBYMC</sub>  | _               | 3    | —    | ms   | Figure 5.72        |

| cancellation of<br>software<br>standby mode      | main clock<br>oscillator* <sup>2</sup>              | Main clock oscillator and PLL circuit operating | t <sub>SBYPC</sub>  | _               | 3.5  | —    | ms   |                    |

| (flash memory,<br>HOCO power                     | External clock input to main                        | Main clock oscillator<br>operating              | t <sub>SBYEX</sub>  | 100             | —    | —    | μs   |                    |

| not supplied)<br>(SOFTCUT[2:0]<br>bits = 111b)*1 | clock oscillator                                    | Main clock oscillator and PLL circuit operating | t <sub>SBYPE</sub>  | 0.5             |      | —    | ms   |                    |

| 510 - 110)                                       | Sub-clock oscillate                                 | r operating                                     | t <sub>SBYSC</sub>  | 2*4             | —    | —    | S    | ]                  |

|                                                  | HOCO clock oscill                                   | ator operating                                  | t <sub>SBYHO</sub>  | —               | —    | 1.2  | ms   | •                  |

|                                                  | LOCO clock oscilla                                  | ator operating                                  | t <sub>SBYLO</sub>  | —               | —    | 10   | ms   |                    |

| Recovery time af                                 | ter cancellation of d                               | eep software standby mode                       | t <sub>DSBY</sub>   | _               |      | 8    | ms   | Figure 5.73        |

| Wait time after ca                               | ancellation of deep s                               | oftware standby mode                            | t <sub>DSBYWT</sub> | _               | _    | 0.8  | ms   |                    |

Note 1. The recovery time varies depending on the state of each oscillator when the WAIT instruction is executed. The recovery time when multiple oscillators are operating varies depending on the operating state of the oscillators that are not selected as the system clock source, and depends on the time set in the wait control registers corresponding to the oscillators.

Note 2. The indicated value is measured for an 8 MHz crystal resonator.

Note 3. When RCR3.RTCEN = 1, the time will be the time set in the SOSCWTCR register minus 2 s.

Note 4. When RCR3.RTCEN = 1, the time will be the time set in the SOSCWTCR register minus 2 s and plus 31.25 ms.

### Table 5.52 Bus Timing (Multiplexed Bus) (1)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V, fBCLK ≤ 25 MHz (BCLK pin output frequency ≤ 12.5 MHz),  $T_a = -40$  to +105°C,  $V_{OH} = VCC \times 0.5$ ,  $V_{OL} = VCC \times 0.5$ ,  $I_{OH} = -1.0$  mA,  $I_{OL} = 1.0$  mA,  $C_L = 30$  pF Where neural extent is each start where drive preservices

When normal output is selected by the drive capacity register

| Item                    | Symbol            | Min. | Тур. | Max. | Unit            |

|-------------------------|-------------------|------|------|------|-----------------|

| Address delay time      | t <sub>AD</sub>   | —    | 60   | ns   | Figure 5.81 and |

| Byte control delay time | t <sub>BCD</sub>  | _    | 60   | ns   | Figure 5.82     |

| CS# delay time          | t <sub>CSD</sub>  | _    | 60   | ns   |                 |

| RD# delay time          | t <sub>RSD</sub>  | —    | 60   | ns   |                 |

| ALE delay time          | t <sub>ALED</sub> | —    | 60   | ns   |                 |

| Read data setup time    | t <sub>RDS</sub>  | 40   | —    | ns   |                 |

| Read data hold time     | t <sub>RDH</sub>  | 0    | —    | ns   |                 |

| WR# delay time          | t <sub>WRD</sub>  | —    | 60   | ns   |                 |

| Write data delay time   | t <sub>WDD</sub>  | —    | 60   | ns   |                 |

| Write data hold time    | t <sub>WDH</sub>  | 0    | —    | ns   |                 |

| WAIT# setup time        | t <sub>WTS</sub>  | 40   | —    | ns   | Figure 5.80     |

| WAIT# hold time         | t <sub>WTH</sub>  | 0    | —    | ns   | 7               |

### Table 5.53 Bus Timing (Multiplexed Bus) (2)

Conditions: VCC = AVCC0 = 1.8 to 2.7 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V, fBCLK ≤ 16 MHz (BCLK pin output frequency ≤ 8 MHz),  $T_a = -40$  to +105°C,  $V_{OH} = VCC \times 0.5$ ,  $V_{OL} = VCC \times 0.5$ ,  $I_{OH} = -1.0$  mA,  $I_{OL} = 1.0$  mA,  $C_L = 30$  pF When normal output is selected by the drive capacity register

| Item                    | Symbol            | Min. | Тур. | Max. | Unit            |

|-------------------------|-------------------|------|------|------|-----------------|

| Address delay time      | t <sub>AD</sub>   | —    | 90   | ns   | Figure 5.81 and |

| Byte control delay time | t <sub>BCD</sub>  | —    | 90   | ns   | Figure 5.82     |

| CS# delay time          | t <sub>CSD</sub>  | _    | 90   | ns   |                 |

| RD# delay time          | t <sub>RSD</sub>  | —    | 90   | ns   |                 |

| ALE delay time          | t <sub>ALED</sub> | —    | 90   | ns   |                 |

| Read data setup time    | t <sub>RDS</sub>  | 60   | —    | ns   |                 |

| Read data hold time     | t <sub>RDH</sub>  | 0    | —    | ns   |                 |

| WR# delay time          | t <sub>WRD</sub>  | —    | 90   | ns   |                 |

| Write data delay time   | t <sub>WDD</sub>  | —    | 90   | ns   |                 |

| Write data hold time    | t <sub>WDH</sub>  | 0    | —    | ns   |                 |

| WAIT# setup time        | t <sub>WTS</sub>  | 60   | —    | ns   | Figure 5.80     |

| WAIT# hold time         | t <sub>WTH</sub>  | 0    | —    | ns   | 7               |

#### Table 5.60 **Timing of On-Chip Peripheral Modules (6)**

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V, fPCLKB = up to 32 MHz,  $T_a = -40 \text{ to } +105^{\circ}\text{C}$

When high-drive output is selected by the drive capacity register

|                               | Item                                    | Symbol            | Min.*1                 | Max.                     | Unit | Test<br>Conditions |  |

|-------------------------------|-----------------------------------------|-------------------|------------------------|--------------------------|------|--------------------|--|

| Simple IIC<br>(Standard mode) | SDA input rise time                     | t <sub>Sr</sub>   | _                      | 1000                     | ns   | Figure             |  |

|                               | SDA input fall time                     | t <sub>Sf</sub>   | _                      | 300                      | ns   | IS                 |  |

|                               | SDA input spike pulse removal time      | t <sub>SP</sub>   | 0                      | $4 \times t_{pcyc}^{*2}$ | ns   |                    |  |

|                               | Data input setup time                   | t <sub>SDAS</sub> | 250                    | _                        | ns   |                    |  |

|                               | Data input hold time                    | t <sub>SDAH</sub> | 0                      | _                        | ns   |                    |  |

|                               | SCL, SDA capacitive load                | Cb                | _                      | 400                      | pF   | 1                  |  |

| Simple IIC<br>(Fast mode)     | SCL, SDA input rise time                | t <sub>Sr</sub>   | 20 + 0.1C <sub>b</sub> | 300                      | ns   | Figure<br>5.98     |  |

|                               | SCL, SDA input fall time                | t <sub>Sf</sub>   | 20 + 0.1C <sub>b</sub> | 300                      | ns   |                    |  |

|                               | SCL, SDA input spike pulse removal time | t <sub>SP</sub>   | 0                      | $4 \times t_{pcyc}^{*2}$ | ns   |                    |  |

|                               | Data input setup time                   | t <sub>SDAS</sub> | 100                    | _                        | ns   |                    |  |

|                               | Data input hold time                    | t <sub>SDAH</sub> | 0                      | —                        | ns   |                    |  |

|                               | SCL, SDA capacitive load                | C <sub>b</sub>    | —                      | 400                      | pF   |                    |  |

Note: •  $t_{Pcyc}$ : PCLK cycle Note 1.  $C_b$  indicates the total capacity of the bus line. Note 2. This applies when the SMR.CKS[1:0] bits = 00b and the SNFR.NFCS[2:0] bits = 010b while the SNFR.NFE bit = 1 and the digital filter is enabled.

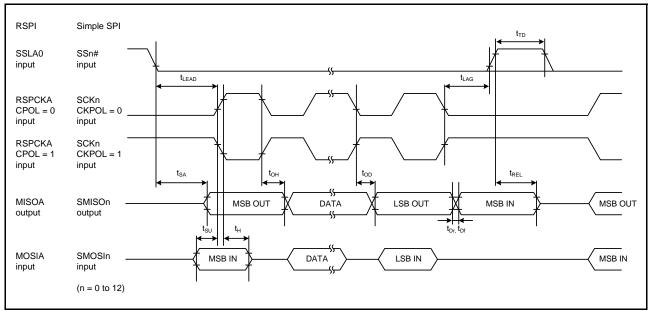

Figure 5.96 RSPI Timing (Slave, CPHA = 0) and Simple SPI Timing (Slave, CKPH = 1)

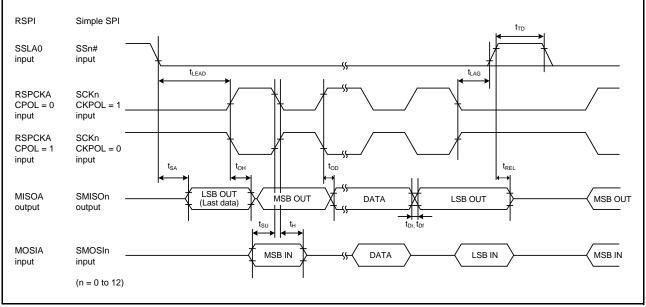

Figure 5.97 RSPI Timing (Slave, CPHA = 1) and Simple SPI Timing (Slave, CKPH = 0)

# 5.4 A/D Conversion Characteristics

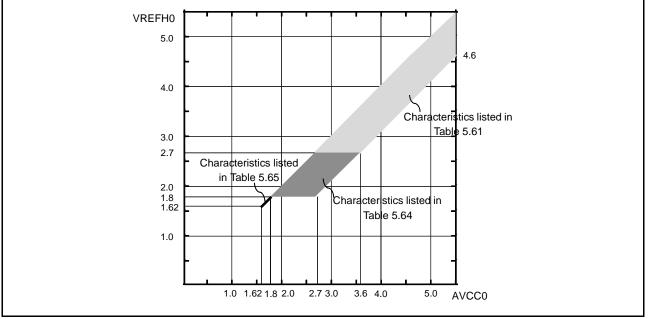

### Table 5.61 A/D Conversion Characteristics (1)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH0  $\ge$  2.7 V, AVCC0-0.9 V  $\le$  VREFH0  $\le$  AVCC0\*3,

| $VSS = AVSS0 = VREFL = VREFL0 = 0 V, T_a =$ | –40 to +105°C |

|---------------------------------------------|---------------|

|---------------------------------------------|---------------|

|                                                        | Min.                                                               | Тур.                       | Max.  | Unit | Test Conditions          |                          |

|--------------------------------------------------------|--------------------------------------------------------------------|----------------------------|-------|------|--------------------------|--------------------------|

| A/D conversion clock frequency (fPCLKD)                |                                                                    | 1                          | —     | 50   | MHz                      |                          |

| Resolution                                             |                                                                    | _                          | —     | 12   | Bit                      |                          |

| Conversion time*1<br>(Operation at<br>fPCLKD = 50 MHz) | Permissible signal source impedance (Max.) = $0.5 \text{ k}\Omega$ | 1.0<br>(0.4)* <sup>2</sup> | —     | _    | μs                       | Sampling in 20 states    |

|                                                        | Permissible signal source<br>impedance (Max.) = 1 kΩ               | 1.1<br>(0.5)* <sup>2</sup> | —     | —    |                          | Sampling in 25 states    |

|                                                        | Permissible signal source<br>impedance (Max.) = 5 kΩ               | 1.5<br>(0.9)*2             | —     | —    |                          | Sampling in 45 states    |

| Analog input capacitance                               |                                                                    | _                          | —     | 30   | pF                       |                          |

| Offset error                                           |                                                                    | _                          | ±0.5  | ±4.5 | LSB                      | High-precision channel   |

|                                                        |                                                                    |                            |       | ±7.5 |                          | Normal-precision channel |

| Full-scale error                                       |                                                                    | _                          | ±0.75 | ±4.5 | LSB                      | High-precision channel   |

|                                                        |                                                                    |                            |       | ±7.5 |                          | Normal-precision channel |

| Quantization error                                     |                                                                    | _                          | ±0.5  | _    | LSB                      |                          |

| Absolute accuracy                                      |                                                                    | _                          | ±1.25 | ±5.0 | LSB                      | High-precision channel   |

|                                                        |                                                                    | ±1.25                      | ±8.0  | LSB  | Normal-precision channel |                          |

| DNL differential nonlinearity error                    |                                                                    | _                          | ±1.0  | —    | LSB                      |                          |

| INL integral nonlinea                                  | _                                                                  | ±1.0                       | ±3.0  | LSB  |                          |                          |

Note: • PCLKD must be set to 40 MHz or lower when HOCO is to be selected as the A/D conversion clock. The characteristics apply when no pin functions other than A/D converter input are used. Absolute accuracy includes quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note: • When using the channel-dedicated sample-and-hold circuit, use the AN000 to AN002 analog input voltage (V<sub>AN</sub>) that satisfies all the following conditions:  $0.25 \text{ V} \le \text{V}_{AN} \le \text{AVCC0} - 0.25 \text{ V}$ ,  $\text{V}_{AN} \le \text{VREFH0}$ , and  $\text{AVCC0} \ge 2.7 \text{ V}$ .

Note 1. The conversion time is the sum of the sampling time and the comparison time. As the test conditions, the number of sampling states is indicated.

Note 2. The value in parentheses indicates the sampling time.

Note 3. When using the temperature sensor, use it when AVCC0 = VREFH0.

Figure 5.99 AVCC0 to VREFH0 Voltage Range

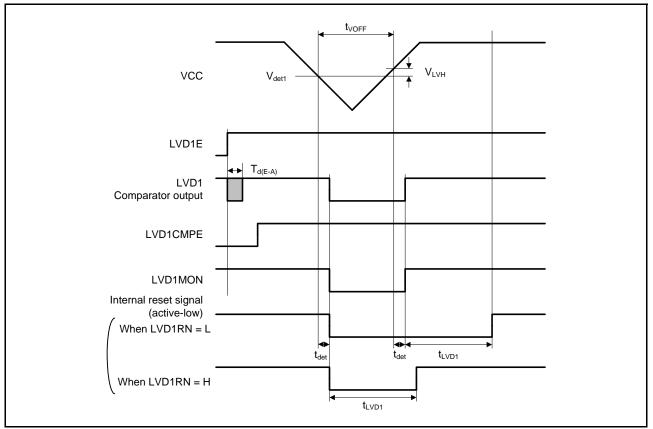

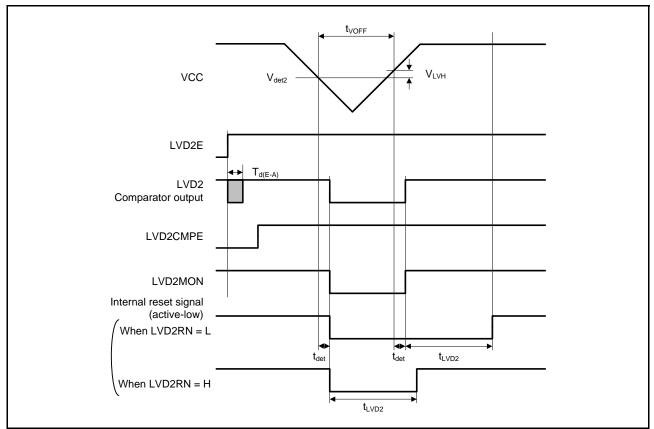

Figure 5.106 Voltage Detection Circuit Timing (V<sub>det1</sub>)

Figure 5.107 Voltage Detection Circuit Timing (V<sub>det2</sub>)

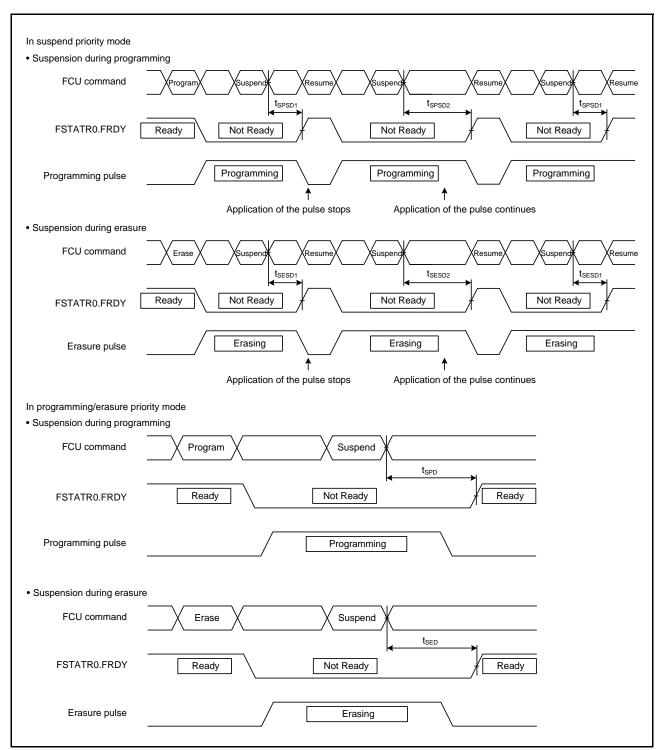

Figure 5.109 Flash Memory Program/Erase Suspend Timing

| Dav  | Data         |                                                                                                                                                                                                                                                                                                                                                                                    | Description                                                                                                              |  |  |  |

|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Rev. | Date         | Page                                                                                                                                                                                                                                                                                                                                                                               | Summary                                                                                                                  |  |  |  |

| 1.40 | Feb 19, 2013 | 96                                                                                                                                                                                                                                                                                                                                                                                 | Table 5.11 DC Characteristics (10), changed                                                                              |  |  |  |