#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 84                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TFLGA                                                                        |

| Supplier Device Package    | 100-TFLGA (7x7)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f52108cdlj-u0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

RX210 Group

#### 1.2 List of Products

Table 1.3 to Table 1.7 are a list of products, and Figure 1.1 shows how to read the product part no., memory capacity, and package type.

| Group | Part No.     | Orderable Part No. | Package      | ROM<br>Capacity | RAM<br>Capacity | E2<br>DataFlash | Operating<br>Frequency<br>(Max.) | Operating<br>Temperature |

|-------|--------------|--------------------|--------------|-----------------|-----------------|-----------------|----------------------------------|--------------------------|

| RX210 | R5F52108ADFP | R5F52108ADFP#V0    | PLQP0100KB-A |                 |                 |                 |                                  |                          |

|       | R5F52108ADFN | R5F52108ADFN#V0    | PLQP0080KB-A | 540 Khutaa      |                 |                 |                                  |                          |

|       | R5F52108ADFM | R5F52108ADFM#V0    | PLQP0064KB-A | 512 Kbytes      |                 |                 |                                  |                          |

|       | R5F52108ADLJ | R5F52108ADLJ#U0    | PTLG0100JA-A |                 | C 4 Khutaa      |                 | 50 MHz                           |                          |

|       | R5F52107ADFP | R5F52107ADFP#V0    | PLQP0100KB-A |                 | 64 Kbytes       |                 |                                  | 40.40.19590              |

|       | R5F52107ADFN | R5F52107ADFN#V0    | PLQP0080KB-A | 004141          |                 |                 |                                  |                          |

|       | R5F52107ADFM | R5F52107ADFM#V0    | PLQP0064KB-A | - 384 Kbytes    |                 |                 |                                  |                          |

|       | R5F52107ADLJ | R5F52107ADLJ#U0    | PTLG0100JA-A |                 |                 |                 |                                  |                          |

|       | R5F52106ADFP | R5F52106ADFP#V0    | PLQP0100KB-A |                 |                 | 8 Kbytes        |                                  | –40 to +85°C             |

|       | R5F52106ADFN | R5F52106ADFN#V0    | PLQP0080KB-A | OFC Khutaa      | 00 1/1-1        |                 |                                  |                          |

|       | R5F52106ADFM | R5F52106ADFM#V0    | PLQP0064KB-A | 256 Kbytes      | 32 Kbytes       |                 |                                  |                          |

|       | R5F52106ADLJ | R5F52106ADLJ#U0    | PTLG0100JA-A |                 |                 |                 |                                  |                          |

|       | R5F52105ADFP | R5F52105ADFP#V0    | PLQP0100KB-A |                 | 5 20 Kbytes     |                 |                                  |                          |

|       | R5F52105ADFN | R5F52105ADFN#V0    | PLQP0080KB-A | 100 Khut        |                 |                 |                                  |                          |

|       | R5F52105ADFM | R5F52105ADFM#V0    | PLQP0064KB-A | 128 Kbytes      |                 |                 |                                  |                          |

|       | R5F52105ADLJ | R5F52105ADLJ#U0    | PTLG0100JA-A | 1               |                 |                 |                                  |                          |

List of Products Chip Version A: D Version (Ta = -40 to +85°C) Table 1.3

Note: • Orderable part numbers are current as of when this manual was published. Please make sure to refer to the relevant product page on the Renesas website for the latest part numbers.

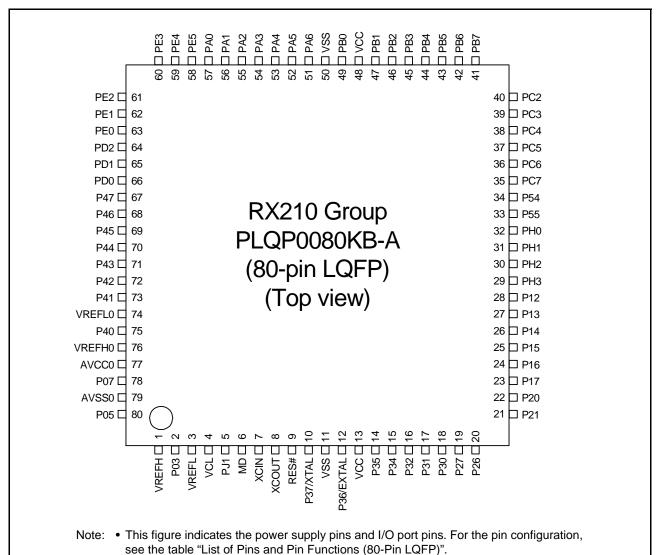

Figure 1.7 Pin Assignments of the 80-Pin LQFP

| Pin | Power Supply, Clock, |          |              | Timers          | Communications           |         |

|-----|----------------------|----------|--------------|-----------------|--------------------------|---------|

| No. | System Control       | I/O Port | External Bus | (MTU, TMR, POE) | (SCIc, SCId, RSPI, RIIC) | Others  |

| 122 |                      | PD4      | D4[A4/D4]    | POE3#           |                          | IRQ4    |

| 123 |                      | PD3      | D3[A3/D3]    | POE8#           |                          | IRQ3    |

| 124 |                      | PD2      | D2[A2/D2]    | MTIOC4D         |                          | IRQ2    |

| 125 |                      | PD1      | D1[A1/D1]    | MTIOC4B         |                          | IRQ1    |

| 126 |                      | PD0      | D0[A0/D0]    |                 |                          | IRQ0    |

| 127 |                      | P93      |              |                 | CTS7#/RTS7#/SS7#         |         |

| 128 |                      | P92      |              |                 | RXD7/SMISO7/SSCL7        |         |

| 129 |                      | P91      |              |                 | SCK7                     |         |

| 130 | VSS                  |          |              |                 |                          |         |

| 131 |                      | P90      |              |                 | TXD7/SMOSI7/SSDA7        |         |

| 132 | VCC                  |          |              |                 |                          |         |

| 133 |                      | P47      |              |                 |                          | AN007   |

| 134 |                      | P46      |              |                 |                          | AN006   |

| 135 |                      | P45      |              |                 |                          | AN005   |

| 136 |                      | P44      |              |                 |                          | AN004   |

| 137 |                      | P43      |              |                 |                          | AN003   |

| 138 |                      | P42      |              |                 |                          | AN002   |

| 139 |                      | P41      |              |                 |                          | AN001   |

| 140 | VREFL0               |          |              |                 |                          |         |

| 141 |                      | P40      |              |                 |                          | AN000   |

| 142 | VREFH0               |          |              |                 |                          |         |

| 143 | AVCC0                |          |              |                 |                          |         |

| 144 |                      | P07      |              |                 |                          | ADTRG0# |

Table 1.10

List of Pins and Pin Functions (144-Pin LQFP) (4 / 4)

Note: • Pin names to which -DS is appended are for pins that can be used to trigger release from deep software standby mode.

Note: • Leave the NC pin open.

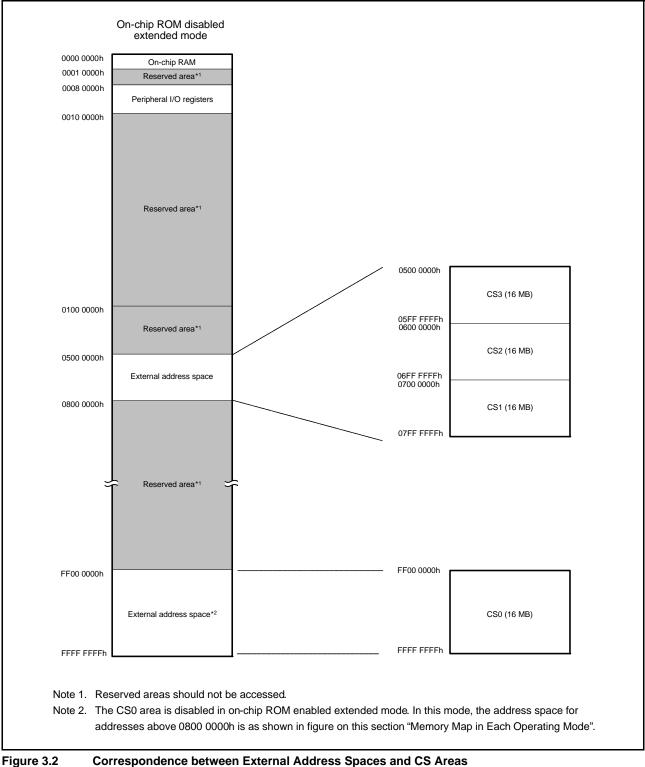

### 3.2 External Address Space

The external address space is divided into up to four CS areas (CS0 to CS3), each corresponding to the CSn# signal output from a CSn# (n = 0 to 3) pin.

Figure 3.2 shows the address ranges corresponding to the individual CS areas (CS0 to CS3) in on-chip ROM disabled extended mode.

(In On-Chip ROM Disabled Extended Mode)

#### Table 4.1 List of I/O Registers (Address Order) (2 / 29)

|            |                  |                                             |                    |                   |                | Number of Access Cyc       |

|------------|------------------|---------------------------------------------|--------------------|-------------------|----------------|----------------------------|

| Address    | Module<br>Symbol | Register Name                               | Register<br>Symbol | Number<br>of Bits | Access<br>Size | ICLK ≥ ICLK <<br>PCLK PCLK |

| 0008 201Dh | DMAC0            | DMA software start register                 | DMREQ              | 8                 | 8              | 2 ICLK                     |

| 0008 201Eh | DMAC0            | DMA status register                         | DMSTS              | 8                 | 8              | 2 ICLK                     |

| 008 201Fh  | DMAC0            | DMA activation source flag control register | DMCSL              | 8                 | 8              | 2 ICLK                     |

| 008 2040h  | DMAC1            | DMA source address register                 | DMSAR              | 32                | 32             | 2 ICLK                     |

| 008 2044h  | DMAC1            | DMA destination address register            | DMDAR              | 32                | 32             | 2 ICLK                     |

| 008 2048h  | DMAC1            | DMA transfer count register                 | DMCRA              | 32                | 32             | 2 ICLK                     |

| 008 204Ch  | DMAC1            | DMA block transfer count register           | DMCRB              | 16                | 16             | 2 ICLK                     |

| 008 2050h  | DMAC1            | DMA transfer mode register                  | DMTMD              | 16                | 16             | 2 ICLK                     |

| 008 2053h  | DMAC1            | DMA interrupt setting register              | DMINT              | 8                 | 8              | 2 ICLK                     |

| 008 2054h  | DMAC1            | DMA address mode register                   | DMAMD              | 16                | 16             | 2 ICLK                     |

| 008 205Ch  | DMAC1            | DMA transfer enable register                | DMCNT              | 8                 | 8              | 2 ICLK                     |

| 008 205Dh  | DMAC1            | DMA software start register                 | DMREQ              | 8                 | 8              | 2 ICLK                     |

| 008 205Eh  | DMAC1            | DMA status register                         | DMSTS              | 8                 | 8              | 2 ICLK                     |

| 008 205Fh  | DMAC1            | DMA activation source flag control register | DMCSL              | 8                 | 8              | 2 ICLK                     |

| 008 2080h  | DMAC2            | DMA source address register                 | DMSAR              | 32                | 32             | 2 ICLK                     |

| 008 2084h  | DMAC2            | DMA destination address register            | DMDAR              | 32                | 32             | 2 ICLK                     |

| 008 2088h  | DMAC2            | DMA transfer count register                 | DMCRA              | 32                | 32             | 2 ICLK                     |

| 008 208Ch  | DMAC2            | DMA block transfer count register           | DMCRB              | 16                | 16             | 2 ICLK                     |

| 008 2090h  | DMAC2            | DMA transfer mode register                  | DMTMD              | 16                | 16             | 2 ICLK                     |

| 008 2093h  | DMAC2            | DMA interrupt setting register              | DMINT              | 8                 | 8              | 2 ICLK                     |

| 008 2094h  | DMAC2            | DMA address mode register                   | DMAMD              | 16                | 16             | 2 ICLK                     |

| 008 209Ch  | DMAC2            | DMA transfer enable register                | DMCNT              | 8                 | 8              | 2 ICLK                     |

| 008 209Dh  | DMAC2            | DMA software start register                 | DMREQ              | 8                 | 8              | 2 IOLK                     |

| 008 209Eh  | DMAC2            |                                             | DMSTS              | 8                 | 8              | 2 IOLK                     |

|            |                  | DMA status register                         |                    | 8                 | 8              |                            |

| 008 209Fh  | DMAC2            | DMA activation source flag control register | DMCSL              |                   |                | 2 ICLK                     |

| 008 20C0h  | DMAC3            | DMA source address register                 | DMSAR              | 32                | 32             | 2 ICLK                     |

| 008 20C4h  | DMAC3            | DMA destination address register            | DMDAR              | 32                | 32             | 2 ICLK                     |

| 008 20C8h  | DMAC3            | DMA transfer count register                 | DMCRA              | 32                | 32             | 2 ICLK                     |

| 008 20CCh  | DMAC3            | DMA block transfer count register           | DMCRB              | 16                | 16             | 2 ICLK                     |

| 008 20D0h  | DMAC3            | DMA transfer mode register                  | DMTMD              | 16                | 16             | 2 ICLK                     |

| 008 20D3h  | DMAC3            | DMA interrupt setting register              | DMINT              | 8                 | 8              | 2 ICLK                     |

| 008 20D4h  | DMAC3            | DMA address mode register                   | DMAMD              | 16                | 16             | 2 ICLK                     |

| 008 20DCh  | DMAC3            | DMA transfer enable register                | DMCNT              | 8                 | 8              | 2 ICLK                     |

| 008 20DDh  | DMAC3            | DMA software start register                 | DMREQ              | 8                 | 8              | 2 ICLK                     |

| 008 20DEh  | DMAC3            | DMA status register                         | DMSTS              | 8                 | 8              | 2 ICLK                     |

| 008 20DFh  | DMAC3            | DMA activation source flag control register | DMCSL              | 8                 | 8              | 2 ICLK                     |

| 008 2200h  | DMAC             | DMA module activation register              | DMAST              | 8                 | 8              | 2 ICLK                     |

| 008 2400h  | DTC              | DTC control register                        | DTCCR              | 8                 | 8              | 2 ICLK                     |

| 008 2404h  | DTC              | DTC vector base register                    | DTCVBR             | 32                | 32             | 2 ICLK                     |

| 008 2408h  | DTC              | DTC address mode register                   | DTCADMOD           | 8                 | 8              | 2 ICLK                     |

| 008 240Ch  | DTC              | DTC module start register                   | DTCST              | 8                 | 8              | 2 ICLK                     |

| 008 240Eh  | DTC              | DTC status register                         | DTCSTS             | 16                | 16             | 2 ICLK                     |

| 008 3002h  | BSC              | CS0 mode register                           | CS0MOD             | 16                | 16             | 1, 2 BCLK                  |

| 008 3004h  | BSC              | CS0 wait control register 1                 | CS0WCR1            | 32                | 32             | 1, 2 BCLK                  |

| 008 3008h  | BSC              | CS0 wait control register 2                 | CS0WCR2            | 32                | 32             | 1, 2 BCLK                  |

| 008 3012h  | BSC              | CS1 mode register                           | CS1MOD             | 16                | 16             | 1, 2 BCLK                  |

| 008 3014h  | BSC              | CS1 wait control register 1                 | CS1WCR1            | 32                | 32             | 1, 2 BCLK                  |

| 008 3018h  | BSC              | CS1 wait control register 2                 | CS1WCR2            | 32                | 32             | 1, 2 BCLK                  |

| 008 3022h  | BSC              | CS2 mode register                           | CS2MOD             | 16                | 16             | 1, 2 BCLK                  |

| 008 3024h  | BSC              | CS2 wait control register 1                 | CS2WCR1            | 32                | 32             | 1, 2 BCLK                  |

| 008 3028h  | BSC              | CS2 wait control register 2                 | CS2WCR2            | 32                | 32             | 1, 2 BCLK                  |

#### Table 4.1 List of I/O Registers (Address Order) (5 / 29)

|           |                  |                                |                    |                   |                | Number of Access Cycle     |  |  |

|-----------|------------------|--------------------------------|--------------------|-------------------|----------------|----------------------------|--|--|

| Address   | Module<br>Symbol | Register Name                  | Register<br>Symbol | Number<br>of Bits | Access<br>Size | ICLK ≥ ICLK <<br>PCLK PCLK |  |  |

| 008 70ABh | ICU              | Interrupt request register 171 | IR171              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70AEh | ICU              | Interrupt request register 174 | IR174              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70AFh | ICU              | Interrupt request register 175 | IR175              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B0h | ICU              | Interrupt request register 176 | IR176              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B1h | ICU              | Interrupt request register 177 | IR177              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B2h | ICU              | Interrupt request register 178 | IR178              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B3h | ICU              | Interrupt request register 179 | IR179              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B4h | ICU              | Interrupt request register 180 | IR180              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B5h | ICU              | Interrupt request register 181 | IR181              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B6h | ICU              | Interrupt request register 182 | IR182              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B7h | ICU              | Interrupt request register 183 | IR183              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B8h | ICU              | Interrupt request register 184 | IR184              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70B9h | ICU              | Interrupt request register 185 | IR185              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70BAh | ICU              | Interrupt request register 186 | IR186              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70BBh | ICU              | Interrupt request register 187 | IR187              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70BCh | ICU              | Interrupt request register 188 | IR188              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70BDh | ICU              | Interrupt request register 189 | IR189              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70BEh | ICU              | Interrupt request register 190 | IR190              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70BFh | ICU              | Interrupt request register 191 | IR191              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C0h | ICU              | Interrupt request register 192 | IR192              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C1h | ICU              | Interrupt request register 193 | IR193              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C2h | ICU              | Interrupt request register 194 | IR194              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C3h | ICU              | Interrupt request register 195 | IR195              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C4h | ICU              | Interrupt request register 196 | IR196              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C5h | ICU              | Interrupt request register 197 | IR197              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C6h | ICU              | Interrupt request register 197 | IR198              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C7h | ICU              | Interrupt request register 199 | IR199              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C8h | ICU              | Interrupt request register 200 | IR200              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C9h | ICU              | Interrupt request register 200 | IR201              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70C5h | ICU              |                                | IR206              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70CEn | ICU              | Interrupt request register 206 | IR200              |                   |                | 2 ICLK                     |  |  |

|           |                  | Interrupt request register 207 |                    | 8                 | 8              |                            |  |  |

| 008 70D0h |                  | Interrupt request register 208 | IR208<br>IR209     | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D1h | ICU              | Interrupt request register 209 |                    | -                 | -              |                            |  |  |

| 008 70D2h | ICU              | Interrupt request register 210 | IR210              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D3h | ICU              | Interrupt request register 211 | IR211              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D4h | ICU              | Interrupt request register 212 | IR212              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D5h | ICU              | Interrupt request register 213 | IR213              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D6h | ICU              | Interrupt request register 214 | IR214              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D7h | ICU              | Interrupt request register 215 | IR215              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D8h | ICU              | Interrupt request register 216 | IR216              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70D9h | ICU              | Interrupt request register 217 | IR217              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70DAh | ICU              | Interrupt request register 218 | IR218              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70DBh | ICU              | Interrupt request register 219 | IR219              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70DCh | ICU              | Interrupt request register 220 | IR220              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70DDh | ICU              | Interrupt request register 221 | IR221              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70DEh | ICU              | Interrupt request register 222 | IR222              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70DFh | ICU              | Interrupt request register 223 | IR223              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70E0h | ICU              | Interrupt request register 224 | IR224              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70E1h | ICU              | Interrupt request register 225 | IR225              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70E2h | ICU              | Interrupt request register 226 | IR226              | 8                 | 8              | 2 ICLK                     |  |  |

| 008 70E3h | ICU              | Interrupt request register 227 | IR227              | 8                 | 8              | 2 ICLK                     |  |  |

#### [Chip version A]

#### Table 5.7DC Characteristics (6)

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V, T<sub>a</sub> = -40 to +105°C

|           |                              | Item                  |                                                       |                 | Symbol          | Тур.  | Max.             | Unit | Test<br>Conditions |

|-----------|------------------------------|-----------------------|-------------------------------------------------------|-----------------|-----------------|-------|------------------|------|--------------------|

| Supply    | Middle-speed                 | Normal                | No peripheral                                         | ICLK = 32 MHz*2 | I <sub>CC</sub> | 7.0   | —                | mA   |                    |

| current*1 | operating modes<br>1A and 1B | operating mode        | operation                                             | ICLK = 20 MHz*3 |                 | 6.0   | —                |      |                    |

|           |                              |                       | All peripheral                                        | ICLK = 32 MHz*4 |                 | 26    | _                |      |                    |

|           |                              |                       | operation:<br>Normal                                  | ICLK = 20 MHz*5 |                 | 18.5  | —                |      |                    |

|           |                              |                       | All peripheral                                        | ICLK = 32 MHz*4 |                 |       | 40               |      |                    |

|           |                              |                       | operation: Max.                                       | ICLK = 20 MHz*5 |                 |       | 30               |      |                    |

|           |                              | Sleep mode            | No peripheral                                         | ICLK = 32 MHz   |                 | 5.0   | —                |      |                    |

|           |                              |                       | operation                                             | ICLK = 20 MHz   |                 | 4.6   | —                | 1    |                    |

|           |                              |                       | All peripheral                                        | ICLK = 32 MHz   |                 | 15.5  | —                |      |                    |

|           |                              |                       | operation:<br>Normal                                  | ICLK = 20 MHz   |                 | 12    |                  |      |                    |

|           |                              | All-module clock      | stop mode                                             | ICLK = 32 MHz   |                 | 4.5   | —                |      |                    |

|           |                              | Increase during       |                                                       | ICLK = 20 MHz   |                 | 4.3   | —                |      |                    |

|           |                              |                       | Middle-speed ope                                      | rating mode 1A  |                 | 25    | —                |      |                    |

|           |                              | BGO operation*6       | Middle-speed operating mode 1B                        |                 |                 | 20    | _                |      |                    |

|           | Low-speed operating mode     | Normal operating mode | No peripheral operation*7                             | ICLK = 1 MHz    |                 | 0.68  | —                |      |                    |

|           | 1<br>Sleep mode              |                       | All peripheral operation: Normal*8                    | ICLK = 1 MHz    |                 | 2.4   | _                |      |                    |

|           |                              |                       | All peripheral operation: Max.*8                      | ICLK = 1 MHz    |                 |       | 7                |      |                    |

|           |                              | Sleep mode            | No peripheral operation                               | ICLK = 1 MHz    |                 | 0.6   | —                |      |                    |

|           |                              |                       | All peripheral<br>operation:<br>Normal                | ICLK = 1 MHz    |                 | 2     |                  |      |                    |

|           |                              | All-module clock      | stop mode                                             | I               |                 | 0.58  | _                |      |                    |

|           | Low-speed operating mode     | Normal operating mode | No peripheral operation*9                             | ICLK = 32 kHz   |                 | 0.024 | -                |      |                    |

|           | 2                            |                       | All peripheral<br>operation:<br>Normal* <sup>10</sup> | ICLK = 32 kHz   |                 | 0.05  |                  | -    |                    |

|           |                              |                       | All peripheral operation: Max.* <sup>10</sup>         | ICLK = 32 kHz   |                 | —     | 3* <sup>11</sup> |      |                    |

|           |                              | Sleep mode            | No peripheral operation                               | ICLK = 32 kHz   |                 | 0.02  | -                |      |                    |

|           |                              |                       | All peripheral operation: Normal                      | ICLK = 32 kHz   |                 | 0.04  | _                |      |                    |

|           |                              | All-module clock      | stop mode                                             | 1               |                 | 0.018 | —                |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 64 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

Note 3. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 40 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

Note 4. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 64 MHz. BCLK, FCLK, and PCLK are ICLK divided by 1.

RENESAS

- Note 5. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 40 MHz. BCLK, FCLK, and PCLK are ICLK divided by 1.

- Note 6. This is the increase if data is programmed to or erasing from the ROM or E2 DataFlash during program execution.

- Note 7. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 32 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

- Note 8. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 32 MHz. BCLK, FCLK, and PCLK are ICLK divided by 1.

- Note 9. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is the sub oscillation circuit. BCLK, FCLK, and PCLK are set to divided by 64.

- Note 10. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is the sub oscillation circuit. BCLK, FCLK, and PCLK are ICLK divided by 1.

- Note 11. Value when the main clock continues oscillating at 12.5 MHz.

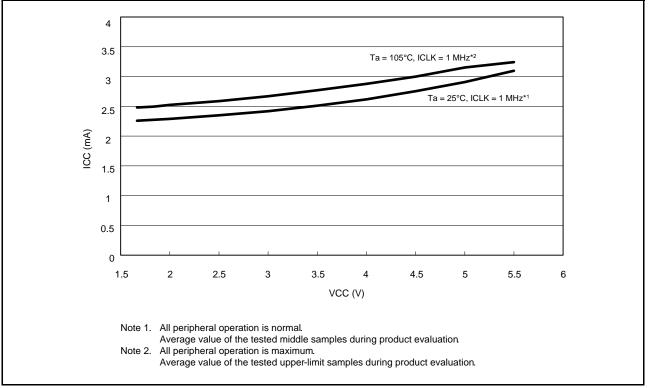

Figure 5.3 Voltage Dependency in Low-Speed Operating Mode 1 (Reference Data) for Chip Version A

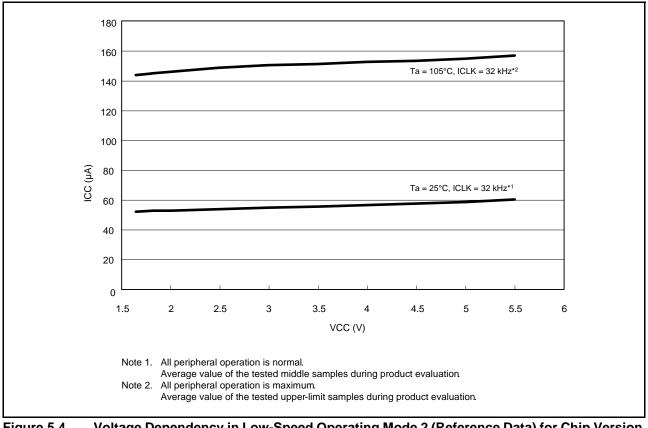

Figure 5.4 Voltage Dependency in Low-Speed Operating Mode 2 (Reference Data) for Chip Version A

## [Chip version B with 768 Kbytes/1 Mbyte of flash memory and 100 to 145 pins]

## Table 5.15DC Characteristics (14)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|                  |                            | Item                  |                                                    |               | Symbol          | Тур. | Max. | Unit | Test<br>Conditions |

|------------------|----------------------------|-----------------------|----------------------------------------------------|---------------|-----------------|------|------|------|--------------------|

| Supply current*1 | High-speed operating mode  | Normal operating mode | No peripheral operation*2                          | ICLK = 50 MHz | I <sub>CC</sub> | 7.8  | _    | mA   |                    |

|                  |                            |                       | All peripheral operation: Normal* <sup>3</sup>     | ICLK = 50 MHz |                 | 29.8 | —    |      |                    |

|                  |                            |                       | All peripheral<br>operation:<br>Max.* <sup>3</sup> | ICLK = 50 MHz |                 | _    | 45   |      |                    |

|                  |                            | Sleep mode            | No peripheral operation                            | ICLK = 50 MHz |                 | 4.3  | —    |      |                    |

|                  |                            |                       | All peripheral operation: Normal                   | ICLK = 50 MHz |                 | 13.5 | —    |      |                    |

|                  | All-module clock stop mode |                       | top mode                                           |               |                 | 3.7  | —    |      |                    |

|                  |                            | Increase during BC    | GO operation*4                                     |               |                 | 23   | _    |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

Note 3. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 100 MHz. BCLK, FCLK, and PCLK are ICLK divided by 2.

Note 4. This is the increase if data is programmed to or erasing from the ROM or E2 DataFlash during program execution.

|           |                          | Item                  |                                                       |               | Symbol          | Тур.       | Max. | Unit | Test<br>Conditions |

|-----------|--------------------------|-----------------------|-------------------------------------------------------|---------------|-----------------|------------|------|------|--------------------|

| Supply    | Low-speed                | Normal                | No peripheral                                         | ICLK = 8 MHz  | I <sub>CC</sub> | 2.1        | _    | mA   |                    |

| current*1 | operating mode           | operating mode        | operation*7                                           | ICLK = 4 MHz  |                 | 1.7        | _    |      |                    |

|           |                          |                       |                                                       | ICLK = 2 MHz  |                 | 1.5        | _    |      |                    |

|           |                          |                       | All peripheral                                        | ICLK = 8 MHz  |                 | 7.3        |      |      |                    |

|           |                          |                       | operation:<br>Normal* <sup>8</sup>                    | ICLK = 4 MHz  |                 | 4.5        |      |      |                    |

|           |                          |                       |                                                       | ICLK = 2 MHz  |                 | 3.1        |      | -    |                    |

|           |                          |                       | All peripheral                                        | ICLK = 8 MHz  |                 |            | 12   |      |                    |

|           |                          |                       | operation: Max.*7                                     | ICLK = 4 MHz  |                 |            |      |      |                    |

|           |                          | Sleep mode            |                                                       | ICLK = 2 MHz  |                 |            |      |      |                    |

|           |                          |                       | No peripheral                                         | ICLK = 8 MHz  |                 | 1.5        | —    |      |                    |

|           |                          |                       | operation                                             | ICLK = 4 MHz  |                 | 1.4        |      | ļ    |                    |

|           |                          |                       |                                                       | ICLK = 2 MHz  |                 | 1.3        |      |      |                    |

|           |                          |                       | All peripheral                                        | ICLK = 8 MHz  | 4.1             | _          |      |      |                    |

|           |                          |                       | operation:<br>Normal                                  | ICLK = 4 MHz  |                 | 3.0<br>2.3 | _    | -    |                    |

|           |                          |                       |                                                       | ICLK = 2 MHz  |                 |            | —    |      |                    |

|           |                          | All-module clock      | stop mode                                             | ICLK = 8 MHz  | 1.4             | 1.4        | —    |      |                    |

|           |                          |                       |                                                       | ICLK = 4 MHz  |                 | 1.3        | —    |      |                    |

|           |                          |                       |                                                       | ICLK = 2 MHz  |                 | 1.2        | _    |      |                    |

|           | Low-speed operating mode | Normal operating mode | No peripheral operation*9                             | ICLK = 32 kHz |                 | 0.022      | 2 _  |      |                    |

|           | 2                        |                       | All peripheral<br>operation:<br>Normal* <sup>10</sup> | ICLK = 32 kHz |                 | 0.06       | _    | -    |                    |

|           |                          |                       | All peripheral<br>operation:<br>Max.* <sup>10</sup>   | ICLK = 32 kHz |                 |            | 3*11 |      |                    |

|           |                          | Sleep mode            | No peripheral operation                               | ICLK = 32 kHz |                 | 0.017      |      |      |                    |

|           |                          |                       | All peripheral<br>operation:<br>Normal                | ICLK = 32 kHz |                 | 0.036      |      |      |                    |

|           |                          | All-module clock      | stop mode                                             |               |                 | 0.017      | _    |      |                    |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 64 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

- Note 3. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 40 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

- Note 4. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is PLL and the VCO oscillation frequency is 64 MHz. BCLK, FCLK, and PCLK are ICLK divided by 1.

- Note 5. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 40 MHz. BCLK, FCLK, and PCLK are ICLK divided by 1.

Note 6. This is the increase if data is programmed to or erasing from the ROM or E2 DataFlash during program execution.

Note 7. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 32 MHz. BCLK, FCLK, and PCLK are set to divided by 64.

Note 8. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is HOCO and the oscillation frequency is 32 MHz. BCLK, FCLK, and PCLK are ICLK divided by 1.

Note 9. Clock supply to the peripheral functions is stopped. This does not include BGO operation. The clock source is the sub oscillation circuit. BCLK, FCLK, and PCLK are set to divided by 64.

Note 10. Clocks are supplied to the peripheral functions. This does not include BGO operation. The clock source is the sub oscillation circuit. BCLK, FCLK, and PCLK are ICLK divided by 1.

Note 11. Value when the main clock continues oscillating at 12.5 MHz.

Figure 5.28 Voltage Dependency in Middle-Speed Operating Modes 2A and 2B (Reference Data) for Chip Version B with 768 Kbytes/1 Mbyte of Flash Memory and 100 to 145 Pins

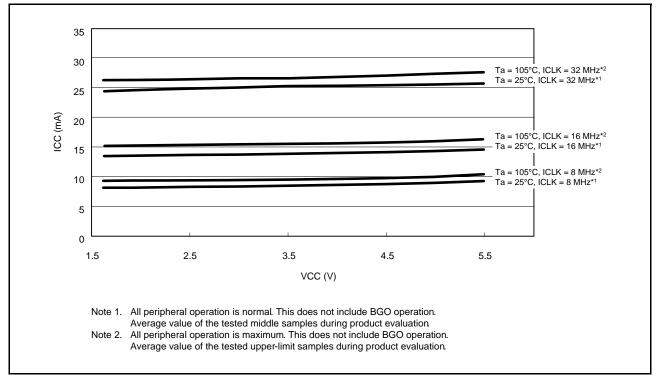

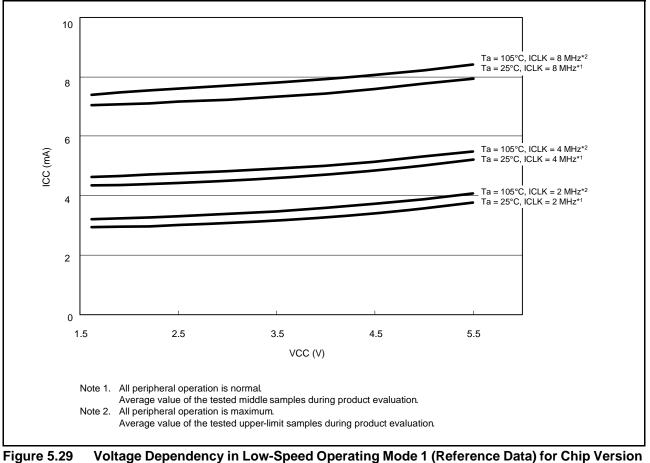

Figure 5.29 Voltage Dependency in Low-Speed Operating Mode 1 (Reference Data) for Chip Version B with 768 Kbytes/1 Mbyte of Flash Memory and 100 to 145 Pins

RENESAS

## [Chip versions B and C]

Table 5.31

Output Values of Voltage (4)

Conditions: VCC = AVCC0 = 2.7 to 4.0 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|                   | Item                               |                        |                 |           | Max. | Unit                     | Test Conditions           |

|-------------------|------------------------------------|------------------------|-----------------|-----------|------|--------------------------|---------------------------|

| Output low        | All output pins Normal output mode |                        | V <sub>OL</sub> | —         | 0.5  | V                        | I <sub>OL</sub> = 1.0 mA  |

| (other than RIIC) |                                    | High-drive output mode |                 | —         | 0.5  |                          | I <sub>OL</sub> = 2.0 mA  |

|                   | RIIC pins                          |                        | _               | 0.4       |      | I <sub>OL</sub> = 3.0 mA |                           |

|                   |                                    |                        |                 | _         | 0.6  | 1                        | I <sub>OL</sub> = 6.0 mA  |

| Output high       | All output pins                    | Normal output mode     | V <sub>OH</sub> | VCC - 0.5 | _    | V                        | I <sub>OH</sub> = -1.0 mA |

|                   |                                    | High-drive output mode |                 | VCC - 0.5 | —    |                          | I <sub>OH</sub> = -2.0 mA |

#### [Chip versions B and C]

#### Table 5.32Output Values of Voltage (5)

Conditions: VCC = AVCC0 = 4.0 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|             | Item                                                                                         | Symbol                 | Min.            | Max.      | Unit | Test Conditions |                           |

|-------------|----------------------------------------------------------------------------------------------|------------------------|-----------------|-----------|------|-----------------|---------------------------|

| Output low  | Output low All output pins<br>(other than RIIC) Normal output mode<br>High-drive output mode |                        | V <sub>OL</sub> | _         | 0.8  | V               | I <sub>OL</sub> = 2.0 mA  |

|             |                                                                                              |                        |                 | -         | 0.8  |                 | I <sub>OL</sub> = 4.0 mA  |

| RIIC pins   |                                                                                              |                        | 1               | _         | 0.4  |                 | I <sub>OL</sub> = 3.0 mA  |

|             |                                                                                              |                        |                 | _         | 0.6  |                 | I <sub>OL</sub> = 6.0 mA  |

| Output high | All output pins                                                                              | Normal output mode     | V <sub>OH</sub> | VCC - 0.8 | _    | V               | I <sub>OH</sub> = -2.0 mA |

|             |                                                                                              | High-drive output mode | -               | VCC - 0.8 |      |                 | I <sub>OH</sub> = -4.0 mA |

## 5.2.1 Standard I/O Pin Output Characteristics (1)

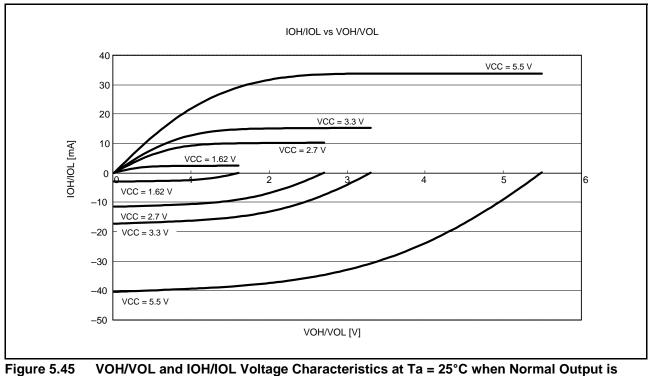

Figure 5.45 to Figure 5.49 show the characteristics when normal output is selected by the drive capacity control register.

Selected (Reference Data)

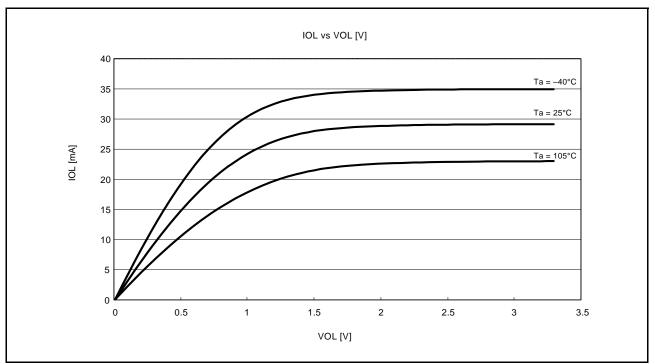

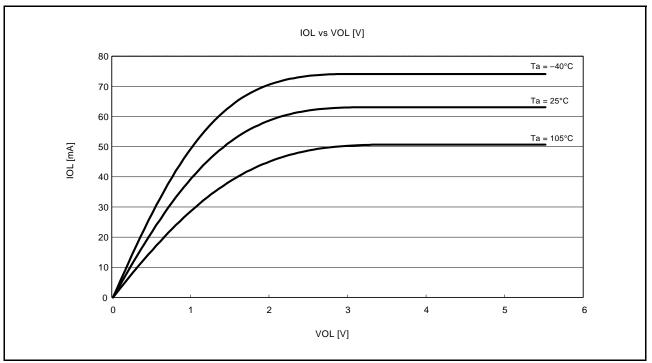

Figure 5.57 VOL and IOL Temperature Characteristics of RIIC Output Pin at VCC = 3.3 V (Reference Data)

Figure 5.58 VOL and IOL Temperature Characteristics of RIIC Output Pin at VCC = 5.5 V (Reference Data)

|    |                                  |        |                                                             | Symbol                           | Min.                         | Max.                                              | Unit*1             | Test Condition                |  |

|----|----------------------------------|--------|-------------------------------------------------------------|----------------------------------|------------------------------|---------------------------------------------------|--------------------|-------------------------------|--|

| יו | Data input setup time            | Master | 2.7 V ≤ VCC ≤ 5.5 V                                         | t <sub>SU</sub>                  | 10                           | _                                                 | ns                 | C = 30pF                      |  |

|    |                                  |        | 1.8 V ≤ VCC < 2.7 V                                         |                                  | 25                           | —                                                 |                    | Figure 5.92 to<br>Figure 5.97 |  |

|    |                                  |        | 1.62 V ≤ VCC < 1.8 V                                        |                                  | 30                           | —                                                 |                    | ge.e.e.                       |  |

|    |                                  | Slave  |                                                             |                                  | 25 – t <sub>Pcyc</sub>       | —                                                 |                    |                               |  |

|    | Data input hold time             | Master | PCLKB set to a<br>division ratio other<br>than divided by 2 | t <sub>H</sub>                   | t <sub>Pcyc</sub>            | —                                                 | ns                 |                               |  |

|    |                                  |        | PCLKB set to divided by 2*2                                 | t <sub>HF</sub>                  | 0                            | _                                                 |                    |                               |  |

|    |                                  | Slave  |                                                             | t <sub>H</sub>                   | 20 + 2 × t <sub>Pcyc</sub>   | —                                                 |                    |                               |  |

|    | SSL setup time                   | Master |                                                             | t <sub>LEAD</sub>                | 1                            | 8                                                 | t <sub>SPcyc</sub> |                               |  |

|    |                                  | Slave  |                                                             |                                  | 4                            | —                                                 | t <sub>Pcyc</sub>  |                               |  |

| ĺ  | SSL hold time                    | Master |                                                             | t <sub>LAG</sub>                 | 1                            | 8                                                 | t <sub>SPcyc</sub> |                               |  |

|    |                                  | Slave  |                                                             |                                  | 4                            | —                                                 | t <sub>Pcyc</sub>  |                               |  |

| ĺ  | Data output delay                | Master | 2.7 V ≤ VCC ≤ 5.5 V                                         | t <sub>OD</sub>                  | _                            | 14                                                | ns                 |                               |  |

|    | time -                           |        | 1.8 V ≤ VCC < 2.7 V                                         |                                  | _                            | 20                                                |                    |                               |  |

|    |                                  |        | 1.62 V ≤ VCC < 1.8 V                                        |                                  | _                            | 25                                                | l                  | 1                             |  |

|    |                                  | Slave  | 2.7 V ≤ VCC ≤ 5.5 V                                         |                                  | _                            | 3 × t <sub>Pcyc</sub> + 65                        |                    |                               |  |

|    |                                  |        | 1.8 V ≤ VCC < 2.7 V                                         |                                  | _                            | 3 × tPcyc +85                                     |                    |                               |  |

|    |                                  |        | 1.62 V ≤ VCC < 1.8 V                                        |                                  | _                            | 3 × tPcyc +95                                     |                    |                               |  |

| ĺ  | Data output hold time            | Master |                                                             | t <sub>OH</sub>                  | 0                            | —                                                 | ns                 |                               |  |

|    |                                  | Slave  |                                                             |                                  | 0                            | —                                                 |                    |                               |  |

|    | Successive<br>transmission delay | Master |                                                             | t <sub>TD</sub>                  | $t_{SPcyc}$ + 2 × $t_{Pcyc}$ | 8 × t <sub>SPcyc</sub> + 2<br>× t <sub>Pcyc</sub> | ns                 |                               |  |

|    | time                             | Slave  |                                                             |                                  | 4 × t <sub>Pcyc</sub>        |                                                   |                    |                               |  |

|    | MOSI and MISO rise/              | Output | 2.7 V ≤ VCC ≤ 5.5 V                                         | t <sub>Dr,</sub> t <sub>Df</sub> | _                            | 10                                                | ns                 |                               |  |

|    | fall time                        |        | 1.8 V ≤ VCC < 2.7 V                                         |                                  | _                            | 15                                                |                    |                               |  |

|    |                                  |        | 1.62 V ≤ VCC < 1.8 V                                        |                                  | _                            | 20                                                |                    |                               |  |

|    |                                  | Input  |                                                             |                                  | —                            | 1                                                 | μs                 |                               |  |

|    | SSL rise/fall time               | Output | 2.7 V ≤ VCC ≤ 5.5 V                                         | t <sub>SSLr,</sub>               | _                            | 10                                                | ns                 |                               |  |

|    |                                  |        | 1.8 V ≤ VCC < 2.7 V                                         | t <sub>SSLf</sub>                | —                            | 15                                                |                    |                               |  |

|    |                                  |        | 1.62 V ≤ VCC < 1.8 V                                        |                                  | _                            | 20                                                |                    |                               |  |

|    |                                  | Input  |                                                             |                                  | _                            | 1                                                 | μs                 |                               |  |

|    | Slave access time                |        | 2.7 V ≤ VCC ≤ 5.5 V                                         | t <sub>SA</sub>                  | _                            | 6                                                 | t <sub>Pcyc</sub>  | C = 30pF                      |  |

|    |                                  |        | 1.8 V ≤ VCC < 2.7 V                                         |                                  | _                            | 7                                                 |                    | Figure 5.96 ar<br>Figure 5.97 |  |

|    |                                  |        | 1.62 V ≤ VCC < 1.8 V                                        |                                  | _                            | 7                                                 |                    |                               |  |

|    | Slave output release ti          | me     | 2.7 V ≤ VCC ≤ 5.5 V                                         | t <sub>REL</sub>                 | _                            | 5                                                 | t <sub>Pcyc</sub>  |                               |  |

|    |                                  |        | 1.8 V ≤ VCC < 2.7 V                                         |                                  | _                            | 6                                                 |                    |                               |  |

|    |                                  |        | 1.62 V ≤ VCC < 1.8 V                                        |                                  | _                            | 6                                                 |                    |                               |  |

Note 1. t<sub>Pcyc</sub>: PCLK cycle Note 2. Divided by 2 can be set only in packages with 768 Kbytes/1 Mbyte of flash memory or 144/145 pins.

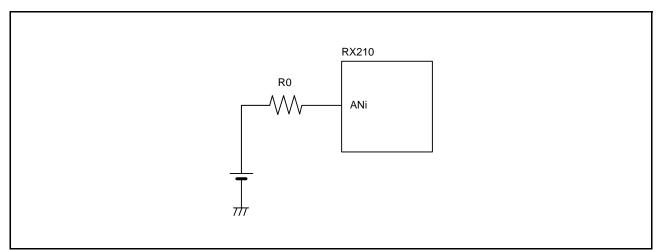

### Table 5.66 Sampling Time

Conditions: VCC = AVCC0 = 1.62 to 5.5 V, VSS = AVSS0 = VREFL = VREFL0 = 0 V,  $T_a = -40$  to +105°C

|               | Item                               | Symbol | Тур.                  | Unit | Test Conditions |

|---------------|------------------------------------|--------|-----------------------|------|-----------------|

| Sampling time | mpling time High-precision channel |        | 0.2 + 0.14 × R0 (KΩ)  | μs   | Figure 5.100    |

|               | Normal-precision channel           |        | 0.35 + 0.14 × R0 (KΩ) |      |                 |

Figure 5.100 Internal Equivalent Circuit of Analog Input Pin

#### [Chip version B]

# Table 5.79 ROM (Flash Memory for Code Storage) Characteristics (6) : middle-speed operating modes 1B and 2B

Conditions: VCC = AVCC0 = 1.62 to 3.6 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation:  $T_a = -40$  to +105°C

| Item                                                                         |           | Symbol             | FCLK = 4 MHz                                     |      |       |                                                  | Unit |                                                                                                           |      |

|------------------------------------------------------------------------------|-----------|--------------------|--------------------------------------------------|------|-------|--------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------|------|

|                                                                              |           | Symbol             | Min.                                             | Тур. | Max.  | Min.                                             | Тур. | Max.                                                                                                      | Unit |

| Programming time                                                             | 2 bytes   | t <sub>P2</sub>    | —                                                | 0.25 | 5.0   | —                                                | 0.21 | 2.8                                                                                                       | ms   |

| when N <sub>PEC</sub> ≤ 100 times                                            | 8 bytes   | t <sub>P8</sub>    | _                                                | 0.25 | 5.3   | —                                                | 0.21 | 3.0                                                                                                       |      |

|                                                                              | 128 bytes | t <sub>P128</sub>  | _                                                | 0.92 | 14.0  | —                                                | 0.65 | 8.3                                                                                                       |      |

| Programming time<br>when N <sub>PEC</sub> > 100 times                        | 2 bytes   | t <sub>P2</sub>    | —                                                | 0.31 | 6.2   | —                                                | 0.26 | 3.5                                                                                                       | ms   |

|                                                                              | 8 bytes   | t <sub>P8</sub>    | —                                                | 0.31 | 6.6   | —                                                | 0.26 | 3.7                                                                                                       |      |

|                                                                              | 128 bytes | t <sub>P128</sub>  | _                                                | 1.09 | 17.5  | —                                                | 0.77 | 10.0                                                                                                      |      |

| Erasure time<br>when N <sub>PEC</sub> ≤ 100 times                            | 2 Kbytes  | t <sub>E2K</sub>   | —                                                | 21.0 | 113.7 | —                                                | 18.5 | 46                                                                                                        | ms   |

| Erasure time<br>when N <sub>PEC</sub> > 100 times                            | 2 Kbytes  | t <sub>E2K</sub>   | _                                                | 25.6 | 220.6 | —                                                | 22.5 | 90 (1000 times ≥<br>N <sub>PEC</sub> > 100 times),<br>98 (10000 times ≥<br>N <sub>PEC</sub> > 1000 times) | ms   |

| Suspend delay time during programming (in programming/erasure priority mode) |           | t <sub>SPD</sub>   | —                                                |      | 1.7   | —                                                |      | 1.6                                                                                                       | ms   |

| First suspend delay time during programming (in suspend priority mode)       |           | t <sub>SPSD1</sub> | —                                                | _    | 220   | —                                                | _    | 120                                                                                                       | μs   |

| Second suspend delay time during programming (in suspend priority mode)      |           | t <sub>SPSD2</sub> | —                                                | _    | 1.7   | —                                                |      | 1.6                                                                                                       | ms   |

| Suspend delay time during erasing (in programming/erasure priority mode)     |           | t <sub>SED</sub>   | —                                                | _    | 1.7   | —                                                |      | 1.6                                                                                                       | ms   |

| First suspend delay time during erasing (in suspend priority mode)           |           | t <sub>SESD1</sub> | —                                                |      | 220   | _                                                |      | 120                                                                                                       | μs   |

| Second suspend delay time during erasing (in suspend priority mode)          |           | t <sub>SESD2</sub> | —                                                | _    | 1.7   | —                                                |      | 1.6                                                                                                       | ms   |

| FCU reset time                                                               |           | t <sub>FCUR</sub>  | 20 µs or<br>longer and<br>FCLK × 6<br>or greater | _    | —     | 20 µs or<br>longer and<br>FCLK × 6<br>or greater | _    | _                                                                                                         | μs   |

Note 1. The operating frequency is 20 MHz (max.) when the voltage is in the range from 1.62 V to less than 1.8 V.

### [Chip version B]

#### Table 5.84

# E2 DataFlash Characteristics (5) : high-speed operating mode, middle-speed operating modes 1A and 2A

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH = VREFH0 = AVCC0, VSS = AVSS0 = VREFL = VREFL0 = 0 V Temperature range for the programming/erasure operation:  $T_a = -40$  to +105°C

| Item                                                                    |                                                               | FCLK = 4 MHz        |      |      |      | FCLK = 32 MHz |      |      | Linit |

|-------------------------------------------------------------------------|---------------------------------------------------------------|---------------------|------|------|------|---------------|------|------|-------|

|                                                                         |                                                               | Symbol              | Min. | Тур. | Max. | Min.          | Тур. | Max. | Unit  |

| Programming time                                                        | 2 bytes                                                       | t <sub>DP2</sub>    | _    | 0.19 | 4.4  | —             | 0.13 | 2.0  | ms    |

| when $N_{DPEC} \le 100$ times                                           | 8 bytes                                                       | t <sub>DP8</sub>    | _    | 0.24 | 5.1  | —             | 0.13 | 2.2  |       |

| Programming time                                                        | 2 bytes                                                       | t <sub>DP2</sub>    | _    | 0.25 | 6.4  | —             | 0.17 | 3.0  | ms    |

| when $N_{DPEC} > 100$ times                                             | 8 bytes                                                       | t <sub>DP8</sub>    | _    | 0.32 | 7.5  | —             | 0.18 | 3.2  |       |

| Erasure time<br>when N <sub>DPEC</sub> ≤ 100 times                      | 128 bytes                                                     | t <sub>DE128</sub>  | —    | 3.3  | 27.1 | —             | 2.5  | 8    | ms    |

| Erasure time<br>when N <sub>DPEC</sub> > 100 times                      | 128 bytes                                                     | t <sub>DE128</sub>  | —    | 4.0  | 45.1 | —             | 3.0  | 12   | ms    |

| Blank check time                                                        | 2 bytes                                                       | t <sub>DBC2</sub>   | _    | —    | 98   | —             | —    | 35   | μs    |

|                                                                         | 2 Kbytes                                                      | t <sub>DBC2K</sub>  | _    | —    | 16   | —             | —    | 2.5  | ms    |

| Suspend delay time during programming/erasure prio                      | t <sub>DSPD</sub>                                             | _                   | _    | 0.9  | —    | _             | 0.8  | ms   |       |

| First suspend delay time during programming (in suspend priority mode)  |                                                               | t <sub>DSPSD1</sub> | _    | -    | 220  | —             | —    | 120  | μs    |

| Second suspend delay time during programming (in suspend priority mode) |                                                               | t <sub>DSPSD2</sub> | —    | _    | 0.9  | —             | —    | 0.8  | ms    |

| Suspend delay time during en<br>(in programming/erasure prio            | t <sub>DSED</sub>                                             | _                   | —    | 0.9  | _    | —             | 0.8  | ms   |       |

| First suspend delay time duri<br>(in suspend priority mode)             | t <sub>DSESD1</sub>                                           | _                   | _    | 220  | —    | -             | 120  | μs   |       |

| Second suspend delay time of (in suspend priority mode)                 | cond suspend delay time during erasing suspend priority mode) |                     |      | -    | 0.9  | —             | -    | 0.8  | ms    |

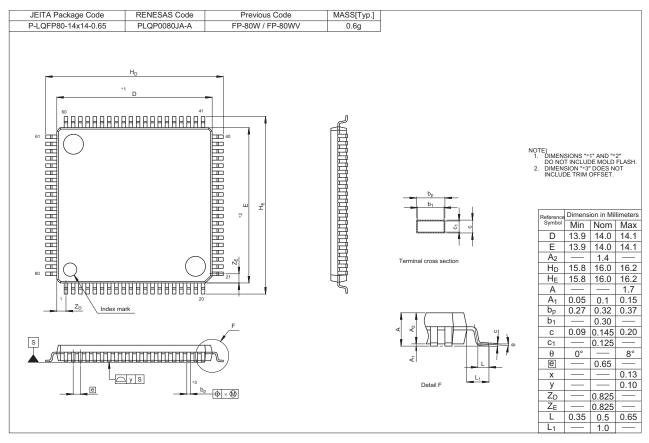

Figure I 80-Pin LQFP (PLQP0080JA-A)

**REVISION HISTORY**

## RX210 Group Datasheet

| Boy  | Data              | Description   |                                                                                                                                                                             |  |  |  |  |  |

|------|-------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Rev. | Date              | Page          | Summary                                                                                                                                                                     |  |  |  |  |  |

| 0.50 | Apr.15, 2011      | _             | First edition, issued                                                                                                                                                       |  |  |  |  |  |

| 0.90 | Aug.10, 2011      |               |                                                                                                                                                                             |  |  |  |  |  |

|      |                   | 4             | Table 1.1 Outline of Specifications: Power supply voltage/ Operating frequency, changed                                                                                     |  |  |  |  |  |

|      |                   | 17, 21, 24,   | Table 1.5 to Table 1.8 List of Pins and Pin Functions (Pin name: LVCMP2 $\rightarrow$ CMPA2), changed                                                                       |  |  |  |  |  |

|      |                   | 26<br>2. CPU  |                                                                                                                                                                             |  |  |  |  |  |

|      |                   | 2. CPU<br>51  | Table 2.14 Instructions that are Converted into Multiple Micro-Operations (multiplier: $32 \times 32 \rightarrow 64$                                                        |  |  |  |  |  |

|      |                   | 51            | bits), (memory source operand), added                                                                                                                                       |  |  |  |  |  |

|      |                   | 4. I/O Regis  |                                                                                                                                                                             |  |  |  |  |  |

|      |                   | 63            | Table 5.1 List of I/O Registers (Address Order), SOSCWTCR, LOCOWTCR2, HOCOWTCR2,                                                                                            |  |  |  |  |  |

|      |                   |               | added                                                                                                                                                                       |  |  |  |  |  |

|      |                   | 114 to 116    | Table 5.1 List of I/O Registers (Address Order): Interrupt source priority register, changed                                                                                |  |  |  |  |  |

|      |                   | 5. Electrical | Characteristics                                                                                                                                                             |  |  |  |  |  |

|      |                   | 85 to 137     | Newly added                                                                                                                                                                 |  |  |  |  |  |

| 1.20 | I.20 Nov 28, 2012 |               | Information on chip versions A, B, and C, corresponding descriptions and notes, added 48-pin products added, PLQP0080JA-A 14 $\times$ 14 mm, 0.65-mm pitch, package deleted |  |  |  |  |  |