# E·XFL

### onsemi - LC88FC2H0BUTJ-2H Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Not For New Designs                                          |

| Core Processor             | Xstormy16                                                    |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 12MHz                                                        |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                            |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 86                                                           |

| Program Memory Size        | 512KB (512K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 24K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 16x12b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-TQFP                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/onsemi/lc88fc2h0butj-2h |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

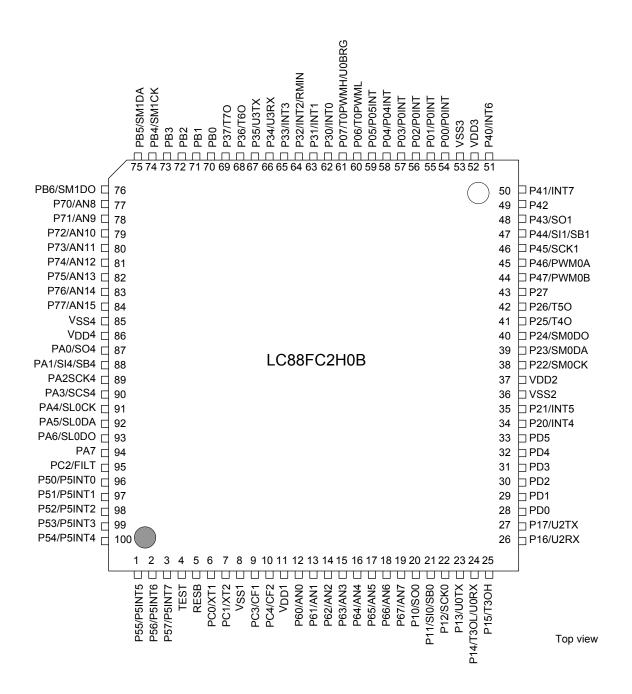

### **Pin Assignment**

TQFP100,14×14 (Pb-Free and Halogen Free type)

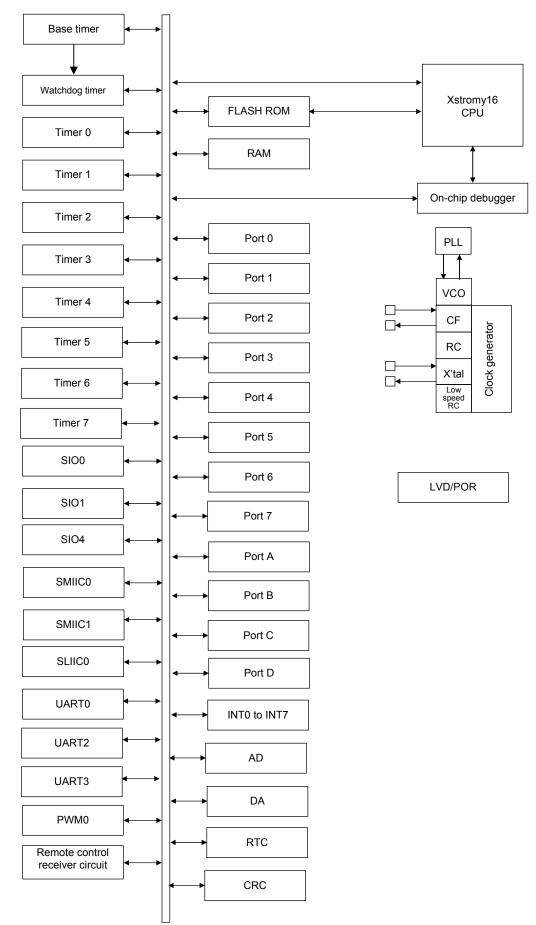

### System Block Diagram

### LC88FC2H0B

| Pin Name     | I/O | Description                                                                                       |  |

|--------------|-----|---------------------------------------------------------------------------------------------------|--|

| Port A       | I/O | • 8-bit I/O port                                                                                  |  |

| PA0 to PA7   |     | • I/O specifiable in 1-bit units                                                                  |  |

| 1110 10 1111 |     | • Pull-up resistors can be turned on and off in 1 bit units                                       |  |

|              |     | Multiplexed pin functions                                                                         |  |

|              |     | PA0 : SIO4 data output                                                                            |  |

|              |     | PA1 : SIO4 data input/pulse input/output                                                          |  |

|              |     | PA2 : SIO4 clock input/output                                                                     |  |

|              |     | PA3 : SIO4 chip select input                                                                      |  |

|              |     | PA4 : SLIIC0 clock input                                                                          |  |

|              |     | PA5 : SLIIC0 bus input/output/data input                                                          |  |

|              |     | PA6 : SLIIC0 data output (used in 3-wire SIO mode)                                                |  |

| Port B       | I/o | • 7-bit I/O port                                                                                  |  |

| PB0 to PB6   |     | • I/O specifiable in 1-bit units                                                                  |  |

|              |     | • Pull-up resistors can be turned on and off in 1 bit units                                       |  |

|              |     | • Multiplexed pin functions                                                                       |  |

|              |     | PB4 : SMIIC1 clock input/output<br>PB5 : SMIIC1 bus input/output/data input                       |  |

|              |     | PB6 : SMIIC1 data output (used in 3-wire SIO mode)                                                |  |

| Port C       | I/O | Source 1 data output (used in 5-wire Sto mode)     Source 1 data output (used in 5-wire Sto mode) |  |

|              | 1/0 | • I/O specifiable in 1-bit units                                                                  |  |

| PC0 to PC4   |     | <ul> <li>Pull-up resistors can be turned on and off in 1 bit units(PC2)</li> </ul>                |  |

|              |     | • Pin functions                                                                                   |  |

|              |     | PC0 : 32.768 kHz crystal oscillator input                                                         |  |

|              |     | PC1 : 32.768 kHz crystal oscillator output                                                        |  |

|              |     | PC2 : FILT of VCO                                                                                 |  |

|              |     | PC3 : Ceramic oscillator input                                                                    |  |

|              |     | PC4 : Ceramic oscillator output/VCO output                                                        |  |

| Port D       | I/O | • 6-bit I/O port                                                                                  |  |

|              | 1/0 | • I/O specifiable in 1-bit units                                                                  |  |

| PD0 to PD5   |     | • Pull-up resistors can be turned on and off in 1 bit units                                       |  |

| TEST         | I/O | TEST pin                                                                                          |  |

|              | 10  | • Used to communicate with on-chip debugger.                                                      |  |

|              |     | • Connects an external 100 k $\Omega$ pull-down resistor.                                         |  |

|              |     | Conneets un enternur 100 kas puir do wir resistor.                                                |  |

|                           | Demonster                               | Samah al            | Applicable Pin                                                                | Conditions                                                                  |                     |       | Specifi | cation                  |      |

|---------------------------|-----------------------------------------|---------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------|-------|---------|-------------------------|------|

|                           | Parameter                               | Symbol              | /Remarks                                                                      | Conditions                                                                  | V <sub>DD</sub> [V] | min   | typ     | max                     | unit |

| Max<br>volt               | ximum supply<br>age                     | V <sub>DD</sub> max | V <sub>DD</sub> 1, V <sub>DD</sub> 2,<br>V <sub>DD</sub> 3, V <sub>DD</sub> 4 | V <sub>SS</sub> 1=V <sub>SS</sub> 2=V <sub>SS</sub> 3=<br>V <sub>SS</sub> 4 |                     | -0.3  |         | +4.6                    |      |

| Inpu                      | ut voltage                              | VI (1)              | RESB                                                                          |                                                                             |                     | -0.3  |         | V <sub>DD</sub><br>+0.3 | v    |

| Inpu                      | ut/output voltage                       | VIO (1)             | Ports 0, 1, 2<br>Ports 3, 4, 5<br>Ports 6, 7<br>Ports A, B, C, D              |                                                                             |                     | -0.3  |         | VDD<br>+0.3             |      |

| High level output current | Peak output<br>current                  | IOPH (1)            | Ports 0, 1, 2, 3<br>P40 to P45<br>Ports 7, A, D<br>PB2 to PB6                 | CMOS output selected<br>Per applicable pin                                  |                     | -7.5  |         |                         |      |

| outpu                     |                                         | IOPH (2)            | P46, P47<br>PB0, PB1                                                          | Per applicable pin                                                          |                     | -12.5 |         |                         |      |

| ıt curi                   |                                         | IOPH (3)            | Port 5, 6<br>PC0 to PC4                                                       | Per applicable pin                                                          |                     | -4.5  |         |                         |      |

| ent                       | Average output<br>current<br>(Note 1-1) | IOMH (1)            | Ports 0, 1, 2, 3<br>P40 to P45<br>Ports 5, 6, 7, A<br>PB2 to PB6<br>Ports D   | CMOS output selected<br>Per applicable pin                                  |                     | -5    |         |                         |      |

|                           |                                         | IOMH (2)            | P46, P47<br>PB0, PB1                                                          | Per applicable pin                                                          |                     | -10   |         |                         |      |

|                           |                                         | IOMH (3)            | Port 5, 6<br>PC0 to PC4                                                       | Per applicable pin                                                          |                     | -3    |         |                         |      |

|                           | Total output current                    | $\Sigma IOAH(1)$    | Pprts 5<br>PC0 to PC4                                                         | Total of currents at applicable pins                                        |                     | -10   |         |                         |      |

|                           |                                         | $\Sigma IOAH(2)$    | Port 6                                                                        | Total of currents at applicable pins                                        |                     | -10   |         |                         | mA   |

|                           |                                         | $\Sigma IOAH(3)$    | Port 5, 6<br>PC0 to PC4                                                       | Total of currents at applicable pins                                        | -20                 |       |         |                         |      |

|                           |                                         | $\Sigma IOAH (4)$   | Ports 1,D1<br>P20 to P21                                                      | Total of currents at applicable pins                                        |                     | -20   |         |                         |      |

|                           |                                         | $\Sigma IOAH (5)$   | P22 to P27                                                                    | Total of currents at applicable pins                                        |                     | -20   |         |                         |      |

|                           |                                         | $\Sigma$ IOAH (6)   | Ports 1, 2, D                                                                 | Total of currents at applicable pins                                        |                     | -40   |         |                         |      |

|                           |                                         | $\Sigma$ IOAH (7)   | Ports 4                                                                       | Total of currents at applicable pins                                        |                     | -20   |         |                         |      |

|                           |                                         | $\Sigma$ IOAH (8)   | Ports 0, 3                                                                    | Total of currents at<br>applicable pins                                     |                     | -20   |         |                         |      |

|                           |                                         | ΣIOAH (9)           | Ports 0, 3, 4                                                                 | Total of currents at<br>applicable pins                                     |                     | -40   |         |                         |      |

|                           |                                         | ΣIOAH (10)          | Ports B, 7                                                                    | Total of currents at<br>applicable pins                                     |                     | -20   |         |                         | 1    |

|                           |                                         | ΣIOAH (11)          | Ports A                                                                       | Total of currents at applicable pins                                        |                     | -20   |         |                         |      |

|                           |                                         | ΣIOAH (12)          | Ports 7, A, B                                                                 | Total of currents at<br>applicable pins                                     |                     | -40   |         |                         | 1    |

# ■ Absolute Maximum Ratings at Ta=25°C, V<sub>SS</sub>1=V<sub>SS</sub>2=V<sub>SS</sub>3= V<sub>SS</sub>4=0V

Note 1-1 : Average output current refers to the average of output currents measured for a period of 100 ms.

Continued on next page.

| Continued from J                             | preceding pag | e.                      |                                                        |                     |     |          |       |      |

|----------------------------------------------|---------------|-------------------------|--------------------------------------------------------|---------------------|-----|----------|-------|------|

| Demonstern                                   | Secondard 1   | Applicable Pin          | Conditions                                             |                     |     | Specific | ation |      |

| Parameter                                    | Symbol        | /Remarks                | Conditions                                             | V <sub>DD</sub> [V] | min | typ      | max   | unit |

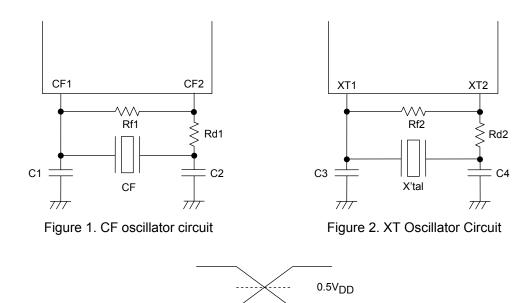

| Oscillation<br>frequency range<br>(Note 2-3) | FmCF (1)      | PC3 (CF1),<br>PC4 (CF2) | 12 MHz ceramic oscillator<br>mode<br>See Fig. 1.       | 3.0 to 3.6          |     | 12       |       |      |

| (                                            | FmCF (2)      | PC3(CF1),<br>PC4(CF2)   | 10 MHz ceramic oscillator<br>mode<br>See Fig. 1.       | 2.7 to 3.6          |     | 10       |       | MHz  |

|                                              | FmRC          |                         | Internal RC oscillation                                | 2.7 to 3.6          | 0.5 | 1.0      | 2.0   |      |

|                                              | FmSLRC        |                         | Internal low-speed RC oscillation                      | 2.7 to 3.6          | 18  | 30       | 45    |      |

|                                              | FsX'tal       | XT1, XT2                | 32.768 kHz crystal oscillator<br>mode<br>See Fig. 2.   | 2.7 to 3.6          |     | 32.768   |       | kHz  |

|                                              | FmVCO(1)      |                         | VCO oscillator<br>When setting FRQSEL=0<br>See Fig. 9. | 2.7 to 3.6          | 12  |          | 28    |      |

|                                              | FmVCO(2)      |                         | VCO oscillator<br>When setting FRQSEL=1<br>See Fig. 9. | 2.7 to 3.6          | 38  |          | 70    | MHz  |

|                                              | FmVCO(5)      |                         | VCO oscillator                                         | 2.7 to 3.6          |     | Note 2-3 |       |      |

Note 2-2 : See Tables 1 and 2 for oscillator constant values.

Note 2-3 : VCO oscillation frequency = Ceramic oscillator frequency × Setting point of SELREF

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# ■ Electrical Characteristics at Ta=-40 to +85°C, V<sub>SS</sub>1=V<sub>SS</sub>2=V<sub>SS</sub>3=V<sub>SS</sub>4=0V

| Parameter                   | Symbol  | Applicable Pin                                                           | Conditions                                                                                          |                     |                      | Specific           | ation |      |

|-----------------------------|---------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|----------------------|--------------------|-------|------|

| Parameter                   | Symbol  | /Remarks                                                                 | Conditions                                                                                          | V <sub>DD</sub> [V] | min                  | typ                | max   | unit |

| High level input<br>current | IIH (1) | Ports 0, 1, 2<br>Ports 3, 4, 5<br>Ports 6, 7<br>Ports A, B,C, D<br>RESB  | Output disabled<br>Pull-up resistor off<br>VIN=VDD<br>(including output Tr. off<br>leakage current) | 2.7 to 3.6          |                      |                    | 1     |      |

| Low level input<br>current  | IIL (1) | Ports 0, 1, 2<br>Ports 3, 4, 5<br>Ports 6, 7<br>Ports A, B, C, D<br>RESB | Output disabled<br>Pull-up resistor off<br>VIN=VSS<br>(including output Tr. off<br>leakage current) | 2.7 to 3.6          | -1                   |                    |       | μΑ   |

| High level output voltage   | VOH (1) | Ports 0, 1, 2, 3<br>Ports 5, 6                                           | IOH=-0.4mA                                                                                          | 3.0 to 3.6          | V <sub>DD</sub> -0.4 |                    |       |      |

|                             | VOH (2) | Ports A, D, PC2<br>P40 to P45<br>PB2 to PB6                              | IOH=-0.2mA                                                                                          | 2.7 to 3.6          | V <sub>DD</sub> -0.4 |                    |       |      |

|                             | VOH (3) | P46, P47                                                                 | IOH=-1.6mA                                                                                          | 3.0 to 3.6          | V <sub>DD</sub> -0.4 |                    |       |      |

|                             | VOH (4) | PB0, PB1                                                                 | IOH=-1.0mA                                                                                          | 2.7 to 3.6          | V <sub>DD</sub> -0.4 |                    |       |      |

|                             | VOH (5) | PC0, PC1,                                                                | IOH=-1.0mA                                                                                          | 3.0 to 3.6          | V <sub>DD</sub> -0.4 |                    |       |      |

|                             | VOH (6) | PC3, PC4,                                                                | IOH=-0.4mA                                                                                          | 2.7 to 3.6          | V <sub>DD</sub> -0.4 |                    |       |      |

| Low level output<br>voltage | VOL (1) | Ports 0, 1, 3 , 4<br>Ports 5, 6, 7, D<br>PC2                             | IOL=1.6mA                                                                                           | 3.0 to 3.6          |                      |                    | 0.4   | v    |

|                             | VOL (2) | P20 to P21,<br>P24 to P27<br>PA0 to PA3<br>PA6 to PA7<br>PB0 to PB3, PB6 | IOL=1.0mA                                                                                           | 2.7 to 3.6          |                      |                    | 0.4   |      |

|                             | VOL (3) | P22, P23,                                                                | IOL=3.0mA                                                                                           | 3.0 to 3.6          |                      |                    | 0.4   |      |

|                             | VOL (4) | PA4, PA5,<br>PB4, PB5                                                    | IOL=1.3mA                                                                                           | 2.7 to 3.6          |                      |                    | 0.4   |      |

|                             | VOL (5) | PC0, PC1,                                                                | IOL=1.0mA                                                                                           | 3.0 to 3.6          |                      |                    | 0.4   |      |

|                             | VOL (6) | PC3, PC4,                                                                | IOL=0.4mA                                                                                           | 2.7 to 3.6          |                      |                    | 0.4   |      |

| Pull-up resistor            | Rpu (1) | Ports 0, 1, 2, 3<br>Ports 4, 5, 6, 7                                     | VOH=0.9V <sub>DD</sub>                                                                              | 3.0 to 3.6          | 15                   | 35                 | 80    | kΩ   |

|                             | Rpu (2) | Ports A, B, D, PC2                                                       |                                                                                                     | 2.7 to 3.6          | 15                   | 35                 | 100   |      |

| Hysteresis voltage          | VHYS    | RESB<br>When ports 1, 2, 3,<br>4, A, B<br>PnFSAn=1                       |                                                                                                     | 2.7 to 3.6          |                      | 0.1V <sub>DD</sub> |       | v    |

| Pin capacitance             | СР      | All pins                                                                 | Pins other than that under<br>test<br>V <sub>IN</sub> =V <sub>SS</sub><br>f=1 MHz<br>Ta=25°C        | 2.7 to 3.6          |                      | 10                 |       | pF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

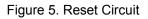

#### 2-1. SIO1 Serial Input/Output Characteristics (Wakeup Function Disabled) (Note 4-3-1)

|               | г            |                           | Shl              | Applicable              | Conditions                                                                                              |                     |      | Specif | ication        |      |

|---------------|--------------|---------------------------|------------------|-------------------------|---------------------------------------------------------------------------------------------------------|---------------------|------|--------|----------------|------|

|               | r            | arameter                  | Symbol           | Pin/Remarks             | Conditions                                                                                              | V <sub>DD</sub> [V] | min  | typ    | max            | unit |

| Seri          | Inpu         | Period                    | tSCK (4)         | SCK1 (P45)              | • See Fig. 6.                                                                                           |                     | 4    |        |                |      |

| Serial clock  | Input clock  | Low level pulse width     | tSCKL (4)        |                         |                                                                                                         |                     | 2    |        |                |      |

|               |              | High level                | tSCKH (4)        |                         |                                                                                                         |                     | 2    |        |                |      |

|               |              | pulse width               | tSCKHA (4)       |                         | <ul> <li>Automatic communication<br/>mode</li> <li>See Fig. 6.</li> </ul>                               | 2.7 to 3.6          | 6    |        |                |      |

|               |              |                           | tSCKHBSY<br>(4a) |                         | <ul> <li>Automatic communication<br/>mode</li> <li>See Fig. 6.</li> </ul>                               |                     | 23   |        |                | tCYC |

|               |              |                           | tSCKHBSY<br>(4b) |                         | <ul> <li>Mode other than automatic<br/>communication mode</li> <li>See Fig. 6.</li> </ul>               |                     | 4    |        |                |      |

|               | Output clock | Period                    | tSCK (5)         | SCK1 (P45)              | CMOS output selected     See Fig. 6.                                                                    |                     | 4    |        |                |      |

|               | t clock      | Low level pulse width     | tSCKL (5)        | _                       |                                                                                                         |                     |      | 1/2    |                | 4SCV |

|               |              | High level<br>pulse width | tSCKH (5)        | _                       |                                                                                                         |                     |      | 1/2    | 1              | tSCK |

|               |              |                           | tSCKHA (5)       |                         | <ul> <li>Automatic communication<br/>mode</li> <li>CMOS output selected</li> <li>See Fig. 6.</li> </ul> | 2.7 to 3.6          | 6    |        |                |      |

|               |              | tSCKHBS<br>(5a)           | tSCKHBSY<br>(5a) |                         | Automatic communication<br>mode     CMOS output selected     See Fig. 6.                                |                     | 4    |        | 23             | tCYC |

|               |              |                           | tSCKHBSY<br>(5b) |                         | <ul> <li>Mode other than automatic<br/>communication mode</li> <li>See Fig. 6.</li> </ul>               |                     | 4    |        |                |      |

| Serial input  | Dat          | ta setup time             | tsDI (3)         | SI1 (P44),<br>SB1 (P44) | <ul> <li>Specified with respect to<br/>rising edge of SIOCLK</li> </ul>                                 |                     | 0.03 |        |                |      |

| input         | Dat          | ta hold time              | thDI (3)         |                         | • See Fig. 6.                                                                                           | 2.7 to 3.6          | 0.03 |        |                |      |

| Serial output | Input clock  | Output delay<br>time      | tdD0 (4)         | SO1 (P43),<br>SB1 (P44) | • (Note 4-3-2)                                                                                          |                     |      |        | 1tCYC<br>+0.05 | μs   |

|               | Output clock |                           | tdDO (5)         | -                       | • (Note 4-3-2)                                                                                          | 2.7 to 3.6          |      |        | 1tCYC<br>+0.05 |      |

Note 4-3-1 : These specifications are theoretical values. Add margin depending on its use.

Note 4-3-2 : Specified with respect to the falling edge of SIOCLK. Specified as the interval up to the time an output change begins in the open drain output mode. See Fig. 6.

### 2-2. SIO1 Serial Input/Output Characteristics (Wakeup Function Enabled) (Note 4-4-1)

|               | п           | arameter              | Symbol          | Applicable              | Conditions                                        |                     |      | Specif | ication        |      |

|---------------|-------------|-----------------------|-----------------|-------------------------|---------------------------------------------------|---------------------|------|--------|----------------|------|

|               | Г           | arameter              | Symbol          | Pin/Remarks             | Conditions                                        | V <sub>DD</sub> [V] | min  | typ    | max            | unit |

| Seria         | Inpu        | Period                | tSCK (6)        | SCK1 (P45)              | • See Fig. 6.                                     |                     | 2    |        |                |      |

| Serial clock  | Input clock | Low level pulse width | tSCKL (6)       |                         |                                                   |                     | 1    |        |                |      |

|               |             | High level            | tSCKH (6)       |                         |                                                   | 2.7 to 3.6          | 1    |        |                | tCYC |

|               |             | pulse width           | tSCKHBSY<br>(6) |                         |                                                   |                     | 2    |        |                |      |

| Serial        | Dat         | ta setup time         | tsDI (4)        | SI1 (P44),<br>SB1 (P44) | • Specified with respect to rising edge of SIOCLK |                     | 0.03 |        |                |      |

| input         | Dat         | ta hold time          | thDI (4)        |                         | • See Fig. 6.                                     | 2.7 to 3.6          | 0.03 |        |                |      |

| Serial output | Input clock | Output delay<br>time  | tdD0 (6)        | SO1 (P43),<br>SB1 (P44) | • (Note 4-4-2)                                    | 2.7 to 3.6          |      |        | 1tCYC<br>+0.05 | μs   |

Note 4-4-1 : These specifications are theoretical values. Add margin depending on its use.

Note 4-4-2 : Specified with respect to the falling edge of SIOCLK. Specified as the interval up to the time an output change begins in the open drain output mode. See Fig. 6.

### 3-2. SIO4 Serial Input/Output Characteristics (Wakeup Function Enabled) (Note 4-6-1)

|               | п           | arameter              | Symbol          | Applicable              | Conditions                                        |                     |      | Specif | ication        |      |

|---------------|-------------|-----------------------|-----------------|-------------------------|---------------------------------------------------|---------------------|------|--------|----------------|------|

|               | Р           | arameter              | Symbol          | Pin/Remarks             | Conditions                                        | V <sub>DD</sub> [V] | min  | typ    | max            | unit |

| Seria         | Inpu        | Period                | tSCK (9)        | SCK4 (P45)              | • See Fig. 6.                                     |                     | 2    |        |                |      |

| Serial clock  | Input clock | Low level pulse width | tSCKL (9)       |                         |                                                   |                     | 1    |        |                |      |

|               |             | High level            | tSCKH (9)       |                         |                                                   | 2.7 to 3.6          | 1    |        |                | tCYC |

|               |             | pulse width           | tSCKHBSY<br>(9) |                         |                                                   |                     | 2    |        |                |      |

| Serial        | Dat         | ta setup time         | tsDI (6)        | SI4 (P44),<br>SB4 (P44) | • Specified with respect to rising edge of SIOCLK |                     | 0.03 |        |                |      |

| input         | Dat         | ta hold time          | thDI (6)        |                         | • See Fig. 6.                                     | 2.7 to 3.6          | 0.03 |        |                |      |

| Serial output | Input clock | Output delay<br>time  | tdD0 (9)        | SO4 (P43),<br>SB4(P44)  | • (Note 4-6-2)                                    | 2.7 to 3.6          |      |        | 1tCYC<br>+0.05 | μs   |

Note 4-6-1 : These specifications are theoretical values. Add margin depending on its use.

Note 4-6-2 : Specified with respect to the falling edge of SIOCLK. Specified as the interval up to the time an output change begins in the open drain output mode. See Fig. 6.

|               | г                                                               | arameter               | Sympol     | Applicable                        | Conditions                                                                                                                                                                         |                     |      | Specif | ication        |      |

|---------------|-----------------------------------------------------------------|------------------------|------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|--------|----------------|------|

|               | P                                                               | rarameter              | Symbol     | Pin/Remarks                       | Conditions                                                                                                                                                                         | V <sub>DD</sub> [V] | min  | typ    | max            | unit |

| Serial clock  | Input clock                                                     | Period                 | tSCK (10)  | SM0CK<br>(P22)                    | See Fig. 6.                                                                                                                                                                        |                     | 4    |        |                |      |

| clock         | clock                                                           | Low level pulse width  | tSCKL (10) |                                   |                                                                                                                                                                                    | 2.7 to 3.6          | 2    |        |                |      |

|               |                                                                 | High level pulse width | tSCKH (10) |                                   |                                                                                                                                                                                    |                     | 2    |        |                | tCYC |

|               | Outpu                                                           | Period                 | tSCK (11)  | SM0CK<br>(P22)                    | CMOS output selected     See Fig. 6.                                                                                                                                               |                     | 4    |        |                |      |

|               | Period<br>Low level<br>pulse width<br>High level<br>pulse width | tSCKL (11)             |            |                                   | 2.7 to 3.6                                                                                                                                                                         |                     | 1/2  |        |                |      |

|               |                                                                 | tSCKH (11)             |            |                                   |                                                                                                                                                                                    |                     | 1/2  |        | tSCK           |      |

| Serial input  | Dat                                                             | ta setup time          | tsDI (7)   | SM0DA<br>(P23),                   | • Specified with respect to rising edge of SIOCLK                                                                                                                                  |                     | 0.03 |        |                |      |

| input         | Dat                                                             | ta hold time           | thDI (7)   |                                   | • See Fig. 6.                                                                                                                                                                      | 2.7 to 3.6          | 0.03 |        |                |      |

| Serial output | Ou                                                              | tput delay time        | tdD0 (10)  | SM0DO<br>(P24),<br>SM0DA<br>(P23) | <ul> <li>Specified with respect to<br/>falling edge of SIOCLK</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> <li>See Fig. 6.</li> </ul> | 2.7 to 3.6          |      |        | 1tCYC<br>+0.05 | μs   |

### 4-1. SMIIC0 Simple SIO Mode Input/Output Characteristics

Note 4-7-1 : These specifications are theoretical values. Add margin depending on its use.

# 4-2. SMIIC0 I<sup>2</sup>C Mode Input/Output Characteristics

|            | D               | aramatar                             |        | Symbol   | Applicable                                                       | Conditions                                                                                                                     |                     |     | Specif | ication | _     |

|------------|-----------------|--------------------------------------|--------|----------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|--------|---------|-------|

|            | Pa              | arameter                             |        | Symbol   | Pin/Remarks                                                      | Conditions                                                                                                                     | V <sub>DD</sub> [V] | min | typ    | max     | unit  |

| Clock      | Input clock     | Period                               |        | tSCL     | SM0CK<br>(P22)                                                   | • See Fig. 8.                                                                                                                  |                     | 5   |        |         |       |

|            | lock            | Low level<br>pulse widt              | Ь      | tSCLL    |                                                                  |                                                                                                                                | 2.7 to 3.6          | 2.5 |        |         |       |

|            |                 | High level                           |        | tSCLH    |                                                                  |                                                                                                                                |                     |     |        |         | Tfilt |

|            |                 | pulse widt                           |        |          |                                                                  |                                                                                                                                |                     | 2   |        |         |       |

|            | Output clock    | Period                               |        | tSCLx    | SM0CK<br>(P22)                                                   | • Specified as interval up to time when output state starts                                                                    |                     | 10  |        |         |       |

|            | clock           | Low level pulse widt                 | h      | tSCLLx   |                                                                  | changing.                                                                                                                      | 2.7 to 3.6          |     | 1/2    |         | 49.01 |

|            |                 | High level<br>pulse widt             |        | tSCLHx   |                                                                  |                                                                                                                                |                     |     | 1/2    |         | tSCL  |

| pin        | s inp           | C and SM0E<br>out spike<br>sion time | )A     | tsp      | SM0CK (P22)<br>SM0DA (P23)                                       | • See Fig. 8.                                                                                                                  | 2.7 to 3.6          |     |        | 1       | Tfilt |

|            |                 |                                      | Input  | tBUF     | SM0CK (P22)<br>SM0DA (P23)                                       | • See Fig. 8.                                                                                                                  |                     | 2.5 |        |         | Tfilt |

|            | weer            | ease time<br>n start and             | Ou     | tBUFx    | SM0CK (P22)<br>SM0DA (P23)                                       | <ul> <li>Standard clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul>   | 2.7 to 3.6          | 5.5 |        |         |       |

|            | sop             |                                      | Output |          |                                                                  | <ul> <li>High-speed clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> |                     | 1.6 |        |         | μs    |

|            |                 |                                      | I      | tHD;STA  | SM0CK (P22)<br>SM0DA (P23)                                       | When SMIIC register<br>control bit,<br>I2CSHDS=0<br>· See Fig. 8.                                                              |                     | 2.0 |        |         |       |

|            |                 | restart                              |        |          | When SMIIC register<br>control bit<br>I2CSHDS=1<br>· See Fig. 8. |                                                                                                                                | 2.5                 |     |        | Tfilt   |       |

| cor<br>tim |                 | on hold                              | 01     | tHD;STAx | SM0CK (P22)<br>SM0DA (P23)                                       | <ul> <li>Standard clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul>   | 2.7 to 3.6          | 4.1 |        |         |       |

|            |                 |                                      | Output |          |                                                                  | <ul> <li>High-speed clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> |                     | 1.0 |        |         | μs    |

|            | _               | _                                    | Input  | tSU;STA  | SM0CK (P22)<br>SM0DA (P23)                                       | • See Fig. 8.                                                                                                                  |                     | 1.0 |        |         | Tfilt |

|            | start<br>up tii | condition<br>me                      | Out    | tSU;STAx | SM0CK (P22)<br>SM0DA (P23)                                       | <ul> <li>Standard clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul>   | 2.7 to 3.6          | 5.5 |        |         |       |

|            |                 |                                      | Output |          |                                                                  | <ul> <li>High-speed clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> |                     | 1.6 |        |         | – μs  |

### 5-2. SMIIC1 I<sup>2</sup>C Mode Input/Output Characteristics

|       | D               | arameter                             |        | Symbol   | Applicable                 | Conditions                                                                                                                     |                     |     | Specif | ication | _      |

|-------|-----------------|--------------------------------------|--------|----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|--------|---------|--------|

|       | P               | arameter                             |        | Symbol   | Pin/Remarks                | Conditions                                                                                                                     | V <sub>DD</sub> [V] | Min | typ    | max     | unit   |

| Clock | Input clock     | Period                               |        | tSCL     | SM1CK<br>(PB4)             | • See Fig. 8.                                                                                                                  |                     | 5   |        |         |        |

|       | lock            | Low level pulse widt                 | h      | tSCLL    |                            |                                                                                                                                | 2.7 to 3.6          | 2.5 |        |         | TCL    |

|       |                 | High level<br>pulse widt             |        | tSCLH    |                            |                                                                                                                                |                     | 2   |        |         | Tfilt  |

|       | Outpu           | Period                               |        | tSCLx    | SM1CK<br>(PB4)             | • Specified as interval up to time when output state starts                                                                    |                     | 10  |        |         |        |

|       | Output clock    | Low level pulse widt                 | h      | tSCLLx   |                            | changing.                                                                                                                      | 2.7 to 3.6          |     | 1/2    |         |        |

|       |                 | High level<br>pulse widt             |        | tSCLHx   |                            |                                                                                                                                |                     |     | 1/2    |         | tSCL   |

| pin   | s inp           | C and SM0E<br>out spike<br>sion time | рА     | tsp      | SM1CK (PB4)<br>SM1DA (PB5) | • See Fig. 8.                                                                                                                  | 2.7 to 3.6          |     |        | 1       | Tfilt  |

|       |                 |                                      | Input  | tBUF     | SM1CK (PB4)<br>SM1DA (PB5) | • See Fig. 8.                                                                                                                  |                     | 2.5 |        |         | Tfilt  |

|       | weer            | ease time<br>n start and             | Ou     | tBUFx    | SM1CK (PB4)<br>SM1DA (PB5) | <ul> <li>Standard clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul>   | 2.7 to 3.6          | 5.5 |        |         |        |

|       |                 |                                      | Output |          |                            | <ul> <li>High-speed clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> |                     | 1.6 |        |         | μsec   |

|       |                 |                                      | In     | tHD;STA  | SM1CK (PB4)<br>SM1DA (PB5) | <ul> <li>When SMIIC register<br/>control bit,<br/>I2CSHDS=0</li> <li>See Fig. 8.</li> </ul>                                    |                     | 2.0 |        |         |        |

|       |                 | estart                               | ıput   |          |                            | When SMIIC register<br>control bit<br>I2CSHDS=1<br>· See Fig. 8.                                                               |                     | 2.5 |        |         | Tfilt  |

| tim   |                 | on hold                              | Ou     | tHD;STAx | SM1CK (PB4)<br>SM1DA (PB5) | <ul> <li>Standard clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul>   | 2.7 to 3.6          | 4.1 |        |         |        |

|       |                 |                                      | Output |          |                            | <ul> <li>High-speed clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> |                     | 1.0 |        |         | μsec   |

|       |                 |                                      | Input  | tSU;STA  | SM1CK (PB4)<br>SM1DA (PB5) | • See Fig. 8.                                                                                                                  |                     | 1.0 |        |         | Tfilt  |

|       | start<br>up tii | condition<br>me                      | Out    | tSU;STAx | SM1CK (PB4)<br>SM1DA (PB5) | <ul> <li>Standard clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul>   | 2.7 to 3.6          | 5.5 |        |         | 11522  |

|       |                 |                                      | Output |          |                            | <ul> <li>High-speed clock mode</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> |                     | 1.6 |        |         | – μsec |

| Parameter     |                   | S-mak al                  | Applicable                                  | Conditions                        |                                                                                                                                                                                    |                     | Specific | cation |                |      |

|---------------|-------------------|---------------------------|---------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|--------|----------------|------|

|               | 1                 | Parameter                 | Symbol                                      | Pin/Remarks                       | Conditions                                                                                                                                                                         | V <sub>DD</sub> [V] | min      | typ    | max            | unit |

| Serial        | Input clock       | Period                    | Period tSCK (13) SLOCK See Fig. 6.<br>(PA4) |                                   |                                                                                                                                                                                    |                     | 4        |        |                |      |

| clock         | clock             | Low level<br>pulse width  | tSCKL (13)                                  |                                   |                                                                                                                                                                                    | 2.7 to 3.6          | 2        |        |                | tCYC |

|               |                   | High level<br>pulse width | tSCKH (13)                                  |                                   |                                                                                                                                                                                    |                     | 2        |        |                |      |

| Serial        | Data setup time   |                           | ta setup time tsDI (9) SL0DA<br>(PA5),      |                                   | • Specified with respect to rising edge of SIOCLK                                                                                                                                  |                     | 0.03     |        |                |      |

| input         | Da                | ta hold time              | thDI (9)                                    |                                   | • See Fig. 6.                                                                                                                                                                      | 2.7 to 3.6          | 0.03     |        |                |      |

| Serial output | Output delay time |                           | tdD0 (13)                                   | SL0DO<br>(PA6),<br>SL0DA<br>(PA5) | <ul> <li>Specified with respect to<br/>falling edge of SIOCLK</li> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> <li>See Fig. 6.</li> </ul> | 2.7 to 3.6          |          |        | 1tCYC<br>+0.05 | μs   |

### 6-1. SLIIC0 Simple SIO Mode Input/Output Characteristics

Note 4-11-1 : These specifications are theoretical values. Add margin depending on its use.

### 6-2. SLIIC1 I<sup>2</sup>C Mode Input/Output Characteristics

|                                                         | р                            | arameter                  |         | Symbol                     | Applicable                                                                                  | Conditions                                                                                      |                     |                                                                                        | Specif | ïcation |       |

|---------------------------------------------------------|------------------------------|---------------------------|---------|----------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------|--------|---------|-------|

|                                                         | P                            | arameter                  |         | Symbol                     | Pin/Remarks                                                                                 | Conditions                                                                                      | V <sub>DD</sub> [V] | 5       .6       2.5       .6       .6       2.5       .6       2.5       .6       2.5 | unit   |         |       |

| Clock                                                   | Input clock                  | Period                    |         | tSCL                       | SLOCK<br>(PA4)                                                                              | • See Fig. 8.                                                                                   |                     | 5                                                                                      |        |         |       |

|                                                         | clock                        | Low level pulse width     | h       | tSCLL                      |                                                                                             |                                                                                                 | 2.7 to 3.6          | 2.5                                                                                    |        |         | Tfilt |

|                                                         |                              | High level<br>pulse width |         | tSCLH                      |                                                                                             |                                                                                                 |                     | 2                                                                                      |        |         |       |

| SLOCK and SLODA<br>pins input spike<br>suppression time |                              |                           | tsp     | SLOCK (PA4)<br>SLODA (PA5) | • See Fig. 8.                                                                               | 2.7 to 3.6                                                                                      |                     |                                                                                        | 1      | Tfilt   |       |

| Bus release time<br>between start and<br>stop           |                              | Input                     | tBUF    | SLOCK (PA4)<br>SLODA (PA5) | • See Fig. 8.                                                                               | 2.7 to 3.6                                                                                      | 2.5                 |                                                                                        |        | Tfilt   |       |

| Start/restart<br>condition hold                         |                              | Input                     | tHD;STA | SLOCK (PA4)<br>SLODA (PA5) | <ul> <li>When SMIIC register<br/>control bit,<br/>I2CSHDS=0</li> <li>See Fig. 8.</li> </ul> | 2.7 to 3.6                                                                                      | 2.0                 |                                                                                        |        | Tfilt   |       |

| tim                                                     | time                         |                           | ut      |                            |                                                                                             | When SMIIC register<br>control bit<br>I2CSHDS=1<br>· See Fig. 8.                                |                     | 2.5                                                                                    |        |         |       |

|                                                         | Restart condition setup time |                           | Input   | tSU;STA                    | SLOCK (PA4)<br>SLODA (PA5)                                                                  | • See Fig. 8.                                                                                   | 2.7 to 3.6          | 1.0                                                                                    |        |         | Tfilt |

|                                                         | op co<br>up ti               | ndition<br>me             | Input   | tSU;STO                    | SLOCK (PA4)<br>SLODA (PA5)                                                                  | • See Fig. 8.                                                                                   | 2.7 to 3.6          | 1.0                                                                                    |        |         | Tfilt |

| De                                                      |                              |                           | Input   | tHD;DAT                    | SL0CK (PA4)<br>SL0DA (PA5)                                                                  | • See Fig. 8.                                                                                   | 2.7 to 3.6          | 0                                                                                      |        |         | TOTA  |

| Da                                                      | Data hold tin                | sia time                  | Output  | tHD;DATx                   | SL0CK (PA4)<br>SL0DA (PA5)                                                                  | <ul> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> | 2.7 10 3.6          | 1                                                                                      |        | 1.5     | Tfilt |

| Da                                                      | Data setup time              |                           | Input   | tSU;DAT                    | SLOCK (PA4)<br>SLODA (PA5)                                                                  | • See Fig. 8.                                                                                   | 2.7 to 3.6          | 1                                                                                      |        |         | T£14  |

| Da                                                      |                              |                           | Output  | tSU;DATx                   | SLOCK (PA4)<br>SLODA (PA5)                                                                  | <ul> <li>Specified as interval up to<br/>time when output state starts<br/>changing.</li> </ul> | 2.7 10 5.0          | 1tSCL-<br>1.5Tfilt                                                                     |        |         | Tfilt |

### ■ AD Converter Characteristics at Ta=-40 to +85°C, V<sub>SS</sub>1=V<sub>SS</sub>2=V<sub>SS</sub>3=V<sub>SS</sub>4=0V 1. 12-bit AD Conversion Mode

|                               | 0 1 1  | Applicable Pin             | Q IV                       |                     | Specification   |     |                 |      |  |

|-------------------------------|--------|----------------------------|----------------------------|---------------------|-----------------|-----|-----------------|------|--|

| Parameter                     | Symbol | /Remarks                   | Conditions                 | V <sub>DD</sub> [V] | min             | typ | max             | unit |  |

| Resolution                    | NAD    | AN0 (P60)<br>to AN7 (P67), |                            | 2.7 to 3.6          |                 | 12  |                 | bit  |  |

| Absolute accuracy             | ETAD   | AN8 (P70)                  | (Note 6-1)                 | 2.7 to 3.6          |                 |     | ±16             | LSB  |  |

| Conversion time               | TCAD12 | to AN15 (P77)              | Conversion time calculated | 3.0 to 3.6          | 64              |     | 115             |      |  |

|                               |        |                            |                            | 2.7 to 3.6          | 128             |     | 230             | μs   |  |

| Analog input<br>voltage range | VAIN   |                            |                            | 2.7 to 3.6          | V <sub>SS</sub> |     | V <sub>DD</sub> | v    |  |

| Analog port<br>input current  | IAINH  |                            | VAIN=V <sub>DD</sub>       | 2.7 to 3.6          |                 |     | 1               |      |  |

| input current                 | IAINL  |                            | VAIN=V <sub>SS</sub>       | 2.7 to 3.6          | -1              |     |                 | μΑ   |  |

- Conversion time calculation formula : TCAD12 =  $(\frac{52}{\text{AD division ratio}} + 2) \times \text{tCYC}$

### 2. 8-bit AD Conversion Mode

| Parameter                     | Course of | Applicable Pin                          | Conditions           |                     |     | Specif | ication         |      |

|-------------------------------|-----------|-----------------------------------------|----------------------|---------------------|-----|--------|-----------------|------|

| Parameter                     | Symbol    | /Remarks                                | Conditions           | V <sub>DD</sub> [V] | min | typ    | max             | unit |

| Resolution                    | NAD       | AN0 (P60)<br>to AN7 (P67),              |                      | 2.7 to 3.6          |     | 8      |                 | bit  |

| Absolute accuracy             | ETAD      | AN8 (P70)                               | (Note 6-1)           | 2.7 to 3.6          |     |        | ±1.5            | LSB  |

| Conversion time               | TCAD8     | to AN15 (P77) Conversion time calculate |                      | 3.0 to 3.6          | 39  |        | 71              |      |

|                               |           |                                         |                      | 2.7 to 3.6          | 79  |        | 140             | μs   |

| Analog input<br>voltage range | VAIN      |                                         |                      | 2.7 to 3.6          | VSS |        | V <sub>DD</sub> | V    |

| Analog port<br>input current  | IAINH     |                                         | VAIN=VDD             | 2.7 to 3.6          |     |        | 1               |      |

| input current                 | IAINL     |                                         | VAIN=V <sub>SS</sub> | 2.7 to 3.6          | -1  |        |                 | μA   |

- Conversion time calculation formula : TCAD8 =  $\left(\frac{52}{\text{AD division ratio}} + 2\right) \times \text{tCYC}$

Note 6-1 : The quantization error ( $\pm 1/2$ LSB) is excluded from the absolute accuracy.

Note 6-2 : The conversion time refers to the interval from the time a conversion starting instruction is issued till the time the complete digital value against the analog input value is loaded in the result register.

The conversion time is twice the normal value when one of the following conditions occurs:

- The first AD conversion is executed in the 12-bit AD conversion mode after a system reset.

- The first AD conversion is executed after the AD conversion mode is switched from 8-bit to 12-bit AD conversion mode.

| Continued from                       | m preceding pa                                                               | ige.                      |                                                                                                             |                     |               |     |     |      |  |

|--------------------------------------|------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------|---------------------|---------------|-----|-----|------|--|

|                                      |                                                                              | Applicable<br>Pin/Remarks |                                                                                                             |                     | Specification |     |     |      |  |

| r ai ailictei                        | Symbol                                                                       | r III/ Keillaiks          | Conditions                                                                                                  | V <sub>DD</sub> [V] | min           | typ | max | unit |  |

| HOLD mode<br>consumption<br>current  | IDDHOLD (1)                                                                  | V <sub>DD</sub> 1         | HOLD mode<br>• CF1=VDD or open<br>(external clock mode)                                                     | 2.7 to 3.6          |               | 0.2 | 45  |      |  |

|                                      | IDDHOLD (2)                                                                  |                           | HOLD mode<br>• CF1=VDD or open<br>(external clock mode)<br>• LVD option selected                            | 2.7 to 3.6          |               | 1.2 | 48  |      |  |

| HOLDX mode<br>consumption<br>current | IDDHOLD (3)                                                                  |                           | HOLDX mode<br>• CF1=VDD or open<br>(external clock mode)<br>• FmX'tal=32.768 kHz crystal<br>oscillator mode | 2.7 to 3.6          |               | 4.6 | 60  | μΑ   |  |

|                                      | IDDHOLD (4)     HOLDX mode       • CF1=VDD or open     (external clock mode) |                           | 2.7 to 3.6                                                                                                  |                     | 5.6           | 63  |     |      |  |

Note 7-1 : The consumption current value includes none of the currents that flow into the output transistor and internal pull-up resistors.

### ■ **F-ROM Programming Characteristics** at Ta=+10 to +55°C, V<sub>SS</sub>1=V<sub>SS</sub>2=V<sub>SS</sub>3=V<sub>SS</sub>4=0V

| Parameter                         | Symbol                        | Applicable        | Conditions                                            |            | Specification |     |      |    |  |

|-----------------------------------|-------------------------------|-------------------|-------------------------------------------------------|------------|---------------|-----|------|----|--|

| Parameter                         | Symbol Pin/Remarks Conditions |                   | V <sub>DD</sub> [V]                                   | min        | typ           | max | unit |    |  |

| Onboard<br>programming<br>current | IDDFW (1)                     | V <sub>DD</sub> 1 | Microcontroller erase current<br>current is excluded. | 2.7 to 3.6 |               |     | 10   | mA |  |

| Onboard<br>programming<br>time    | tFW (1)                       |                   | • 2K-byte erase operation                             | 2.7 to 3.6 |               |     | 25   | ms |  |

|                                   | tFW (2)                       |                   | 2-byte programming operation                          | 2.7 to 3.6 |               |     | 45   | μs |  |

### Characteristics of a Sample Main System Clock Oscillation Circuit

Given below are the characteristics of a sample main system clock oscillation circuit that are measured using a Our Company -designated oscillation characteristics evaluation board and external components with circuit constant values with which the oscillator vendor confirmed normal and stable oscillation.

### Table 1 Characteristics of a Sample Main System Clock Oscillator Circuit with a Ceramic Resonator

| Nominal   | Vendor Name  | Decemeter       |            | Circuit    | Constant  |            | Operating<br>Voltage | Oscillation<br>Stabilization Time |             | Remarks                   |  |

|-----------|--------------|-----------------|------------|------------|-----------|------------|----------------------|-----------------------------------|-------------|---------------------------|--|

| Frequency | vendor Ivame | Resonator       | C3<br>[pF] | C4<br>[pF] | Rf<br>[Ω] | Rd2<br>[Ω] | Range<br>[V]         | typ<br>[ms]                       | max<br>[ms] | Kennarks                  |  |

| 12 MHz    |              | CSTCE12M0G52-R0 | (10)       | (10)       | OPEN      | 330        | 2.2 to 3.6           | 0.02                              | 0.2         | C1, C2<br>integrated type |  |

| 10 MHz    | MURATA       | CSTCE10M0G52-R0 | (10)       | (10)       | OPEN      | 680        | 2.2 to 2.6           | 0.02                              | 0.2         | C1, C2<br>integrated type |  |

| 10 MHZ    |              | CSTLS10M0G53-B0 | (15)       | (15)       | OPEN      | 680        | 2.2 to 3.6           | 0.02                              | 0.2         | C1, C2<br>integrated type |  |

The oscillation stabilization time refers to the time interval that is required for the oscillation to get stabilized after V<sub>DD</sub> goes above the lower limit level of the operating voltage range (see Figure 4)

### ■ Characteristics of a Sample Subsystem Clock Oscillator Circuit

Given below are the characteristics of a sample subsystem clock oscillation circuit that are measured using a Our Company -designated oscillation characteristics evaluation board and external components with circuit constant values with which the oscillator vendor confirmed normal and stable oscillation.

### Table 2 Characteristics of a Sample Subsystem Clock Oscillator Circuit with a Crystal Resonator

| Nominal    | Vendor Name      | Resonator  | Circuit Constant |            |            | t          | Operating Voltage | Oscillation<br>Stabilization Time |            | Remarks  |  |

|------------|------------------|------------|------------------|------------|------------|------------|-------------------|-----------------------------------|------------|----------|--|

| Frequency  | vendor Name      | Resolution | C3<br>[pF]       | C4<br>[pF] | Rf2<br>[Ω] | Rd2<br>[Ω] | Range<br>[V]      | typ<br>[s]                        | max<br>[s] | Keinarks |  |

| 32.768 kHz | EPSON<br>TOYOCOM | MC-306     | 10               | 10         | Open       | 330K       | 2.2 to 3.6        | 1.0                               | 3.0        | CL=7.0pF |  |

The oscillation stabilization time refers to the time interval that is required for the oscillation to get stabilized after the instruction for starting the subclock oscillator circuit is executed plus the time interval that is required for the oscillation to get stabilized after the HOLD mode is released (see Figure 4).

Note : The traces to and from the components that are involved in oscillation should be kept as short as possible as the oscillation characteristics are affected by their trace pattern.

Note :

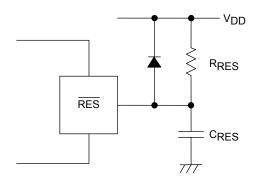

Reset signal must be present when power supply rises.

Determine the value of  $C_{RES}$  and  $R_{RES}$  so that the reset signal is present for 10 µs after the supply voltage gets stabilized.

\* Remarks: DIx and DOx denote the last bits communicated; x=0 to 32768

Figure 6. Serial I/O Waveforms

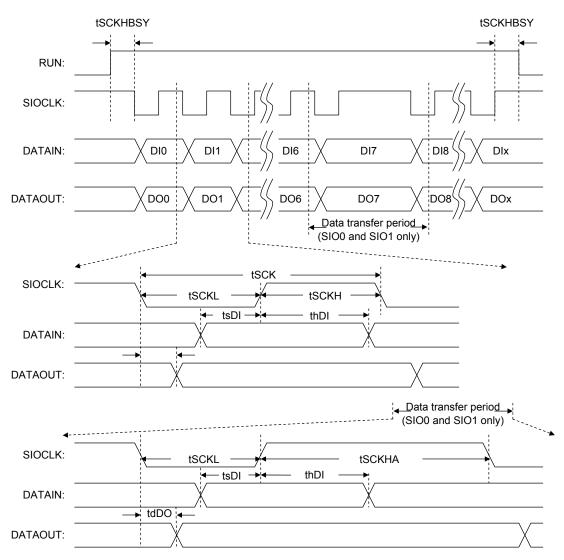

Figure 10. Waveform observed when only POR is used (LVD not used) (RESET pin : Pull-up resistor R<sub>RES</sub> only)

- The POR function generates a reset only when power is turned on starting at the VSS level.