Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 25MHz                                                                                    |

| Connectivity               | EBI/EMI, Serial Port                                                                     |

| Peripherals                | POR, WDT                                                                                 |

| Number of I/O              | 36                                                                                       |

| Program Memory Size        | 32KB (32K x 8)                                                                           |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 44-BQFP                                                                                  |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w77l058a25fl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 5. FUNCTIONAL DESCRIPTION

The W77L058 is 8052 pin compatible and instruction set compatible. It includes the resources of the standard 8052 such as four 8-bit I/O Ports, three 16-bit timer/counters, full duplex serial port and interrupt sources.

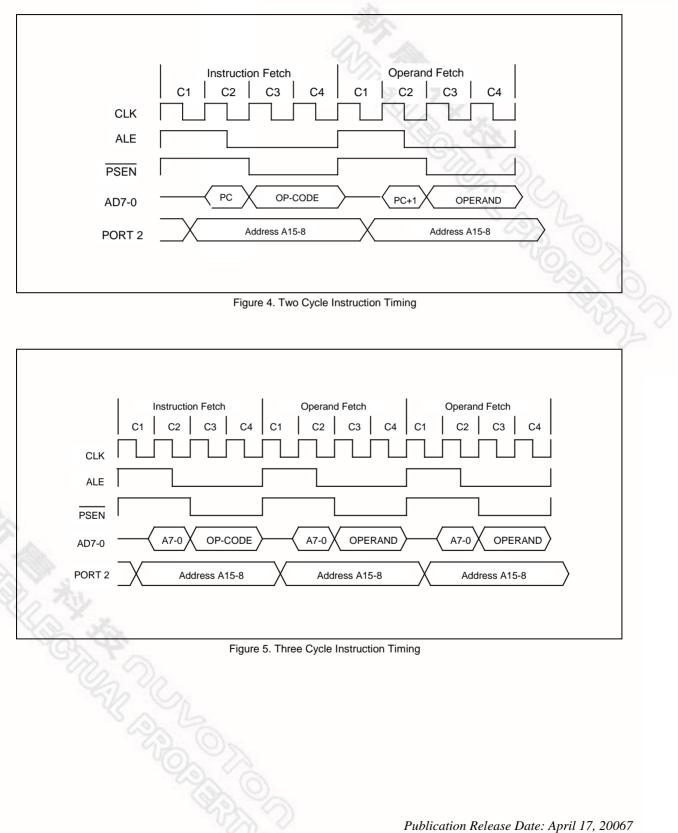

The W77L058 features a faster running and better performance 8-bit CPU with a redesigned core processor without wasted clock and memory cycles. it improves the performance not just by running at high frequency but also by reducing the machine cycle duration from the standard 8052 period of twelve clocks to four clock cycles for the majority of instructions. This improves performance by an average of 1.5 to 3 times. The W77L058 also provides dual Data Pointers (DPTRs) to speed up block data memory transfers. It can also adjust the duration of the MOVX instruction (access to off-chip data memory) between two machine cycles and nine machine cycles. This flexibility allows the W77L058 to work efficiently with both fast and slow RAMs and peripheral devices. In addition, the W77L058 contains on-chip 1KB MOVX SRAM, the address of which is between 0000H and 03FFH. It only can be accessed by MOVX instruction; this on-chip SRAM is optional under software control.

The W77L058 is an 8052 compatible device that gives the user the features of the original 8052 device, but with improved speed and power consumption characteristics. It has the same instruction set as the 8051 family, with one addition: DEC DPTR (op-code A5H, the DPTR is decreased by 1). While the original 8051 family was designed to operate at 12 clock periods per machine cycle, the W77L058 operates at a much reduced clock rate of only 4 clock periods per machine cycle. This naturally speeds up the execution of instructions. Consequently, the W77L058 can run at a higher speed as compared to the original 8052, even if the same crystal is used. Since the W77L058 is a fully static CMOS design, it can also be operated at a lower crystal clock, giving the same throughput in terms of instruction execution, yet reducing the power consumption.

The 4 clocks per machine cycle feature in the W77L058 is responsible for a three-fold increase in execution speed. The W77L058 has all the standard features of the 8052, and has a few extra peripherals and features as well.

### I/O Ports

The W77L058 has four 8-bit ports and one extra 4-bit port. Port 0 can be used as an Address/Data bus when external program is running or external memory/device is accessed by MOVC or MOVX instruction. In these cases, it has strong pull-ups and pull-downs, and does not need any external pull-ups. Otherwise it can be used as a general I/O port with open-drain circuit. Port 2 is used chiefly as the upper 8-bits of the Address bus when port 0 is used as an address/data bus. It also has strong pull-ups and pull-downs when it serves as an address bus. Port 1 and 3 act as I/O ports with alternate functions. Port 4 is only available on 44-pin PLCC/QFP package type. It serves as a general purpose I/O port as Port 1 and Port 3. The P4.0 has an alternate function WAIT which is the wait state control signal. When wait state control signal is enabled, P4.0 is input only.

#### Serial I/O

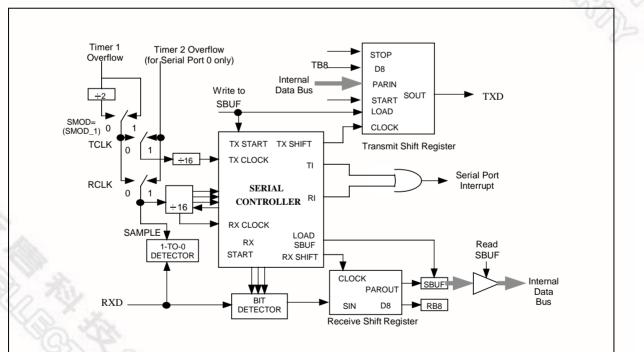

The W77L058 has two enhanced serial ports that are functionally similar to the serial port of the original 8052 family. However the serial ports on the W77L058 can operate in different modes in order to obtain timing similarity as well. Note that the serial port 0 can use Timer 1 or 2 as baud rate generator, but the serial port 1 can only use Timer 1 as baud rate generator. The serial ports have the enhanced features of Automatic Address recognition and Frame Error detection.

| 80h Indirect RAM   Option Direct RAM                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------|

| Direct RAM                                                                                                                    |

| Direct RAM                                                                                                                    |

|                                                                                                                               |

| 30h<br>2Fh 7F 7E 7D 7C 7B 7A 79 78                                                                                            |

| 2Eh 77 76 75 74 73 72 71 70                                                                                                   |

| 2Dh 6F 6E 6D 6C 6B 6A 69 68                                                                                                   |

| 2Ch 67 66 65 64 63 62 61 60                                                                                                   |

| 2Bh 5F 5E 5D 5C 5B 5A 59 58                                                                                                   |

| 2Ah 57 56 55 54 53 52 51 50                                                                                                   |

| 29h 4F 4E 4D 4C 4B 4A 49 48                                                                                                   |

| 28h 47 46 45 44 43 42 41 40 Bit Addressal                                                                                     |

| 27h <u>3F 3E 3D 3C 3B 3A 39 38</u>                                                                                            |

| 26h 37 36 35 34 33 32 31 30 20H-2FH                                                                                           |

| 25h 2F 2E 2D 2C 2B 2A 29 28                                                                                                   |

| 24h 27 26 25 24 23 22 21 20                                                                                                   |

| 23h     1F     1E     1D     1C     1B     1A     19     18       22h     17     16     15     14     13     12     11     10 |

| 211 17 16 15 14 13 12 11 10<br>211 0F 0E 0D 0C 0B 0A 09 08                                                                    |

| 20h 07 06 05 04 03 02 01 00                                                                                                   |

| 1Eb                                                                                                                           |

| 18h Bank 3                                                                                                                    |

| 17h Bank 2                                                                                                                    |

|                                                                                                                               |

| 08h Bank 1                                                                                                                    |

| 0011                                                                                                                          |

Figure 2. Scratchpad RAM/Register Addressing

### **Special Function Registers**

The W77L058 uses Special Function Registers (SFRs) to control and monitor peripherals and their Modes.

The SFRs reside in the register locations 80-FFh and are accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where one wishes to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0 or 8. The W77L058 contains all the SFRs present in the standard 8052. However, some additional SFRs have been added. In some cases unused bits in the original 8052 have been given new functions. The list of SFRs is as follows. The table is condensed with eight locations per row. Empty locations indicate that there are no registers at these addresses. When a bit or register is not implemented, it will read high.

#### Timer 1 MSB

| Bit:                                                             | 7        | 6     | 5     | 4     | 3         | 2         | 1     | 0     |  |

|------------------------------------------------------------------|----------|-------|-------|-------|-----------|-----------|-------|-------|--|

|                                                                  | TH1.7    | TH1.6 | TH1.5 | TH1.4 | TH1.3     | TH1.2     | TH1.1 | TH1.0 |  |

| Mnemoni                                                          | c: TH1   |       | S/S   | A     | ddress: 8 | Dh        |       |       |  |

| TH1.7-0: Timer 1 MSB                                             |          |       |       |       |           |           |       |       |  |

| Clock Control                                                    |          |       |       |       |           |           |       |       |  |

| Bit:                                                             | 7        | 6     | 5     | 4     | 3         | 2         | 1     | 0     |  |

|                                                                  | WD1      | WD0   | T2M   | T1M   | том       | MD2       | MD1   | MD0   |  |

| Mnemoni                                                          | c: CKCON |       |       |       | A         | ddress: 8 | Eh    |       |  |

| WD1-0: Watchdog timer n<br>timer. In all four tin<br>out period. |          |       |       |       |           |           |       |       |  |

| WD1 | WD0 | Interrupt time-out | Reset time-out        |

|-----|-----|--------------------|-----------------------|

| 0   | 0   | 2 <sup>17</sup>    | 2 <sup>17</sup> + 512 |

| 0   | 1   | 2 <sup>20</sup>    | 2 <sup>20</sup> + 512 |

| 1   | 0   | 2 <sup>23</sup>    | 2 <sup>23</sup> + 512 |

| 1   | 1   | 2 <sup>26</sup>    | 2 <sup>26</sup> + 512 |

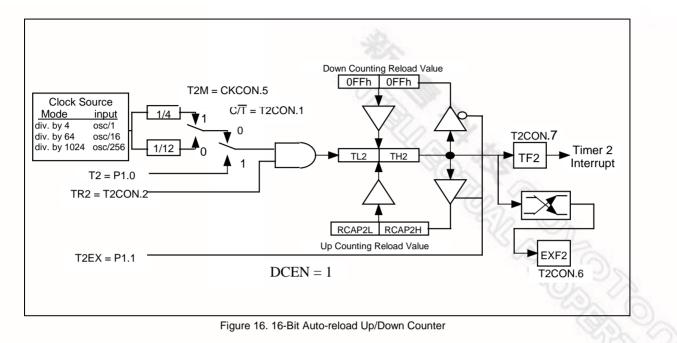

- T2M: Timer 2 clock select: When T2M is set to 1, timer 2 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- T1M: Timer 1 clock select: When T1M is set to 1, timer 1 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- T0M: Timer 0 clock select: When T0M is set to 1, timer 0 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- MD2-0: Stretch MOVX select bits: These three bits are used to select the stretch value for the MOVX instruction. Using a variable MOVX length enables the user to access slower external memory devices or peripherals without the need for external circuits. The RD or WR strobe will be stretched by the selected interval. When accessing the on-chip SRAM, the MOVX instruction is always in 2 machine cycles regardless of the stretch setting. By default, the stretch has value of 1. If the user needs faster accessing, then a stretch value of 0 should be selected.

| MD2  | MD1 | MD0 | Stretch value | MOVX duration              |

|------|-----|-----|---------------|----------------------------|

| 0    | 0   | 0   | 0             | 2 machine cycles           |

| 0    | 0   | 1   | 1             | 3 machine cycles (Default) |

| 0    | 1   | 0   | 2             | 4 machine cycles           |

| 0    | 1   | 1   | 3             | 5 machine cycles           |

| 01 V | 0   | 0   | 4             | 6 machine cycles           |

| 1    | 0   | 1   | 5             | 7 machine cycles           |

| 1/3  | 16  | 0   | 6             | 8 machine cycles           |

| 1 7  | 1   | 01  | 7             | 9 machine cycles           |

|      |     |     |               |                            |

### W77LE58/W77L058A

### nuvoTon

Port 1

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | P1.7 | P1.6 | P1.5 | P1.4 | P1.3 | P1.2 | P1.1 | P1.0 |

|      |      |      | 2.20 | 122  |      |      |      |      |

Mnemonic: P1

Address: 90h

P1.7-0: General purpose I/O port. Most instructions will read the port pins in case of a port read access, however in case of read-modify-write instructions, the port latch is read. Some pins also have alternate input or output functions. This alternate functions are described below:

| P1.0 : T2   | External I/O for Timer/Counter 2       |

|-------------|----------------------------------------|

| P1.1 : T2EX | Timer/Counter 2 Capture/Reload Trigger |

| P1.2 : RXD1 | Serial Port 1 Receive                  |

| P1.3 : TXD1 | Serial Port 1 Transmit                 |

| P1.4 : INT2 | External Interrupt 2                   |

| P1.5 : INT3 | External Interrupt 3                   |

| P1.6 : INT4 | External Interrupt 4                   |

| P1.7 : INT5 | External Interrupt 5                   |

#### **External Interrupt Flag**

| Bit: | 7   | 6   | 5   | 4   | 3     | 2    | 1    | 0 |

|------|-----|-----|-----|-----|-------|------|------|---|

|      | IE5 | IE4 | IE3 | IE2 | XT/RG | RGMD | RGSL | 0 |

Mnemonic: EXIF

Address: 91h

IE5: External Interrupt 5 flag. Set by hardware when a falling edge is detected on INT5.

IE4: External Interrupt 4 flag. Set by hardware when a rising edge is detected on INT4.

IE3: External Interrupt 3 flag. Set by hardware when a falling edge is detected on  $\overline{INT3}$ .

IE2: External Interrupt 2 flag. Set by hardware when a rising edge is detected on INT2.

- XT/RG: Crystal/RC Oscillator Select. Setting this bit selects crystal or external clock as system clock source. Clearing this bit selects the on-chip RC oscillator as clock source. XTUP(STATUS.4) must be set to 1 and XTOFF (PMR.3) must be cleared before this bit can be set. Attempts to set this bit without obeying these conditions will be ignored. This bit is set to 1 after a power- on reset and unchanged by other forms of reset.

- RGMD: RC Mode Status. This bit indicates the current clock source of microcontroller. When cleared, CPU is operating from the external crystal or oscillator. When set, CPU is operating from the onchip RC oscillator. This bit is cleared to 0 after a power-on reset and unchanged by other forms of reset.

- RGSL: RC Oscillator Select. This bit selects the clock source following a resume from Power Down Mode. Setting this bit allows device operating from RC oscillator when a resume from Power Down Mode. When this bit is cleared, the device will hold operation until the crystal oscillator has warmed-up following a resume from Power Down Mode. This bit is cleared to 0 after a power-on reset and unchanged by other forms of reset.

- SM2\_1: Multiple processors communication. Setting this bit to 1 enables the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2\_1 is set to 1, then RI\_1 will not be activated if the received 9th data bit (RB8\_1) is 0. In mode 1, if SM2\_1 = 1, then RI\_1 will not be activated if a valid stop bit was not received. In mode 0, the SM2\_1 bit controls the serial port 1 clock. If set to 0, then the serial port 1 runs at a divide by 12 clock of the oscillator. This gives compatibility with the standard 8052. When set to 1, the serial clock become divide by 4 of the oscillator clock. This results in faster synchronous serial communication.

- REN\_1: Receive enable: When set to 1 serial reception is enabled, otherwise reception is disabled.

- TB8\_1: This is the 9th bit to be transmitted in modes 2 and 3. This bit is set and cleared by software as desired.

- RB8\_1: In modes 2 and 3 this is the received 9th data bit. In mode 1, if SM2\_1 = 0, RB8\_1 is the stop bit that was received. In mode 0 it has no function.

- TI\_1: Transmit interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or at the beginning of the stop bit in all other modes during serial transmission. This bit must be cleared by software.

- RI\_1: Receive interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or halfway through the stop bits time in the other modes during serial reception. However the restrictions of SM2\_1 apply to this bit. This bit can be cleared only by software.

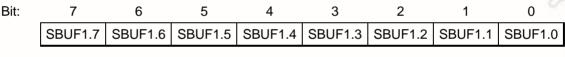

#### Serial Data Buffer 1

ROMMAP

Mnemonic: SBUF1

Address: C1h

SBUF1.7-0: Serial data of the serial port 1 is read from or written to this location. It actually consists of two separate 8-bit registers. One is the receive resister, and the other is the transmit buffer. Any read access gets data from the receive data buffer, while write accesses are to the transmit data buffer.

| Bit: | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|----|---|---|---|---|---|---|---|

|      | WS | 1 | - | - | - | - | - | - |

|      |    |   |   |   |   |   |   |   |

Mnemonic: ROMMAP

Address: C2h

WS: Wait State Signal Enable. Setting this bit enables the  $\overline{WAIT}$  signal on P4.0. The device will sample the wait state control signal  $\overline{WAIT}$  via P4.0 during MOVX instruction. This bit is time access protected.

#### **Power Management Register**

| Bit: | 7          | 6   | 5   | 4 | 3     | 2        | 1   | 0    |

|------|------------|-----|-----|---|-------|----------|-----|------|

|      | CD1        | CD0 | SWB | - | XTOFF | ALE-OFF  | -   | DME0 |

| Mne  | emonic: PN | ИR  |     |   |       | Address: | C4h |      |

CD1, CD0: Clock Divide Control. These bit selects the number of clocks required to generate one machine cycle. There are three modes including divide by 4, 64 or 1024. Switching between modes must first go back devide by 4 mode. For instance, to go from 64 to 1024

### W77LE58/W77L058A

# nuvoTon

|        | Bit:             | 7                                         | 6          | 5 5        | )          | 4           | 3           | 2          | 1           | 0          |

|--------|------------------|-------------------------------------------|------------|------------|------------|-------------|-------------|------------|-------------|------------|

|        |                  | RCAP2                                     | 7 RCAF     | P2L.6 RCA  | P2L.5 RC/  | AP2L.4 RC   | AP2L.3 R    | CAP2L.2    | RCAP2L.1    | RCAP2L.0   |

|        |                  | Mnemonic                                  | : RCAP2L   |            |            |             | A           | ddress: C  | CAh         |            |

| RCAP   |                  | egister is us<br>2L is also u<br>mode.    |            |            |            |             |             |            |             |            |

| Timer  | 2 Capture        | e MSB                                     |            |            |            |             |             |            |             |            |

|        | Bit:             | 7                                         | 6          | 5          | 4          |             | 3           | 2          | 20          | 0          |

|        |                  | RCAP2H.7                                  | RCAP2H     | .6 RCAP2   | H.5 RCAP   | 2H.4 RCA    | P2H.3 RC    | AP2H.2 R   | CAP2H.1     | RCAP2H.0   |

|        |                  | Mnemonic                                  | : RCAP2H   | 1          |            |             | A           | ddress: C  | CBh         |            |

| RCAP2  | RCAP:<br>auto-re | egister is us<br>2H is also<br>eload mode | used as th |            |            |             |             |            |             |            |

| Timer  | 2 200            | Bit:                                      | 7          | 6          | 5          | 4           | 3           | 2          | 1           | 0          |

|        |                  | DIL.                                      | 7<br>TL2.7 | 0<br>TL2.6 | 5<br>TL2.5 | 4<br>TL2.4  | 5<br>TL2.3  | Z<br>TL2.2 | TL2.1       | TL2.0      |

|        |                  | Mnemonic                                  |            | 122.0      | 1 2210     |             |             | ddress: C  |             | 122.0      |

| TL2:   | Timer 2          |                                           | . 1 L Z    |            |            |             | A           |            |             |            |

| Timer  | -                |                                           |            |            |            |             |             |            |             |            |

|        |                  | Bit:                                      | 7          | 6          | 5          | 4           | 3           | 2          | 1           | 0          |

|        |                  |                                           | TH2.7      | TH2.6      | TH2.5      | TH2.4       | TH2.3       | TH2.2      | TH2.1       | TH2.0      |

|        |                  | Mnemonic                                  | : TH2      |            |            |             | A           | ddress: C  | Dh          |            |

| TH2:   | Timer 2          | MSB                                       |            |            |            |             |             |            |             |            |

| Progra | am Status        | Word                                      |            |            |            |             |             |            |             |            |

|        |                  | Bit:                                      | 7          | 6          | 5          | 4           | 3           | 2          | 1           | 0          |

|        |                  |                                           | CY         | AC         | F0         | RS1         | RS0         | OV         | F1          | Р          |

|        |                  | Mnemonic                                  | : PSW      |            |            |             | A           | ddress: E  | D0h         |            |

| CY:    |                  | g: Set for a used as th                   |            |            |            |             | a carry be  | eing gene  | erated fror | n the ALU. |

| AC:    | Auxiliary        | carry: Set                                | when the   | previous   | operation  | resulted ir | n a carry f | rom the h  | nigh order  | nibble.    |

| F0:    | User flag        | g 0: Genera                               | al purpose | flag that  | can be se  | t or cleare | ed by the u | user.      |             |            |

|        |                  |                                           |            |            |            |             |             |            |             |            |

| Table 3. Instruction Timing for W77L058, continued | d |

|----------------------------------------------------|---|

|----------------------------------------------------|---|

| INSTRUCTION          | HEX<br>OP-CODE                       | BYTES | W77L058<br>MACHINE<br>CYCLES | W77L058<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | W77L058 VS<br>8032 SPEED<br>RATIO |

|----------------------|--------------------------------------|-------|------------------------------|----------------------------|-------------------------|-----------------------------------|

| ADDC A, R5           | 3D                                   | 1     | 1 9                          | 4                          | 12                      | 3                                 |

| ADDC A, R6           | 3E                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, R7           | 3F                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, @R0          | 36                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ADDC A, @R1          | 37                                   | 1     | 1                            | 4 9                        | 12                      | 3                                 |

| ADDC A, direct       | 35                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ADDC A, #data        | 34                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ACALL addr11         | 71, 91, B1,<br>11, 31, 51,<br>D1, F1 | 2     | 3                            | 12                         | 24                      | 2                                 |

| AJMP ADDR11          | 01, 21, 41,<br>61, 81, A1,<br>C1, E1 | 2     | 3                            | 12                         | 24                      | 2                                 |

| ANL A, R0            | 58                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R1            | 59                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R2            | 5A                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R3            | 5B                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R4            | 5C                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R5            | 5D                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R6            | 5E                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, R7            | 5F                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, @R0           | 56                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, @R1           | 57                                   | 1     | 1                            | 4                          | 12                      | 3                                 |

| ANL A, direct        | 55                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ANL A, #data         | 54                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ANL direct, A        | 52                                   | 2     | 2                            | 8                          | 12                      | 1.5                               |

| ANL direct, #data    | 53                                   | 3     | 3                            | 12                         | 24                      | 2                                 |

| ANL C, bit           | 82                                   | 2     | 2                            | 8                          | 24                      | 3                                 |

| ANL C, /bit          | B0                                   | 2     | 2                            | 8                          | 24                      | 3                                 |

| CJNE A, direct, rel  | B5                                   | 3     | 4                            | 16                         | 24                      | 1.5                               |

| CJNE A, #data, rel   | B4                                   | 3     | 4                            | 16                         | 24                      | 1.5                               |

| CJNE @R0, #data, rel | B6                                   | 3     | 4                            | 16                         | 24                      | 1.5                               |

| INSTRUCTION      | HEX<br>OP-CODE | BYTES | W77L058<br>MACHINE<br>CYCLES | W77L058<br>CLOCK<br>CYCLES | 8032<br>CLOCK<br>CYCLES | W77L058 VS<br>8032 SPEED<br>RATIO |

|------------------|----------------|-------|------------------------------|----------------------------|-------------------------|-----------------------------------|

| DJNZ R3, rel     | DB             | 2     | 3                            | 12                         | 24                      | 2                                 |

| DJNZ R4, rel     | DC             | 2     | 3                            | 12                         | 24                      | 2                                 |

| DJNZ R6, rel     | DE             | 2     | 3                            | 12                         | 24                      | 2                                 |

| DJNZ R7, rel     | DF             | 2     | 3                            | 12                         | 24                      | 2                                 |

| DJNZ direct, rel | D5             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| INC A            | 04             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R0           | 08             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R1           | 09             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R2           | 0A             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R3           | 0B             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R4           | 0C             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R6           | 0E             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC R7           | 0F             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC @R0          | 06             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC @R1          | 07             | 1     | 1                            | 4                          | 12                      | 3                                 |

| INC direct       | 05             | 2     | 2                            | 8                          | 12                      | 1.5                               |

| INC DPTR         | A3             | 1     | 2                            | 8                          | 24                      | 3                                 |

| JMP @A+DPTR      | 73             | 1     | 2                            | 8                          | 24                      | 3                                 |

| JZ rel           | 60             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JNZ rel          | 70             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JC rel           | 40             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JNC rel          | 50             | 2     | 3                            | 12                         | 24                      | 2                                 |

| JB bit, rel      | 20             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| JNB bit, rel     | 30             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| JBC bit, rel     | 10             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| LCALL addr16     | 12             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| LJMP addr16      | 02             | 3     | 4                            | 16                         | 24                      | 1.5                               |

| MUL AB           | A4             | 1     | 5                            | 20                         | 48                      | 2.4                               |

| MOV A, R0        | E8             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R1        | E9             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R2        | EA             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R3        | EB             | 1     | 1                            | 4                          | 12                      | 3                                 |

| MOV A, R4        | EC             | 01    | 1                            | 4                          | 12                      | 3                                 |

Table 3. Instruction Timing for W77L058, continued

Revision A7

#### **MOVX Instruction**

The W77L058, like the standard 8032, uses the MOVX instruction to access external Data Memory. This Data Memory includes both off-chip memory as well as memory mapped peripherals. While the results of the MOVX instruction are the same as in the standard 8032, the operation and the timing of the strobe signals have been modified in order to give the user much greater flexibility.

The MOVX instruction is of two types, the MOVX @Ri and MOVX @DPTR. In the MOVX @Ri, the address of the external data comes from two sources. The lower 8-bits of the address are stored in the Ri register of the selected working register bank. The upper 8-bits of the address come from the port 2 SFR. In the MOVX @DPTR type, the full 16-bit address is supplied by the Data Pointer.

Since the W77L058 has two Data Pointers, DPTR and DPTR1, the user has to select between the two by setting or clearing the DPS bit. The Data Pointer Select bit (DPS) is the LSB of the DPS SFR, which exists at location 86h. No other bits in this SFR have any effect, and they are set to 0. When DPS is 0, then DPTR is selected, and when set to 1, DPTR1 is selected. The user can switch between DPTR and DPTR1 by toggling the DPS bit. The quickest way to do this is by the INC instruction. The advantage of having two Data Pointers is most obvious while performing block move operations. The accompanying code shows how the use of two separate Data Pointers speeds up the execution time for code performing the same task.

#### Block Move with single Data Pointer:

; SH and SL are the high and low bytes of Source Address

; DH and DL are the high and low bytes of Destination Address

; CNT is the number of bytes to be moved

| , -   | · · · · · · · · · · · · · · · · · · · | Machine cy                                        | cles | of<br># | W77L058 |

|-------|---------------------------------------|---------------------------------------------------|------|---------|---------|

| MOV   | R2, #CNT                              | ; Load R2 with the count value                    |      | 2       |         |

| MOV   | R3, #SL                               | ; Save low byte of Source Address in R3           |      | 2       |         |

| MOV   | R4, #SH                               | ; Save high byte of Source address in R4          |      | 2       |         |

| MOV   | R5, #DL                               | ; Save low byte of Destination Address in R5      |      | 2       |         |

| MOV   | R6, #DH                               | ; Save high byte of Destination address in R6     |      | 2       |         |

| LOOP: |                                       |                                                   |      |         |         |

| MOV   | DPL, R3                               | ; Load DPL with low byte of Source address        |      | 2       |         |

| MOV   | DPH, R4                               | ; Load DPH with high byte of Source address       |      | 2       |         |

| MOVX  | A, @DPTR                              | ; Get byte from Source to Accumulator             |      | 2       |         |

| INC   | DPTR                                  | ; Increment Source Address to next byte           |      | 2       |         |

| MOV   | R3, DPL                               | ; Save low byte of Source address in R3           |      | 2       |         |

| MOV   | R4, DPH                               | ; Save high byte of Source Address in R4          |      | 2       |         |

| MOV   | DPL, R5                               | ; Load low byte of Destination Address in DPL     |      | 2       |         |

| MOV   | DPH, R6                               | ; Load high byte of Destination Address in DPH    |      | 2       |         |

| MOVX  | @DPTR, A                              | ; Write data to destination                       |      | 2       |         |

| INC   | DPTR                                  | ; Increment Destination Address                   |      | 2       |         |

| MOV   | DPL, R5                               | ; Save low byte of new destination address in R52 |      |         |         |

| MOV   | DPH, R6                               | ; Save high byte of new destination address in R6 |      | 2       |         |

| DJNZ  | R2, LOOP                              | ; Decrement count and do LOOP again if count <>   | 0    | 2       |         |

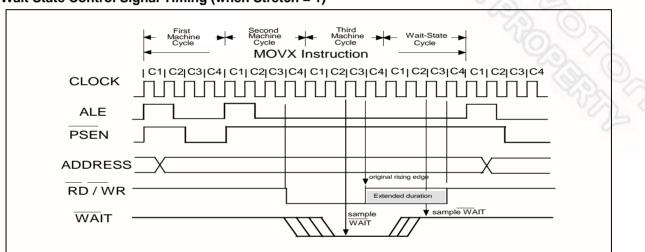

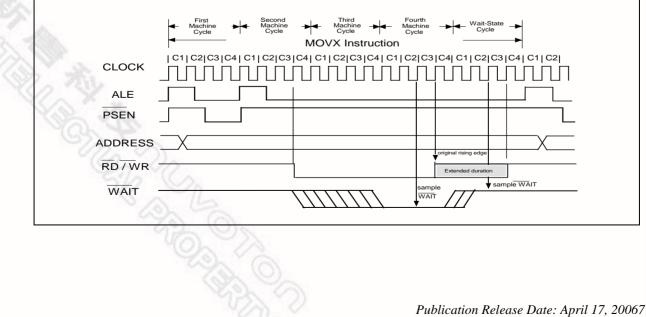

### 6.2.1 Wait State Control Signal

Either with the software using stretch value to change the required machine cycle of MOVX instruction, the W77L058 provides another hardware signal  $\overrightarrow{WAIT}$  to implement the wider duration of external data access timing. This wait state control signal is the alternate function of P4.0 such that it can only be invoked to 44-pin PLCC/QFP package type. The wait state control signal can be enabled by setting WS (ROMMAP.7) bit. When enabled, the setting of stretch value decides the minimum length of MOVX instruction cycle and the device will sample the  $\overrightarrow{WAIT}$  pin at each C3 state before the rising edge of read/write strobe signal during MOVX instruction. Once this signal being recongnized, one more machine cycle (wait state cycle) will be inserted into next cycle. The inserted wait state cycles are unlimited, so the MOVX instruction cycle will end in which the wait state control signal is deactivated. Using wait state control signal allows a dynamically access timing to a selected external peripheral. The WS bit is accessed by the Timed Access Protection procedure.

#### Wait State Control Signal Timing (when Stretch = 1)

Wait State Control Signal Timing (when Stretch = 2)

Revision A7

### 6.5 Reset State

Most of the SFRs and registers on the device will go to the same condition in the reset state. The Program Counter is forced to 0000h and is held there as long as the reset condition is applied. However, the reset state does not affect the on-chip RAM. The data in the RAM will be preserved during the reset. However, the stack pointer is reset to 07h, and therefore the stack contents will be lost. The RAM contents will be lost if the VDD falls below approximately 2V, as this is the minimum voltage level required for the RAM to operate normally. Therefore after a first time power on reset the RAM contents will be indeterminate. During a power fail condition, if the power falls below 2V, the RAM contents are lost.

After a reset most SFRs are cleared. Interrupts and Timers are disabled. The Watchdog timer is disabled if the reset source was a POR. The port SFRs have FFh written into them which puts the port pins in a high state. Port 0 floats as it does not have on-chip pull-ups.

|    | SFR NAME | RESET VALUE | SFR NAME | RESET VALUE |

|----|----------|-------------|----------|-------------|

|    | P0       | 1111111b    | IE       | 0000000b    |

|    | SP       | 00000111b   | SADDR    | 0000000b    |

|    | DPL      | 0000000b    | P3       | 1111111b    |

|    | DPH      | 0000000b    | IP       | x000000b    |

|    | DPL1     | 0000000b    | SADEN    | 0000000b    |

|    | DPH1     | 0000000b    | T2CON    | 0000000b    |

|    | DPS      | 0000000b    | T2MOD    | 00000x00b   |

|    | PCON     | 00xx0000b   | RCAP2L   | 0000000b    |

|    | TCON     | 0000000b    | RCAP2H   | 0000000b    |

|    | TMOD     | 0000000b    | TL2      | 0000000b    |

|    | TL0      | 0000000b    | TH2      | 0000000b    |

|    | TL1      | 0000000b    | ТА       | 11111111b   |

| 24 | TH0      | 0000000b    | PSW      | 0000000b    |

| 2  | TH1      | 0000000b    | WDCON    | 0x0x0xx0b   |

| C  | CKCON    | 0000001b    | ACC      | 0000000b    |

|    | P1       | 1111111b    | EIE      | xxx00000b   |

|    | SCON     | 0000000b    | В        | 0000000b    |

| 20 | SBUF     | xxxxxxxb    | EIP      | xxx00000b   |

| X  | P2       | 1111111b    | PC       | 0000000b    |

|    | SADDR1   | 0000000b    | SADEN1   | 0000000b    |

|    | SCON1    | 0000000b    | SBUF1    | xxxxxxxb    |

|    | ROMMAP   | 01xxx110b   | PMR      | 010xx0x0b   |

|    | EXIF     | 0000xxx0b   | STATUS   | 000x0000b   |

|    | P4       | xxxx1111b   |          |             |

#### Table 6. SFR Reset Value

The WDCON SFR bits are set/cleared in reset condition depending on the source of the reset.

Watchdog reset

External reset

Power on reset

### 7.1.6 Baud Rate Generator Mode

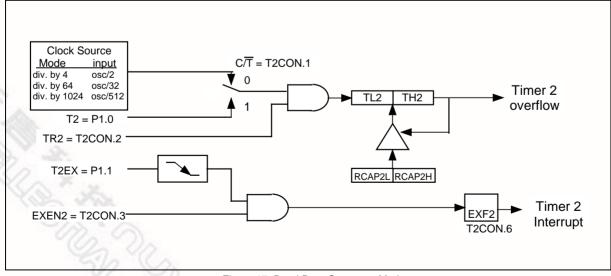

The baud rate generator mode is enabled by setting either the RCLK or TCLK bits in T2CON register. While in the baud rate generator mode, Timer/Counter 2 is a 16 bit counter with auto reload when the count rolls over from FFFFh. However, rolling over does not set the TF2 bit. If EXEN2 bit is set, then a negative transition of the T2EX pin will set EXF2 bit in the T2CON register and cause an interrupt request. T2OE bit must be cleared in this mode.

Figure 17. Baud Rate Generator Mode

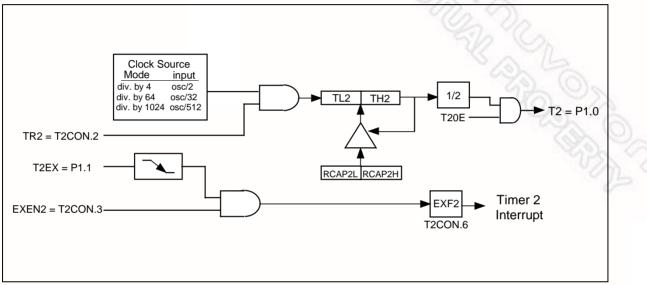

### 7.1.7 Programmable Clock-out

Timer 2 is equipped with a new clock-out feature which outputs a 50% duty cycle clock on P1.0. It can be invoked as a programmable clock generator. To configure Timer 2 with clock-out mode, software must initiate it by setting bit T2OE = 1, C/T2 = 0 and CP/RL = 0. Setting bit TR2 will start the timer. This mode is similar to the baud rate generator mode, it will not generate an interrupt while Timer 2 overflow. So it is possible to use Timer 2 as a baud rate generator and a clock generator at the same time. The clock-out frequency is determined by the following equation:

The Clock-out Frequency = Oscillator Frequency / [4 x (65536-RCAP2H, RCAP2L)]

Figure 18. Programmable Clock-Out Mode

### Watchdog Timer

The Watchdog timer is a free-running timer which can be programmed by the user to serve as a system monitor, a time-base generator or an event timer. It is basically a set of dividers that divide the system clock. The divider output is selectable and determines the time-out interval. When the time-out occurs a flag is set, which can cause an interrupt if enabled, and a system reset can also be caused if it is enabled. The interrupt will occur if the individual interrupt enable and the global enable are set. The interrupt and reset functions are independent of each other and may be used separately or together depending on the users software.

| WD1 | WD0 | WATCHDOG<br>INTERVAL | NUMBER OF<br>CLOCKS | TIME<br>@ 1.8432 MHZ | TIME<br>@ 10 MHZ | TIME<br>@ 25 MHZ |

|-----|-----|----------------------|---------------------|----------------------|------------------|------------------|

| 0   | 0   | 2 <sup>17</sup>      | 131072              | 71.11 mS             | 13.11 mS         | 5.24 mS          |

| 0   | 1   | 2 <sup>20</sup>      | 1048576             | 568.89 mS            | 104.86 mS        | 41.94 mS         |

| 1   | 0   | 2 <sup>23</sup>      | 8388608             | 4551.11 mS           | 838.86 mS        | 335.54 mS        |

| 1   | 1   | 2 <sup>26</sup>      | 67108864            | 36408.88 mS          | 6710.89 mS       | 2684.35 mS       |

#### Table 9. Time-out values for the Watchdog timer

The Watchdog timer will de disabled by a power-on/fail reset. The Watchdog timer reset does not disable the watchdog timer, but will restart it. In general, software should restart the timer to put it into a known state.

The control bits that support the Watchdog timer are discussed below.

#### 7.1.8 Watchdog Control

- WDIF: WDCON.3 Watchdog Timer Interrupt flag. This bit is set whenever the time-out occurs in the watchdog timer. If the Watchdog interrupt is enabled (EIE.4), then an interrupt will occur (if the global interrupt enable is set and other interrupt requirements are met). Software or any reset can clear this bit.

- WTRF: WDCON.2 Watchdog Timer Reset flag. This bit is set whenever a watchdog reset occurs. This bit is useful for determined the cause of a reset. Software must read it, and clear it manually. A Power-fail reset will clear this bit. If EWT = 0, then this bit will not be affected by the watchdog timer.

- EWT: WDCON.1 Enable Watchdog timer Reset. This bit when set to 1 will enable the Watchdog timer reset function. Setting this bit to 0 will disable the Watchdog timer reset function, but will leave the timer running.

- RWT: WDCON.0 Reset Watchdog Timer. This bit is used to clear the Watchdog timer and to restart it. This bit is self-clearing, so after the software writes 1 to it the hardware will automatically clear it. If the Watchdog timer reset is enabled, then the RWT has to be set by the user within 512 clocks of the time-out. If this is not done then a Watchdog timer reset will occur.

W77LE58/W77L058A

### nuvoTon

If the first bit detected after the falling edge of RxD pin, is not 0, then this indicates an invalid start bit, and the reception is immediately aborted. The serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the rest of the bits are also detected and shifted into the SBUF. After shifting in 9 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

1. RI must be 0 and

2. Either SM2 = 0, or the received stop bit = 1.

If these conditions are met, then the stop bit goes to RB8, the 8 data bits go into SBUF and RI is set. Otherwise the received frame may be lost. After the middle of the stop bit, the receiver goes back to looking for a 1-to-0 transition on the RxD pin.

#### MODE 3

This mode is similar to Mode 2 in all respects, except that the baud rate is programmable. The user must first initialize the Serial related SFR SCON before any communication can take place. This involves selection of the Mode and baud rate. The Timer 1 should also be initialized if modes 1 and 3 are used. In all four modes, transmission is started by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0 and REN = 1. This will generate a clock on the TxD pin and shift in 8 bits on the RxD pin. Reception is initiated in the other modes by the incoming start bit if REN = 1. The external device will start the communication by transmitting the start bit.

Figure 23. Serial Port Mode 3

### **10. SECURITY BITS**

During the on-chip ROM operation mode, the ROM can be programmed and verified repeatedly. Until the code inside the ROM is confirmed OK, the code can be protected. The protection of ROM and those operations on it are described below.

The W77L058 has a Security Register which can not be accessed in normal mode. These registers can only be accessed from the ROM operation mode. Those bits of the Security Registers can not be changed once they have been programmed from high to low. They can only be reset through erase-all operation. The Security Register is addressed in the ROM operation mode by address #0FFFFh.

| (option bits)<br>Reserved B3 B2 B1 B0 Security Bits<br>B0: Lock bit, logic 0: active<br>B1: MOVC inhibit,<br>logic 0: the MOVC instruction in external memory<br>cannot access the code in internal memory.<br>logic1 : no restriction.<br>B3: This bit must be H.<br>Default 1 for each bit.<br>Special Setting 3 | On-Chip<br>32KB ROM<br>Program Memory<br>Reserved<br>Security Register | 0000h<br>7FFFh | O A |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------|-----|

|                                                                                                                                                                                                                                                                                                                    |                                                                        |                |     |

#### B0: Lock bit

This bit is used to protect the customer's program code in the W77L058. It may be set after the programmer finishes the programming and verifies sequence. Once this bit is set to logic 0, both the ROM data and Special Setting Registers can not be accessed again.

#### **B1: MOVC Inhibit**

This bit is used to restrict the accessible region of the MOVC instruction. It can prevent the MOVC instruction in external program memory from reading the internal program code. When this bit is set to logic 0, a MOVC instruction in external program memory space will be able to access code only in the external memory, not in the internal memory. A MOVC instruction in internal program memory space will always be able to access the ROM data in both internal and external memory. If this bit is logic 1, there are no restrictions on the MOVC instruction.

| M2 | M1 | MO | MOVX Cycles      | t <sub>MCS</sub>     |

|----|----|----|------------------|----------------------|

| 0  | 0  | 0  | 2 machine cycles | 0                    |

| 0  | 0  | 1  | 3 machine cycles | 4 t <sub>CLCL</sub>  |

| 0  | 1  | 0  | 4 machine cycles | 8 t <sub>CLCL</sub>  |

| 0  | 1  | 1  | 5 machine cycles | 12 t <sub>CLCL</sub> |

| 1  | 0  | 0  | 6 machine cycles | 16 t <sub>CLCL</sub> |

| 1  | 0  | 1  | 7 machine cycles | 20 t <sub>CLCL</sub> |

| 1  | 1  | 0  | 8 machine cycles | 24 t <sub>CLCL</sub> |

| 1  | 1  | 1  | 9 machine cycles | 28 t <sub>CLCL</sub> |

#### **Explanation of Logic Symbols**

In order to maintain compatibility with the original 8051 family, this device specifies the same parameter for each device, using the same symbols. The explanation of the symbols is as follows.

| t | Time                    | А | Address         |

|---|-------------------------|---|-----------------|

| С | Clock                   | D | Input Data      |

| Н | Logic level high        | L | Logic level low |

| Ι | Instruction             | Р | PSEN            |

| Q | Output Data             | R | RD signal       |

| V | Valid                   | W | WR signal       |

| Х | No longer a valid state | Z | Tri-state       |

### W77LE58/W77L058A

## nuvoTon

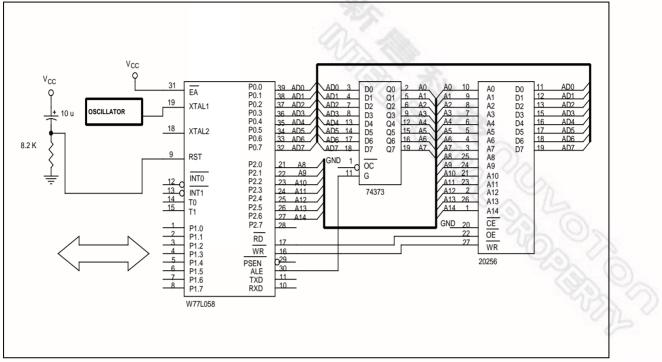

### **Expanded External Data Memory and Oscillator**

Figure B