Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | RX                                                                               |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                               |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 52                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 8K x 8                                                                           |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                      |

| Data Converters            | A/D 14x12b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | 64-LFQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f51305adfm-30 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification             | Module/Function                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA                        | Data transfer controller<br>(DTCa)               | <ul> <li>Transfer modes: Normal transfer, repeat transfer, and block transfer</li> <li>Activation sources: Interrupts</li> <li>Chain transfer function</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I/O ports                  | General I/O ports                                | 100-pin /80-pin /64-pin /48-pin<br>• I/O: 88/68/52/38<br>• Input: 1/1/1/1<br>• Pull-up resistors: 88/68/52/38<br>• Open-drain outputs: 67/47/35/26<br>• 5-V tolerance: 4/4/2/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Event link control         | ler (ELC)                                        | <ul> <li>Event signals of 47 types can be directly connected to the module</li> <li>Operations of timer modules are selectable at event input</li> <li>Capable of event link operation for port B</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Multi-function pin         | controller (MPC)                                 | Capable of selecting the input/output function from multiple pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Timers                     | Multi-function timer pulse<br>unit 2 (MTU2a)     | <ul> <li>(16 bits × 6 channels) × 1 unit</li> <li>Up to 16 pulse-input/output lines and three pulse-input lines are available based on the six 16-bit timer channels</li> <li>Select from among eight or seven counter-input clock signals for each channel (PCLK/1, PCLK/4, PCLK/16, PCLK/64, PCLK/256, PCLK/1024, MTCLKA, MTCLKB, MTCLKC, MTCLKD) other than channel 5, for which only four signals are available.</li> <li>Input capture function</li> <li>21 output compare/input capture registers</li> <li>Pulse output mode</li> <li>Complementary PWM output mode</li> <li>Reset synchronous PWM mode</li> <li>Phase-counting mode</li> <li>Capable of generating conversion start triggers for the A/D converter</li> </ul>                                                                           |

|                            | Port output enable 2 (POE2a)                     | Controls the high-impedance state of the MTU's waveform output pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                            | Compare match timer<br>(CMT)                     | <ul> <li>(16 bits × 2 channels) × 1 unit</li> <li>Select from among four clock signals (PCLK/8, PCLK/32, PCLK/128, PCLK/512)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | Independent watchdog<br>timer (IWDTa)            | <ul> <li>14 bits × 1 channel</li> <li>Count clock: Dedicated low-speed on-chip oscillator for the IWDT<br/>Frequency divided by 1, 16, 32, 64, 128, or 256</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                            | Realtime clock (RTCc)* <sup>1</sup>              | <ul> <li>Clock source: Sub-clock</li> <li>Calendar count mode or binary count mode selectable</li> <li>Interrupts: Alarm interrupt, periodic interrupt, and carry interrupt</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            | Low power timer (LPT)                            | <ul> <li>16 bits × 1 channel</li> <li>Clock source: Sub-clock, Dedicated low-speed on-chip oscillator for the IWDT Frequency divided by 2, 4, 8, 16, or 32</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                            | 8-bit timer (TMR)                                | <ul> <li>(8 bits × 2 channels) × 2 units</li> <li>Seven internal clocks (PCLK/1, PCLK/2, PCLK/8, PCLK/32, PCLK/64, PCLK/1024, and PCLK/8192) and an external clock can be selected</li> <li>Pulse output and PWM output with any duty cycle are available</li> <li>Two channels can be cascaded and used as a 16-bit timer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Communication<br>functions | Serial communications<br>interfaces (SClg, SClh) | <ul> <li>7 channels (channel 0, 1, 5, 6, 8, 9: SClg, channel 12: SClh)</li> <li>SClg<br/>Serial communications modes: Asynchronous, clock synchronous, and smart-card interface<br/>On-chip baud rate generator allows selection of the desired bit rate<br/>Choice of LSB-first or MSB-first transfer<br/>Average transfer rate clock can be input from TMR timers for SCl5, SCl6, and SCl12<br/>Start-bit detection: Level or edge detection is selectable.<br/>Simple I<sup>2</sup>C<br/>Simple SPI<br/>9-bit transfer mode<br/>Bit rate modulation<br/>Event linking by the ELC (only on channel 5)</li> <li>SClh (The following functions are added to SClg)<br/>Supports the serial communications protocol, which contains the start frame and information frame<br/>Supports the LIN format</li> </ul> |

|                            | I <sup>2</sup> C bus interface (RIICa)           | <ul> <li>1 channel</li> <li>Communications formats: I<sup>2</sup>C bus format/SMBus format</li> <li>Master mode or slave mode selectable</li> <li>Supports fast mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### Table 1.1Outline of Specifications (2/3)

### 1.4 Pin Functions

Table 1.4 lists the pin functions.

### Table 1.4Pin Functions (1/3)

| Classifications                      | Pin Name                              | I/O    | Description                                                                                                                                                |

|--------------------------------------|---------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply                         | VCC                                   | Input  | Power supply pin. Connect it to the system power supply.                                                                                                   |

|                                      | VCL                                   | _      | Connect this pin to the VSS pin via the 4.7 $\mu F$ smoothing capacitor used to stabilize the internal power supply. Place the capacitor close to the pin. |

|                                      | VSS                                   | Input  | Ground pin. Connect it to the system power supply (0 V).                                                                                                   |

| Clock                                | XTAL                                  | Output | Pins for connecting a crystal. An external clock can be input through the                                                                                  |

|                                      | EXTAL                                 | Input  | EXTAL pin.                                                                                                                                                 |

|                                      | XCIN                                  | Input  | Input/output pins for the sub-clock oscillator. Connect a crystal between                                                                                  |

|                                      | XCOUT                                 | Output | XCIN and XCOUT.                                                                                                                                            |

|                                      | CLKOUT                                | Output | Clock output pin.                                                                                                                                          |

| Operating mode control               | MD                                    | Input  | Pin for setting the operating mode. The signal levels on this pin must not be changed during operation.                                                    |

| System control                       | RES#                                  | Input  | Reset pin. This MCU enters the reset state when this signal goes low.                                                                                      |

| CAC                                  | CACREF                                | Input  | Input pin for the clock frequency accuracy measurement circuit.                                                                                            |

| On-chip<br>emulator                  | FINED                                 | I/O    | FINE interface pin.                                                                                                                                        |

| Interrupts                           | NMI                                   | Input  | Non-maskable interrupt request pin.                                                                                                                        |

|                                      | IRQ0 to IRQ7                          | Input  | Interrupt request pins.                                                                                                                                    |

| Multi-function<br>timer pulse unit 2 | MTIOC0A, MTIOC0B,<br>MTIOC0C, MTIOC0D | I/O    | The TGRA0 to TGRD0 input capture input/output compare output/PWM output pins.                                                                              |

|                                      | MTIOC1A, MTIOC1B                      | I/O    | The TGRA1 and TGRB1 input capture input/output compare output/PWM output pins.                                                                             |

|                                      | MTIOC2A, MTIOC2B                      | I/O    | The TGRA2 and TGRB2 input capture input/output compare output/PWM output pins.                                                                             |

|                                      | MTIOC3A, MTIOC3B,<br>MTIOC3C, MTIOC3D | I/O    | The TGRA3 to TGRD3 input capture input/output compare output/PWM output pins.                                                                              |

|                                      | MTIOC4A, MTIOC4B,<br>MTIOC4C, MTIOC4D | I/O    | The TGRA4 to TGRD4 input capture input/output compare output/PWM output pins.                                                                              |

|                                      | MTIC5U, MTIC5V, MTIC5W                | Input  | The TGRU5, TGRV5, and TGRW5 input capture input/external pulse input pins.                                                                                 |

|                                      | MTCLKA, MTCLKB,<br>MTCLKC, MTCLKD     | Input  | Input pins for the external clock.                                                                                                                         |

| Port output<br>enable 2              | POE0# to POE3#, POE8#                 | Input  | Input pins for request signals to place the MTU pins in the high impedance state.                                                                          |

| Realtime clock                       | RTCOUT                                | Output | Output pin for the 1-Hz/64-Hz clock.                                                                                                                       |

| 8-bit timer                          | TMO0 to TMO3                          | Output | Compare match output pins.                                                                                                                                 |

|                                      | TMCI0 to TMCI3                        | Input  | Input pins for the external clock to be input to the counter.                                                                                              |

|                                      | TMRI0 to TMRI3                        | Input  | Counter reset input pins.                                                                                                                                  |

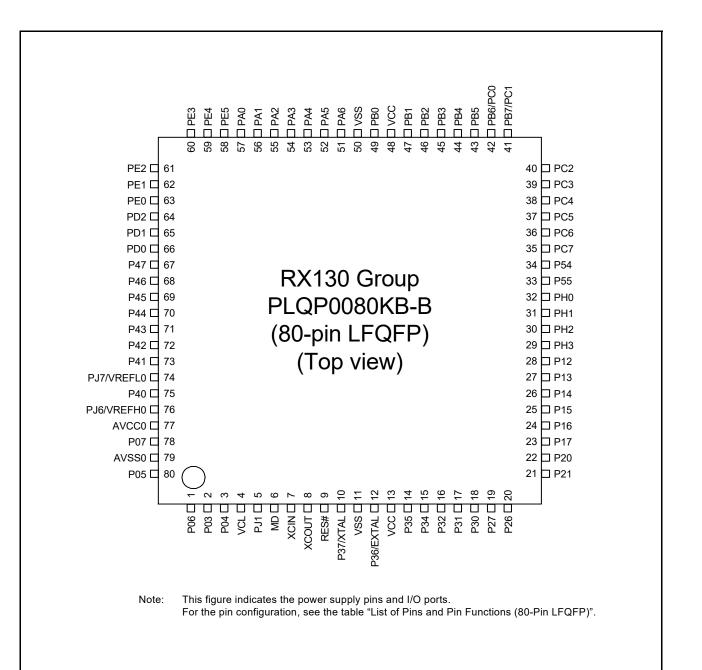

### Figure 1.4 Pin Assignments of the 80-Pin LFQFP

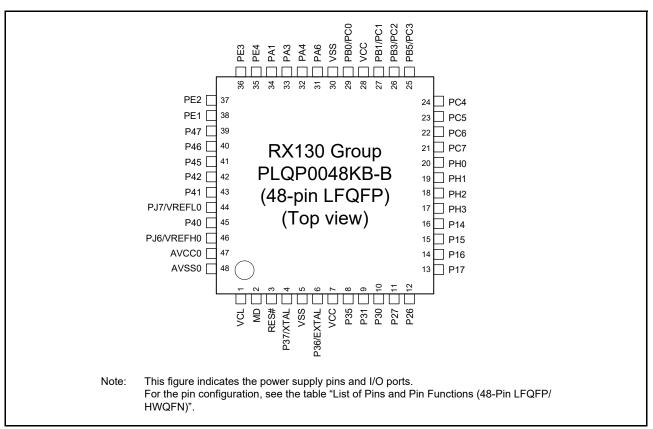

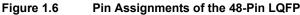

Figure 1.7 Pin Assignments of the 48-Pin HWQFN

RENESAS

# 2.1 General-Purpose Registers (R0 to R15)

This CPU has 16 general-purpose registers (R0 to R15). R0 to R15 can be used as data registers or address registers. R0, a general-purpose register, also functions as the stack pointer (SP). The stack pointer is switched to operate as the interrupt stack pointer (ISP) or user stack pointer (USP) by the value of the stack pointer select bit (U) in the processor status word (PSW).

## 2.2 Control Registers

### (1) Interrupt Stack Pointer (ISP)/User Stack Pointer (USP)

The stack pointer (SP) can be either of two types, the interrupt stack pointer (ISP) or the user stack pointer (USP). Whether the stack pointer operates as the ISP or USP depends on the value of the stack pointer select bit (U) in the processor status word (PSW).

Set the ISP or USP to a multiple of 4, as this reduces the numbers of cycles required to execute interrupt sequences and instructions entailing stack manipulation.

### (2) Interrupt Table Register (INTB)

The interrupt table register (INTB) specifies the address where the relocatable vector table starts.

### (3) Program Counter (PC)

The program counter (PC) indicates the address of the instruction being executed.

### (4) Processor Status Word (PSW)

The processor status word (PSW) indicates the results of instruction execution or the state of the CPU.

### (5) Backup PC (BPC)

The backup PC (BPC) is provided to speed up response to interrupts. After a fast interrupt has been generated, the contents of the program counter (PC) are saved in the BPC register.

### (6) Backup PSW (BPSW)

The backup PSW (BPSW) is provided to speed up response to interrupts.

After a fast interrupt has been generated, the contents of the processor status word (PSW) are saved in the BPSW. The allocation of bits in the BPSW corresponds to that in the PSW.

### (7) Fast Interrupt Vector Register (FINTV)

The fast interrupt vector register (FINTV) is provided to speed up response to interrupts. The FINTV register specifies a branch destination address when a fast interrupt has been generated.

# 2.3 Register Associated with DSP Instructions

### (1) Accumulator (ACC)

The accumulator (ACC) is a 64-bit register used for DSP instructions. The accumulator is also used for the multiply and multiply-and-accumulate instructions; EMUL, EMULU, MUL, and RMPA, in which case the prior value in the accumulator is modified by execution of the instruction.

Use the MVTACHI and MVTACLO instructions for writing to the accumulator. The MVTACHI and MVTACLO instructions write data to the higher-order 32 bits (bits 63 to 32) and the lower-order 32 bits (bits 31 to 0), respectively. Use the MVFACHI and MVFACMI instructions for reading data from the accumulator. The MVFACHI and MVFACMI instructions read data from the higher-order 32 bits (bits 63 to 32) and the middle 32 bits (bits 47 to 16), respectively.

| Address     | Module<br>Symbol | Register Name                     | Register Symbol | Number<br>of Bits | Access<br>Size | Number of Access Cycles |

|-------------|------------------|-----------------------------------|-----------------|-------------------|----------------|-------------------------|

| 0008 C065h  | PORT5            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C06Ah  | PORTA            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C06Bh  | PORTB            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C06Ch  | PORTC            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C06Dh  | PORTD            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C06Eh  | PORTE            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C071h  | PORTH            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C072h  | PORTJ            | Port Mode Register                | PMR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C082h  | PORT1            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C083h  | PORT1            | Open Drain Control Register 1     | ODR1            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C084h  | PORT2            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C085h  | PORT2            | Open Drain Control Register 1     | ODR1            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C086h  | PORT3            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C087h  | PORT3            | Open Drain Control Register 1     | ODR1            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C094h  | PORTA            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C095h  | PORTA            | Open Drain Control Register 1     | ODR1            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C096h  | PORTB            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C097h  | PORTB            | Open Drain Control Register 1     | ODR1            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C098h   | PORTC            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C099h  | PORTC            | Open Drain Control Register 1     | ODR1            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C09Ah   | PORTD            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C09Ch  | PORTE            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0A4h   | PORTJ            | Open Drain Control Register 0     | ODR0            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0C0h  | PORT0            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0C1h  | PORT1            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0C2h  | PORT2            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0C3h   | PORT3            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0C4h  | PORT4            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0C5h   | PORT5            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0CAh  | PORTA            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0CBh  | PORTB            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0CCh   | PORTC            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0CDh  | PORTD            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0CEh   | PORTE            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0D1h  | PORTH            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0D2h  | PORTJ            | Pull-Up Control Register          | PCR             | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0E1h  | PORT1            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0E2h   | PORT2            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0E3h   | PORT3            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0E5h   | PORT5            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0EAh   | PORTA            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0EBh  | PORTB            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0ECh  | PORTC            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C0EDh   | PORTD            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0EEh  | PORTE            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0F1h  | PORTH            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C0F2h  | PORTJ            | Drive Capacity Control Register   | DSCR            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C11Fh  | MPC              | Write-Protect Register            | PWPR            | 8                 | 8              | 2 or 3 PCLKB            |

| 0008 C120h  | PORT             | Port Switching Register B         | PSRB            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C12011  | PORT             | Port Switching Register A         | PSRA            | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C12 III | MPC              |                                   | P03PFS          | 8                 | 8              | 2 or 3 PCLKB            |

| 008 C143h   | MPC              | P03 Pin Function Control Register | PU3PFS          | 0                 | 0              | 2 or 3 PCLKB            |

### Table 4.1 List of I/O Registers (Address Order) (13 / 18)

MPC

P05 Pin Function Control Register

0008 C145h

P05PFS

8

8

2 or 3 PCLKB

#### [Products with 128 Kbytes of flash memory or less (except for 100-pin packages)] Table 5.7 DC Characteristics (5)

Conditions: 1.8 V ≤ VCC = AVCC0 < 2.0 V, 2.0 V ≤ VCC ≤ 5.5 V, 2.0 V ≤ AVCC0 ≤ 5.5 V, VSS = AVSS0 = 0 V, Ta = -40 to +105°C

|           |                    | I                 | tem                                          |              | Symbol          | Тур. | Max. | Unit | Test<br>Conditions |

|-----------|--------------------|-------------------|----------------------------------------------|--------------|-----------------|------|------|------|--------------------|

| Supply    | High-speed         | Normal            | No peripheral                                | ICLK = 32MHz | I <sub>CC</sub> | 3.1  | —    | mA   |                    |

| current*1 | operating<br>mode  | operating<br>mode | operation* <sup>2</sup>                      | ICLK = 16MHz |                 | 2.1  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 8MHz  |                 | 1.6  | —    |      |                    |

|           |                    |                   | All peripheral                               | ICLK = 32MHz |                 | 10.0 | —    |      |                    |

|           |                    |                   | operation: Normal* <sup>3</sup>              | ICLK = 16MHz |                 | 5.7  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 8MHz  |                 | 3.5  | _    |      |                    |

|           |                    |                   | All peripheral operation: Max.* <sup>3</sup> | ICLK = 32MHz |                 | —    | 17.5 |      |                    |

|           |                    | Sleep mode        | No peripheral                                | ICLK = 32MHz |                 | 1.6  | —    |      |                    |

|           |                    |                   | operation* <sup>2</sup>                      | ICLK = 16MHz |                 | 1.2  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 8MHz  |                 | 1.1  | —    |      |                    |

|           |                    |                   | All peripheral                               | ICLK = 32MHz |                 | 5.3  | —    |      |                    |

|           |                    |                   | operation: Normal* <sup>3</sup>              | ICLK = 16MHz |                 | 3.2  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 8MHz  |                 | 2.0  | —    |      |                    |

|           |                    | Deep sleep        | No peripheral                                | ICLK = 32MHz |                 | 1.0  | —    |      |                    |

|           |                    | mode              | operation* <sup>2</sup>                      | ICLK = 16MHz |                 | 0.9  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 8MHz  |                 | 0.8  | —    |      |                    |

|           |                    |                   | All peripheral                               | ICLK = 32MHz |                 | 4.2  | —    |      |                    |

|           |                    |                   | operation: Normal* <sup>3</sup>              | ICLK = 16MHz |                 | 2.5  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 8MHz  |                 | 1.7  | —    |      |                    |

|           |                    | Increase duri     | ng flash rewrite* <sup>5</sup>               | •            |                 | 2.5  | —    |      |                    |

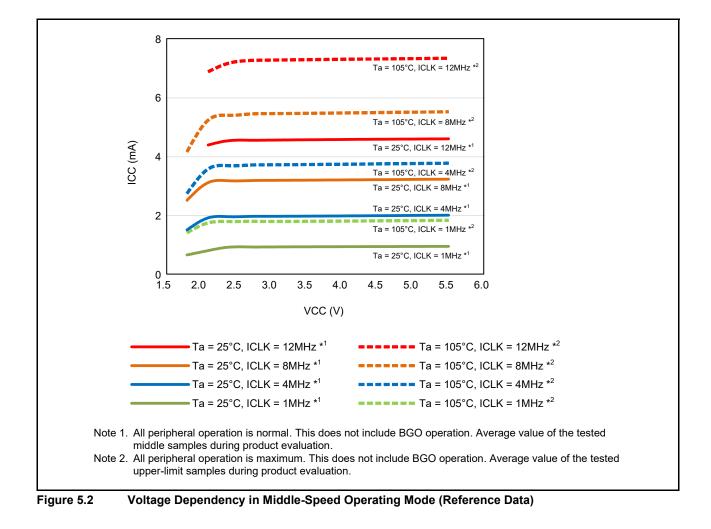

|           | Middle-speed       | Normal            | No peripheral                                | ICLK = 12MHz | I <sub>CC</sub> | 1.9  | —    | mA   |                    |

|           | operating<br>modes | operating<br>mode | operation* <sup>6</sup>                      | ICLK = 8MHz  |                 | 1.2  | —    |      |                    |

|           | modee              | mouo              |                                              | ICLK = 4MHz  |                 | 0.6  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 1MHz  |                 | 0.3  | —    |      |                    |

|           |                    |                   | All peripheral                               | ICLK = 12MHz |                 | 4.6  | —    |      |                    |

|           |                    |                   | operation: Normal* <sup>7</sup>              | ICLK = 8MHz  |                 | 3.2  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 4MHz  |                 | 2.0  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 1MHz  |                 | 0.9  | —    |      |                    |

|           |                    |                   | All peripheral operation: Max.* <sup>7</sup> | ICLK = 12MHz | -               | _    | 8.2  |      |                    |

|           |                    | Sleep mode        | No peripheral                                | ICLK = 12MHz | I <sub>CC</sub> | 1.2  | —    | mA   |                    |

|           |                    |                   | operation* <sup>6</sup>                      | ICLK = 8MHz  | 1               | 0.8  | _    |      |                    |

|           |                    |                   |                                              | ICLK = 4MHz  | 1               | 0.3  | _    |      |                    |

|           |                    |                   |                                              | ICLK = 1MHz  | 1               | 0.2  | —    |      |                    |

|           |                    |                   | All peripheral                               | ICLK = 12MHz | 1               | 2.7  | —    |      |                    |

|           |                    |                   | operation: Normal* <sup>7</sup>              | ICLK = 8MHz  | 1               | 1.9  | —    |      |                    |

|           |                    |                   |                                              | ICLK = 4MHz  | 1               | 1.2  | —    | 1    |                    |

|           |                    |                   |                                              | ICLK = 1MHz  | 1               | 0.7  | _    |      |                    |

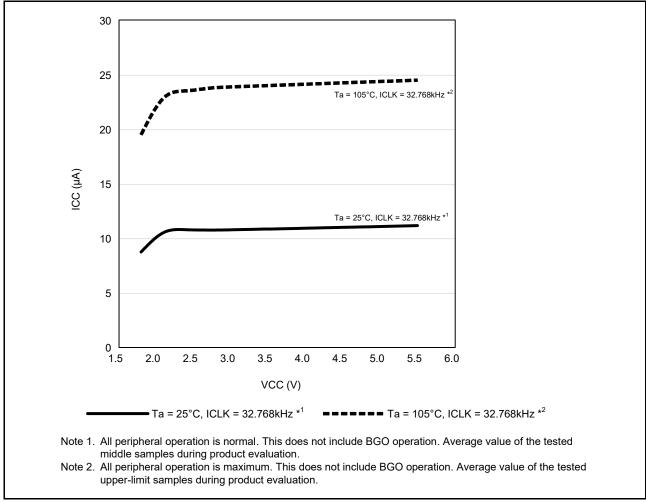

Figure 5.3 Voltage Dependency in Low-Speed Operating Mode (Reference Data)

### [Products with 128 Kbytes of flash memory or less (except for 100-pin packages)]

#### Table 5.9DC Characteristics (6)

Conditions:  $1.8 V \le VCC = AVCC0 < 2.0 V$ ,  $2.0 V \le VCC \le 5.5 V$ ,  $2.0 V \le AVCC0 \le 5.5 V$ , VSS = AVSS0 = 0 V, Ta = -40 to  $+105^{\circ}C$

|           | ltem                                                  |                        | Symbol          | Typ.* <sup>3</sup> | Max.  | Unit                                                           | Test Conditions                              |

|-----------|-------------------------------------------------------|------------------------|-----------------|--------------------|-------|----------------------------------------------------------------|----------------------------------------------|

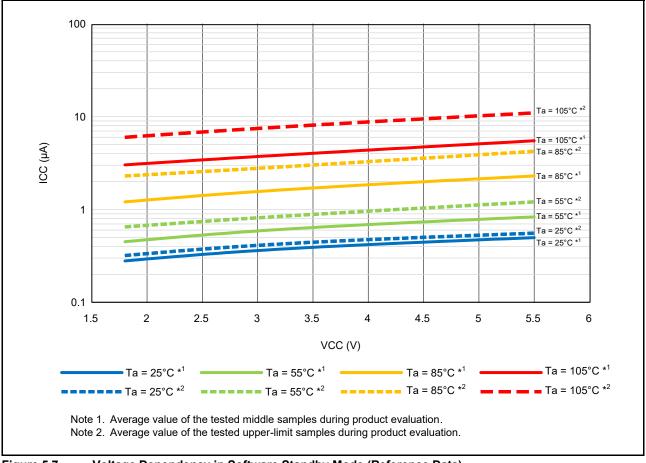

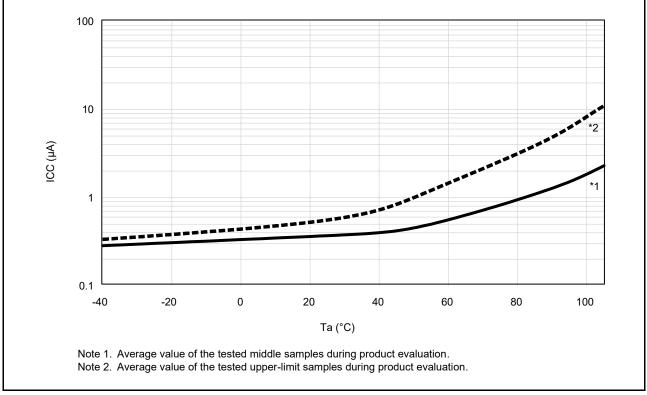

| Supply    | Software standby                                      | T <sub>a</sub> = 25°C  | I <sub>CC</sub> | 0.37               | 0.71  | μA                                                             |                                              |

| current*1 | mode*2                                                | T <sub>a</sub> = 55°C  |                 | 0.50               | 1.70  |                                                                |                                              |

|           |                                                       | T <sub>a</sub> = 85°C  |                 | 1.20               | 8.00  |                                                                |                                              |

|           |                                                       | T <sub>a</sub> = 105°C |                 | 2.30               | 19.60 |                                                                |                                              |

|           | Increment for RTC operation                           |                        |                 | 0.40               | _     |                                                                | RCR3.RTCDV[2:0] set to low drive capacity    |

|           |                                                       |                        |                 | 1.21               | _     |                                                                | RCR3.RTCDV[2:0] set to normal drive capacity |

|           | Increment for low-poperation                          | -                      | 0.37            | _                  |       | LPTCR1.LPCNTCKSEL set to IWDT-<br>dedicated on-chip oscillator |                                              |

|           | Increment for Independent<br>Watchdog Timer operation |                        |                 | 0.37               | _     |                                                                |                                              |

Note 1. Supply current values are with all output pins unloaded and all input pull-up MOSs in the off state.

Note 2. The IWDT, LVD, and CMPB are stopped.

Note 3. VCC = 3.3 V.

Note 4. Includes the oscillation circuit.

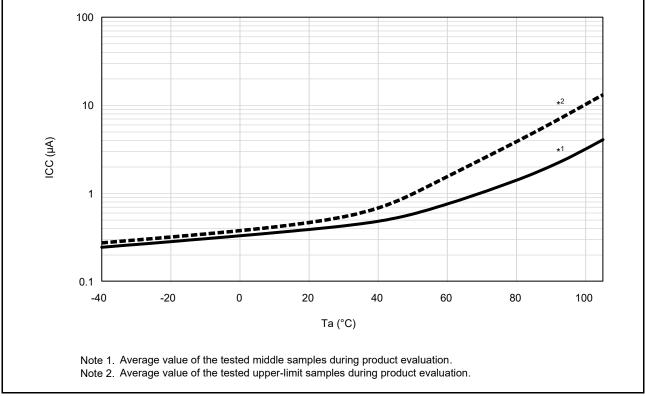

Voltage Dependency in Software Standby Mode (Reference Data)

Figure 5.8 Temperature Dependency in Software Standby Mode (Reference Data)

Figure 5.10 Temperature Dependency in Software Standby Mode (Reference Data)

### Table 5.11 DC Characteristics (7)

Conditions: 1.8 V ≤ VCC = AVCC0 < 2.0 V, 2.0 V ≤ VCC ≤ 5.5 V, 2.0 V ≤ AVCC0 ≤ 5.5 V, VSS = AVSS0 = 0 V

| Item                                  | Symbol | Тур. | Max. | Unit | Test Conditions |

|---------------------------------------|--------|------|------|------|-----------------|

| Permissible total power consumption*1 | Pd     | -    | 300  | mW   | D version       |

|                                       |        |      | 105  |      | G version       |

Note: Please contact a Renesas Electronics sales office for information on the derating of the G-version product. Derating is the systematic reduction of load to improve reliability.

Note 1. Total power dissipated by the entire chip (including output currents)

### Table 5.19 Output Values of Voltage (1)

Conditions:  $1.8 V \le VCC = AVCC0 < 2.0 V$ ,  $2.0 V \le VCC < 2.7 V$ ,  $2.0 V \le AVCC0 < 2.7 V$ , VSS = AVSS0 = 0 V, Ta = -40 to  $+105^{\circ}C$

| Item                                     |                  |                      |                                        | Symbol          | Min.        | Max. | Unit                     | Test Conditions           |

|------------------------------------------|------------------|----------------------|----------------------------------------|-----------------|-------------|------|--------------------------|---------------------------|

| Output low                               | All output ports | Normal output mode   |                                        | V <sub>OL</sub> | —           | 0.8  | V                        | I <sub>OL</sub> = 0.5 mA  |

| (except for RIIC) High-drive output mode |                  | de                   |                                        | —               | 0.8         |      | I <sub>OL</sub> = 1.0 mA |                           |

| Output high                              | All output ports | Normal output mode   | P03 to P07,<br>P40 to P47,<br>PJ6, PJ7 | V <sub>OH</sub> | AVCC0 - 0.5 | _    | V                        | I <sub>OH</sub> = -0.5 mA |

|                                          |                  |                      | Ports other than above                 |                 | VCC - 0.5   | _    |                          |                           |

|                                          |                  | High-drive output mo | de                                     |                 | VCC - 0.5   |      |                          | I <sub>OH</sub> = -1.0 mA |

### Table 5.20 Output Values of Voltage (2)

Conditions: 2.7 V ≤ VCC < 4.0 V, 2.7 V ≤ AVCC0 < 4.0 V, VSS = AVSS0 = 0 V,  $T_a = -40$  to +105°C

|             | Item                                                                       |                      |                                        | Symbol          | Min.        | Max. | Unit | Test Conditions           |  |

|-------------|----------------------------------------------------------------------------|----------------------|----------------------------------------|-----------------|-------------|------|------|---------------------------|--|

| Output low  |                                                                            |                      |                                        | V <sub>OL</sub> | —           | 0.8  | V    | I <sub>OL</sub> = 1.0 mA  |  |

|             | (except for RIIC)                                                          | High-drive output mo | de                                     |                 | —           | 0.8  |      | I <sub>OL</sub> = 2.0 mA  |  |

|             | RIIC pins<br>(Normal output mode)<br>Fast mode<br>(High-drive output mode) |                      | )                                      |                 | —           | 0.4  |      | I <sub>OL</sub> = 3.0 mA  |  |

|             |                                                                            |                      | ode)                                   |                 | _           | 0.4  |      | I <sub>OL</sub> = 6.0 mA  |  |

| Output high | All output ports                                                           |                      | P03 to P07,<br>P40 to P47,<br>PJ6, PJ7 | V <sub>OH</sub> | AVCC0 - 0.8 | _    | V    | I <sub>OH</sub> = -1.0 mA |  |

|             |                                                                            |                      | Ports other than above                 |                 | VCC - 0.8   |      |      |                           |  |

|             |                                                                            | High-drive output mo | de                                     |                 | VCC - 0.8   | _    |      | I <sub>OH</sub> = -2.0 mA |  |

#### Table 5.21Output Values of Voltage (3)

Conditions:  $4.0 \text{ V} \le \text{VCC} \le 5.5 \text{ V}, 4.0 \text{ V} \le \text{AVCC0} \le 5.5 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{ T}_{a} = -40 \text{ to } +105^{\circ}\text{C}$

|             | ltem                                            |                                       |                                        | Symbol          | Min.        | Max. | Unit | Test Conditions           |

|-------------|-------------------------------------------------|---------------------------------------|----------------------------------------|-----------------|-------------|------|------|---------------------------|

| Output low  | All output ports                                |                                       |                                        | V <sub>OL</sub> | —           | 0.8  | V    | I <sub>OL</sub> = 2.0 mA  |

|             | (except for RIIC)                               | High-drive output mo                  | de                                     |                 | _           | 0.8  |      | I <sub>OL</sub> = 4.0 mA  |

|             | RIIC pins Standard mode<br>(Normal output mode) |                                       |                                        |                 | —           | 0.4  |      | I <sub>OL</sub> = 3.0 mA  |

|             |                                                 | Fast mode<br>(High-drive output mode) |                                        |                 | _           | 0.6  |      | I <sub>OL</sub> = 6.0 mA  |

| Output high | All output ports                                | Normal output mode                    | P03 to P07,<br>P40 to P47,<br>PJ6, PJ7 | V <sub>OH</sub> | AVCC0 - 0.8 | _    | V    | I <sub>OH</sub> = -2.0 mA |

|             |                                                 |                                       | Ports other than above                 |                 | VCC - 0.8   | _    |      |                           |

|             |                                                 | High-drive output mo                  | de                                     | 1               | VCC - 0.8   | —    |      | I <sub>OH</sub> = -4.0 mA |

### Table 5.31 Operating Mode Transition Time

Conditions: 1.8 V ≤ VCC = AVCC0 < 2.0 V, 2.0 V ≤ VCC ≤ 5.5 V, 2.0 V ≤ AVCC0 ≤ 5.5 V, VSS = AVSS0 = 0 V, Ta = -40 to +105°C

| Mode before Transition                                 | Mode after Transition                                     | ICLK Frequency | Tra  | Unit |      |       |

|--------------------------------------------------------|-----------------------------------------------------------|----------------|------|------|------|-------|

| Mode before transmon                                   |                                                           | ICLK Flequency | Min. | Тур. | Max. | Offic |

| High-speed operating mode                              | Middle-speed operating modes                              | 8 MHz          | —    | 10   | —    | μs    |

| Middle-speed operating modes                           | High-speed operating mode                                 | 8 MHz          | —    | 37.5 | —    | μs    |

| Low-speed operating mode                               | Middle-speed operating mode,<br>high-speed operating mode | 32.768 kHz     | —    | 215  | —    | μs    |

| Middle-speed operating mode, high-speed operating mode | Low-speed operating mode                                  | 32.768 kHz     | —    | 185  | —    | μs    |

Note: Values when the frequencies of PCLKB, PCLKD, and FCLK are not divided.

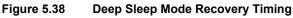

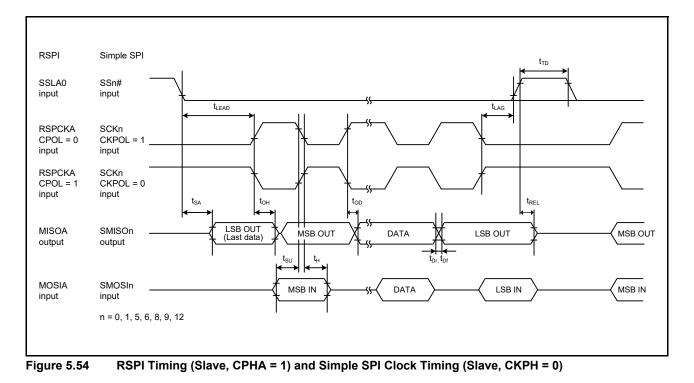

#### Table 5.34 **Timing of On-Chip Peripheral Modules (2)**

Conditions: 1.8 V ≤ VCC = AVCC0 < 2.0 V, 2.0 V ≤ VCC ≤ 5.5 V, 2.0 V ≤ AVCC0 ≤ 5.5 V, VSS = AVSS0 = 0 V, Ta = -40 to +105°C, C = 30 pF, when high-drive output is selected by the drive capacity register

|   |                                      |         | Item                                                        | Symbol                            | Min.                                                                     | Max.                                              | Unit                 | Test<br>Condition |

|---|--------------------------------------|---------|-------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------|---------------------------------------------------|----------------------|-------------------|

|   | RSPCK                                | Master  |                                                             | t <sub>SPcyc</sub>                | 2                                                                        | 4096                                              | t <sub>Pcyc</sub> *1 | Figure 5.50       |

|   | clock cycle                          | Slave   |                                                             |                                   | 8                                                                        | _                                                 |                      |                   |

|   | RSPCK<br>clock high                  | Master  |                                                             | t <sub>SPCKW</sub><br>Н           | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 | _                                                 | ns                   |                   |

|   | pulse width                          | Slave   |                                                             |                                   | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     | _                                                 |                      |                   |

|   | RSPCK<br>clock low                   | Master  |                                                             | t <sub>SPCKW</sub>                | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2 – 3 | _                                                 | ns                   |                   |

|   | pulse width                          | Slave   |                                                             |                                   | (t <sub>SPcyc</sub> – t <sub>SPCKr</sub> –<br>t <sub>SPCKf</sub> )/2     | _                                                 |                      |                   |

|   | RSPCK                                | Output  | 2.7 V or above                                              | t <sub>SPCKr</sub> ,              |                                                                          | 10                                                | ns                   |                   |

|   | clock rise/<br>fall time             |         | 1.8 V or above                                              | t <sub>SPCKf</sub>                | _                                                                        | 15                                                |                      |                   |

|   |                                      | Input   | •                                                           |                                   | —                                                                        | 0.1                                               | μs/V                 | -                 |

| ľ | Data input                           | Master  | 2.7 V or above                                              | t <sub>SU</sub>                   | 10                                                                       | _                                                 | ns                   | Figure 5.5        |

|   | setup time                           |         | 1.8 V or above                                              |                                   | 30                                                                       | _                                                 |                      | to<br>Figure 5.5  |

|   | Data input<br>hold time<br>SSL setup | Slave   | 1                                                           | -                                 | 25 – t <sub>Pcyc</sub>                                                   | _                                                 |                      | Figure 5.5        |

|   |                                      | Master  | RSPCK set to a division ratio other than PCLKB divided by 2 | t <sub>H</sub>                    | t <sub>Pcyc</sub>                                                        | _                                                 | ns                   |                   |

|   |                                      |         | RSPCK set to PCLKB divided by 2                             | t <sub>HF</sub>                   | 0                                                                        | _                                                 |                      |                   |

|   |                                      | Slave   | •                                                           | t <sub>H</sub>                    | 20 + 2 × t <sub>Pcyc</sub>                                               | _                                                 |                      |                   |

| ľ | SSL setup                            | Master  |                                                             | t <sub>LEAD</sub>                 | -30 + N*2 × t <sub>SPcyc</sub>                                           |                                                   | ns                   |                   |

|   | time                                 | Slave   |                                                             |                                   | 2                                                                        |                                                   | t <sub>Pcyc</sub>    | _                 |

| ľ | SSL hold                             | Master  |                                                             | t <sub>LAG</sub>                  | $-30 + N^{*3} \times t_{SPcyc}$                                          | _                                                 | ns                   | 1                 |

|   | time                                 | Slave   |                                                             |                                   | 2                                                                        | _                                                 | t <sub>Pcyc</sub>    | _                 |

|   |                                      | Master  | 2.7 V or above                                              | t <sub>OD</sub>                   | —                                                                        | 14                                                | ns                   | -                 |

|   | delay time                           |         | 1.8 V or above                                              |                                   | —                                                                        | 30                                                |                      |                   |

|   |                                      | Slave   | 2.7 V or above                                              | -                                 | _                                                                        | 3 × t <sub>Pcyc</sub> + 65                        |                      |                   |

|   |                                      |         | 1.8 V or above                                              |                                   |                                                                          | 3 × t <sub>Pcyc</sub> +105                        |                      |                   |

| ľ | Data output                          | Master  |                                                             | t <sub>OH</sub>                   | 0                                                                        |                                                   | ns                   |                   |

|   | hold time                            | Slave   |                                                             |                                   | 0                                                                        |                                                   |                      |                   |

|   | Successive<br>transmissio            | Master  |                                                             | t <sub>TD</sub>                   | $t_{SPcyc}$ + 2 × $t_{Pcyc}$                                             | 8 × t <sub>SPcyc</sub> + 2 ×<br>t <sub>Pcyc</sub> | ns                   |                   |

|   | n delay time                         | Slave   |                                                             |                                   | 4 × t <sub>Pcyc</sub>                                                    | _                                                 |                      |                   |

|   | MOSI and                             | Output  | 2.7 V or above                                              | t <sub>Dr</sub> , t <sub>Df</sub> | —                                                                        | 10                                                | ns                   | 1                 |

|   | MISO rise/<br>fall time              |         | 1.8 V or above                                              | 1                                 |                                                                          | 15                                                | 1                    |                   |

| ļ |                                      | Input   |                                                             | 1                                 | —                                                                        | 1                                                 | μs                   | 1                 |

|   | SSL rise/fall                        | Output  | 2.7 V or above                                              | t <sub>SSLr</sub> ,               | _                                                                        | 10                                                | ns                   | 1                 |

| l | time                                 |         | 1.8 V or above                                              | t <sub>SSLf</sub>                 | —                                                                        | 15                                                | ns                   | ]                 |

| I |                                      | Input   |                                                             | 1                                 | —                                                                        | 1                                                 | μs                   | 1                 |

| ľ | Slave access                         | time    | 2.7 V or above                                              | t <sub>SA</sub>                   | _                                                                        | 6                                                 | t <sub>Pcyc</sub>    | Figure 5.5        |

|   |                                      |         | 1.8 V or above                                              | -                                 | —                                                                        | 7                                                 | 1                    | Figure 5.5        |

|   | Slave output                         | release | 2.7 V or above                                              | t <sub>REL</sub>                  | _                                                                        | 5                                                 | t <sub>Pcyc</sub>    | 1                 |

| 1 | time                                 |         | 1.8 V or above                                              | 1                                 | —                                                                        | 6                                                 | 1                    |                   |

Note 1.

t<sub>Pcyc</sub>: PCLK cycle

Note 2.

N: An integer from 1 to 8 that can be set by the RSPI clock delay register (SPCKD)

Note 3.

N: An integer from 1 to 8 that can be set by the RSPI slave select negation delay register (SSLND)

RENESAS

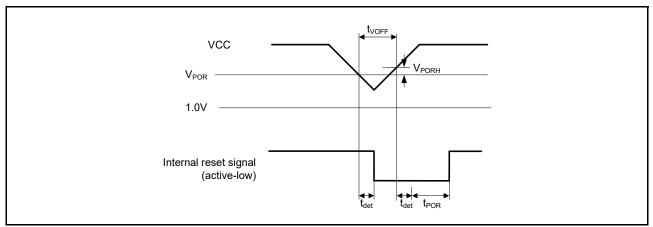

### Table 5.50 Power-On Reset Circuit and Voltage Detection Circuit Characteristics (2)

Conditions:  $1.8 \text{ V} \le \text{VCC} = \text{AVCC0} < 2.0 \text{ V}, 2.0 \text{ V} \le \text{VCC} \le 5.5 \text{ V}, 2.0 \text{ V} \le \text{AVCC0} \le 5.5 \text{ V}, \text{VSS} = \text{AVSS0} = 0 \text{ V}, \text{ T}_a = -40 \text{ to } +105^{\circ}\text{C}$

| Item                                                          |                                                                  | Symbol              | Min. | Тур. | Max. | Unit          | Test Conditions                   |  |  |

|---------------------------------------------------------------|------------------------------------------------------------------|---------------------|------|------|------|---------------|-----------------------------------|--|--|

| Wait time after                                               | At normal startup*1                                              | t <sub>POR</sub>    | —    | 9.1  | _    | ms            | Figure 5.62                       |  |  |

| power-on reset cancellation                                   | During fast startup<br>time <sup>*2</sup>                        | t <sub>POR</sub>    | —    | 1.6  | —    |               |                                   |  |  |

| Wait time after<br>voltage monitoring 0<br>reset cancellation | Power-on voltage<br>monitoring 0 reset<br>disabled* <sup>1</sup> | t <sub>LVD0</sub>   | —    | 568  | -    | μs            | Figure 5.63                       |  |  |

|                                                               | Power-on voltage<br>monitoring 0 reset<br>enabled <sup>*2</sup>  |                     | _    | 100  | —    |               |                                   |  |  |

| Wait time after voltage monitoring 1 reset cancellation       |                                                                  | t <sub>LVD1</sub>   | —    | 100  | —    | μs            | Figure 5.64                       |  |  |

| Wait time after voltage monitoring 2 reset cancellation       |                                                                  | t <sub>LVD2</sub>   | —    | 100  | —    | μs            | Figure 5.65                       |  |  |

| Response delay time                                           |                                                                  | t <sub>det</sub>    | —    | _    | 350  | μs            | Figure 5.61                       |  |  |

| Minimum VCC down time*3                                       |                                                                  | t <sub>VOFF</sub>   | 350  |      | —    | μs            | Figure 5.61, VCC = 1.0 V or above |  |  |

| Power-on reset enable time                                    |                                                                  | t <sub>W(POR)</sub> | 1    |      | —    | ms            | Figure 5.62, VCC = below 1.0<br>V |  |  |

| LVD operation stabilization time (after LVD is enabled)       |                                                                  | t <sub>d(E-A)</sub> | —    |      | 300  | μs            | Figure 5.64, Figure 5.65          |  |  |

| Hysteresis width (power-on rest (POR))                        |                                                                  | V <sub>PORH</sub>   | —    | 110  | —    | mV            |                                   |  |  |

| Hysteresis width (LVD                                         | 0, LVD1, and LVD2)                                               | V <sub>LVH</sub>    | —    | 70   | —    | mV            | Vdet0_0 to Vdet0_3 selected       |  |  |

|                                                               |                                                                  |                     | _    | 70   | —    |               | Vdet1_0 to Vdet1_4 selected       |  |  |

|                                                               |                                                                  |                     | _    | 60   | —    |               | Vdet1_5 to 9 selected             |  |  |

|                                                               |                                                                  |                     |      | 50   | —    | 1             | Vdet1_A to B selected             |  |  |

|                                                               |                                                                  |                     | —    | 40   | —    | 1             | Vdet1_C to D selected             |  |  |

|                                                               |                                                                  |                     | 60   | _    | ]    | LVD2 selected |                                   |  |  |

Note: These characteristics apply when noise is not superimposed on the power supply. When a setting is made so that the voltage detection level overlaps with that of the voltage detection circuit (LVD1), it cannot be specified which of LVD1 and LVD2 is used for voltage detection.

Note 1. When OFS1.(LVDAS, FASTSTUP) = 11b.

Note 2. When OFS1.(LVDAS, FASTSTUP) ≠ 11b.

Note 3. The minimum VCC down time indicates the time when VCC is below the minimum value of voltage detection levels  $V_{POR}$ ,  $V_{det0}$ ,  $V_{det1}$ , and  $V_{det2}$  for the POR/LVD.

# 5.11 ROM (Flash Memory for Code Storage) Characteristics

| Table 5.52 | ROM (Flash Memory for Code Storage) Characteristics (1) |

|------------|---------------------------------------------------------|

|------------|---------------------------------------------------------|

| Item                          |                                      | Symbol           | Min.     | Тур. | Max. | Unit  | Conditions             |

|-------------------------------|--------------------------------------|------------------|----------|------|------|-------|------------------------|

| Reprogramming/erasure cycle*1 |                                      | N <sub>PEC</sub> | 1000     |      |      | Times |                        |

| Data retention                | After 1000 times of $N_{\text{PEC}}$ | t <sub>DRP</sub> | 20*2, *3 |      |      | Year  | T <sub>a</sub> = +85°C |

Note 1. Definition of reprogram/erase cycle: The reprogram/erase cycle is the number of erasing for each block. When the reprogram/ erase cycle is n times (n = 1000), erasing can be performed n times for each block. For instance, when 4-byte programming is performed 256 times for different addresses in 1-Kbyte block and then the entire block is erased, the reprogram/erase cycle is counted as one. However, programming the same address for several times as one erasing is not enabled (overwriting is prohibited).

Note 2. Characteristic when using the flash memory programmer and the self-programming library provided from Renesas Electronics. Note 3. This result is obtained from reliability testing.

### Table 5.53 ROM (Flash Memory for Code Storage) Characteristics (2) High-Speed Operating Mode

Conditions: 2.7 V  $\leq$  VCC  $\leq$  5.5 V, 2.7 V  $\leq$  AVCC0  $\leq$  5.5 V, VSS = AVSS0 = 0 V

Temperature range for the programming/erasure operation:  $T_a = -40$  to  $+105^{\circ}C$

| ltem                                 |           | Symbol             | F    | CLK = 1 M⊦ | z    | FCLK = 32 MHz |      |       | Linit |

|--------------------------------------|-----------|--------------------|------|------------|------|---------------|------|-------|-------|

|                                      |           | Symbol             | Min. | Тур.       | Max. | Min.          | Тур. | Max.  | Unit  |

| Programming time                     | 4-byte    | t <sub>P4</sub>    | _    | 103        | 931  | _             | 52   | 489   | μs    |

| Erasure time                         | 1-Kbyte   | t <sub>E1K</sub>   | _    | 8.23       | 267  | —             | 5.48 | 214   | ms    |

|                                      | 256-Kbyte | t <sub>E256K</sub> | _    | 407        | 928  | —             | 39   | 457   | ms    |

| Blank check time                     | 4-byte    | t <sub>BC4</sub>   | _    | —          | 48   | —             | —    | 15.9  | μs    |

|                                      | 1-Kbyte   | t <sub>BC1K</sub>  | _    | —          | 1.58 | —             | —    | 0.127 | ms    |

| Erase operation forcible stop time   |           | t <sub>SED</sub>   | _    | —          | 21.6 | —             | —    | 12.8  | μs    |

| Start-up area switching setting time |           | t <sub>SAS</sub>   | _    | 12.6       | 543  | —             | 6.16 | 432   | ms    |

| Access window setting time           |           | t <sub>AWS</sub>   | _    | 12.6       | 543  | —             | 6.16 | 432   | ms    |

| ROM mode transition wait time 1      |           | t <sub>DIS</sub>   | 2    | —          | —    | 2             | —    | —     | μs    |

| ROM mode transition wait time 2      |           | t <sub>MS</sub>    | 5    | —          | —    | 5             | —    | —     | μs    |

Note:Does not include the time until each operation of the flash memory is started after instructions are executed by software.Note:The lower-limit frequency of FCLK is 1 MHz during programming or erasing of the flash memory. When using FCLK at below<br/>4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note: The frequency accuracy of FCLK should be ±3.5%.

### **REVISION HISTORY**

### **RX130 Group Datasheet**

Classifications

- Items with Technical Update document number: Changes according to the corresponding issued Technical Update

- Items without Technical Update document number: Minor changes that do not require Technical Update to be issued

| Rev.     | Date         |                  | Classification                                                                                                                                                          |                |  |  |  |

|----------|--------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

|          |              | Page             | Classification                                                                                                                                                          |                |  |  |  |

| 1.00     | Oct 30, 2015 |                  | First edition, issued                                                                                                                                                   |                |  |  |  |

| 2.00 Sep | Sep 01, 2017 | All              | Products with at least 256 Kbytes of code flash memory and 100-pin packages added                                                                                       |                |  |  |  |

|          |              | 4. I/O Registers |                                                                                                                                                                         |                |  |  |  |