Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, Motor Control PWM, QEI, POR, PWM, WDT             |

| Number of I/O              | 68                                                                             |

| Program Memory Size        | 144KB (48K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 4K x 8                                                                         |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6010a-20e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U S A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-953-2

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **High-Performance, 16-bit Digital Signal Controllers**

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

#### High-Performance Modified RISC CPU:

- Modified Harvard architecture

- C compiler optimized instruction set architecture with flexible Addressing modes

- 83 base instructions

- 24-bit wide instructions, 16-bit wide data path

- 144 Kbytes on-chip Flash program space (Instruction words)

- 8 Kbytes of on-chip data RAM

- 4 Kbytes of nonvolatile data EEPROM

- Up to 30 MIPS operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- 7.37 MHz internal RC with PLL active (4x, 8x, 16x)

- 44 interrupt sources:

- Five external interrupt sources

- Eight user selectable priority levels for each interrupt source

- Four processor trap sources

- 16 x 16-bit working register array

# **DSP Engine Features:**

- Dual data fetch

- Accumulator write-back for DSP operations

- Modulo and Bit-Reversed Addressing modes

- Two, 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single-cycle hardware fractional/ integer multiplier

- · All DSP instructions single cycle

- ±16-bit single-cycle shift

# **Peripheral Features:**

- High-current sink/source I/O pins: 25 mA/25 mA

- Timer module with programmable prescaler:

- Five 16-bit timers/counters; optionally pair 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- 16-bit Compare/PWM output functions

- 3-wire SPI modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- Two UART modules with FIFO Buffers

- Two CAN modules, 2.0B compliant (dsPIC306010A)

- One CAN module, 2.0B compliant (dsPIC306015)

# Motor Control PWM Module Features:

- Eight PWM output channels:

- Complementary or Independent Output modes

- Edge and Center-Aligned modes

- Four duty cycle generators

- · Dedicated time base

- Programmable output polarity

- Dead-Time control for Complementary mode

- Manual output control

- Trigger for A/D conversions

# Quadrature Encoder Interface Module Features:

- Phase A, Phase B and Index Pulse input

- 16-bit up/down position counter

- · Count direction status

- Position Measurement (x2 and x4) mode

- · Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- · Interrupt on position counter rollover/underflow

# **Analog Features:**

- 10-bit Analog-to-Digital Converter (ADC) with four S/H Inputs:

- 1 Msps conversion rate

- 16 input channels

- Conversion available during Sleep and Idle

- Programmable Brown-out Reset

# **Special Microcontroller Features:**

- Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for

- industrial temperature range, 100K (typical)Data EEPROM memory:

- 100,000 erase/write cycle (min.) for industrial temperature range, 1M (typical)

- Self-reprogrammable under software control

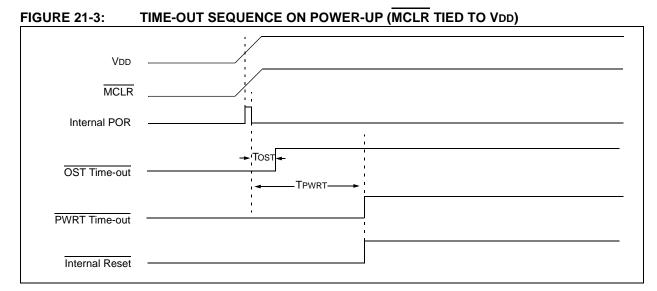

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip, low-power RC oscillator for reliable operation

- Fail-Safe Clock Monitor operation detects clock failure and switches to on-chip, low-power RC oscillator

- Programmable code protection

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Selectable Power Management modes

- Sleep, Idle and Alternate Clock modes

# **CMOS Technology:**

- · Low-power, high-speed Flash technology

- Wide operating voltage range (2.5V to 5.5V)

- Industrial and Extended temperature ranges

- Low-power consumption

# dsPIC30F Motor Control and Power Conversion Family

| Device        | Pins | Program<br>Mem. Bytes/<br>Instructions | SRAM<br>Bytes | EEPROM<br>Bytes | Timer<br>16-bit |   | Output<br>Comp/Std<br>PWM | Motor<br>Control<br>PWM | A/D 10-bit<br>1 Msps | Quad<br>Enc | UART | IdS | I²C™ | CAN |

|---------------|------|----------------------------------------|---------------|-----------------|-----------------|---|---------------------------|-------------------------|----------------------|-------------|------|-----|------|-----|

| dsPIC30F6010A | 80   | 144K/48K                               | 8192          | 4096            | 5               | 8 | 8                         | 8 ch                    | 16 ch                | Yes         | 2    | 2   | 1    | 2   |

| dsPIC30F6015  | 64   | 144K/48K                               | 8192          | 4096            | 5               | 8 | 8                         | 8 ch                    | 16 ch                | Yes         | 2    | 2   | 1    | 1   |

# **Table of Contents**

| 1.0   | Device Overview                                            | 9   |

|-------|------------------------------------------------------------|-----|

| 2.0   | CPU Architecture Overview                                  | 15  |

| 3.0   | Memory Organization                                        | 23  |

| 4.0   | Address Generator Units                                    | 35  |

| 5.0   | Interrupts                                                 | 41  |

| 6.0   | Flash Program Memory                                       | 49  |

| 7.0   | Data EEPROM Memory                                         | 55  |

| 8.0   | I/O Ports                                                  | 59  |

| 9.0   | Timer1 Module                                              | 65  |

| 10.0  | Timer2/3 Module                                            | 69  |

| 11.0  | Timer4/5 Module                                            | 77  |

| 12.0  | Input Capture Module                                       | -   |

| 13.0  | Output Compare Module                                      |     |

|       | Quadrature Encoder Interface (QEI) Module                  |     |

|       | Motor Control PWM Module                                   |     |

|       | SPI Module                                                 | -   |

| -     | I2C™ Module                                                |     |

|       | Universal Asynchronous Receiver Transmitter (UART) Module  |     |

|       | CAN Module                                                 |     |

|       | 10-bit High-Speed Analog-to-Digital Converter (ADC) Module |     |

| 21.0  | System Integration                                         |     |

| 22.0  | Instruction Set Summary                                    |     |

| 23.0  | Development Support                                        |     |

| 24.0  | Electrical Characteristics                                 |     |

|       | Packaging Information                                      |     |

|       | ndix A: Revision History                                   |     |

|       |                                                            |     |

|       | Aicrochip Web Site                                         |     |

|       | omer Change Notification Service                           |     |

|       | omer Support                                               |     |

|       | er Response                                                |     |

| Produ | Ict Identification System                                  | 235 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

The SA and SB bits are modified each time data passes through the adder/subtractor, but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation, or bit 39 for 40-bit saturation) and will be saturated if saturation is enabled. When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three Saturation and Overflow modes.

- 1. Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (e.g., gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x008000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used so the OA, OB or OAB bits are never set.

- 3. Bit 39 Catastrophic Overflow The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remain set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

# 2.4.2.2 Accumulator 'Write-Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- 1. W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+ = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

# 2.4.2.3 Round Logic

The round logic is a combinational block, which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value will tend to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the LSb (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory, via the X bus (subject to data saturation, see Section 2.4.2.4 "Data Space Write Saturation"). Note that for the MAC class of instructions, the accumulator write-back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

# 3.0 MEMORY ORGANIZATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

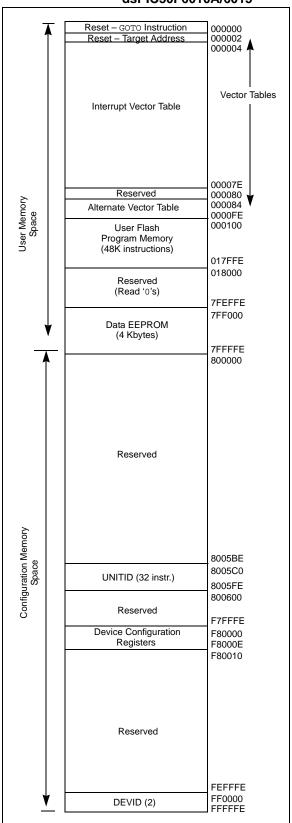

# 3.1 Program Address Space

The program address space is 4M instruction words. It is addressable by the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space, as defined by Table 3-1. Note that the program space address is incremented by two between successive program words, in order to provide compatibility with data space addressing.

User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE), for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, read/write instructions, bit 23 allows access to the device ID, the user ID and the Configuration bits. Otherwise, bit 23 is always clear.

#### FIGURE 3-1:

#### PROGRAM SPACE MEMORY MAP FOR dsPIC30F6010A/6015

# 5.1 Interrupt Priority

The user-assignable Interrupt Priority bits (IP<2:0>) for each individual interrupt source are located in the Least Significant 3 bits of each nibble within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user-assignable priority levels start at  |

|-------|-----------------------------------------------|

|       | 0, as the lowest priority and level 7, as the |

|       | highest priority.                             |

Since more than one interrupt request source may be assigned to a specific user-assigned priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority".

Natural Order Priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 5-1 lists the interrupt numbers and interrupt sources for the dsPIC DSC devices and their associated vector numbers.

- **Note 1:** The Natural Order Priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:** The Natural Order Priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels means that the user can assign a very high overall priority level to an interrupt with a low natural order priority.

#### TABLE 5-1: INTERRUPT VECTOR TABLE

| IABLE 5       |                  | TERRUPT VECTOR TABLE                                 |  |  |  |  |  |  |

|---------------|------------------|------------------------------------------------------|--|--|--|--|--|--|

| INT<br>Number | Vector<br>Number | Interrupt Source                                     |  |  |  |  |  |  |

|               | Highest          | Natural Order Priority                               |  |  |  |  |  |  |

| 0             | 8                | INT0 – External Interrupt 0                          |  |  |  |  |  |  |

| 1             | 9                | IC1 – Input Capture 1                                |  |  |  |  |  |  |

| 2             | 10               | OC1 – Output Compare 1                               |  |  |  |  |  |  |

| 3             | 11               | T1 – Timer1                                          |  |  |  |  |  |  |

| 4             | 12               | IC2 – Input Capture 2                                |  |  |  |  |  |  |

| 5             | 13               | OC2 – Output Compare 2                               |  |  |  |  |  |  |

| 6             | 14               | T2 – Timer2                                          |  |  |  |  |  |  |

| 7             | 15               | T3 – Timer3                                          |  |  |  |  |  |  |

| 8             | 16               | SPI1                                                 |  |  |  |  |  |  |

| 9             | 17               | U1RX – UART1 Receiver                                |  |  |  |  |  |  |

| 10            | 18               | U1TX – UART1 Transmitter                             |  |  |  |  |  |  |

| 11            | 19               | ADC – ADC Convert Done                               |  |  |  |  |  |  |

| 12            | 20               | NVM - NVM Write Complete                             |  |  |  |  |  |  |

| 13            | 21               | SI2C – I <sup>2</sup> C <sup>™</sup> Slave Interrupt |  |  |  |  |  |  |

| 14            | 22               | MI2C – I <sup>2</sup> C Master Interrupt             |  |  |  |  |  |  |

| 15            | 23               | Input Change Interrupt                               |  |  |  |  |  |  |

| 16            | 24               | INT1 – External Interrupt 1                          |  |  |  |  |  |  |

| 17            | 25               | IC7 – Input Capture 7                                |  |  |  |  |  |  |

| 18            | 26               | IC8 – Input Capture 8                                |  |  |  |  |  |  |

| 19            | 27               | OC3 – Output Compare 3                               |  |  |  |  |  |  |

| 20            | 28               | OC4 – Output Compare 4                               |  |  |  |  |  |  |

| 21            | 29               | T4 – Timer4                                          |  |  |  |  |  |  |

| 22            | 30               | T5 – Timer5                                          |  |  |  |  |  |  |

| 23            | 31               | INT2 – External Interrupt 2                          |  |  |  |  |  |  |

| 24            | 32               | U2RX – UART2 Receiver                                |  |  |  |  |  |  |

| 25            | 33               | U2TX – UART2 Transmitter                             |  |  |  |  |  |  |

| 26            | 34               | SPI2                                                 |  |  |  |  |  |  |

| 27            | 35               | C1 – Combined IRQ for CAN1                           |  |  |  |  |  |  |

| 28            | 36               | IC3 – Input Capture 3                                |  |  |  |  |  |  |

| 29            | 37               | IC4 – Input Capture 4                                |  |  |  |  |  |  |

| 30            | 38               | IC5 – Input Capture 5                                |  |  |  |  |  |  |

| 31            | 39               | IC6 – Input Capture 6                                |  |  |  |  |  |  |

| 32            | 40               | OC5 – Output Compare 5                               |  |  |  |  |  |  |

| 33            | 41               | OC6 – Output Compare 6                               |  |  |  |  |  |  |

| 34            | 42               | OC7 – Output Compare 7                               |  |  |  |  |  |  |

| 35            | 43               | OC8 – Output Compare 8                               |  |  |  |  |  |  |

| 36            | 44               | INT3 – External Interrupt 3                          |  |  |  |  |  |  |

| 37            | 45               | INT4 - External Interrupt 4                          |  |  |  |  |  |  |

| 38            | 46               | C2 – Combined IRQ for CAN2                           |  |  |  |  |  |  |

| 39            | 47               | PWM – PWM Period Match                               |  |  |  |  |  |  |

| 40            | 48               | QEI – QEI Interrupt                                  |  |  |  |  |  |  |

| 41            | 49               | Reserved                                             |  |  |  |  |  |  |

| 42            | 50               | Reserved                                             |  |  |  |  |  |  |

| 43            | 51               | FLTA – PWM Fault A                                   |  |  |  |  |  |  |

| 44            | 52               | FLTB – PWM Fault B                                   |  |  |  |  |  |  |

| 45-53         | 53-61            | Reserved                                             |  |  |  |  |  |  |

|               | Lowest           | Natural Order Priority                               |  |  |  |  |  |  |

### 6.6 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. A programming operation is nominally 2 msec in duration and the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

#### 6.6.1 PROGRAMMING ALGORITHM FOR PROGRAM FLASH

The user can erase or program one row of program Flash memory at a time. The general process is:

- 1. Read one row of program Flash (32 instruction words) and store into data RAM as a data "image".

- 2. Update the data image with the desired new data.

- 3. Erase program Flash row.

- a) Set up NVMCON register for multi-word, program Flash, erase, and set WREN bit.

- b) Write address of row to be erased into NVMADRU/NVMDR.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit. This will begin erase cycle.

- f) CPU will stall for the duration of the erase cycle.

- g) The WR bit is cleared when erase cycle ends.

- 4. Write 32 instruction words of data from data RAM "image" into the program Flash write latches.

- 5. Program 32 instruction words into program Flash.

- Set up NVMCON register for multi-word, program Flash, program, and set WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. This will begin program cycle.

- e) CPU will stall for duration of the program cycle.

- f) The WR bit is cleared by the hardware when program cycle ends.

- 6. Repeat steps 1 through 5 as needed to program desired amount of program Flash memory.

# 6.6.2 ERASING A ROW OF PROGRAM MEMORY

Example 6-1 shows a code sequence that can be used to erase a row (32 instructions) of program memory.

# EXAMPLE 6-1: ERASING A ROW OF PROGRAM MEMORY

| Setur   | NVMCON    | for erase operation, multi wor      | d | write                                 |

|---------|-----------|-------------------------------------|---|---------------------------------------|

| ; progi | ram memor | ry selected, and writes enabled     | l |                                       |

|         | MOV       | #0x4041,W0                          | ; |                                       |

|         | MOV       | W0 NVMCON                           | ; | Init NVMCON SFR                       |

| ; Init  | pointer   | to row to be ERASED                 |   |                                       |

|         | MOV       | <pre>#tblpage(PROG_ADDR),W0</pre>   | ; |                                       |

|         | MOV       | W0 NVMADRU                          | ; | Initialize PM Page Boundary SFR       |

|         | MOV       | <pre>#tbloffset(PROG_ADDR),W0</pre> | ; | Intialize in-page EA[15:0] pointer    |

|         | MOV       | W0, NVMADR                          | ; | Intialize NVMADR SFR                  |

|         | DISI      | #5                                  | ; | Block all interrupts with priority <7 |

|         |           |                                     | ; | for next 5 instructions               |

|         | MOV       | #0x55,W0                            |   |                                       |

|         | MOV       | WONVMKEY                            | ; | Write the 0x55 key                    |

|         | MOV       | #0xAA,W1                            | ; |                                       |

|         | MOV       | W1 NVMKEY                           | ; | Write the OxAA key                    |

|         | BSET      | NVMCON, #WR                         | ; | Start the erase sequence              |

|         | NOP       |                                     | ; | Insert two NOPs after the erase       |

|         | NOP       |                                     | ; | command is asserted                   |

|         |           |                                     |   |                                       |

#### 7.3.2 WRITING A BLOCK OF DATA EEPROM

To write a block of data EEPROM, write to all sixteen latches first, then set the NVMCON register and program the block.

| EXAMPLE 7-5:  | DATA EEPROW             |   |                                                            |

|---------------|-------------------------|---|------------------------------------------------------------|

| MOV           | #LOW_ADDR_WORD,W0       | ; | Init pointer                                               |

| MOV           | #HIGH_ADDR_WORD,W1      |   | *                                                          |

| MOV           | W1 TBLPAG               |   |                                                            |

| MOV           | ,<br>#data1,W2          | ; | Get 1st data                                               |

| TBLWTL        | W2 [W0]++               | ; | write data                                                 |

| MOV           | #data2,W2               | ; | Get 2nd data                                               |

| TBLWTL        | W2 [W0]++               | ; | write data                                                 |

| MOV           | #data3,W2               | ; | Get 3rd data                                               |

| TBLWTL        | W2 [W0]++               | ; | write data                                                 |

| MOV           | #data4,W2               | ; | Get 4th data                                               |

| TBLWTL        | W2 [ W0 ] ++            | ; | write data                                                 |

| MOV           | #data5,W2               | ; | Get 5th data                                               |

| TBLWTL        | W2 [ W0 ] ++            | ; | write data                                                 |

| MOV           | #data6,W2               | ; | Get 6th data                                               |

| TBLWTL        | W2 [ W0 ] ++            | ; | write data                                                 |

| MOV           | #data7,W2               | ; | Get 7th data                                               |

| TBLWTL        | W2,[W0]++               | ; | write data                                                 |

| MOV           | #data8,W2               | ; | Get 8th data                                               |

| TBLWTL        | W2 <sub>,</sub> [W0]++  |   | write data                                                 |

| MOV           | #data9,W2               |   | Get 9th data                                               |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data10,W2              |   | Get 10th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data11,W2              |   | Get 11th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data12,W2              |   | Get 12th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data13,W2              |   | Get 13th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data14,W2              |   | Get 14th data                                              |

| TBLWTL        | W2 [ W0 ] ++            |   | write data                                                 |

| MOV           | #data15,W2              |   | Get 15th data                                              |

| TBLWTL        | W2 [ W0 ] ++            |   | write data<br>Get 16th data                                |

| MOV<br>TBLWTL | #data16,W2              |   | write data. The NVMADR captures last table access address. |

|               | W2,[W0]++               |   | Select data EEPROM for multi word op                       |

| MOV<br>MOV    | #0x400A,W0<br>W0 NVMCON |   | Operate Key to allow program operation                     |

| DISI          | #5                      |   | Block all interrupts with priority <7                      |

| DISI          | #5                      |   | for next 5 instructions                                    |

| MOV           | #0x55,W0                | ' |                                                            |

| MOV           | WONVMKEY                | ; | Write the 0x55 key                                         |

| MOV           | #0xAA,W1                |   |                                                            |

| MOV           | W1 NVMKEY               | ; | Write the OxAA key                                         |

| BSET          | ,<br>NVMCON, #WR        |   | Start write cycle                                          |

| NOP           |                         |   | -                                                          |

| NOP           |                         |   |                                                            |

|               |                         |   |                                                            |

#### EXAMPLE 7-5: DATA EEPROM BLOCK WRITE

# 7.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 7.5 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared; also, the Power-up Timer prevents EEPROM write.

The write initiate sequence and the WREN bit together, help prevent an accidental write during brown-out, power glitch or software malfunction.

# TABLE 11-1: TIMER4/5 REGISTER MAP<sup>(1)</sup>

| © 2011           |  |

|------------------|--|

| 1 Microchip -    |  |

| ip Technology Ir |  |

| ology Inc        |  |

| SFR Name | Addr. | Bit 15                                        | Bit 14                                               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7        | Bit 6               | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1          | Bit 0          | Reset State         |

|----------|-------|-----------------------------------------------|------------------------------------------------------|--------|--------|--------|--------|-------|-------|--------------|---------------------|--------|--------|-------|-------|----------------|----------------|---------------------|

| TMR4     | 0114  |                                               | Timer4 Register                                      |        |        |        |        |       |       |              |                     |        |        |       |       |                | uuuu uuuu uuuu |                     |

| TMR5HLD  | 0116  |                                               | Timer5 Holding Register (For 32-bit operations only) |        |        |        |        |       |       |              |                     |        |        |       |       | uuuu uuuu uuuu |                |                     |

| TMR5     | 0118  |                                               | Timer5 Register                                      |        |        |        |        |       |       |              |                     |        |        |       |       | uuuu uuuu uuuu |                |                     |

| PR4      | 011A  |                                               |                                                      |        |        |        |        |       | Per   | riod Registe | er 4                |        |        |       |       |                |                | 1111 1111 1111 1111 |

| PR5      | 011C  |                                               |                                                      |        |        |        |        |       | Per   | riod Registe | er 5                |        |        |       |       |                |                | 1111 1111 1111 1111 |

| T4CON    | 011E  | TON - TSIDL TGATE TCKPS1 TCKPS0 T45 - TCS - 0 |                                                      |        |        |        |        |       |       |              | 0000 0000 0000 0000 |        |        |       |       |                |                |                     |

| T5CON    | 0120  | TON                                           | _                                                    | TSIDL  | _      | _      |        | _     | _     | _            | TGATE               | TCKPS1 | TCKPS0 |       | _     | TCS            |                | 0000 0000 0000 0000 |

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0'

Note

1:

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

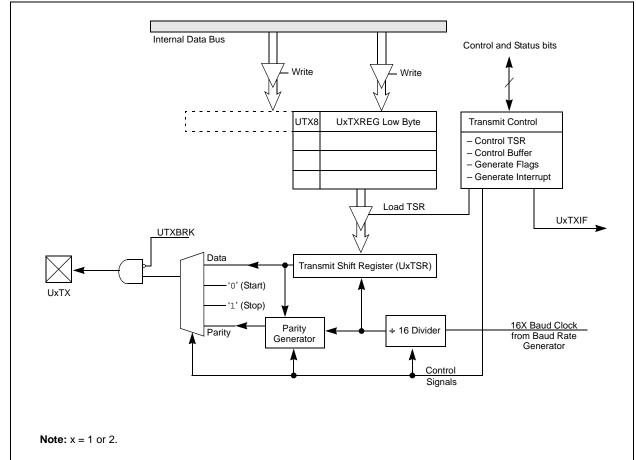

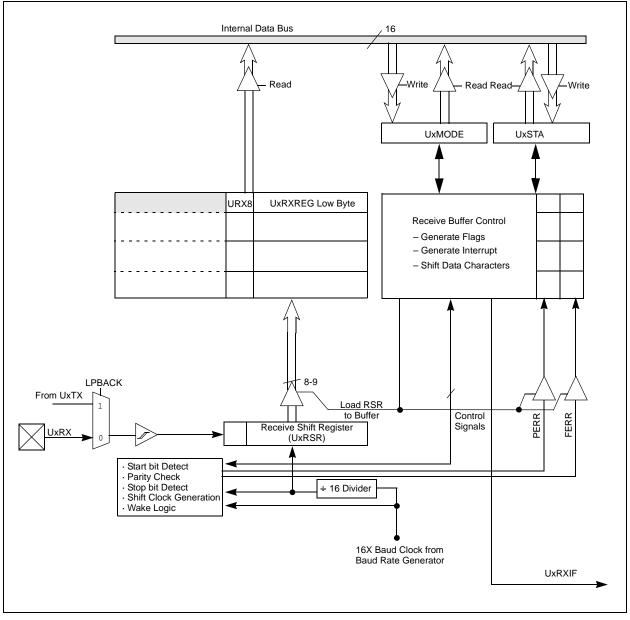

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the Universal Asynchronous Receiver/Transmitter Communications module.

# 18.1 UART Module Overview

The key features of the UART module are:

- Full-duplex, 8 or 9-bit data communication

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Fully integrated Baud Rate Generator with 16-bit prescaler

- Baud rates range from 38 bps to 1.875 Mbps at a 30 MHz instruction rate

- 4-word deep transmit data buffer

- 4-word deep receive data buffer

- Parity, Framing and Buffer Overrun error detection

- Support for Interrupt only on Address Detect (9th bit = 1)

- Separate Transmit and Receive Interrupts

- Loopback mode for diagnostic support

#### FIGURE 18-1: UART TRANSMITTER BLOCK DIAGRAM

# FIGURE 18-2: UART RECEIVER BLOCK DIAGRAM

• Receive Error Interrupts

A receive error interrupt will be indicated by the ERRIF bit. This bit shows that an error condition occurred. The source of the error can be determined by checking the bits in the CAN Interrupt STATUS register, CIINTF.

• Invalid message received

If any type of error occurred during reception of the last message, an error will be indicated by the IVRIF bit.

Receiver overrun

The RXnOVR bit indicates that an overrun condition occurred.

Receiver warning

The RXWAR bit indicates that the Receive Error Counter (RERRCNT<7:0>) has reached the Warning limit of 96.

• Receiver error passive

The RXEP bit indicates that the Receive Error Counter has exceeded the Error Passive limit of 127 and the module has gone into Error Passive state.

# 19.5 Message Transmission

#### 19.5.1 TRANSMIT BUFFERS

The CAN module has three transmit buffers. Each of the three buffers occupies 14 bytes of data. Eight of the bytes are the maximum 8 bytes of the transmitted message. Five bytes hold the standard and extended identifiers and other message arbitration information.

#### 19.5.2 TRANSMIT MESSAGE PRIORITY

Transmit priority is a prioritization within each node of the pending transmittable messages. There are 4 levels of transmit priority. If TXPRI<1:0> (CiTXnCON<1:0>, where n = 0, 1 or 2 represents a particular transmit buffer) for a particular message buffer is set to '11', that buffer has the highest priority. If TXPRI<1:0> for a particular message buffer is set to '10' or '01', that buffer has an intermediate priority. If TXPRI<1:0> for a particular message buffer is '00', that buffer has the lowest priority.

#### 19.5.3 TRANSMISSION SEQUENCE

To initiate transmission of the message, the TXREQ bit (CiTXnCON<3>) must be set. The CAN bus module resolves any timing conflicts between setting of the TXREQ bit and the Start of Frame (SOF), ensuring that if the priority was changed, it is resolved correctly before the SOF occurs. When TXREQ is set, the TXABT (CiTXnCON<6>), TXLARB (CiTXnCON<5>) and TXERR (CiTXnCON<4>) flag bits are automatically cleared. Setting TXREQ bit simply flags a message buffer as enqueued for transmission. When the module detects an available bus, it begins transmitting the message which has been determined to have the highest priority.

If the transmission completes successfully on the first attempt, the TXREQ bit is cleared automatically and an interrupt is generated if TXIE was set.

If the message transmission fails, one of the error condition flags will be set and the TXREQ bit will remain set indicating that the message is still pending for transmission. If the message encountered an error condition during the transmission attempt, the TXERR bit will be set and the error condition may cause an interrupt. If the message loses arbitration during the transmission attempt, the TXLARB bit is set. No interrupt is generated to signal the loss of arbitration.

#### 19.5.4 ABORTING MESSAGE TRANSMISSION

The system can also abort a message by clearing the TXREQ bit associated with each message buffer. Setting the ABAT bit (CiCTRL<12>) will request an abort of all pending messages. If the message has not yet started transmission, or if the message started but is interrupted by loss of arbitration or an error, the abort will be processed. The abort is indicated when the module sets the TXABT bit, and the TXnIF flag is not automatically set.

#### 19.5.5 TRANSMISSION ERRORS

The CAN module will detect the following transmission errors:

- Acknowledge error

- Form error

- Bit error

These transmission errors will not necessarily generate an interrupt, but are indicated by the transmission error counter. However, each of these errors will cause the transmission error counter to be incremented by one. Once the value of the error counter exceeds the value of 96, the ERRIF (CiINTF<5>) and the TXWAR bit (CiINTF<10>) are set. Once the value of the error counter exceeds the value of 96, an interrupt is generated and the TXWAR bit in the Error Flag register is set.

#### 21.2.6 LOW-POWER RC OSCILLATOR (LPRC)

The LPRC oscillator is a component of the Watchdog Timer (WDT) and oscillates at a nominal frequency of 512 kHz. The LPRC oscillator is the clock source for the Power-up Timer (PWRT) circuit, WDT and clock monitor circuits. It may also be used to provide a low frequency clock source option for applications where power consumption is critical, and timing accuracy is not required.

The LPRC oscillator is always enabled at a Power-on Reset, because it is the clock source for the PWRT. After the PWRT expires, the LPRC oscillator will remain ON if one of the following is TRUE:

- The Fail-Safe Clock Monitor is enabled

- The WDT is enabled

- The LPRC oscillator is selected as the system clock via the COSC<2:0> control bits in the OSCCON register

If one of the above conditions is not true, the LPRC will shut-off after the PWRT expires.

- Note 1: OSC2 pin function is determined by the Primary Oscillator mode selection (FPR<4:0>).

- 2: Note that OSC1 pin cannot be used as an I/O pin, even if the secondary oscillator or an internal clock source is selected at all times.

# 21.2.7 FAIL-SAFE CLOCK MONITOR

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by appropriately programming the FCKSM Configuration bits (Clock Switch and Monitor Selection bits) in the Fosc device Configuration register. If the FSCM function is enabled, the LPRC internal oscillator will run at all times (except during Sleep mode) and will not be subject to control by the SWDTEN bit.

In the event of an oscillator failure, the FSCM will generate a clock failure trap event and will switch the system clock over to the FRC oscillator. The user will then have the option to either attempt to restart the oscillator or execute a controlled shutdown. The user may decide to treat the trap as a warm Reset by simply loading the Reset address into the oscillator fail trap vector. In this event, the CF (Clock Fail) Status bit (OSCCON<3>) is also set whenever a clock failure is recognized.

In the event of a clock failure, the WDT is unaffected and continues to run on the LPRC clock.

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<2:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC oscillator as follows:

- 1. The COSC bits (OSCCON<14:12>) are loaded with the FRC oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- Primary

- Secondary

- Internal FRC

- Internal LPRC

The user can switch between these functional groups, but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<4:0> Configuration bits.

The OSCCON register holds the control and Status bits related to clock switching.

- COSC<2:0>: Read-only Status bits always reflect the current oscillator group in effect.

- NOSC<2:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<2:0> and NOSC<2:0> are both loaded with the Configuration bit values FOS<2:0>.

- LOCK: The LOCK Status bit indicates a PLL lock.

- CF: Read-only Status bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1' when a clock transition sequence is initiated. Clearing the OSWEN control bit will abort a clock transition in progress (used for hang-up situations).

If Configuration bits FCKSM<1:0> = 1x, then the clock switching and Fail-Safe Clock Monitor functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<2:0> and FPR<4:0> bits directly control the oscillator selection and the COSC<2:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

**Note:** The application should not attempt to switch to a clock of frequency lower than 100 kHz when the Fail-Safe Clock Monitor is enabled. If clock switching is performed, the device may generate an oscillator fail trap and switch to the fast RC oscillator.

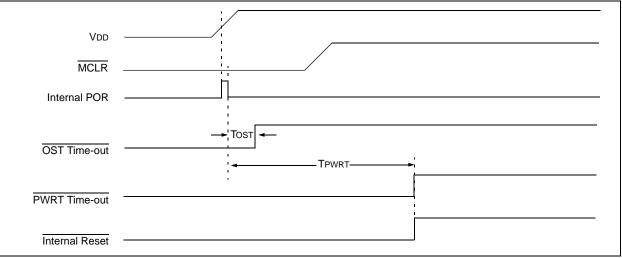

# FIGURE 21-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

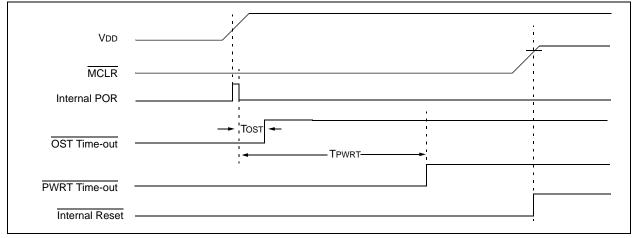

# FIGURE 21-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# 23.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 23.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 23.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

# 23.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 23.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 23.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 23.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 23.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 23.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| DC CHA       | RACTERIS   | STICS                                                               | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                  |  |  |  |

|--------------|------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|----------------------------------|--|--|--|

| Param<br>No. | Symbol     | Characteristic                                                      | Min                                                                                                                                                                                      | Typ <sup>(1)</sup> | Max | Units | Conditions                       |  |  |  |

| Operatir     | ng Voltage | (2)                                                                 |                                                                                                                                                                                          |                    |     |       | -                                |  |  |  |

| DC10         | Vdd        | Supply Voltage                                                      | 2.5                                                                                                                                                                                      | _                  | 5.5 | V     | Industrial temperature           |  |  |  |

| DC11         | Vdd        | Supply Voltage                                                      | 3.0                                                                                                                                                                                      | _                  | 5.5 | V     | Extended temperature             |  |  |  |

| DC12         | Vdr        | RAM Data Retention Voltage <sup>(3)</sup>                           | 1.75                                                                                                                                                                                     | _                  |     | V     | —                                |  |  |  |

| DC16         | VPOR       | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _                                                                                                                                                                                        | Vss                | _   | V     | _                                |  |  |  |

| DC17         | SVDD       | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05                                                                                                                                                                                     | —                  |     | V/ms  | 0-5V in 0.1 sec<br>0-3V in 60 ms |  |  |  |

# TABLE 24-5: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

3: This is the limit to which VDD can be lowered without losing RAM data.

#### TABLE 24-8: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACI       | FERISTICS                  |     | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |            |      |                                                |  |  |  |  |  |

|------------------|----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------------------------------------------|--|--|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>     | Мах | Units                                                                                                                                                                                    | Conditions |      |                                                |  |  |  |  |  |

| Power-Down       | Current (IPD) <sup>(</sup> | 2)  |                                                                                                                                                                                          |            |      |                                                |  |  |  |  |  |

| DC60a            | 0.2                        | _   | μA                                                                                                                                                                                       | 25°C       |      |                                                |  |  |  |  |  |

| DC60b            | 1.2                        | 40  | μA                                                                                                                                                                                       | 85°C       | 3.3V |                                                |  |  |  |  |  |

| DC60c            | 12                         | 65  | μA                                                                                                                                                                                       | 125°C      |      | Base Power-Down Current <sup>(3)</sup>         |  |  |  |  |  |

| DC60e            | 0.4                        | —   | μA                                                                                                                                                                                       | 25°C       |      | Base Power-Down Current                        |  |  |  |  |  |

| DC60f            | 1.7                        | 55  | μA                                                                                                                                                                                       | 85°C       | 5V   |                                                |  |  |  |  |  |

| DC60g            | 15                         | 90  | μA                                                                                                                                                                                       | 125°C      |      |                                                |  |  |  |  |  |

| DC61a            | 9                          | 15  | μA                                                                                                                                                                                       | 25°C       |      |                                                |  |  |  |  |  |

| DC61b            | 9                          | 15  | μA                                                                                                                                                                                       | 85°C       | 3.3V |                                                |  |  |  |  |  |

| DC61c            | 9                          | 15  | μΑ                                                                                                                                                                                       | 125°C      |      | Watchdog Timer Current: ∆IwDT <sup>(3)</sup>   |  |  |  |  |  |

| DC61e            | 18                         | 30  | μA                                                                                                                                                                                       | 25°C       |      |                                                |  |  |  |  |  |

| DC61f            | 17                         | 30  | μΑ                                                                                                                                                                                       | 85°C       | 5V   |                                                |  |  |  |  |  |

| DC61g            | 16                         | 30  | μΑ                                                                                                                                                                                       | 125°C      |      |                                                |  |  |  |  |  |

| DC62a            | 4                          | 10  | μΑ                                                                                                                                                                                       | 25°C       |      |                                                |  |  |  |  |  |

| DC62b            | 5                          | 10  | μΑ                                                                                                                                                                                       | 85°C       | 3.3V |                                                |  |  |  |  |  |

| DC62c            | 4                          | 10  | μΑ                                                                                                                                                                                       | 125°C      |      | Timer1 w/32 kHz Crystal: ∆I⊤i32 <sup>(3)</sup> |  |  |  |  |  |

| DC62e            | 4                          | 15  | μΑ                                                                                                                                                                                       | 25°C       |      |                                                |  |  |  |  |  |

| DC62f            | 6                          | 15  | μΑ                                                                                                                                                                                       | 85°C       | 5V   |                                                |  |  |  |  |  |

| DC62g            | 5                          | 15  | μΑ                                                                                                                                                                                       | 125°C      |      |                                                |  |  |  |  |  |

| DC63a            | 29                         | 52  | μA                                                                                                                                                                                       | 25°C       | 3.3V |                                                |  |  |  |  |  |

| DC63b            | 32                         | 52  | μΑ                                                                                                                                                                                       | 85°C       |      |                                                |  |  |  |  |  |

| DC63c            | 33                         | 52  | μΑ                                                                                                                                                                                       | 125°C      |      | BOR On: ∆IBOR <sup>(3)</sup>                   |  |  |  |  |  |

| DC63e            | 34                         | 60  | μΑ                                                                                                                                                                                       | 25°C       |      |                                                |  |  |  |  |  |

| DC63f            | 39                         | 60  | μΑ                                                                                                                                                                                       | 85°C       | 5V   |                                                |  |  |  |  |  |

| DC63g            | 38                         | 60  | μA                                                                                                                                                                                       | 125°C      |      |                                                |  |  |  |  |  |

**Note 1:** Data in the "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled high. BOR, WDT, etc. are all switched off.

3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.