Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, Motor Control PWM, QEI, POR, PWM, WDT            |

| Number of I/O              | 52                                                                            |

| Program Memory Size        | 144KB (48K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 4K x 8                                                                        |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6015-30i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Pin Name                                                             | Pin<br>Type | Buffer<br>Type | Description                              |  |  |  |  |

|----------------------------------------------------------------------|-------------|----------------|------------------------------------------|--|--|--|--|

| U1RX                                                                 | I           | ST             | UART1 Receive.                           |  |  |  |  |

| U1TX                                                                 | 0           |                | UART1 Transmit.                          |  |  |  |  |

| U1ARX                                                                | I           | ST             | UART1 Alternate Receive.                 |  |  |  |  |

| U1ATX                                                                | 0           |                | UART1 Alternate Transmit.                |  |  |  |  |

| U2RX                                                                 | I           | ST             | JART2 Receive.                           |  |  |  |  |

| U2TX                                                                 | 0           | —              | ART2 Transmit.                           |  |  |  |  |

| Vdd                                                                  | Р           | —              | Positive supply for logic and I/O pins.  |  |  |  |  |

| Vss                                                                  | Р           | —              | Ground reference for logic and I/O pins. |  |  |  |  |

| Vref+                                                                | I           | Analog         | Analog Voltage Reference (High) input.   |  |  |  |  |

| Vref-                                                                | I           | Analog         | Analog Voltage Reference (Low) input.    |  |  |  |  |

| Legend: CMOS = CMOS compatible input or output Analog = Analog input |             |                |                                          |  |  |  |  |

#### **TABLE 1-1:** dsPIC30F6010A/6015 I/O PIN DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels = Input

L

0 Output

Power =

Ρ

### 2.4.1 MULTIPLIER

The 17x17-bit multiplier is capable of signed or unsigned operations and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17x17-bit multiplier/ scaler is a 33-bit value, which is sign-extended to 40 bits. Integer data is inherently represented as a signed two's complement value, where the MSB is defined as a sign bit. Generally speaking, the range of an N-bit two's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ . For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,645 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two's complement fraction, where the MSB is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two's complement fraction with this implied radix point is -1.0 to  $(1-2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF), including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, a 16x16 multiply operation generates a 1.31 product, which has a precision of 4.65661x10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

# 2.4.2 DATA ACCUMULATORS AND ADDER/SUBTRACTOR

The data accumulator consists of a 40-bit adder/subtractor with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter, prior to accumulation.

# 2.4.2.1 Adder/Subtractor, Overflow and Saturation

The adder/subtractor is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input. In the case of addition, the carry/borrow input is active-high and the other input is true data (not complemented), whereas in the case of subtraction, the carry/borrow input is active-low and the other input is complemented. The adder/subtractor generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS register.

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described above, and the SATA/B (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS register bits have been provided to support saturation and overflow. They are:

- 1. OA: AccA overflowed into guard bits

- OB: AccB overflowed into guard bits

- 3. SA:

AccA saturated (bit 31 overflow and saturation) or

AccA overflowed into guard bits and saturated (bit 39 overflow and saturation)

4. SB:

AccB saturated (bit 31 overflow and saturation) or

AccB overflowed into guard bits and saturated (bit 39 overflow and saturation)

5. OAB:

Logical OR of OA and OB

6. SAB:

Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtractor. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding overflow trap flag enable bit (OVATE, OVBTE) in the INTCON1 register (refer to **Section 5.0 "Interrupts**") is set. This allows the user to take immediate action, for example, to correct system gain.

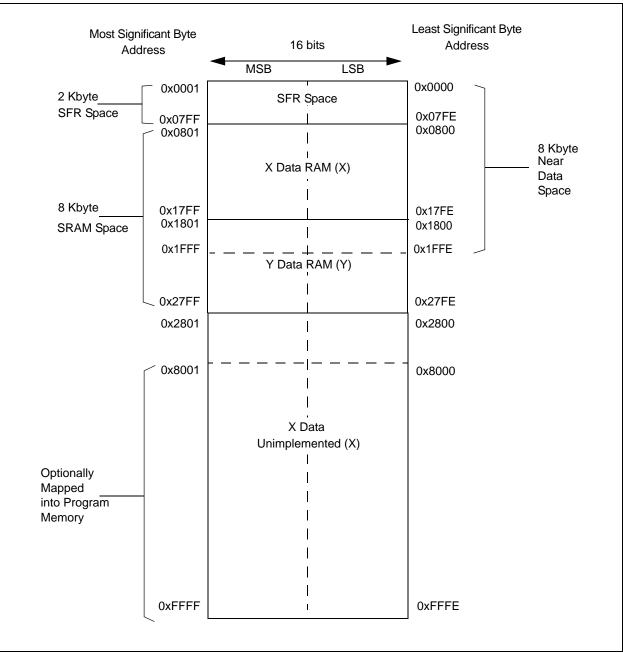

#### FIGURE 3-6: dsPIC30F6010A/6015 DATA SPACE MEMORY MAP

# 6.4 RTSP Operation

The dsPIC30F Flash program memory is organized into rows and panels. Each row consists of 32 instructions, or 96 bytes. Each panel consists of 128 rows, or  $4K \times 24$  instructions. RTSP allows the user to erase one row (32 instructions) at a time and to program 32 instructions at one time.

Each panel of program memory contains write latches that hold 32 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the panel write latches. The data to be programmed into the panel is loaded in sequential order into the write latches; instruction 0, instruction 1, etc. The addresses loaded must always be from a 32 address boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the write latches. Programming is performed by setting the special bits in the NVMCON register. 32 TBLWTL and 32 TBLWTH instructions are required to load the 32 instructions.

All of the table write operations are single-word writes (2 instruction cycles), because only the table latches are written.

After the latches are written, a programming operation needs to be initiated to program the data.

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

### 6.5 RTSP Control Registers

The four SFRs used to read and write the program Flash memory are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

#### 6.5.1 NVMCON REGISTER

The NVMCON register controls which blocks are to be erased, which memory type is to be programmed and start of the programming cycle.

#### 6.5.2 NVMADR REGISTER

The NVMADR register is used to hold the lower two bytes of the Effective Address. The NVMADR register captures the EA<15:0> of the last table instruction that has been executed and selects the row to write.

#### 6.5.3 NVMADRU REGISTER

The NVMADRU register is used to hold the upper byte of the Effective Address. The NVMADRU register captures the EA<23:16> of the last table instruction that has been executed.

#### 6.5.4 NVMKEY REGISTER

NVMKEY is a write-only register that is used for write protection. To start a programming or an erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

Note: The user can also directly write to the NVMADR and NVMADRU registers to specify a program memory address for erasing or programming.

#### 7.3.2 WRITING A BLOCK OF DATA EEPROM

To write a block of data EEPROM, write to all sixteen latches first, then set the NVMCON register and program the block.

| EXAMPLE 7-5:  | DATA EEPROW             |   |                                                            |

|---------------|-------------------------|---|------------------------------------------------------------|

| MOV           | #LOW_ADDR_WORD,W0       | ; | Init pointer                                               |

| MOV           | #HIGH_ADDR_WORD,W1      |   | *                                                          |

| MOV           | W1 TBLPAG               |   |                                                            |

| MOV           | ,<br>#data1,W2          | ; | Get 1st data                                               |

| TBLWTL        | W2 [W0]++               | ; | write data                                                 |

| MOV           | #data2,W2               | ; | Get 2nd data                                               |

| TBLWTL        | W2 [W0]++               | ; | write data                                                 |

| MOV           | #data3,W2               | ; | Get 3rd data                                               |

| TBLWTL        | W2 [W0]++               | ; | write data                                                 |

| MOV           | #data4,W2               | ; | Get 4th data                                               |

| TBLWTL        | W2 [ W0 ] ++            | ; | write data                                                 |

| MOV           | #data5,W2               | ; | Get 5th data                                               |

| TBLWTL        | W2 [ W0 ] ++            | ; | write data                                                 |

| MOV           | #data6,W2               | ; | Get 6th data                                               |

| TBLWTL        | W2 [ W0 ] ++            | ; | write data                                                 |

| MOV           | #data7,W2               | ; | Get 7th data                                               |

| TBLWTL        | W2,[W0]++               | ; | write data                                                 |

| MOV           | #data8,W2               | ; | Get 8th data                                               |

| TBLWTL        | W2 <sub>,</sub> [W0]++  |   | write data                                                 |

| MOV           | #data9,W2               |   | Get 9th data                                               |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data10,W2              |   | Get 10th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data11,W2              |   | Get 11th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data12,W2              |   | Get 12th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data13,W2              |   | Get 13th data                                              |

| TBLWTL        | W2,[W0]++               |   | write data                                                 |

| MOV           | #data14,W2              |   | Get 14th data                                              |

| TBLWTL        | W2 [ W0 ] ++            |   | write data                                                 |

| MOV           | #data15,W2              |   | Get 15th data                                              |

| TBLWTL        | W2 [ W0 ] ++            |   | write data<br>Get 16th data                                |

| MOV<br>TBLWTL | #data16,W2              |   | write data. The NVMADR captures last table access address. |

|               | W2,[W0]++               |   | Select data EEPROM for multi word op                       |

| MOV<br>MOV    | #0x400A,W0<br>W0 NVMCON |   | Operate Key to allow program operation                     |

| DISI          | #5                      |   | Block all interrupts with priority <7                      |

| DISI          | #5                      |   | for next 5 instructions                                    |

| MOV           | #0x55,W0                | ' |                                                            |

| MOV           | WONVMKEY                | ; | Write the 0x55 key                                         |

| MOV           | #0xAA,W1                | - |                                                            |

| MOV           | W1 NVMKEY               | ; | Write the OxAA key                                         |

| BSET          | ,<br>NVMCON, #WR        |   | Start write cycle                                          |

| NOP           |                         |   | -                                                          |

| NOP           |                         |   |                                                            |

|               |                         |   |                                                            |

#### EXAMPLE 7-5: DATA EEPROM BLOCK WRITE

### 7.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 7.5 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared; also, the Power-up Timer prevents EEPROM write.

The write initiate sequence and the WREN bit together, help prevent an accidental write during brown-out, power glitch or software malfunction.

# 13.1 Timer2 and Timer3 Selection Mode

Each output compare channel can select between one of two 16-bit timers; Timer2 or Timer3.

The selection of the timers is controlled by the OCTSEL bit (OCxCON<3>). Timer2 is the default timer resource for the Output Compare module.

#### 13.2 Simple Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 001, 010 or 011, the selected output compare channel is configured for one of three simple output compare match modes:

- Compare forces I/O pin low

- Compare forces I/O pin high

- Compare toggles I/O pin

The OCxR register is used in these modes. The OCxR register is loaded with a value and is compared to the selected incrementing timer count. When a compare occurs, one of these compare match modes occurs. If the counter resets to zero before reaching the value in OCxR, the state of the OCx pin remains unchanged.

### 13.3 Dual Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 100 or 101, the selected output compare channel is configured for one of two Dual Output Compare modes, which are:

- Single Output Pulse mode

- Continuous Output Pulse mode

#### 13.3.1 SINGLE PULSE MODE

For the user to configure the module for the generation of a single output pulse, the following steps are required (assuming timer is off):

- Determine instruction cycle time Tcy.

- Calculate desired pulse-width value based on Tcy.

- Calculate time to start pulse from timer start value of 0x0000.

- Write pulse-width start and stop times into OCxR and OCxRS Compare registers (x denotes channel 1, 2, ...,N).

- Set Timer Period register to value equal to, or greater than, value in OCxRS Compare register.

- Set OCM<2:0> = 100.

- Enable timer, TON (TxCON<15>) = 1.

To initiate another single pulse, issue another write to set OCM<2:0> = 100.

#### 13.3.2 CONTINUOUS PULSE MODE

For the user to configure the module for the generation of a continuous stream of output pulses, the following steps are required:

- Determine instruction cycle time Tcy.

- Calculate desired pulse value based on Tcy.

- Calculate timer to start pulse width from timer start value of 0x0000.

- Write pulse-width start and stop times into OCxR and OCxRS (x denotes channel 1, 2, ...,N) Compare registers, respectively.

- Set Timer Period register to value equal to, or greater than, value in OCxRS Compare register.

- Set OCM<2:0> = 101.

- Enable timer, TON (TxCON<15>) = 1.

### 13.4 Simple PWM Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 110 or 111, the selected output compare channel is configured for the PWM mode of operation. When configured for the PWM mode of operation, OCxR is the main latch (read-only) and OCxRS is the secondary latch. This enables glitchless PWM transitions.

The user must perform the following steps in order to configure the output compare module for PWM operation:

- 1. Set the PWM period by writing to the appropriate period register.

- 2. Set the PWM duty cycle by writing to the OCxRS register.

- 3. Configure the output compare module for PWM operation.

- 4. Set the TMRx prescale value and enable the Timer, TON (TxCON<15>) = 1.

#### 13.4.1 INPUT PIN FAULT PROTECTION FOR PWM

When control bits OCM<2:0> (OCxCON<2:0>) = 111, the selected output compare channel is again configured for the PWM mode of operation, with the additional feature of input Fault protection. While in this mode, if a logic '0' is detected on the OCFA/B pin, the respective PWM output pin is placed in the highimpedance input state. The OCFLT bit (OCxCON<4>) indicates whether a Fault condition has occurred. This state will be maintained until both of the following events have occurred:

- The external Fault condition has been removed.

- The PWM mode has been re-enabled by writing to the appropriate control bits.

#### 14.4 Programmable Digital Noise Filters

The digital noise filter section is responsible for rejecting noise on the incoming quadrature signals. Schmitt Trigger inputs and a three-clock cycle delay filter combine to reject low level noise and large, short duration noise spikes that typically occur in noise prone applications, such as a motor system.

The filter ensures that the filtered output signal is not permitted to change until a stable value has been registered for three consecutive clock cycles.

For the QEA, QEB and INDX pins, the clock divide frequency for the digital filter is programmed by bits QECK<2:0> (DFLTCON<6:4>) and are derived from the base instruction cycle TcY.

To enable the filter output for channels QEA, QEB and INDX, the QEOUT bit must be '1'. The filter network for all channels is disabled on POR and BOR.

# 14.5 Alternate 16-bit Timer/Counter

When the QEI module is not configured for the QEI mode QEIM<2:0> = 001, the module can be configured as a simple 16-bit timer/counter. The setup and control of the auxiliary timer is accomplished through the QEI-CON SFR register. This timer functions identically to Timer1. The QEA pin is used as the timer clock input.

When configured as a timer, the POSCNT register serves as the Timer Count register and the MAXCNT register serves as the Period register. When a Timer/ Period register match occur, the QEI interrupt flag will be asserted.

The only exception between the general purpose timers and this timer is the added feature of external up/down input select. When the UPDN pin is asserted high, the timer will increment up. When the UPDN pin is asserted low, the timer will be decremented.

Note: Changing the operational mode (i.e., from QEI to Timer or vice versa), will not affect the Timer/Position Count register contents.

The UPDN control/Status bit (QEICON<11>) can be used to select the count direction state of the Timer register. When UPDN = 1, the timer will count up. When UPDN = 0, the timer will count down.

In addition, control bit, UDSRC (QEICON<0>), determines whether the timer count direction state is based on the logic state, written into the UPDN control/Status bit (QEICON<11>), or the QEB pin state. When UDSRC = 1, the timer count direction is controlled from the QEB pin. Likewise, when UDSRC = 0, the timer count direction is controlled by the UPDN bit.

**Note:** This Timer does not support the External Asynchronous Counter mode of operation. If using an external clock source, the clock will automatically be synchronized to the internal instruction cycle.

### 14.6 QEI Module Operation During CPU Sleep Mode

#### 14.6.1 QEI OPERATION DURING CPU SLEEP MODE

The QEI module will be halted during the CPU Sleep mode.

#### 14.6.2 TIMER OPERATION DURING CPU SLEEP MODE

During CPU Sleep mode, the timer will not operate, because the internal clocks are disabled.

#### 14.7 QEI Module Operation During CPU Idle Mode

Since the QEI module can function as a Quadrature Encoder Interface, or as a 16-bit timer, the following section describes operation of the module in both modes.

# 14.7.1 QEI OPERATION DURING CPU IDLE MODE

When the CPU is placed in the Idle mode, the QEI module will operate if the QEISIDL bit (QEICON<13>) = 0. This bit defaults to a logic '0' upon executing POR and BOR. For halting the QEI module during the CPU Idle mode, QEISIDL should be set to '1'.

### 15.6 Complementary PWM Operation

In the Complementary mode of operation, each pair of PWM outputs is obtained by a complementary PWM signal. A dead time may be optionally inserted during device switching, when both outputs are inactive for a short period (Refer to **Section 15.7 "Dead-Time Generators"**).

In Complementary mode, the duty cycle comparison units are assigned to the PWM outputs as follows:

- PDC1 register controls PWM1H/PWM1L outputs

- PDC2 register controls PWM2H/PWM2L outputs

- PDC3 register controls PWM3H/PWM3L outputs

- PDC4 register controls PWM4H/PWM4L outputs

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in the PWMCON1 SFR. The PWM I/O pins are set to Complementary mode by default upon a device Reset.

#### 15.7 Dead-Time Generators

Dead-time generation may be provided when any of the PWM I/O pin pairs are operating in the Complementary Output mode. The PWM outputs use Push-Pull drive circuits. Due to the inability of the power output devices to switch instantaneously, some amount of time must be provided between the turn off event of one PWM output in a complementary pair and the turn on event of the other transistor.

The PWM module allows two different dead times to be programmed. These two dead times may be used in one of two methods described below to increase user flexibility:

- The PWM output signals can be optimized for different turn off times in the high side and low side transistors in a complementary pair of transistors. The first dead time is inserted between the turn off event of the lower transistor of the complementary pair and the turn on event of the upper transistor. The second dead time is inserted between the turn off event of the upper transistor and the turn on event of the lower transistor.

- The two dead times can be assigned to individual PWM I/O pin pairs. This Operating mode allows the PWM module to drive different transistor/load combinations with each complementary PWM I/O pin pair.

#### 15.7.1 DEAD-TIME GENERATORS

Each complementary output pair for the PWM module has a 6-bit down counter that is used to produce the dead-time insertion. As shown in Figure 15-4, each dead-time unit has a rising and falling edge detector connected to the duty cycle comparison output.

#### 15.7.2 DEAD-TIME ASSIGNMENT

The DTCON2 SFR contains control bits that allow the dead times to be assigned to each of the complementary outputs. Table 15-1 summarizes the function of each dead-time selection control bit.

|  | TABLE 15-1: | DEAD-TIME SELECTION BITS |

|--|-------------|--------------------------|

|--|-------------|--------------------------|

| Bit   | Selects                              |

|-------|--------------------------------------|

| DTS1A | PWM1L/PWM1H active edge dead time.   |

| DTS1I | PWM1L/PWM1H inactive edge dead time. |

| DTS2A | PWM2L/PWM2H active edge dead time.   |

| DTS2I | PWM2L/PWM2H inactive edge dead time. |

| DTS3A | PWM3L/PWM3H active edge dead time.   |

| DTS3I | PWM3L/PWM3H inactive edge dead time. |

| DTS4A | PWM4L/PWM4H active edge dead time.   |

| DTS4I | PWM4L/PWM4H inactive edge dead time. |

#### 15.7.3 DEAD-TIME RANGES

The amount of dead time provided by each dead-time unit is selected by specifying the input clock prescaler value and a 6-bit unsigned value. The amount of dead time provided by each unit may be set independently.

Four input clock prescaler selections have been provided to allow a suitable range of dead times, based on the device operating frequency. The clock prescaler option may be selected independently for each of the two dead-time values. The dead-time clock prescaler values are selected using the DTAPS<1:0> and DTBPS<1:0> control bits in the DTCON1 SFR. One of four clock prescaler options (Tcy, 2 Tcy, 4 Tcy or 8 Tcy) may be selected for each of the dead-time values.

After the prescaler values are selected, the dead time for each unit is adjusted by loading two 6-bit unsigned values into the DTCON1 SFR.

The dead-time unit prescalers are cleared on the following events:

- On a load of the down timer due to a duty cycle comparison edge event.

- On a write to the DTCON1 or DTCON2 registers.

- On any device Reset.

Note: The user should not modify the DTCON1 or DTCON2 values while the PWM module is operating (PTEN = 1). Unexpected results may occur.

# 20.1 A/D Result Buffer

The module contains a 16-word dual port, read-only buffer, called ADCBUF0...ADCBUFF, to buffer the A/D results. The RAM is 10-bits wide, but is read into different format 16-bit words. The contents of the sixteen A/D Conversion Result Buffer registers, ADCBUF0 through ADCBUFF, cannot be written by user software.

# 20.2 Conversion Operation

After the A/D module has been configured, the sample acquisition is started by setting the SAMP bit. Various sources, such as a programmable bit, timer time-outs and external events, will terminate acquisition and start a conversion. When the A/D conversion is complete, the result is loaded into ADCBUF0...ADCBUFF, and the A/D Interrupt Flag ADIF and the DONE bit are set after the number of samples specified by the SMPI bit.

The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O

- Select A/D input channels

- Select A/D conversion clock

- Select A/D conversion trigger

- Turn on A/D module

- 2. Configure A/D interrupt (if required):

- Clear ADIF bit

- Select A/D interrupt priority

- 3. Start sampling.

- 4. Wait the required acquisition time.

- 5. Trigger acquisition end, start conversion

- 6. Wait for A/D conversion to complete, by either:Waiting for the A/D interrupt

- 7. Read A/D result buffer, clear ADIF if required.

# 20.3 Selecting the Conversion Sequence

Several groups of control bits select the sequence in which the A/D connects inputs to the sample/hold channels, converts channels, writes the buffer memory, and generates interrupts. The sequence is controlled by the sampling clocks.

The SIMSAM bit controls the acquire/convert sequence for multiple channels. If the SIMSAM bit is '0', the two or four selected channels are acquired and converted sequentially, with two or four sample clocks. If the SIMSAM bit is '1', two or four selected channels are acquired simultaneously, with one sample clock. The channels are then converted sequentially. Obviously, if there is only 1 channel selected, the SIMSAM bit is not applicable.

The CHPS bits selects how many channels are sampled. This can vary from 1, 2 or 4 channels. If CHPS selects 1 channel, the CH0 channel will be sampled at the sample clock and converted. The result is stored in the buffer. If CHPS selects 2 channels, the CH0 and CH1 channels will be sampled and converted. If CHPS selects 4 channels, the CH0, CH1, CH2 and CH3 channels will be sampled and converted.

The SMPI bits select the number of acquisition/conversion sequences that would be performed before an interrupt occurs. This can vary from 1 sample per interrupt to 16 samples per interrupt.

The user cannot program a combination of CHPS and SMPI bits that specifies more than 16 conversions per interrupt, or 8 conversions per interrupt, depending on the BUFM bit. The BUFM bit, when set, will split the 16-word results buffer (ADCBUF0...ADCBUFF) into two 8-word groups. Writing to the 8-word buffers will be alternated on each interrupt event. Use of the BUFM bit will depend on how much time is available for moving data out of the buffers after the interrupt, as determined by the application.

If the processor can quickly unload a full buffer within the time it takes to acquire and convert one channel, the BUFM bit can be '0' and up to 16 conversions may be done per interrupt. The processor will have one sample and conversion time to move the sixteen conversions.

If the processor cannot unload the buffer within the acquisition and conversion time, the BUFM bit should be '1'. For example, if SMPI<3:0> (ADCON2<5:2> = 0111), then eight conversions will be loaded into 1/2 of the buffer, following which an interrupt occurs. The next eight conversions will be loaded into the other 1/2 of the buffer. The processor will have the entire time between interrupts to move the eight conversions.

The ALTS bit can be used to alternate the inputs selected during the sampling sequence. The input multiplexer has two sets of sample inputs: MUX A and MUX B. If the ALTS bit is '0', only the MUX A inputs are selected for sampling. If the ALTS bit is '1' and SMPI<3:0> = 0000, on the first sample/convert sequence, the MUX A inputs are selected, and on the next acquire/convert sequence, the MUX B inputs are selected.

The CSCNA bit (ADCON2<10>) will allow the CH0 channel inputs to be alternately scanned across a selected number of analog inputs for the MUX A group. The inputs are selected by the ADCSSL register. If a particular bit in the ADCSSL register is '1', the corresponding input is selected. The inputs are always scanned from lower to higher numbered inputs, starting after each interrupt. If the number of inputs selected is greater than the number of samples taken per interrupt, the higher numbered inputs are unused.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions, but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction, require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double word moves require two cycles. The double word instructions execute in two instruction cycles.

| Note: | For more deta   | ails on the instr | ruction set, |

|-------|-----------------|-------------------|--------------|

|       | refer to the "1 | 6-bit MCU and     | DSC Pro-     |

|       | grammer's       | Reference         | Manual"      |

|       | (DS70157).      |                   |              |

| Field           | Description                                                                      |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------|--|--|--|--|

| #text           | Means literal defined by "text"                                                  |  |  |  |  |

| (text)          | Means "content of text"                                                          |  |  |  |  |

| [text]          | Means "the location addressed by text"                                           |  |  |  |  |

| { }             | Optional field or operation                                                      |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                               |  |  |  |  |

| .b              | Byte mode selection                                                              |  |  |  |  |

| .d              | Double Word mode selection                                                       |  |  |  |  |

| .S              | Shadow register select                                                           |  |  |  |  |

| .w              | Word mode selection (default)                                                    |  |  |  |  |

| Acc             | One of two accumulators {A, B}                                                   |  |  |  |  |

| AWB             | Accumulator Write-Back Destination Address register ∈ {W13, [W13]+ = 2}          |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$    |  |  |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Zero                    |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                   |  |  |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                           |  |  |  |  |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                             |  |  |  |  |

| lit4            | 4-bit unsigned literal ∈ {015}                                                   |  |  |  |  |

| lit5            | 5-bit unsigned literal ∈ {031}                                                   |  |  |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                  |  |  |  |  |

| lit10           | 10-bit unsigned literal $\in \{0255\}$ for Byte mode, $\{0:1023\}$ for Word mode |  |  |  |  |

| lit14           | 14-bit unsigned literal ∈ {016384}                                               |  |  |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                               |  |  |  |  |

| lit23           | 23-bit unsigned literal $\in \{08388608\}$ ; LSB must be '0'                     |  |  |  |  |

| None            | Field does not require an entry, may be blank                                    |  |  |  |  |

| OA, OB, SA, SB  | DSP Status bits: AccA Overflow, AccB Overflow, AccA Saturate, AccB Saturate      |  |  |  |  |

| PC              | Program Counter                                                                  |  |  |  |  |

| Slit10          | 10-bit signed literal $\in$ {-512511}                                            |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                            |  |  |  |  |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                   |  |  |  |  |

### 23.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 23.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 23.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 23.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 23.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### TABLE 24-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACT         | FRISTICS                  |     | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) |                                                                                                        |         |                |  |  |

|--------------------|---------------------------|-----|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------|----------------|--|--|

| DC CHARACTERISTICS |                           |     | Operating te                                                          | Operating temperature         -40°C ≤TA ≤+85°C for Industrial           -40°C ≤TA ≤+125°C for Extended |         |                |  |  |

| Parameter<br>No.   | Typical <sup>(1)</sup>    | Мах | Units                                                                 |                                                                                                        | ditions |                |  |  |

| Operating Cur      | rent (IDD) <sup>(2)</sup> |     |                                                                       |                                                                                                        |         |                |  |  |

| DC31a              | 9.5                       | 15  | mA                                                                    | 25°C                                                                                                   |         |                |  |  |

| DC31b              | 9.5                       | 15  | mA                                                                    | 85°C                                                                                                   | 3.3V    |                |  |  |

| DC31c              | 9.4                       | 15  | mA                                                                    | 125°C                                                                                                  |         | 0.128 MIPS     |  |  |

| DC31e              | 18                        | 27  | mA                                                                    | 25°C                                                                                                   |         | LPRC (512 kHz) |  |  |

| DC31f              | 17                        | 27  | mA                                                                    | 85°C                                                                                                   | 5∨      |                |  |  |

| DC31g              | 17                        | 27  | mA                                                                    | 125°C                                                                                                  | ]       |                |  |  |

| DC30a              | 15                        | 23  | mA                                                                    | 25°C                                                                                                   |         |                |  |  |

| DC30b              | 15                        | 23  | mA                                                                    | 85°C                                                                                                   | 3.3V    |                |  |  |

| DC30c              | 14                        | 23  | mA                                                                    | 125°C                                                                                                  | ]       | (1.8 MIPS)     |  |  |

| DC30e              | 30                        | 45  | mA                                                                    | 25°C                                                                                                   |         | FRC (7.37 MHz) |  |  |

| DC30f              | 29                        | 45  | mA                                                                    | 85°C                                                                                                   | 5V      |                |  |  |

| DC30g              | 27                        | 45  | mA                                                                    | 125°C                                                                                                  |         |                |  |  |

| DC23a              | 40                        | 50  | mA                                                                    | 25°C                                                                                                   |         |                |  |  |

| DC23b              | 40                        | 50  | mA                                                                    | 85°C                                                                                                   | 3.3V    | 4 MIPS         |  |  |

| DC23c              | 36                        | 50  | mA                                                                    | 125°C                                                                                                  |         |                |  |  |

| DC23e              | 44                        | 64  | mA                                                                    | 25°C                                                                                                   |         |                |  |  |

| DC23f              | 43                        | 64  | mA                                                                    | 85°C                                                                                                   | 5V      |                |  |  |

| DC23g              | 43                        | 64  | mA                                                                    | 125°C                                                                                                  |         |                |  |  |

| DC24a              | 50                        | 75  | mA                                                                    | 25°C                                                                                                   |         |                |  |  |

| DC24b              | 51                        | 75  | mA                                                                    | 85°C                                                                                                   | 3.3V    |                |  |  |

| DC24c              | 51                        | 75  | mA                                                                    | 125°C                                                                                                  | ]       |                |  |  |

| DC24e              | 85                        | 125 | mA                                                                    | 25°C                                                                                                   |         | 10 MIPS        |  |  |

| DC24f              | 84                        | 125 | mA                                                                    | 85°C                                                                                                   | 5V      |                |  |  |

| DC24g              | 84                        | 125 | mA                                                                    | 125°C                                                                                                  | ]       |                |  |  |

| DC27a              | 89                        | 115 | mA                                                                    | 25°C                                                                                                   | 2.21/   |                |  |  |

| DC27b              | 89                        | 115 | mA                                                                    | 85°C                                                                                                   | 3.3V    |                |  |  |

| DC27d              | 147                       | 185 | mA                                                                    | 25°C                                                                                                   |         | 20 MIPS        |  |  |

| DC27e              | 146                       | 185 | mA                                                                    | 85°C                                                                                                   | 5V      |                |  |  |

| DC27f              | 145                       | 185 | mA                                                                    | 125°C                                                                                                  | ]       |                |  |  |

| DC29a              | 206                       | 255 | mA                                                                    | 25°C                                                                                                   | E)/     |                |  |  |

| DC29b              | 205                       | 255 | mA                                                                    | 85°C                                                                                                   | 5V      | 30 MIPS        |  |  |

**Note 1:** Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption. The test conditions for all IDD measurements are as follows: OSC1 driven with external square wave from rail-to-rail. All I/O pins are configured as Inputs and pulled to VDD. MCLR = VDD, WDT, FSCM, LVD and BOR are disabled. CPU, SRAM, Program Memory and Data Memory are operational. No peripheral modules are operating.

| TABLE 24-15: | PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.5 TO 5.5 V) |  |

|--------------|------------------------------------------------------|--|

|--------------|------------------------------------------------------|--|

| АС СНА       | RACTERIS | STICS                | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                  |                    |                     |       |                                   |

|--------------|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|---------------------|-------|-----------------------------------|

| Param<br>No. | Symbol   | Characterist         | ic <sup>(1)</sup>                                                                                                                                                                        | Min              | Тур <sup>(2)</sup> | Мах                 | Units | Conditions                        |

| OS50         | Fplli    | PLL Input Frequency  | <sup>,</sup> Range <sup>(2)</sup>                                                                                                                                                        | 4                |                    | 10                  | MHz   | EC with 4x PLL                    |

|              |          |                      |                                                                                                                                                                                          | 4                | _                  | 10                  | MHz   | EC with 8x PLL                    |

|              |          |                      |                                                                                                                                                                                          | 4                | —                  | 7.5 <sup>(4)</sup>  | MHz   | EC with 16x PLL                   |

|              |          |                      |                                                                                                                                                                                          | 4                | _                  | 10                  | MHz   | XT with 4x PLL                    |

|              |          |                      |                                                                                                                                                                                          | 4                | —                  | 10                  | MHz   | XT with 8x PLL                    |

|              |          |                      |                                                                                                                                                                                          | 4                | —                  | 7.5 <sup>(4)</sup>  | MHz   | XT with 16x PLL                   |

|              |          |                      |                                                                                                                                                                                          | 5 <sup>(3)</sup> | —                  | 10                  | MHz   | HS/2 with 4x PLL                  |

|              |          |                      |                                                                                                                                                                                          | 5 <b>(3)</b>     | —                  | 10                  | MHz   | HS/2 with 8x PLL                  |

|              |          |                      |                                                                                                                                                                                          | 5 <sup>(3)</sup> | _                  | 7.5 <sup>(4)</sup>  | MHz   | HS/2 with 16x PLL                 |

|              |          |                      |                                                                                                                                                                                          | 4                | _                  | 8.33 <sup>(3)</sup> | MHz   | HS/3 with 4x PLL                  |

|              |          |                      |                                                                                                                                                                                          | 4                | —                  | 8.33 <sup>(3)</sup> | MHz   | HS/3 with 8x PLL                  |

|              |          |                      |                                                                                                                                                                                          | 4                | —                  | 7.5 <sup>(4)</sup>  | MHz   | HS/3 with 16x PLL                 |

| OS51         | Fsys     | On-Chip PLL Output   | (2)                                                                                                                                                                                      | 16               | _                  | 120                 | MHz   | EC, XT, HS/2, HS/3 modes with PLL |

|              |          |                      |                                                                                                                                                                                          |                  |                    |                     |       |                                   |

| OS52         | TLOC     | PLL Start-up Time (L | ock lime)                                                                                                                                                                                | —                | 20                 | 50                  | μs    | —                                 |

$\label{eq:Note 1: These parameters are characterized but not tested in manufacturing.$

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** Limited by oscillator frequency range.

4: Limited by device operating frequency range.

#### TABLE 24-16: PLL JITTER

| AC CHAI      | RACTERISTICS   | (unless | d Operat<br>otherwis | se stated | )<br>-40°C | 2.5V to 5.5V<br>C ≤TA ≤+85°C for Industr<br>C ≤TA ≤+125°C for Exter |                   |  |

|--------------|----------------|---------|----------------------|-----------|------------|---------------------------------------------------------------------|-------------------|--|

| Param<br>No. | Characteristic | Min     | Typ <sup>(1)</sup>   | Max       | Units      | Conditions                                                          |                   |  |

| OS61         | x4 PLL         |         | 0.251                | 0.413     | %          | -40°C ≤TA ≤+85°C                                                    | VDD = 3.0 to 3.6V |  |

|              |                | —       | 0.251                | 0.413     | %          | -40°C ≤TA ≤+125°C                                                   | VDD = 3.0 to 3.6V |  |

|              |                | —       | 0.256                | 0.47      | %          | -40°C ≤TA ≤+85°C                                                    | VDD = 4.5 to 5.5V |  |

|              |                | —       | 0.256                | 0.47      | %          | -40°C ≤TA ≤+125°C                                                   | VDD = 4.5 to 5.5V |  |

|              | x8 PLL         | —       | 0.355                | 0.584     | %          | -40°C ≤TA ≤+85°C                                                    | VDD = 3.0 to 3.6V |  |

|              |                | —       | 0.355                | 0.584     | %          | -40°C ≤TA ≤+125°C                                                   | VDD = 3.0 to 3.6V |  |

|              |                | —       | 0.362                | 0.664     | %          | -40°C ≤TA ≤+85°C                                                    | VDD = 4.5 to 5.5V |  |

|              |                | —       | 0.362                | 0.664     | %          | -40°C ≤TA ≤+125°C                                                   | VDD = 4.5 to 5.5V |  |

|              | x16 PLL        |         | 0.67                 | 0.92      | %          | -40°C ≤TA ≤+85°C                                                    | VDD = 3.0 to 3.6V |  |

|              |                | —       | 0.632                | 0.956     | %          | -40°C ≤TA ≤+85°C                                                    | VDD = 4.5 to 5.5V |  |

|              |                | _       | 0.632                | 0.956     | %          | -40°C ≤TA ≤+125°C                                                   | VDD = 4.5 to 5.5V |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

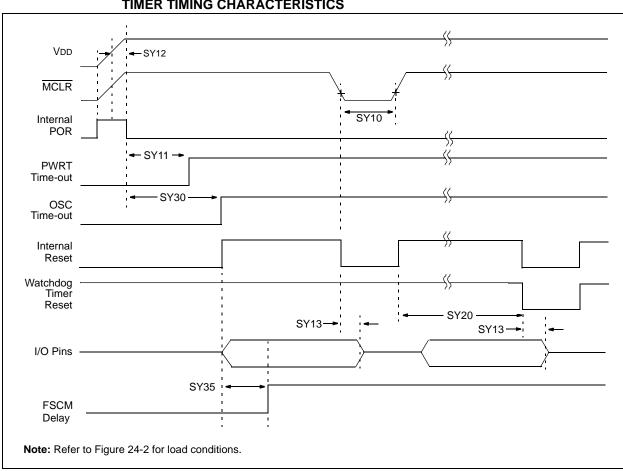

# FIGURE 24-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

#### TABLE 24-24: TIMER2 AND TIMER4 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                   |                                                                | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                                         |     |         |       |                               |  |

|--------------------|-----------|-------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-------|-------------------------------|--|

| Param<br>No.       | Symbol    | Characte          | Characteristic                                                 |                                                                                                                                                                                                          |                                         | Тур | Max     | Units | Conditions                    |  |

| TB10               | TtxH      | TxCK High Time    | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                                                                          | 0.5 TCY + 20                            |     |         | ns    | Must also meet parameter TB15 |  |

|                    |           |                   |                                                                |                                                                                                                                                                                                          | 10                                      |     | _       | ns    |                               |  |

| TB11               | TtxL      | TxCK Low Time     | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                                                                          | 0.5 TCY + 20                            |     |         | ns    | Must also meet parameter TB15 |  |

|                    |           |                   |                                                                |                                                                                                                                                                                                          | 10                                      |     | —       | ns    |                               |  |

| TB15               | TtxP      | TxCK Input Period | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                                                                          | Tcy + 10                                |     | —       | ns    | N = prescale<br>value         |  |

|                    |           |                   |                                                                |                                                                                                                                                                                                          | Greater of:<br>20 ns or<br>(TcY + 40)/N |     |         |       | (1, 8, 64, 256)               |  |

| TB20               | TCKEXTMRL |                   | y from External TxCK Clock<br>e to Timer Increment             |                                                                                                                                                                                                          |                                         |     | 1.5 TCY | _     | _                             |  |

#### TABLE 24-25: TIMER3 AND TIMER5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                           |                                                                          | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                                         |     |            |            |                               |  |

|--------------------|-----------|-----------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|------------|------------|-------------------------------|--|

| Param<br>No.       | Symbol    | Characte                                                  |                                                                          | Min                                                                                                                                                                                      | Тур                                     | Max | Units      | Conditions |                               |  |

| TC10               | TtxH      | TxCK High Time                                            | Synchronous                                                              |                                                                                                                                                                                          | 0.5 TCY + 20                            |     |            | ns         | Must also meet parameter TC15 |  |

| TC11               | TtxL      | TxCK Low Time                                             | Synchronous                                                              |                                                                                                                                                                                          | 0.5 Tcy + 20                            |     | _          | ns         | Must also meet parameter TC15 |  |

| TC15               | TtxP      | TxCK Input Period                                         | ut Period Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                                                          | Tcy + 10                                | -   | _          | ns         | N = prescale<br>value         |  |

|                    |           |                                                           |                                                                          |                                                                                                                                                                                          | Greater of:<br>20 ns or<br>(Tcy + 40)/N |     |            |            | (1, 8, 64, 256)               |  |

| TC20               | TCKEXTMRL | Delay from External TxCK Clock<br>Edge to Timer Increment |                                                                          |                                                                                                                                                                                          | 0.5 TCY                                 | _   | 1.5<br>Тсү | _          | —                             |  |

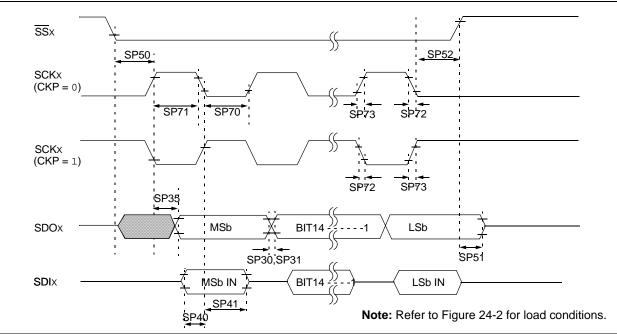

#### FIGURE 24-18: SPI MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 24-35: SPI MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                      |                                                      | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                    |  |

|--------------------|--------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|--|

| Param<br>No.       | Symbol Characteristic <sup>(1)</sup> |                                                      | Min                                                                                                                                                                                      | Тур <sup>(2)</sup> | Max | Units | Conditions         |  |

| SP70               | TscL                                 | SCKx Input Low Time                                  | 30                                                                                                                                                                                       | —                  | _   | ns    | —                  |  |

| SP71               | TscH                                 | SCKx Input High Time                                 | 30                                                                                                                                                                                       | —                  | _   | ns    | —                  |  |

| SP72               | TscF                                 | SCKx Input Fall Time <sup>(3)</sup>                  |                                                                                                                                                                                          | 10                 | 25  | ns    | —                  |  |

| SP73               | TscR                                 | SCKx Input Rise Time <sup>(3)</sup>                  | _                                                                                                                                                                                        | 10                 | 25  | ns    | —                  |  |

| SP30               | TdoF                                 | SDOx Data Output Fall Time <sup>(3)</sup>            | _                                                                                                                                                                                        | —                  | —   | ns    | See parameter DO32 |  |

| SP31               | TdoR                                 | SDOx Data Output Rise Time <sup>(3)</sup>            |                                                                                                                                                                                          | _                  | —   | ns    | See parameter DO31 |  |

| SP35               | TscH2doV,<br>TscL2doV                | SDOx Data Output Valid after<br>SCKx Edge            | —                                                                                                                                                                                        | -                  | 30  | ns    | —                  |  |

| SP40               | TdiV2scH,<br>TdiV2scL                | Setup Time of SDIx Data Input to SCKx Edge           | 20                                                                                                                                                                                       | _                  | —   | ns    | —                  |  |

| SP41               | TscH2diL,<br>TscL2diL                | Hold Time of SDIx Data Input to SCKx Edge            | 20                                                                                                                                                                                       | —                  | _   | ns    | —                  |  |

| SP50               | TssL2scH,<br>TssL2scL                | SSx↓to SCKx↑ or SCKx↓Input                           | 120                                                                                                                                                                                      | —                  |     | ns    | —                  |  |

| SP51               | TssH2doZ                             | SSx↑ to SDOx Output<br>High-impedance <sup>(3)</sup> | 10                                                                                                                                                                                       | —                  | 50  | ns    | —                  |  |

| SP52               | TscH2ssH<br>TscL2ssH                 | SSx after SCK Edge                                   | 1.5 Tcy +40                                                                                                                                                                              | —                  |     | ns    | —                  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** Assumes 50 pF load on all SPI pins.

# TABLE 24-37: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |                   |                               |                           | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |      |       |                        |  |  |