# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SLDM, SPI, UART/USART                    |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 93                                                                          |

| Program Memory Size        |                                                                             |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | <u>.</u>                                                                    |

| RAM Size                   | 10K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 128-LQFP                                                                    |

| Supplier Device Package    | PG-TQFP-128-2                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c161jclfcakxqma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2    | Pi         | n Definit      | ions and Fur                                                                                                                                                                                                                                                                                                                                                                                                  | nctions                                                                                                                                                                                                                                             |  |  |  |  |  |

|------------|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol     | Pin<br>No. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                     |  |  |  |  |  |

| RST<br>OUT | 1          | 0              | when the par<br>a watchdog t                                                                                                                                                                                                                                                                                                                                                                                  | Internal Reset Indication Output. This pin is set to a low level<br>when the part is executing either a hardware-, a software- or<br>a watchdog timer reset. RSTOUT remains low until the EINIT<br>(end of initialization) instruction is executed. |  |  |  |  |  |

| NMI        | 2          | 1              | Non-Maskable Interrupt Input. A high to low transition at this pin causes the CPU to vector to the NMI trap routine. When the PWRDN (power down) instruction is executed, the NMI pin must be low in order to force the C161CS/JC/JI to go into power down mode. If NMI is high, when PWRDN is executed, the part will continue to run in normal mode. If not used, pin NMI should be pulled high externally. |                                                                                                                                                                                                                                                     |  |  |  |  |  |

| P6         |            | 10             | Port 6 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 6 outputs can be configured as push/<br>pull or open drain drivers.<br>The Port 6 pins also serve for alternate functions:                                                                   |                                                                                                                                                                                                                                                     |  |  |  |  |  |

| P6.0       | 5          | 0              | ·                                                                                                                                                                                                                                                                                                                                                                                                             | Chip Select 0 Output                                                                                                                                                                                                                                |  |  |  |  |  |

| P6.1       | 6          | 0              |                                                                                                                                                                                                                                                                                                                                                                                                               | Chip Select 1 Output                                                                                                                                                                                                                                |  |  |  |  |  |

| P6.2       | 7          | 0              |                                                                                                                                                                                                                                                                                                                                                                                                               | Chip Select 2 Output                                                                                                                                                                                                                                |  |  |  |  |  |

| P6.3       | 8          | 0              |                                                                                                                                                                                                                                                                                                                                                                                                               | Chip Select 3 Output                                                                                                                                                                                                                                |  |  |  |  |  |

| P6.4       | 9          | 0              |                                                                                                                                                                                                                                                                                                                                                                                                               | Chip Select 4 Output                                                                                                                                                                                                                                |  |  |  |  |  |

| P6.5       | 10         |                |                                                                                                                                                                                                                                                                                                                                                                                                               | External Master Hold Request Input                                                                                                                                                                                                                  |  |  |  |  |  |

| P6.6       | 11         | I/O            |                                                                                                                                                                                                                                                                                                                                                                                                               | Hold Acknowledge Output (master mode)                                                                                                                                                                                                               |  |  |  |  |  |

|            |            |                |                                                                                                                                                                                                                                                                                                                                                                                                               | or Input (slave mode)                                                                                                                                                                                                                               |  |  |  |  |  |

| P6.7       | 12         | 0              | BREQ                                                                                                                                                                                                                                                                                                                                                                                                          | Bus Request Output                                                                                                                                                                                                                                  |  |  |  |  |  |

| Symbol     | Pin<br>No. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Ρ4         |            | IO             | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. The Port 4 outputs can be configured as<br>push/pull or open drain drivers. The input threshold of Port 4<br>is selectable (TTL or special).<br>Port 4 can be used to output the segment address lines and<br>for serial interface lines: <sup>1)</sup> |  |  |  |  |  |

| P4.0       | 70         | 0              | A16 Least Significant Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| P4.1       | 71         | 0              | A17 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| P4.2       | 72         | 0              | A18 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| P4.3       | 73         | 0              | A19 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| P4.4       | 74         | 0              | A20 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|            |            | 1              | CAN2_RxD CAN 2 Receive Data Input, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|            |            | I              | SDL_RxD SDLM Receive Data Input (C161JC/JI)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| P4.5       | 75         | 0              | A21 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|            |            | I              | CAN1_RxD CAN 1 Receive Data Input, (C161CS/JC)                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| P4.6       | 76         | 0              | A22 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|            |            | 0              | CAN1_TxD CAN 1 Transmit Data Output, (C161CS/JC)                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|            |            | 0              | CAN2_TxD CAN 2 Transmit Data Output, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|            |            | I              | SDL_RxD SDLM Receive Data Input (C161JC/JI)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| P4.7       | 77         | 0              | A23 Most Significant Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|            |            | 1              | CAN1_RxD CAN 1 Receive Data Input, (C161CS/JC)                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|            |            | 0              | CAN2_TxD CAN 2 Transmit Data Output, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|            |            |                | CAN2_RxD CAN 2 Receive Data Input, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|            |            | 0              | SDL_TxDSDLM Transmit Data Output(C161JC/JI)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RD         | 80         | 0              | External Memory Read Strobe. $\overline{RD}$ is activated for every external instruction or data read access.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| WR/<br>WRL | 81         | 0              | External Memory Write Strobe. In WR-mode this pin is<br>activated for every external data write access. In WRL-mode<br>this pin is activated for low byte data write accesses on a<br>16-bit bus, and for every data write access on an 8-bit bus.<br>See WRCFG in register SYSCON for mode selection.                                                                                                                                                              |  |  |  |  |  |

| Table 2           | Piı                                                                           | n Definit      | ions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|-------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Pin<br>No.                                                                    | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RSTIN             | 128                                                                           | I/O            | Reset Input with Schmitt-Trigger characteristics. A low level<br>at this pin while the oscillator is running resets the C161CS/<br>JC/JI. An internal pullup resistor permits power-on reset<br>using only a capacitor connected to $V_{SS}$ .<br>A spike filter suppresses input pulses < 10 ns. Input pulses<br>> 100 ns safely pass the filter. The minimum duration for a<br>safe recognition should be 100 ns + 2 CPU clock cycles.<br>In bidirectional reset mode (enabled by setting bit BDRSTEN<br>in register SYSCON) the RSTIN line is internally pulled low<br>for the duration of the internal reset sequence upon any reset<br>(HW, SW, WDT). See note below this table.<br><i>Note: To let the reset configuration of PORTO settle and to</i><br><i>let the PLL lock a reset duration of ca. 1 ms is</i> |

|                   | 05                                                                            |                | recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VAREF             | 35                                                                            | -              | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>AGND</sub> | 36                                                                            | -              | Reference ground for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>DD</sub>   | 4, 18,<br>26 <sup>2)</sup> ,<br>42, 52,<br>68, 78,<br>93, 111,<br>121         | -              | <ul> <li>Digital Supply Voltage:</li> <li>+5 V during normal operation and idle mode.</li> <li>≥ 2.5 V during power down mode if RTC is off</li> <li>≥ 2.7 V during power down mode if RTC is running</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>   | 3, 17,<br>25 <sup>2)</sup> ,<br>41, 51,<br>69, 79,<br>94, 112,<br>122,<br>125 | -              | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

<sup>1)</sup> The CAN and/or SDLM interface lines are assigned to ports P4 and P7 under software control. Within the CAN module or SDLM several assignments can be selected.

<sup>2)</sup> Supply pins 25 and 26 feed the Analog/Digital Converter and should be decoupled separately.

Note: When one or both of the on-chip CAN Modules or the SDLM are used with the interface lines assigned to Port 4, the interface lines override the segment address lines and the segment address output on Port 4 is therefore limited to 6/4 bits i.e. address lines A21/A19 ... A16. CS lines can be used to increase the total amount of addressable external memory.

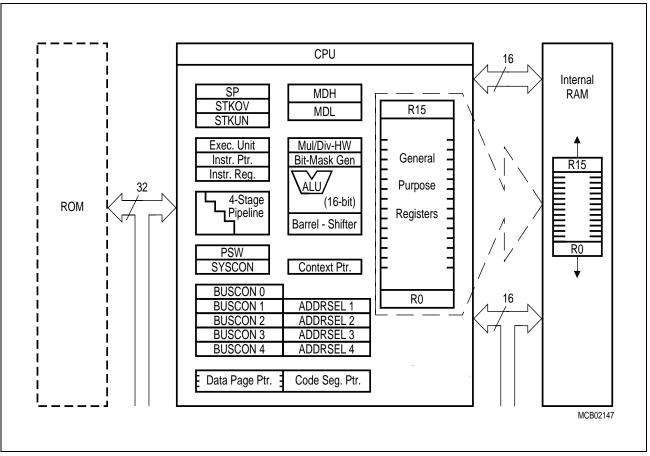

### **Central Processing Unit (CPU)**

The main core of the CPU consists of a 4-stage instruction pipeline, a 16-bit arithmetic and logic unit (ALU) and dedicated SFRs. Additional hardware has been spent for a separate multiply and divide unit, a bit-mask generator and a barrel shifter.

Based on these hardware provisions, most of the C161CS/JC/JI's instructions can be executed in just one machine cycle which requires 80 ns at 25 MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle independent of the number of bits to be shifted. All multiple-cycle instructions have been optimized so that they can be executed very fast as well: branches in 2 cycles, a  $16 \times 16$  bit multiplication in 5 cycles and a 32-/16-bit division in 10 cycles. Another pipeline optimization, the so-called 'Jump Cache', allows reducing the execution time of repeatedly performed jumps in a loop from 2 cycles to 1 cycle.

Figure 4 CPU Block Diagram

#### Interrupt System

With an interrupt response time within a range from just 5 to 12 CPU clocks (in case of internal program execution), the C161CS/JC/JI is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the C161CS/JC/JI supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source or the destination pointer. An individual PEC transfer counter is implicity decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The C161CS/JC/JI has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt sources. Via its related register, each source can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 3** shows all of the possible C161CS/JC/JI interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not used by associated peripherals, may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

#### General Purpose Timer (GPT) Unit

The GPT unit represents a very flexible multifunctional timer/counter structure which may be used for many different time related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT unit incorporates five 16-bit timers which are organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation, which are Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the CPU clock, divided by a programmable prescaler, while Counter Mode allows a timer to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. The maximum resolution of the timers in module GPT1 is 16 TCL.

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD) to facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B via their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals, so the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components, or may be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

#### Serial Channels

Serial communication with other microcontrollers, processors, terminals or external peripheral components is provided by three serial interfaces with different functionality, two Asynchronous/Synchronous Serial Channels (**ASC0/ASC1**) and a High-Speed Synchronous Serial Channel (**SSC**).

**The ASC0** is upward compatible with the serial ports of the Infineon 8-bit microcontroller families and supports full-duplex asynchronous communication at up to 781 kBaud and half-duplex synchronous communication at up to 3.1 MBaud (@ 25 MHz CPU clock).

A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling 4 separate interrupt vectors are provided. In asynchronous mode, 8- or 9-bit data frames are transmitted or received, preceded by a start bit and terminated by one or two stop bits. For multiprocessor communication, a mechanism to distinguish address from data bytes has been included (8-bit data plus wake up bit mode).

In synchronous mode, the ASC0 transmits or receives bytes (8 bits) synchronously to a shift clock which is generated by the ASC0. The ASC0 always shifts the LSB first. A loop back option is available for testing purposes.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. A parity bit can automatically be generated on transmission or be checked on reception. Framing error detection allows to recognize data frames with missing stop bits. An overrun error will be generated, if the last character received has not been read out of the receive buffer register at the time the reception of a new character is complete.

**The ASC1** is function compatible with the ASC0, except that its registers are not bitaddressable (XBUS peripheral) and it provides only three interrupt vectors.

**The SSC** supports full-duplex synchronous communication at up to 6.25 MBaud (@ 25 MHz CPU clock). It may be configured so it interfaces with serially linked peripheral components. A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling three separate interrupt vectors are provided.

The SSC transmits or receives characters of 2 ... 16 bits length synchronously to a shift clock which can be generated by the SSC (master mode) or by an external master (slave mode). The SSC can start shifting with the LSB or with the MSB and allows the selection of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. Transmit and receive error supervise the correct handling of the data buffer. Phase and baudrate error detect incorrect serial data.

#### Table 7 C161CS/JC/JI Registers, Ordered by Name (cont'd)

| Name Physic<br>Addres |                            |                     | 8-Bit<br>Addr.  | Description                         | Reset<br>Value    |

|-----------------------|----------------------------|---------------------|-----------------|-------------------------------------|-------------------|

| CC13IC                | b                          | FF92 <sub>H</sub>   | C9 <sub>H</sub> | CAPCOM Reg. 13 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC14                  |                            | FE9C <sub>H</sub>   | 4E <sub>H</sub> | CAPCOM Register 14                  | 0000 <sub>H</sub> |

| CC14IC                | b                          | FF94 <sub>H</sub>   | CA <sub>H</sub> | CAPCOM Reg. 14 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC15                  |                            | FE9E <sub>H</sub>   | 4F <sub>H</sub> | CAPCOM Register 15                  | 0000 <sub>H</sub> |

| CC15IC                | b                          | FF96 <sub>H</sub>   | CB <sub>H</sub> | CAPCOM Reg. 15 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC16                  |                            | FE60 <sub>H</sub>   | 30 <sub>H</sub> | CAPCOM Register 16                  | 0000 <sub>H</sub> |

| CC16IC                | b                          | F160 <sub>H</sub> E | B0 <sub>H</sub> | CAPCOM Reg.16 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

| CC17                  |                            | FE62 <sub>H</sub>   | 31 <sub>H</sub> | CAPCOM Register 17                  | 0000 <sub>H</sub> |

| CC17IC                | b                          | F162 <sub>H</sub> E | B1 <sub>H</sub> | CAPCOM Reg. 17 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC18                  |                            | FE64 <sub>H</sub>   | 32 <sub>H</sub> | CAPCOM Register 18                  | 0000 <sub>H</sub> |

| CC18IC                | b                          | F164 <sub>H</sub> E | B2 <sub>H</sub> | CAPCOM Reg. 18 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC19                  |                            | FE66 <sub>H</sub>   | 33 <sub>H</sub> | CAPCOM Register 19                  | 0000 <sub>H</sub> |

| CC19IC                | <b>b</b> F166 <sub>H</sub> |                     | B3 <sub>H</sub> | CAPCOM Reg. 19 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC1IC                 | b                          | FF7A <sub>H</sub>   | BD <sub>H</sub> | CAPCOM Reg. 1 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

| CC2                   |                            | FE84 <sub>H</sub>   | 42 <sub>H</sub> | CAPCOM Register 2                   | 0000 <sub>H</sub> |

| CC20                  |                            | FE68 <sub>H</sub>   | 34 <sub>H</sub> | CAPCOM Register 20                  | 0000 <sub>H</sub> |

| CC20IC                | b                          | F168 <sub>H</sub> E | B4 <sub>H</sub> | CAPCOM Reg. 20 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC21                  |                            | FE6A <sub>H</sub>   | 35 <sub>H</sub> | CAPCOM Register 21                  | 0000 <sub>H</sub> |

| CC21IC                | b                          | F16A <sub>H</sub> E | B5 <sub>H</sub> | CAPCOM Reg. 21 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC22                  |                            | FE6C <sub>H</sub>   | 36 <sub>H</sub> | CAPCOM Register 22                  | 0000 <sub>H</sub> |

| CC22IC                | b                          | F16C <sub>H</sub> E | B6 <sub>H</sub> | CAPCOM Reg. 22 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC23                  |                            | FE6E <sub>H</sub>   | 37 <sub>H</sub> | CAPCOM Register 23                  | 0000 <sub>H</sub> |

| CC23IC                | b                          | F16E <sub>H</sub> E | B7 <sub>H</sub> | CAPCOM Reg. 23 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC24                  |                            | FE70 <sub>H</sub>   | 38 <sub>H</sub> | CAPCOM Register 24                  | 0000 <sub>H</sub> |

| CC24IC                | b                          | F170 <sub>H</sub> E | B8 <sub>H</sub> | CAPCOM Reg. 24 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC25                  |                            | FE72 <sub>H</sub>   | 39 <sub>H</sub> | CAPCOM Register 25                  | 0000 <sub>H</sub> |

| CC25IC                | b                          | F172 <sub>H</sub> E | B9 <sub>H</sub> | CAPCOM Reg. 25 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC26                  |                            | FE74 <sub>H</sub>   | 3A <sub>H</sub> | CAPCOM Register 26                  | 0000 <sub>H</sub> |

| CC26IC                | b                          | F174 <sub>H</sub> E | BA <sub>H</sub> | CAPCOM Reg. 26 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC27                  |                            | FE76 <sub>H</sub>   | 3B <sub>H</sub> | CAPCOM Register 27                  | 0000 <sub>H</sub> |

| CC27IC                | b                          | F176 <sub>H</sub> E | BB <sub>H</sub> | CAPCOM Reg. 27 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC28                  |                            | FE78 <sub>H</sub>   | 3C <sub>H</sub> | CAPCOM Register 28                  | 0000 <sub>H</sub> |

#### Table 7 C161CS/JC/JI Registers, Ordered by Name (cont'd)

| Name   |                   | Physica<br>Address     |                                                                           | 8-Bit<br>Addr.  | Description                                                    | Reset<br>Value    |

|--------|-------------------|------------------------|---------------------------------------------------------------------------|-----------------|----------------------------------------------------------------|-------------------|

| RXD18  |                   | EB58 <sub>H</sub>      | Χ                                                                         |                 | SDLM Receive Data Register 18 (bus)                            | 0000 <sub>H</sub> |

| S0BG   | FEB4 <sub>H</sub> |                        |                                                                           | 5A <sub>H</sub> | Serial Channel 0 Baud Rate Generator<br>Reload Register        | 0000 <sub>H</sub> |

| SOCON  | b                 | b FFB0 <sub>H</sub> Da |                                                                           |                 | Serial Channel 0 Control Register                              | 0000 <sub>H</sub> |

| SOEIC  | b                 | FF70 <sub>H</sub>      |                                                                           | B8 <sub>H</sub> | Serial Channel 0 Error Interrupt Ctrl.<br>Reg.                 | 0000 <sub>H</sub> |

| SORBUF |                   | FEB2 <sub>H</sub>      |                                                                           | 59 <sub>H</sub> | Serial Channel 0 Receive Buffer<br>Register (read only)        | XXXX <sub>H</sub> |

| SORIC  | b                 | FF6E <sub>H</sub>      |                                                                           | B7 <sub>H</sub> | Serial Channel 0 Receive Interrupt<br>Control Register         | 0000 <sub>H</sub> |

| SOTBIC | b                 | F19C <sub>H</sub>      | Ε                                                                         | CEH             | Serial Channel 0 Transmit Buffer<br>Interrupt Control Register | 0000 <sub>H</sub> |

| S0TBUF |                   | FEB0 <sub>H</sub>      |                                                                           | 58 <sub>H</sub> | Serial Channel 0 Transmit Buffer<br>Register                   | 0000 <sub>H</sub> |

| SOTIC  | b                 | FF6C <sub>H</sub>      |                                                                           | B6 <sub>H</sub> | Serial Channel 0 Transmit Interrupt<br>Control Register        | 0000 <sub>H</sub> |

| S1BG   |                   | EDA4 <sub>H</sub>      | Χ                                                                         |                 | Serial Channel 1 Baud Rate Generator<br>Reload Register        | 0000 <sub>H</sub> |

| S1CON  |                   | EDA6 <sub>H</sub>      | Χ                                                                         |                 | Serial Channel 1 Control Register                              | 0000 <sub>H</sub> |

| S1RBUF |                   | EDA2 <sub>H</sub>      | Χ                                                                         |                 | Serial Channel 1 Receive Buffer<br>Register (read only)        | XXXX <sub>H</sub> |

| S1TBUF |                   | EDA0 <sub>H</sub>      | Χ                                                                         |                 | Serial Channel 1 Transmit Buffer<br>Register                   | 0000 <sub>H</sub> |

| SOFPTR |                   | EB60 <sub>H</sub>      | Χ                                                                         |                 | SDLM Start-of-Frame Pointer Register                           | 0000 <sub>H</sub> |

| SP     |                   | FE12 <sub>H</sub>      |                                                                           | 09 <sub>H</sub> | CPU System Stack Pointer Register                              | FC00 <sub>H</sub> |

| SSCBR  |                   | F0B4 <sub>H</sub>      | Ε                                                                         | 5A <sub>H</sub> | SSC Baudrate Register                                          | 0000 <sub>H</sub> |

| SSCCON | b                 | FFB2 <sub>H</sub>      |                                                                           | D9 <sub>H</sub> | SSC Control Register                                           | 0000 <sub>H</sub> |

| SSCEIC | b                 | FF76 <sub>H</sub>      |                                                                           | BB <sub>H</sub> | SSC Error Interrupt Control Register                           | 0000 <sub>H</sub> |

| SSCRB  |                   | F0B2 <sub>H</sub>      | Ε                                                                         | 59 <sub>H</sub> | SSC Receive Buffer (read only)                                 | XXXX <sub>H</sub> |

| SSCRIC | b                 | FF74 <sub>H</sub>      |                                                                           | BA <sub>H</sub> | SSC Receive Interrupt Control Register                         | 0000 <sub>H</sub> |

| SSCTB  |                   | F0B0 <sub>H</sub>      | B0 <sub>H</sub> <b>E</b> 58 <sub>H</sub> SSC Transmit Buffer (write only) |                 | SSC Transmit Buffer (write only)                               | 0000 <sub>H</sub> |

| SSCTIC | b                 | FF72 <sub>H</sub>      |                                                                           | B9 <sub>H</sub> | SSC Transmit Interrupt Control Register                        | 0000 <sub>H</sub> |

| STKOV  |                   | FE14 <sub>H</sub>      |                                                                           | 0A <sub>H</sub> | CPU Stack Overflow Pointer Register                            | FA00 <sub>H</sub> |

| STKUN  |                   | FE16 <sub>H</sub>      |                                                                           | 0B <sub>H</sub> | CPU Stack Underflow Pointer Register                           | FC00 <sub>H</sub> |

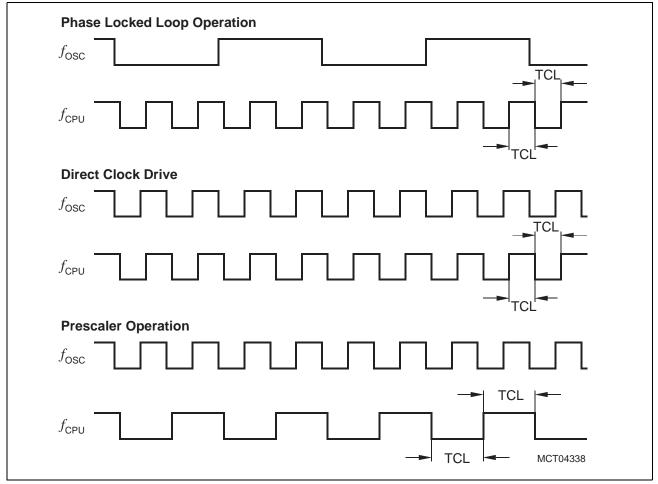

#### AC Characteristics Definition of Internal Timing

The internal operation of the C161CS/JC/JI is controlled by the internal CPU clock  $f_{CPU}$ . Both edges of the CPU clock can trigger internal (e.g. pipeline) or external (e.g. bus cycles) operations.

The specification of the external timing (AC Characteristics) therefore depends on the time between two consecutive edges of the CPU clock, called "TCL" (see Figure 11).

Figure 11 Generation Mechanisms for the CPU Clock

The CPU clock signal  $f_{CPU}$  can be generated from the oscillator clock signal  $f_{OSC}$  via different mechanisms. The duration of TCLs and their variation (and also the derived external timing) depends on the used mechanism to generate  $f_{CPU}$ . This influence must be regarded when calculating the timings for the C161CS/JC/JI.

Note: The example for PLL operation shown in the fig. above refers to a PLL factor of 4.

The used mechanism to generate the basic CPU clock is selected by bitfield CLKCFG in register RP0H.7-5.

Upon a long hardware reset register RP0H is loaded with the logic levels present on the upper half of PORT0 (P0H), i.e. bitfield CLKCFG represents the logic levels on pins

P0.15-13 (P0H.7-5). Register RP0H can be loaded from the upper half of register RSTCON under software control.

**Table 10** associates the combinations of these three bits with the respective clock generation mode.

| CLKCFG<br>(P0H.7-5) | $CPU Frequency f_{CPU} = f_{OSC} \times F$ | External Clock<br>Input Range <sup>1)</sup> | Notes                      |

|---------------------|--------------------------------------------|---------------------------------------------|----------------------------|

| 1 1 1               | $f_{OSC} \times 4$                         | 2.5 to 6.25 MHz                             | Default configuration      |

| 1 1 0               | $f_{OSC} \times 3$                         | 3.33 to 8.33 MHz                            | -                          |

| 1 0 1               | $f_{OSC} \times 2$                         | 5 to 12.5 MHz                               | -                          |

| 1 0 0               | $f_{OSC} \times 5$                         | 2 to 5 MHz                                  | -                          |

| 0 1 1               | $f_{OSC} \times 1$                         | 1 to 25 MHz                                 | Direct drive <sup>2)</sup> |

| 0 1 0               | $f_{OSC} \times 1.5$                       | 6.66 to 16.6 MHz                            | -                          |

| 0 0 1               | f <sub>OSC</sub> / 2                       | 2 to 50 MHz                                 | CPU clock via prescaler    |

| 0 0 0               | $f_{OSC} \times 2.5$                       | 4 to 10 MHz                                 | -                          |

Table 10

C161CS/JC/JI Clock Generation Modes

<sup>1)</sup> The external clock input range refers to a CPU clock range of 10 ... 25 MHz.

<sup>2)</sup> The maximum frequency depends on the duty cycle of the external clock signal.

#### **Prescaler Operation**

When prescaler operation is configured (CLKCFG =  $001_B$ ) the CPU clock is derived from the internal oscillator (input clock signal) by a 2:1 prescaler.

The frequency of  $f_{CPU}$  is half the frequency of  $f_{OSC}$  and the high and low time of  $f_{CPU}$  (i.e. the duration of an individual TCL) is defined by the period of the input clock  $f_{OSC}$ .

The timings listed in the AC Characteristics that refer to TCLs therefore can be calculated using the period of  $f_{OSC}$  for any TCL.

#### Phase Locked Loop

When PLL operation is configured (via CLKCFG) the on-chip phase locked loop is enabled and provides the CPU clock (see table above). The PLL multiplies the input frequency by the factor **F** which is selected via the combination of pins P0.15-13 (i.e.  $f_{CPU} = f_{OSC} \times \mathbf{F}$ ). With every **F**'th transition of  $f_{OSC}$  the PLL circuit synchronizes the CPU clock to the input clock. This synchronization is done smoothly, i.e. the CPU clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{CPU}$  is constantly adjusted so it is locked to  $f_{OSC}$ . The slight variation causes a jitter of  $f_{CPU}$  which also effects the duration of individual TCLs.

#### AC Characteristics External Clock Drive XTAL3 (Auxiliary Oscillator)

(Operating Conditions apply)

| Parameter         | Symbol                |    | Optimum I<br>= 32 kHz | nput Clock | Variable Inpu<br>1 / t <sub>OSCA</sub> = 10 | Unit                  |    |

|-------------------|-----------------------|----|-----------------------|------------|---------------------------------------------|-----------------------|----|

|                   |                       |    | min.                  | max.       | min.                                        | max.                  |    |

| Oscillator period | t <sub>OSCA</sub>     | SR | 31                    | 31         | 20                                          | 100                   | μs |

| High time         | <i>t</i> <sub>1</sub> | SR | 6 <sup>1)</sup>       | _          | $0.2 \times t_{OSCA}^{1)}$                  | _                     | μs |

| Low time          | <i>t</i> <sub>2</sub> | SR | 6 <sup>1)</sup>       | -          | $0.2 \times t_{OSCA}^{1)}$                  | -                     | μs |

| Rise time         | t <sub>3</sub>        | SR | -                     | 12         | -                                           | $0.4 \times t_{OSCA}$ | μs |

| Fall time         | <i>t</i> <sub>4</sub> | SR | _                     | 12         | _                                           | $0.4 \times t_{OSCA}$ | μs |

#### Table 12AC Characteristics

<sup>1)</sup> The clock input signal must reach the defined levels  $V_{\rm IL}$  and  $V_{\rm IH2}$ .

Operation at lower input frequencies is possible but is guaranteed by design only (not 100% tested).

Note: The auxiliary oscillator is optimized for oscillation with a crystal at a frequency of 32 kHz. When driven by an external clock signal it will accept the specified frequency range.

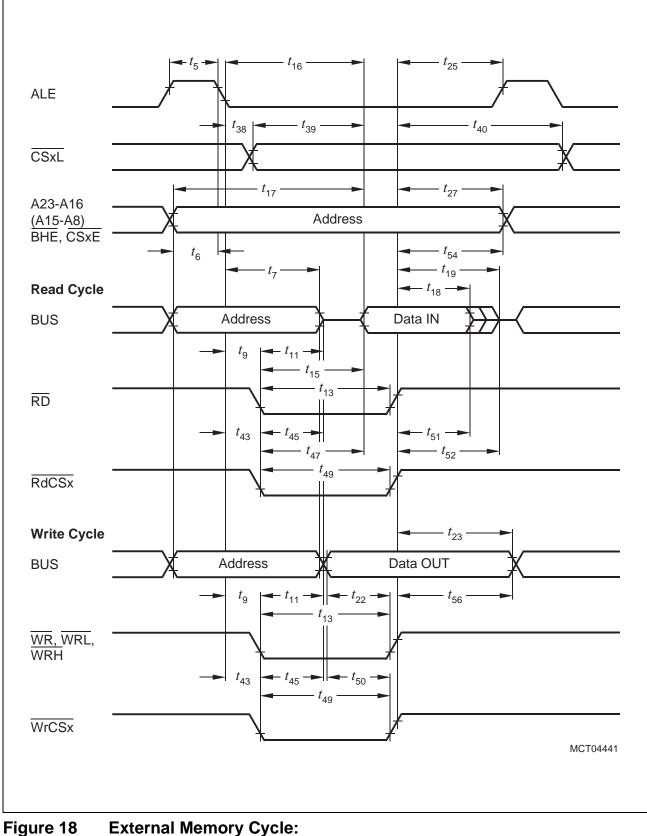

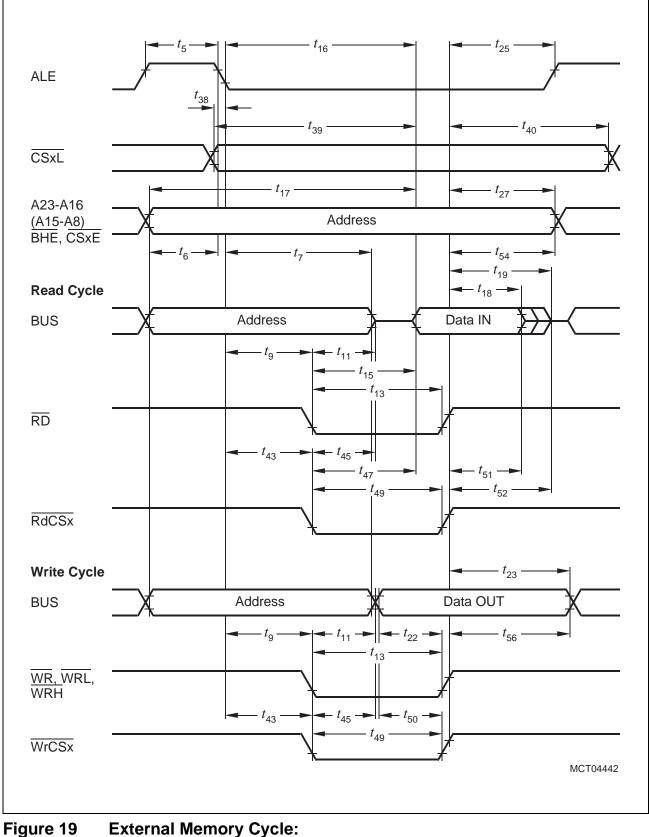

#### Multiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                         | Sym                    | nbol |                            | PU Clock<br>MHz            |                                      | CPU Clock<br>1 to 25 MHz             | Unit |

|---------------------------------------------------|------------------------|------|----------------------------|----------------------------|--------------------------------------|--------------------------------------|------|

|                                                   |                        |      | min.                       | max.                       | min.                                 | max.                                 |      |

| ALE fall. edge to RdCS,<br>WrCS (no RW delay)     | <i>t</i> <sub>43</sub> | CC   | $-4 + t_{A}$               | -                          | -4<br>+ t <sub>A</sub>               | -                                    | ns   |

| Address float after RdCS,<br>WrCS (with RW delay) | t <sub>44</sub>        | CC   | _                          | 0                          | -                                    | 0                                    | ns   |

| Address float after RdCS,<br>WrCS (no RW delay)   | t <sub>45</sub>        | CC   | _                          | 20                         | _                                    | TCL                                  | ns   |

| RdCS to Valid Data In (with RW delay)             | t <sub>46</sub>        | SR   | _                          | 16 + <i>t</i> <sub>C</sub> | _                                    | 2TCL - 24<br>+ <i>t</i> <sub>C</sub> | ns   |

| RdCS to Valid Data In (no RW delay)               | t <sub>47</sub>        | SR   | _                          | $36 + t_{\rm C}$           | _                                    | 3TCL - 24<br>+ <i>t</i> <sub>C</sub> | ns   |

| RdCS, WrCS Low Time<br>(with RW delay)            | t <sub>48</sub>        | СС   | 30 + <i>t</i> <sub>C</sub> | _                          | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | _                                    | ns   |

| RdCS, WrCS Low Time<br>(no RW delay)              | t <sub>49</sub>        | CC   | 50 + <i>t</i> <sub>C</sub> | _                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                    | ns   |

| Data valid to WrCS                                | t <sub>50</sub>        | CC   | 26 + $t_{\rm C}$           | -                          | 2TCL - 14<br>+ <i>t</i> <sub>C</sub> | -                                    | ns   |

| Data hold after RdCS                              | <i>t</i> <sub>51</sub> | SR   | 0                          | -                          | 0                                    | -                                    | ns   |

| Data float after RdCS                             | t <sub>52</sub>        | SR   | _                          | $20 + t_{\rm F}$           | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>F</sub> | ns   |

| Address hold after<br>RdCS, WrCS                  | t <sub>54</sub>        | CC   | 20 + $t_{\rm F}$           | -                          | 2TCL - 20<br>+ <i>t</i> <sub>F</sub> | -                                    | ns   |

| Data hold after WrCS                              | t <sub>56</sub>        | CC   | 20 + <i>t</i> <sub>F</sub> | -                          | 2TCL - 20<br>+ <i>t</i> <sub>F</sub> | -                                    | ns   |

<sup>1)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

#### gure 18 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Normal ALE

#### 19 External Memory Cycle: Multiplexed Bus, No Read/Write Delay, Extended ALE

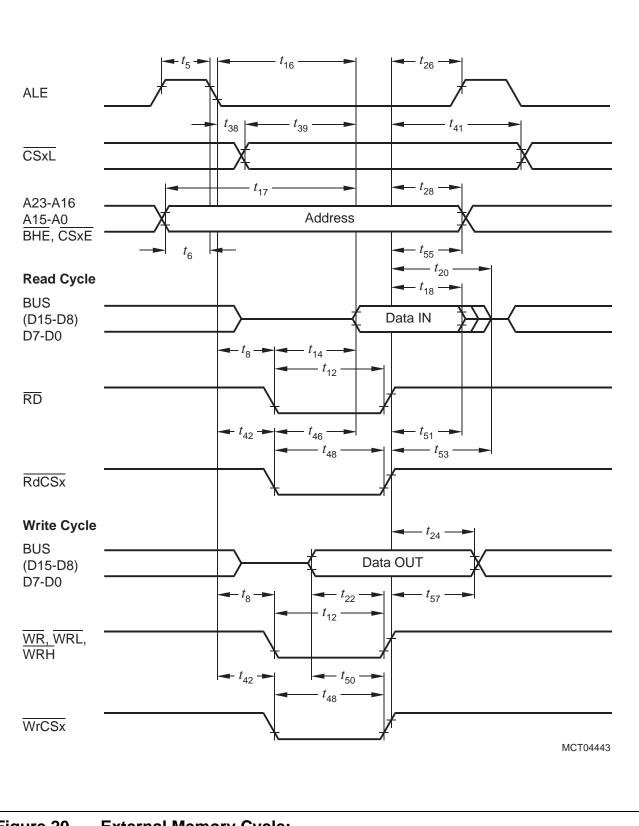

### Demultiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                            | Symbol                    |                            |             | Variable (<br>1 / 2TCL =            | Unit                             |    |

|------------------------------------------------------|---------------------------|----------------------------|-------------|-------------------------------------|----------------------------------|----|

|                                                      |                           | min.                       | max.        | min.                                | max.                             |    |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup> | <i>t</i> <sub>68</sub> SR | _                          | $0 + t_{F}$ | -                                   | TCL - 20<br>+ $2t_A + t_F^{(1)}$ | ns |

| Address hold after<br>RdCS, WrCS                     | <i>t</i> <sub>55</sub> CC | -6 + <i>t</i> <sub>F</sub> | _           | -6 + <i>t</i> <sub>F</sub>          | -                                | ns |

| Data hold after WrCS                                 | <i>t</i> <sub>57</sub> CC | $6 + t_{F}$                | _           | TCL - 14 +<br><i>t</i> <sub>F</sub> | _                                | ns |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

#### Figure 20 External Memory Cycle: Demultiplexed Bus, With Read/Write Delay, Normal ALE

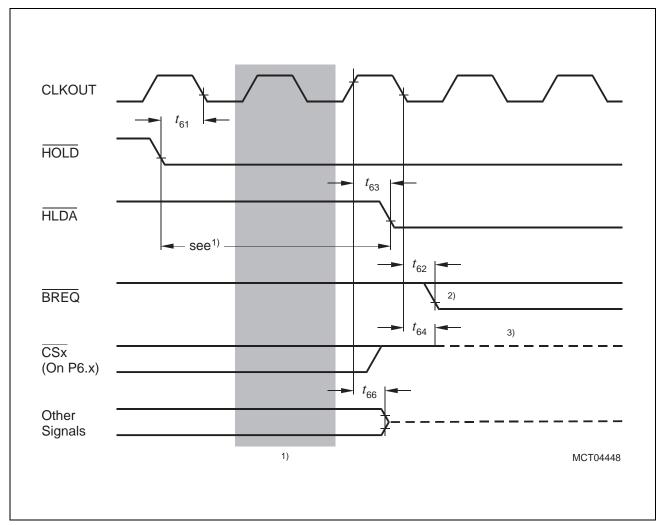

Figure 25 External Bus Arbitration, Releasing the Bus

- **Notes** <sup>1)</sup> The C161CS/JC/JI will complete the currently running bus cycle before granting bus access.

- <sup>2)</sup> This is the first possibility for BREQ to get active.

- <sup>3)</sup> The  $\overline{CS}$  outputs will be resistive high (pullup) after  $t_{64}$ .

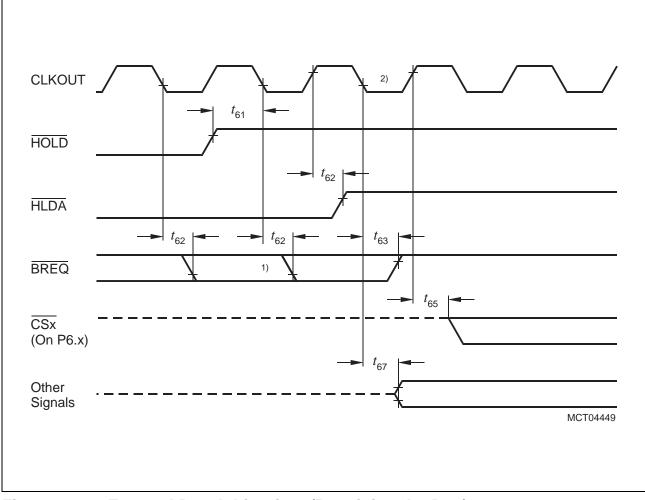

Figure 26 External Bus Arbitration, (Regaining the Bus)

# Notes

<sup>1)</sup> This is the last chance for BREQ to trigger the indicated regain-sequence. Even if BREQ is activated earlier, the regain-sequence is initiated by HOLD going high. Please note that HOLD may also be deactivated without the C161CS/JC/JI requesting the bus.

<sup>2)</sup> The next C161CS/JC/JI driven bus cycle may start here.

## Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com