Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Details                    |                                                                             |

| Product Status             | Discontinued at Digi-Key                                                    |

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SLDM, SPI, UART/USART                            |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 93                                                                          |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 10K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 128-LQFP                                                                    |

| Supplier Device Package    | PG-TQFP-128-2                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sab-c161ji-lf-ca |

- Idle, Sleep, and Power Down Modes with Flexible Power Management

- Programmable Watchdog Timer and Oscillator Watchdog

- Up to 93 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- Supported by a Large Range of Development Tools like C-Compilers,

Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers,

Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

- 128-Pin TQFP Package

This document describes several derivatives of the C161 group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

Table 1 C161CS/JC/JI Derivative Synopsis

| Derivative                         | On-Chip<br>Program Memory | Serial Bus<br>Interface(s) | Maximum CPU Frequency |

|------------------------------------|---------------------------|----------------------------|-----------------------|

| SAK-C161CS-32RF<br>SAB-C161CS-32RF | 256 KByte ROM             | CAN1, CAN2                 | 25 MHz                |

| SAK-C161CS-LF<br>SAB-C161CS-LF     |                           | CAN1, CAN2                 | 25 MHz                |

| SAK-C161JC-32RF<br>SAB-C161JC-32RF | 256 KByte ROM             | CAN1, SDLM                 | 25 MHz                |

| SAK-C161JC-LF<br>SAB-C161JC-LF     |                           | CAN1, SDLM                 | 25 MHz                |

| SAK-C161JI-32RF<br>SAB-C161JI-32RF | 256 KByte ROM             | SDLM                       | 25 MHz                |

| SAK-C161JI-LF<br>SAB-C161JI-LF     |                           | SDLM                       | 25 MHz                |

For simplicity all versions are referred to by the term C161CS/JC/JI throughout this document.

Data Sheet 2 V3.0, 2001-01

Table 2 Pin Definitions and Functions (cont'd)

| Symbol |     | Input | Function                                 |                                                        |  |  |  |

|--------|-----|-------|------------------------------------------|--------------------------------------------------------|--|--|--|

|        | No. | Outp. |                                          |                                                        |  |  |  |

| P3     |     | IO    | Port 3 is a                              | 15-bit bidirectional I/O port. It is bit-wise          |  |  |  |

|        |     |       | programma                                | able for input or output via direction bits. For a pin |  |  |  |

|        |     |       | _                                        | as input, the output driver is put into high-          |  |  |  |

|        |     |       | -                                        | state. Port 3 outputs can be configured as push/       |  |  |  |

|        |     |       | -                                        | n drain drivers. The input threshold of Port 3 is      |  |  |  |

|        |     |       |                                          | (TTL or special).                                      |  |  |  |

|        |     |       |                                          | ng Port 3 pins also serve for alternate functions:     |  |  |  |

| P3.0   | 53  |       | TOIN                                     | CAPCOM1 Timer T0 Count Input,                          |  |  |  |

|        |     | 0     | TxD1                                     | ASC1 Clock/Data Output (Async./Sync)                   |  |  |  |

| P3.1   | 54  | 0     | T6OUT GPT2 Timer T6 Toggle Latch Output, |                                                        |  |  |  |

|        |     | I/O   | RxD1                                     | ASC1 Data Input (Async.) or Inp./Output (Sync.)        |  |  |  |

| P3.2   | 55  | I     | CAPIN                                    | GPT2 Register CAPREL Capture Input                     |  |  |  |

| P3.3   | 56  | 0     | T3OUT                                    | GPT1 Timer T3 Toggle Latch Output                      |  |  |  |

| P3.4   | 57  | I     | T3EUD                                    | GPT1 Timer T3 External Up/Down Control Input           |  |  |  |

| P3.5   | 58  | 1     | T4IN                                     | GPT1 Timer T4 Count/Gate/Reload/Capture Inp            |  |  |  |

| P3.6   | 59  | 1     | T3IN                                     | GPT1 Timer T3 Count/Gate Input                         |  |  |  |

| P3.7   | 60  | 1     | T2IN                                     | GPT1 Timer T2 Count/Gate/Reload/Capture Inp            |  |  |  |

| P3.8   | 61  | I/O   | MRST                                     | SSC Master-Receive/Slave-Transmit Inp./Outp.           |  |  |  |

| P3.9   | 62  | I/O   | MTSR                                     | SSC Master-Transmit/Slave-Receive Outp./Inp.           |  |  |  |

| P3.10  | 63  | 0     | TxD0                                     | ASC0 Clock/Data Output (Async./Sync.)                  |  |  |  |

| P3.11  | 64  | I/O   | RxD0                                     | ASC0 Data Input (Async.) or Inp./Outp. (Sync.)         |  |  |  |

| P3.12  | 65  | 0     | BHE                                      | External Memory High Byte Enable Signal,               |  |  |  |

|        |     | 0     | WRH                                      | External Memory High Byte Write Strobe                 |  |  |  |

| P3.13  | 66  | I/O   | SCLK                                     | SSC Master Clock Output / Slave Clock Input.           |  |  |  |

| P3.15  | 67  | 0     | CLKOUT                                   | System Clock Output (= CPU Clock)                      |  |  |  |

|        |     | 0     | FOUT                                     | Programmable Frequency Output                          |  |  |  |

Data Sheet 9 V3.0, 2001-01

Table 2 Pin Definitions and Functions (cont'd)

| Symbol                      | Pin<br>No. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-----------------------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| READY                       | 82         | 1              | Ready Input. When the Ready function is enabled, a high level at this pin during an external memory access will force the insertion of memory cycle time waitstates until the pin returns to a low level.  An internal pullup device will hold this pin high when nothing is driving it.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| ALE                         | 83         | 0              | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the multiplexed bus modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| ĒĀ                          | 84         | I              | External Access Enable pin. A low level at this pin during and after Reset forces the C161CS/JC/JI to begin instruction execution out of external memory. A high level forces execution out of the internal program memory. "ROMless" versions must have this pin tied to '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| PORT0<br>P0L.0-7<br>P0H.0-7 | 92         | IO             | PORT0 consists of the two 8-bit bidirectional I/O ports P0L and P0H. It is bit-wise programmable for input or output via direction bits. For a pin configured as input, the output driver is put into high-impedance state.  In case of an external bus configuration, PORT0 serves as the address (A) and address/data (AD) bus in multiplexed bus modes and as the data (D) bus in demultiplexed bus modes.  Demultiplexed bus modes:  Data Path Width: 8-bit 16-bit P0L.0 – P0L.7: D0 – D7 D0 - D7 P0H.0 – P0H.7: I/O D8 - D15  Multiplexed bus modes:  Data Path Width: 8-bit 16-bit P0L.0 – P0L.7: AD0 – AD7 AD0 - AD7 P0H.0 – P0H.7: AB - AD15  Note: At the and of an external reset (EA = '0') PORT0 also |  |  |  |  |  |  |

|                             |            |                | Note: At the end of an external reset (EA = '0') PORT0 also inputs the configuration values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

Data Sheet 11 V3.0, 2001-01

## **Functional Description**

The architecture of the C161CS/JC/JI combines advantages of both RISC and CISC processors and of advanced peripheral subsystems in a very well-balanced way. In addition the on-chip memory blocks allow the design of compact systems with maximum performance.

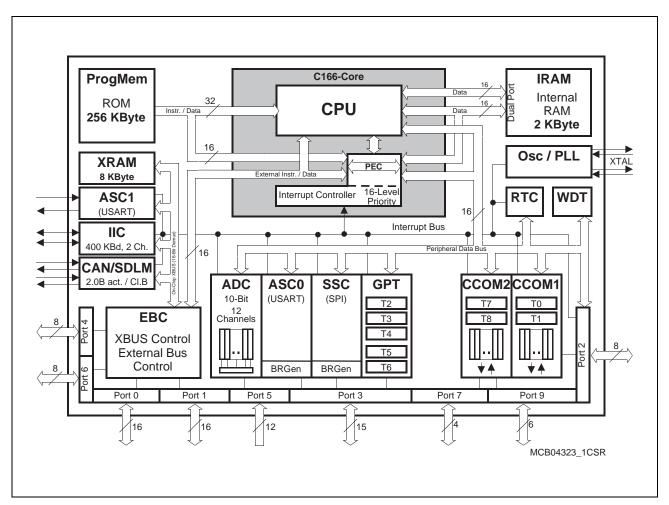

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the C161CS/JC/JI.

Note: All time specifications refer to a CPU clock of 25 MHz (see definition in the AC Characteristics section).

Figure 3 Block Diagram

The program memory, the internal RAM (IRAM) and the set of generic peripherals are connected to the CPU via separate buses. A fourth bus, the XBUS, connects external resources as well as additional on-chip resources, the X-Peripherals (see **Figure 3**).

The XBUS resources (XRAM, CAN, SDLM, IIC, ASC1) of the C161CS/JC/JI can be enabled during initialization by setting the general X-Peripheral enable bit XPEN (SYSCON.2).

If the X-Peripherals remain disabled they consume neither address space nor port pins.

Data Sheet 15 V3.0, 2001-01

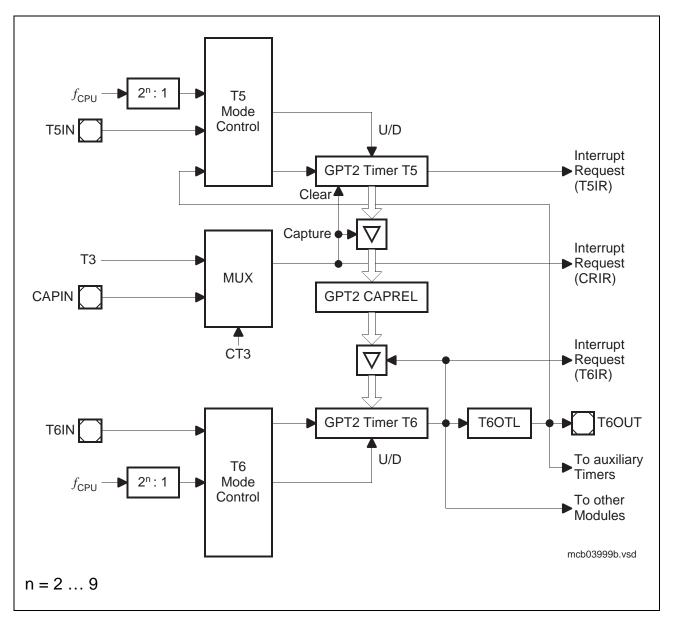

after the capture procedure. This allows the C161CS/JC/JI to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

Figure 7 Block Diagram of GPT2

#### **Real Time Clock**

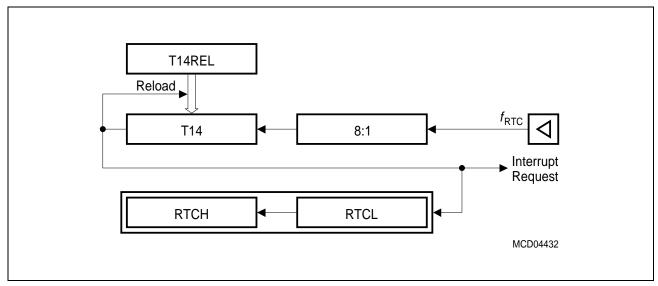

The Real Time Clock (RTC) module of the C161CS/JC/JI consists of a chain of 3 divider blocks, a fixed 8:1 divider, the reloadable 16-bit timer T14, and the 32-bit RTC timer (accessible via registers RTCH and RTCL). The RTC module is directly clocked via a separate clock driver with the on-chip main oscillator frequency divided by 32 ( $f_{\rm RTC} = f_{\rm OSCm}$  / 32) or with the on-chip auxiliary oscillator frequency ( $f_{\rm RTC} = f_{\rm OSCa}$ ). It is therefore independent from the selected clock generation mode of the C161CS/JC/JI. All timers count up.

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- · Cyclic time based interrupt

- 48-bit timer for long term measurements

Figure 8 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to maintain the correct system time even when intermediate resets are executed.

Data Sheet 29 V3.0, 2001-01

#### **Serial Channels**

Serial communication with other microcontrollers, processors, terminals or external peripheral components is provided by three serial interfaces with different functionality, two Asynchronous/Synchronous Serial Channels (ASC0/ASC1) and a High-Speed Synchronous Serial Channel (SSC).

**The ASC0** is upward compatible with the serial ports of the Infineon 8-bit microcontroller families and supports full-duplex asynchronous communication at up to 781 kBaud and half-duplex synchronous communication at up to 3.1 MBaud (@ 25 MHz CPU clock).

A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling 4 separate interrupt vectors are provided. In asynchronous mode, 8- or 9-bit data frames are transmitted or received, preceded by a start bit and terminated by one or two stop bits. For multiprocessor communication, a mechanism to distinguish address from data bytes has been included (8-bit data plus wake up bit mode).

In synchronous mode, the ASC0 transmits or receives bytes (8 bits) synchronously to a shift clock which is generated by the ASC0. The ASC0 always shifts the LSB first. A loop back option is available for testing purposes.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. A parity bit can automatically be generated on transmission or be checked on reception. Framing error detection allows to recognize data frames with missing stop bits. An overrun error will be generated, if the last character received has not been read out of the receive buffer register at the time the reception of a new character is complete.

**The ASC1** is function compatible with the ASC0, except that its registers are not bit-addressable (XBUS peripheral) and it provides only three interrupt vectors.

**The SSC** supports full-duplex synchronous communication at up to 6.25 MBaud (@ 25 MHz CPU clock). It may be configured so it interfaces with serially linked peripheral components. A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling three separate interrupt vectors are provided.

The SSC transmits or receives characters of 2 ... 16 bits length synchronously to a shift clock which can be generated by the SSC (master mode) or by an external master (slave mode). The SSC can start shifting with the LSB or with the MSB and allows the selection of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. Transmit and receive error supervise the correct handling of the data buffer. Phase and baudrate error detect incorrect serial data.

Data Sheet 31 V3.0, 2001-01

Table 7 C161CS/JC/JI Registers, Ordered by Name (cont'd)

| Name   |   | Physica<br>Address |                                 | 8-Bit<br>Addr.  | Description                                                 | Reset<br>Value    |  |  |

|--------|---|--------------------|---------------------------------|-----------------|-------------------------------------------------------------|-------------------|--|--|

| RXD18  |   | EB58 <sub>H</sub>  | X                               |                 | SDLM Receive Data Register 18 (bus)                         | 0000 <sub>H</sub> |  |  |

| S0BG   |   | FEB4 <sub>H</sub>  | 34 <sub>H</sub> 5A <sub>H</sub> |                 | Serial Channel 0 Baud Rate Generator Reload Register        |                   |  |  |

| S0CON  | b | FFB0 <sub>H</sub>  |                                 | D8 <sub>H</sub> | Serial Channel 0 Control Register                           | 0000 <sub>H</sub> |  |  |

| S0EIC  | b | FF70 <sub>H</sub>  |                                 | B8 <sub>H</sub> | Serial Channel 0 Error Interrupt Ctrl. Reg.                 | 0000 <sub>H</sub> |  |  |

| S0RBUF |   | FEB2 <sub>H</sub>  |                                 | 59 <sub>H</sub> | Serial Channel 0 Receive Buffer Register (read only)        | XXXX <sub>H</sub> |  |  |

| SORIC  | b | FF6E <sub>H</sub>  |                                 | B7 <sub>H</sub> | Serial Channel 0 Receive Interrupt<br>Control Register      | 0000 <sub>H</sub> |  |  |

| S0TBIC | b | F19C <sub>H</sub>  | Ε                               | CE <sub>H</sub> | Serial Channel 0 Transmit Buffer Interrupt Control Register | 0000 <sub>H</sub> |  |  |

| S0TBUF |   | FEB0 <sub>H</sub>  |                                 | 58 <sub>H</sub> | Serial Channel 0 Transmit Buffer<br>Register                | 0000 <sub>H</sub> |  |  |

| S0TIC  | b | FF6C <sub>H</sub>  |                                 | B6 <sub>H</sub> | Serial Channel 0 Transmit Interrupt<br>Control Register     | 0000 <sub>H</sub> |  |  |

| S1BG   |   | EDA4 <sub>H</sub>  | X                               |                 | Serial Channel 1 Baud Rate Generator Reload Register        | 0000 <sub>H</sub> |  |  |

| S1CON  |   | EDA6 <sub>H</sub>  | X                               |                 | Serial Channel 1 Control Register                           | 0000 <sub>H</sub> |  |  |

| S1RBUF |   | EDA2 <sub>H</sub>  | X                               |                 | Serial Channel 1 Receive Buffer Register (read only)        | XXXX <sub>H</sub> |  |  |

| S1TBUF |   | EDA0 <sub>H</sub>  | X                               |                 | Serial Channel 1 Transmit Buffer<br>Register                | 0000 <sub>H</sub> |  |  |

| SOFPTR |   | EB60 <sub>H</sub>  | X                               |                 | SDLM Start-of-Frame Pointer Register                        | 0000 <sub>H</sub> |  |  |

| SP     |   | FE12 <sub>H</sub>  |                                 | 09 <sub>H</sub> | CPU System Stack Pointer Register                           | FC00 <sub>H</sub> |  |  |

| SSCBR  |   | F0B4 <sub>H</sub>  | Ε                               | 5A <sub>H</sub> | SSC Baudrate Register                                       | 0000 <sub>H</sub> |  |  |

| SSCCON | b | FFB2 <sub>H</sub>  |                                 | D9 <sub>H</sub> | SSC Control Register                                        | 0000 <sub>H</sub> |  |  |

| SSCEIC | b | FF76 <sub>H</sub>  |                                 | BB <sub>H</sub> | SSC Error Interrupt Control Register                        | 0000 <sub>H</sub> |  |  |

| SSCRB  |   | F0B2 <sub>H</sub>  | Ε                               | 59 <sub>H</sub> | SSC Receive Buffer (read only)                              | XXXX <sub>H</sub> |  |  |

| SSCRIC | b | FF74 <sub>H</sub>  |                                 | BA <sub>H</sub> | SSC Receive Interrupt Control Register                      | 0000 <sub>H</sub> |  |  |

| SSCTB  |   |                    |                                 | 58 <sub>H</sub> | SSC Transmit Buffer (write only)                            | 0000 <sub>H</sub> |  |  |

| SSCTIC | b | FF72 <sub>H</sub>  |                                 | B9 <sub>H</sub> | 9 <sub>H</sub> SSC Transmit Interrupt Control Register      |                   |  |  |

| STKOV  |   | FE14 <sub>H</sub>  |                                 | 0A <sub>H</sub> | CPU Stack Overflow Pointer Register                         | FA00 <sub>H</sub> |  |  |

| STKUN  |   | FE16 <sub>H</sub>  |                                 | 0B <sub>H</sub> | CPU Stack Underflow Pointer Register                        | FC00 <sub>H</sub> |  |  |

Table 7 C161CS/JC/JI Registers, Ordered by Name (cont'd)

| Name     |                                           | Physica Address   |                                | 8-Bit<br>Addr.                          | Description                             | Reset<br>Value                  |

|----------|-------------------------------------------|-------------------|--------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------|

| T8       |                                           | F052 <sub>H</sub> | Ε                              | 29 <sub>H</sub>                         | CAPCOM Timer 8 Register                 | 0000 <sub>H</sub>               |

| T8IC     | b                                         | F17C <sub>H</sub> | Е                              | BE <sub>H</sub>                         | CAPCOM Timer 8 Interrupt Ctrl. Reg.     | 0000 <sub>H</sub>               |

| T8REL    |                                           | F056 <sub>H</sub> | Ε                              | 2B <sub>H</sub>                         | CAPCOM Timer 8 Reload Register          | 0000 <sub>H</sub>               |

| TFR      | b                                         | FFAC <sub>H</sub> |                                | D6 <sub>H</sub>                         | Trap Flag Register                      | 0000 <sub>H</sub>               |

| TRANSSTA | AΤ                                        | EB1E <sub>H</sub> | X                              |                                         | SDLM Transmission Status Register       | 0000 <sub>H</sub>               |

| TXCNT    |                                           | EB3C <sub>H</sub> | X                              |                                         | SDLM Bus Transmit Byte Counter Reg.     | 0000 <sub>H</sub>               |

| TXCPU    |                                           | EB3E <sub>H</sub> | X                              |                                         | SDLM CPU Transmit Byte Counter Reg.     | 0000 <sub>H</sub>               |

| TXD0     |                                           | EB30 <sub>H</sub> | X                              |                                         | SDLM Transmit Data Register 0           | 0000 <sub>H</sub>               |

| TXD10    |                                           | EB3A <sub>H</sub> | X                              |                                         | SDLM Transmit Data Register 10          | 0000 <sub>H</sub>               |

| TXD2     |                                           | EB32 <sub>H</sub> | X                              |                                         | SDLM Transmit Data Register 2           | 0000 <sub>H</sub>               |

| TXD4     |                                           | EB34 <sub>H</sub> | H X SDLM Transmit Data Registe |                                         | SDLM Transmit Data Register 4           | 0000 <sub>H</sub>               |

| TXD6     | <b>XD6</b> EB36 <sub>H</sub> <b>X</b>     |                   | X                              |                                         | SDLM Transmit Data Register 6           | 0000 <sub>H</sub>               |

| TXD8     |                                           | EB38 <sub>H</sub> | X                              |                                         | SDLM Transmit Data Register 8           | 0000 <sub>H</sub>               |

| TxDELAY  |                                           | EB16 <sub>H</sub> | X                              |                                         | SDLM Transceiver Delay Register         | 0014 <sub>H</sub>               |

| WDT      |                                           | FEAE <sub>H</sub> |                                | 57 <sub>H</sub>                         | Watchdog Timer Register (read only)     | 0000 <sub>H</sub>               |

| WDTCON   | b                                         | FFAE <sub>H</sub> |                                | D7 <sub>H</sub>                         | Watchdog Timer Control Register         | <sup>2)</sup> 00XX <sub>H</sub> |

| XP0IC    | b                                         | F186 <sub>H</sub> | Ε                              | C3 <sub>H</sub>                         | IIC Data Interrupt Control Register     | 0000 <sub>H</sub>               |

| XP1IC    | b                                         | F18E <sub>H</sub> | Ε                              | C7 <sub>H</sub>                         | IIC Protocol Interrupt Control Register | 0000 <sub>H</sub>               |

| XP2IC    | b                                         | F196 <sub>H</sub> | Е                              | CB <sub>H</sub>                         | CAN1 Interrupt Control Register         | 0000 <sub>H</sub>               |

| XP3IC    | b                                         | F19E <sub>H</sub> | Ε                              | CF <sub>H</sub>                         | PLL/RTC Interrupt Control Register      | 0000 <sub>H</sub>               |

| XP4IC    | <b>P4IC b</b> F182 <sub>H</sub> <b>E</b>  |                   | Е                              | C1 <sub>H</sub>                         | ASC1 Transmit Interrupt Ctrl. Reg.      | 0000 <sub>H</sub>               |

| XP5IC    | <b>XP5IC b</b> F18A <sub>H</sub> <b>E</b> |                   | C5 <sub>H</sub>                | ASC1 Receive Interrupt Control Register | 0000 <sub>H</sub>                       |                                 |

| XP6IC    | <b>XP6IC b</b> F192 <sub>H</sub> <b>E</b> |                   | C9 <sub>H</sub>                | ASC1 Error Interrupt Control Register   | 0000 <sub>H</sub>                       |                                 |

| XP7IC    | b                                         | F19A <sub>H</sub> | Ε                              | CD <sub>H</sub>                         | CAN2/SDLM Interrupt Control Register    | 0000 <sub>H</sub>               |

| ZEROS    | b                                         | FF1C <sub>H</sub> |                                | 8E <sub>H</sub>                         | Constant Value 0's Register (read only) | 0000 <sub>H</sub>               |

<sup>1)</sup> The system configuration is selected during reset.

<sup>&</sup>lt;sup>2)</sup> The reset value depends on the indicated reset source.

## **Absolute Maximum Ratings**

Table 8 Absolute Maximum Rating Parameters

| Parameter                                                            | Symbol     | Limit ' | Values                | Unit | Notes      |

|----------------------------------------------------------------------|------------|---------|-----------------------|------|------------|

|                                                                      |            | min.    | max.                  |      |            |

| Storage temperature                                                  | $T_{ST}$   | -65     | 150                   | °C   | _          |

| Junction temperature                                                 | $T_{J}$    | -40     | 150                   | °C   | under bias |

| Voltage on $V_{\rm DD}$ pins with respect to ground ( $V_{\rm SS}$ ) | $V_{DD}$   | -0.5    | 6.5                   | V    | -          |

| Voltage on any pin with respect to ground $(V_{SS})$                 | $V_{IN}$   | -0.5    | V <sub>DD</sub> + 0.5 | V    | -          |

| Input current on any pin during overload condition                   | _          | -10     | 10                    | mA   | -          |

| Absolute sum of all input currents during overload condition         | _          | -       | 100                   | mA   | _          |

| Power dissipation                                                    | $P_{DISS}$ | _       | 1.5                   | W    | _          |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

Data Sheet 49 V3.0, 2001-01

### **Operating Conditions**

The following operating conditions must not be exceeded in order to ensure correct operation of the C161CS/JC/JI. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Table 9 Operating Condition Parameters

| Parameter                         | Symbol                   | Limit             | Values | Unit | Notes                                             |

|-----------------------------------|--------------------------|-------------------|--------|------|---------------------------------------------------|

|                                   |                          | min.              | max.   |      |                                                   |

| Digital supply voltage            | $V_{DD}$                 | 4.5               | 5.5    | V    | Active mode, $f_{\text{CPUmax}} = 25 \text{ MHz}$ |

|                                   |                          | 2.5 <sup>1)</sup> | 5.5    | V    | PowerDown mode                                    |

| Digital ground voltage            | $V_{SS}$                 |                   | 0      | V    | Reference voltage                                 |

| Overload current                  | $I_{OV}$                 | _                 | ±5     | mA   | Per pin <sup>2)3)4)</sup>                         |

| Absolute sum of overload currents | $\Sigma  I_{\text{OV}} $ | _                 | 50     | mA   | 3)                                                |

| External Load Capacitance         | $C_{L}$                  | _                 | 100    | pF   | Pin drivers in fast edge mode <sup>5)</sup>       |

| Ambient temperature               | $T_{A}$                  | 0                 | 70     | °C   | SAB-C161CS/JC/JI                                  |

|                                   |                          | -40               | 85     | °C   | SAF-C161CS/JC/JI                                  |

|                                   |                          | -40               | 125    | °C   | SAK-C161CS/JC/JI                                  |

$<sup>^{1)}</sup>$  Output voltages and output currents will be reduced when  $V_{

m DD}$  leaves the range defined for active mode.

Data Sheet 50 V3.0, 2001-01

Overload conditions occur if the standard operatings conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e.  $V_{\text{OV}} > V_{\text{DD}} + 0.5 \text{ V}$  or  $V_{\text{OV}} < V_{\text{SS}} - 0.5 \text{ V}$ ). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltage must remain within the specified limits. Proper operation is not guaranteed if overload conditions occur on functional pins line XTAL1,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , etc.

<sup>3)</sup> Not 100% tested, guaranteed by design and characterization.

Due to the different port structure of Port 9 (required by the IIC bus specification) the pins of Port 9 can only tolerate positive overload current, i.e.  $V_{OV} > V_{SS}$  - 0.5 V.

<sup>&</sup>lt;sup>5)</sup> The timing is valid for pin drivers in high current or dynamic current mode. The reduced static output current in dynamic current mode must be respected when designing the system.

- <sup>6)</sup> These parameters describe the  $\overline{\text{RSTIN}}$  pullup, which equals a resistance of ca. 50 to 250 k $\Omega$ .

- 7) The maximum current may be drawn while the respective signal line remains inactive.

- 8) The minimum current must be drawn in order to drive the respective signal line active.

- This specification is valid during Reset and during Hold-mode or Adapt-mode. During Hold-mode Port 6 pins are only affected, if they are used (configured) for  $\overline{CS}$  output and the open drain function is not enabled. The  $\overline{READY}$ -pullup is always active, except for Powerdown mode.

- <sup>10)</sup> This specification is valid during Reset and during Adapt-mode.

- <sup>11)</sup> Not 100% tested, guaranteed by design and characterization.

# Power Consumption C161CS/JC/JI

(Operating Conditions apply)

| Parameter                                                                                    | Symbol                          | Lim  | it Values                      | Unit | <b>Test Condition</b>                                                             |

|----------------------------------------------------------------------------------------------|---------------------------------|------|--------------------------------|------|-----------------------------------------------------------------------------------|

|                                                                                              |                                 | min. | max.                           |      |                                                                                   |

| Power supply current (active) with all peripherals active                                    | $I_{DD}$                        | _    | 15 +<br>2.5 × f <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IL}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$  |

| Idle mode supply current with all peripherals active                                         | $I_{IDX}$                       | _    | 5 +<br>1.5 × f <sub>CPU</sub>  | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$ |

| Idle mode supply curr., Main osc, with all peripherals deactivated, PLL off, SDD factor = 32 | $I_{IDOM}^{2)}$                 | _    | 500 +<br>50 × f <sub>OSC</sub> | μΑ   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{OSC}} \text{ in [MHz]}^{1)}$ |

| Idle mode supply curr., Aux. osc, with all peripherals deactivated, PLL off, SDD factor = 32 | I <sub>IDOA</sub> <sup>2)</sup> | _    | 100                            | μΑ   | $V_{\rm DD} = V_{\rm DDmax}$<br>$f_{\rm OSC} = 32 \text{ kHz}^3$                  |

| Sleep and Power-down mode supply current with RTC running on main oscillator                 | I <sub>PDRM</sub> <sup>2)</sup> | _    | 200 +<br>25 × f <sub>OSC</sub> | μΑ   | $V_{\rm DD} = V_{\rm DDmax}$<br>$f_{\rm OSC}$ in [MHz] <sup>3)</sup>              |

| Sleep and Power-down mode supply current with RTC disabled                                   | $I_{PDO}$                       | _    | 50                             | μΑ   | $V_{\rm DD} = V_{\rm DDmax}^{3)}$                                                 |

The supply current is a function of the operating frequency. This dependency is illustrated in Figure 10. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

Data Sheet 53 V3.0, 2001-01

This parameter is determined mainly by the current consumed by the oscillator (see Figure 9). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The values given refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{\rm DD}$  - 0.1 V to  $V_{\rm DD}$ , all outputs (including pins configured as outputs) disconnected.

The timings listed in the AC Characteristics that refer to TCLs therefore must be calculated using the minimum TCL that is possible under the respective circumstances.

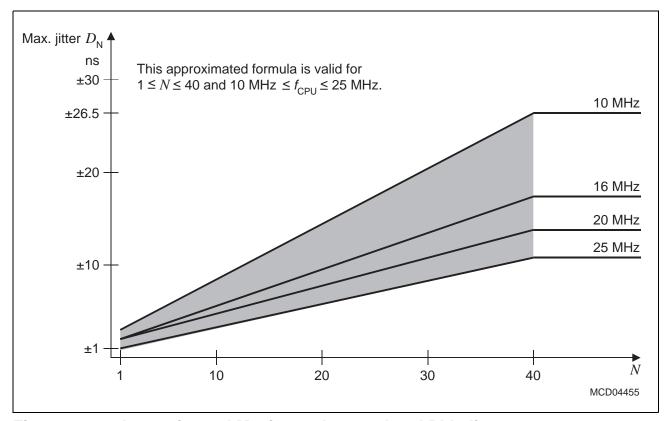

The actual minimum value for TCL depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency (crystal or oscillator) the relative deviation for periods of more than one TCL is lower than for one single TCL (see formula and Figure 12).

For a period of  $N \times TCL$  the minimum value is computed using the corresponding deviation  $D_N$ :

$$(N \times TCL)_{min} = N \times TCL_{NOM} - D_N$$

[ns] =  $\pm (13.3 + N \times 6.3) / f_{CPU}$  [MHz],

where N = number of consecutive TCLs and  $1 \le N \le 40$ .

So for a period of 3 TCLs @ 25 MHz (i.e. N = 3): D<sub>3</sub> = (13.3 +  $3 \times$  6.3) / 25 = 1.288 ns, and (3TCL)<sub>min</sub> = 3TCL<sub>NOM</sub> - 1.288 ns = 58.7 ns (@  $f_{CPU}$  = 25 MHz).

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is neglectible.

Note: For all periods longer than 40 TCL the N = 40 value can be used (see Figure 12).

Figure 12 Approximated Maximum Accumulated PLL Jitter

Data Sheet 58 V3.0, 2001-01

# AC Characteristics External Clock Drive XTAL1 (Main Oscillator)

(Operating Conditions apply)

Table 11 External Clock Drive Characteristics

| Parameter               | Symbol     |    | Direct Drive<br>1:1 |      | Prescaler<br>2:1 |      | PLL<br>1:N       |                   | Unit |

|-------------------------|------------|----|---------------------|------|------------------|------|------------------|-------------------|------|

|                         |            |    | min.                | max. | min.             | max. | min.             | max.              |      |

| Oscillator period       | $t_{OSCM}$ | SR | 40                  | _    | 20               | _    | 60 <sup>1)</sup> | 500 <sup>1)</sup> | ns   |

| High time <sup>2)</sup> | $t_1$      | SR | 20 <sup>3)</sup>    | _    | 6                | _    | 10               | _                 | ns   |

| Low time <sup>2)</sup>  | $t_2$      | SR | 20 <sup>3)</sup>    | _    | 6                | _    | 10               | _                 | ns   |

| Rise time <sup>2)</sup> | $t_3$      | SR | _                   | 10   | _                | 6    | _                | 10                | ns   |

| Fall time <sup>2)</sup> | $t_4$      | SR | _                   | 10   | _                | 6    | _                | 10                | ns   |

<sup>1)</sup> The minimum and maximum oscillator periods for PLL operation depend on the selected CPU clock generation mode. Please see respective table above.

<sup>&</sup>lt;sup>3)</sup> The minimum high and low time refers to a duty cycle of 50%. The maximum operating frequency ( $f_{CPU}$ ) in direct drive mode depends on the duty cycle of the clock input signal.

Figure 13 External Clock Drive XTAL1

Note: If the on-chip oscillator is used together with a crystal, the oscillator frequency is limited to a range of 4 MHz to 16 MHz.

It is strongly recommended to measure the oscillation allowance (or margin) in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the limits specified by the crystal supplier.

When driven by an external clock signal it will accept the specified frequency range. Operation at lower input frequencies is possible but is guaranteed by design only (not 100% tested).

Data Sheet 60 V3.0, 2001-01

<sup>&</sup>lt;sup>2)</sup> The clock input signal must reach the defined levels  $V_{\rm IL2}$  and  $V_{\rm IH2}$ .

# AC Characteristics External Clock Drive XTAL3 (Auxiliary Oscillator)

(Operating Conditions apply)

Table 12 AC Characteristics

| Parameter         | Symbol     |    | Symbol Optimum Input Clock<br>= 32 kHz |      |                                   | Variable Inpu<br>1 / t <sub>OSCA</sub> = 10 | Unit |

|-------------------|------------|----|----------------------------------------|------|-----------------------------------|---------------------------------------------|------|

|                   |            |    | min.                                   | max. | min.                              | max.                                        |      |

| Oscillator period | $t_{OSCA}$ | SR | 31                                     | 31   | 20                                | 100                                         | μs   |

| High time         | $t_1$      | SR | 6 <sup>1)</sup>                        | _    | $0.2 \times t_{\text{OSCA}}^{1)}$ | _                                           | μs   |

| Low time          | $t_2$      | SR | 6 <sup>1)</sup>                        |      | $0.2 \times t_{\text{OSCA}}^{1)}$ |                                             | μs   |

| Rise time         | $t_3$      | SR | _                                      | 12   | _                                 | $0.4 \times t_{OSCA}$                       | μs   |

| Fall time         | $t_4$      | SR | _                                      | 12   | _                                 | $0.4 \times t_{OSCA}$                       | μs   |

$<sup>^{\</sup>rm 1)}~$  The clock input signal must reach the defined levels  $V_{\rm IL}$  and  $V_{\rm IH2}.$

Note: The auxiliary oscillator is optimized for oscillation with a crystal at a frequency of 32 kHz. When driven by an external clock signal it will accept the specified frequency range.

Operation at lower input frequencies is possible but is guaranteed by design only (not 100% tested).

Data Sheet 61 V3.0, 2001-01

### A/D Converter Characteristics

(Operating Conditions apply)

Table 13 A/D Converter Characteristics

| Parameter                                       | Symbol            |    | Limit                 | Values                             | Unit | Test                                  |  |

|-------------------------------------------------|-------------------|----|-----------------------|------------------------------------|------|---------------------------------------|--|

|                                                 |                   |    | min.                  | max.                               |      | Condition                             |  |

| Analog reference supply                         | $V_{AREF}$        | SR | 4.0                   | $V_{\rm DD}$ + 0.1                 | V    | 1)                                    |  |

| Analog reference ground                         | $V_{AGND}$        | SR | V <sub>SS</sub> - 0.1 | $V_{SS} + 0.2$                     | V    |                                       |  |

| Analog input voltage range                      | $V_{AIN}$         | SR | $V_{AGND}$            | $V_{AREF}$                         | V    | 2)                                    |  |

| Basic clock frequency                           | $f_{BC}$          |    | 0.5                   | 6.25                               | MHz  | 3)                                    |  |

| Conversion time                                 | $t_{C}$           | СС | _                     | 40 t <sub>BC</sub> +               | _    | 4)                                    |  |

|                                                 |                   |    |                       | $t_{S} + 2t_{CPU}$                 |      | $t_{\text{CPU}} = 1 / f_{\text{CPU}}$ |  |

| Calibration time after reset                    | $t_{CAL}$         | CC | _                     | 3328 t <sub>BC</sub>               | _    | 5)                                    |  |

| Total unadjusted error                          | TUE               | CC | _                     | <u>+2</u>                          | LSB  | 1)                                    |  |

| Internal resistance of reference voltage source | R <sub>AREF</sub> | SR | _                     | t <sub>BC</sub> / 60<br>- 0.25     | kΩ   | $t_{\rm BC}$ in [ns] <sup>6)7)</sup>  |  |

| Internal resistance of analog source            | R <sub>ASRC</sub> | SR | _                     | <i>t</i> <sub>S</sub> / 450 - 0.25 | kΩ   | $t_{\rm S}$ in [ns] <sup>7)8)</sup>   |  |

| ADC input capacitance                           | $C_{AIN}$         | CC | _                     | 33                                 | pF   | 7)                                    |  |

|                                                 | •                 |    | •                     | •                                  |      | •                                     |  |

- TUE is tested at  $V_{\text{AREF}}$  = 5.0 V,  $V_{\text{AGND}}$  = 0 V,  $V_{\text{DD}}$  = 4.9 V. It is guaranteed by design for all other voltages within the defined voltage range.

- If the analog reference supply voltage exceeds the power supply voltage by up to 0.2 V

- (i.e.  $V_{AREF} = V_{DD} = +0.2 \text{ V}$ ) the maximum TUE is increased to  $\pm 3$  LSB. This range is not 100% tested.

- The specified TUE is guaranteed only if the absolute sum of input overload currents on Port 5 pins (see  $I_{OV}$  specification) does not exceed 10 mA.

- During the reset calibration sequence the maximum TUE may be ±4 LSB.

- $^{2)}$   $V_{\rm AIN}$  may exceed  $V_{\rm AGND}$  or  $V_{\rm AREF}$  up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- <sup>3)</sup> The limit values for  $f_{BC}$  must not be exceeded when selecting the CPU frequency and the ADCTC setting.

- This parameter includes the sample time  $t_{S}$ , the time for determining the digital result and the time to load the result register with the conversion result.

- Values for the basic clock  $t_{BC}$  depend on programming and can be taken from Table 14.

- This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

- <sup>5)</sup> During the reset calibration conversions can be executed (with the current accuracy). The time required for these conversions is added to the total reset calibration time.

- <sup>6)</sup> During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference voltage source must allow the capacitance to reach its respective voltage level within each conversion step. The maximum internal resistance results from the programmed conversion timing.

- 7) Not 100% tested, guaranteed by design and characterization.

Data Sheet 62 V3.0, 2001-01

<sup>8)</sup> During the sample time the input capacitance  $C_{\text{AIN}}$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_{\text{S}}$ . After the end of the sample time  $t_{\text{S}}$ , changes of the analog input voltage have no effect on the conversion result.

Values for the sample time  $t_S$  depend on programming and can be taken from Table 14.

Sample time and conversion time of the C161CS/JC/JI's A/D Converter are programmable. **Table 14** should be used to calculate the above timings. The limit values for  $f_{\rm BC}$  must not be exceeded when selecting ADCTC.

Table 14 A/D Converter Computation Table

| ADCON.15 14<br>(ADCTC) | A/D Converter Basic Clock $f_{\mathrm{BC}}$ | ADCON.13 12<br>(ADSTC) | Sample time $t_{S}$    |

|------------------------|---------------------------------------------|------------------------|------------------------|

| 00                     | f <sub>CPU</sub> / 4                        | 00                     | $t_{\rm BC} \times 8$  |

| 01                     | f <sub>CPU</sub> / 2                        | 01                     | $t_{\rm BC} \times 16$ |

| 10                     | f <sub>CPU</sub> / 16                       | 10                     | $t_{\rm BC} \times 32$ |

| 11                     | f <sub>CPU</sub> / 8                        | 11                     | $t_{\rm BC} \times 64$ |

## Converter Timing Example:

Assumptions:  $f_{CPU} = 25 \text{ MHz}$  (i.e.  $t_{CPU} = 40 \text{ ns}$ ), ADCTC = '00', ADSTC = '00'.

Basic clock  $f_{BC} = f_{CPU} / 4 = 6.25 \text{ MHz}$ , i.e.  $t_{BC} = 160 \text{ ns}$ .

Sample time  $t_S = t_{BC} \times 8 = 1280 \text{ ns.}$

Conversion time  $t_C = t_S + 40 t_{BC} + 2 t_{CPU} = (1280 + 6400 + 80) \text{ ns} = 7.8 \,\mu\text{s}.$

Data Sheet 63 V3.0, 2001-01

## **Memory Cycle Variables**

The timing tables below use three variables which are derived from the BUSCONx registers and represent the special characteristics of the programmed memory cycle. The following table describes, how these variables are to be computed.

Table 15 Memory Cycle Variables

| Description                  | Symbol  | Values                      |

|------------------------------|---------|-----------------------------|

| ALE Extension                | $t_{A}$ | TCL × <alectl></alectl>     |

| Memory Cycle Time Waitstates | $t_{C}$ | 2TCL × (15 - <mctc>)</mctc> |

| Memory Tristate Time         | $t_{F}$ | 2TCL × (1 - <mttc>)</mttc>  |

Note: Please respect the maximum operating frequency of the respective derivative.

### **AC Characteristics**

### **Multiplexed Bus**

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                           | Symbol                 |    | Max. CPU Clock<br>= 25 MHz |      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |         | Unit |

|-------------------------------------------------------------------------------------|------------------------|----|----------------------------|------|----------------------------------------------|---------|------|

|                                                                                     |                        |    | min.                       | max. | min.                                         | max.    |      |

| ALE high time                                                                       | <i>t</i> <sub>5</sub>  | CC | 10 + t <sub>A</sub>        | _    | TCL - 10<br>+ t <sub>A</sub>                 | _       | ns   |

| Address setup to ALE                                                                | <i>t</i> <sub>6</sub>  | CC | $4 + t_A$                  | _    | TCL - 16<br>+ t <sub>A</sub>                 | _       | ns   |

| Address hold after ALE                                                              | <i>t</i> <sub>7</sub>  | CC | 10 + t <sub>A</sub>        | _    | TCL - 10<br>+ t <sub>A</sub>                 | _       | ns   |

| ALE falling edge to $\overline{\text{RD}}$ , $\overline{\text{WR}}$ (with RW-delay) | <i>t</i> <sub>8</sub>  | CC | 10 + t <sub>A</sub>        | _    | TCL - 10<br>+ t <sub>A</sub>                 | _       | ns   |

| ALE falling edge to $\overline{\text{RD}}$ , $\overline{\text{WR}}$ (no RW-delay)   | <i>t</i> <sub>9</sub>  | CC | -10 + t <sub>A</sub>       | _    | -10 + t <sub>A</sub>                         | _       | ns   |

| Address float after RD, WR (with RW-delay)                                          | <i>t</i> <sub>10</sub> | CC | _                          | 6    | _                                            | 6       | ns   |

| Address float after RD, WR (no RW-delay)                                            | t <sub>11</sub>        | CC | _                          | 26   | _                                            | TCL + 6 | ns   |

| RD, WR low time<br>(with RW-delay)                                                  | <i>t</i> <sub>12</sub> | CC | 30 + t <sub>C</sub>        | _    | 2TCL - 10<br>+ t <sub>C</sub>                | _       | ns   |

Data Sheet 65 V3.0, 2001-01

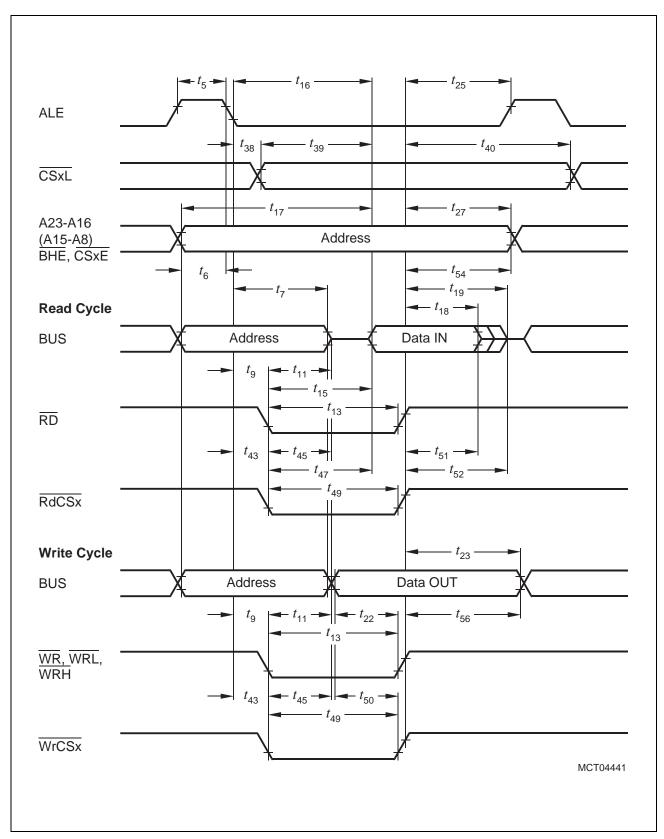

Figure 18 External Memory Cycle:

Multiplexed Bus, No Read/Write Delay, Normal ALE

## Demultiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                         | Symbol                    | Max. CPU Clock<br>= 25 MHz |                    | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                              | Unit |

|---------------------------------------------------|---------------------------|----------------------------|--------------------|----------------------------------------------|------------------------------|------|

|                                                   |                           | min.                       | max.               | min.                                         | max.                         |      |

| Data float after RdCS (no RW-delay) <sup>1)</sup> | <i>t</i> <sub>68</sub> SR | _                          | 0 + t <sub>F</sub> | _                                            | TCL - 20 + $2t_A + t_F^{1)}$ | ns   |

| Address hold after RdCS, WrCS                     | <i>t</i> <sub>55</sub> CC | -6 + t <sub>F</sub>        | _                  | -6 + t <sub>F</sub>                          | _                            | ns   |

| Data hold after WrCS                              | <i>t</i> <sub>57</sub> CC | 6 + t <sub>F</sub>         | _                  | TCL - 14 + t <sub>F</sub>                    | _                            | ns   |

$<sup>^{1)}</sup>$  RW-delay and  $t_{\rm A}$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

Data Sheet 74 V3.0, 2001-01

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising  $\overline{\text{RD}}$  edge. Therefore address changes before the end of  $\overline{\text{RD}}$  have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).