Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SLDM, SPI, UART/USART                    |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 93                                                                          |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 10K × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 128-LQFP                                                                    |

| Supplier Device Package    | PG-TQFP-128-2                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-c161jc-lf-ca |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2001-01

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2001. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

- Idle, Sleep, and Power Down Modes with Flexible Power Management

- Programmable Watchdog Timer and Oscillator Watchdog

- Up to 93 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- Supported by a Large Range of Development Tools like C-Compilers, Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers, Simulators, Logic Analyzer Disassemblers, Programming Boards

- On-Chip Bootstrap Loader

- 128-Pin TQFP Package

This document describes several derivatives of the C161 group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

| Derivative                         | On-Chip<br>Program Memory | Serial Bus<br>Interface(s) | Maximum CPU<br>Frequency |

|------------------------------------|---------------------------|----------------------------|--------------------------|

| SAK-C161CS-32RF<br>SAB-C161CS-32RF | 256 KByte ROM             | CAN1, CAN2                 | 25 MHz                   |

| SAK-C161CS-LF<br>SAB-C161CS-LF     |                           | CAN1, CAN2                 | 25 MHz                   |

| SAK-C161JC-32RF<br>SAB-C161JC-32RF | 256 KByte ROM             | CAN1, SDLM                 | 25 MHz                   |

| SAK-C161JC-LF<br>SAB-C161JC-LF     |                           | CAN1, SDLM                 | 25 MHz                   |

| SAK-C161JI-32RF<br>SAB-C161JI-32RF | 256 KByte ROM             | SDLM                       | 25 MHz                   |

| SAK-C161JI-LF<br>SAB-C161JI-LF     |                           | SDLM                       | 25 MHz                   |

## Table 1 C161CS/JC/JI Derivative Synopsis

For simplicity all versions are referred to by the term **C161CS/JC/JI** throughout this document.

| Symbol     | Pin<br>No. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|------------|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Ρ4         |            | IO             | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. The Port 4 outputs can be configured as<br>push/pull or open drain drivers. The input threshold of Port 4<br>is selectable (TTL or special).<br>Port 4 can be used to output the segment address lines and<br>for serial interface lines: <sup>1)</sup> |  |  |  |  |  |  |

| P4.0       | 70         | 0              | A16 Least Significant Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| P4.1       | 71         | 0              | A17 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| P4.2       | 72         | 0              | A18 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| P4.3       | 73         | 0              | A19 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| P4.4       | 74         | 0              | A20 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|            |            | 1              | CAN2_RxD CAN 2 Receive Data Input, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|            |            | 1              | SDL_RxD SDLM Receive Data Input (C161JC/JI)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| P4.5       | 75         | 0              | A21 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|            |            | I              | CAN1_RxD CAN 1 Receive Data Input, (C161CS/JC)                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| P4.6       | 76         | 0              | A22 Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|            |            | 0              | CAN1_TxD CAN 1 Transmit Data Output, (C161CS/JC)                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|            |            | 0              | CAN2_TxD CAN 2 Transmit Data Output, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|            |            | 1              | SDL_RxDSDLM Receive Data Input(C161JC/JI)                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| P4.7       | 77         | 0              | A23 Most Significant Segment Address Line,                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|            |            | 1              | CAN1_RxD CAN 1 Receive Data Input, (C161CS/JC)                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|            |            | 0              | CAN2_TxD CAN 2 Transmit Data Output, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|            |            | 1              | CAN2_RxD CAN 2 Receive Data Input, (C161CS)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|            |            | 0              | SDL_TxD SDLM Transmit Data Output (C161JC/JI)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| RD         | 80         | 0              | External Memory Read Strobe. $\overline{RD}$ is activated for every external instruction or data read access.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| WR/<br>WRL | 81         | 0              | External Memory Write Strobe. In WR-mode this pin is<br>activated for every external data write access. In WRL-mode<br>this pin is activated for low byte data write accesses on a<br>16-bit bus, and for every data write access on an 8-bit bus.<br>See WRCFG in register SYSCON for mode selection.                                                                                                                                                              |  |  |  |  |  |  |

# **Functional Description**

The architecture of the C161CS/JC/JI combines advantages of both RISC and CISC processors and of advanced peripheral subsystems in a very well-balanced way. In addition the on-chip memory blocks allow the design of compact systems with maximum performance.

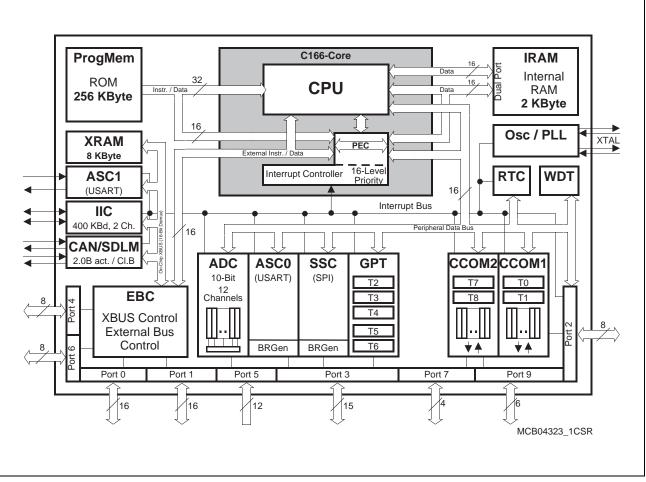

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the C161CS/JC/JI.

Note: All time specifications refer to a CPU clock of 25 MHz (see definition in the AC Characteristics section).

## Figure 3 Block Diagram

The program memory, the internal RAM (IRAM) and the set of generic peripherals are connected to the CPU via separate buses. A fourth bus, the XBUS, connects external resources as well as additional on-chip resources, the X-Peripherals (see **Figure 3**).

The XBUS resources (XRAM, CAN, SDLM, IIC, ASC1) of the C161CS/JC/JI can be enabled during initialization by setting the general X-Peripheral enable bit XPEN (SYSCON.2).

If the X-Peripherals remain disabled they consume neither address space nor port pins.

# Table 3C161CS/JC/JI Interrupt Nodes (cont'd)

| Source of Interrupt or PEC Service Request             | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location   | Trap<br>Number  |

|--------------------------------------------------------|-----------------|----------------|---------------------|----------------------|-----------------|

| CAPCOM Register 30                                     | CC30IR          | CC30IE         | CC30INT             | 00'0114 <sub>H</sub> | 45 <sub>H</sub> |

| CAPCOM Register 31                                     | CC31IR          | CC31IE         | CC31INT             | 00'0118 <sub>H</sub> | 46 <sub>H</sub> |

| CAPCOM Timer 0                                         | T0IR            | TOIE           | TOINT               | 00'0080 <sub>H</sub> | 20 <sub>H</sub> |

| CAPCOM Timer 1                                         | T1IR            | T1IE           | T1INT               | 00'0084 <sub>H</sub> | 21 <sub>H</sub> |

| CAPCOM Timer 7                                         | T7IR            | T7IE           | T7INT               | 00'00F4 <sub>H</sub> | 3D <sub>H</sub> |

| CAPCOM Timer 8                                         | T8IR            | T8IE           | T8INT               | 00'00F8 <sub>H</sub> | 3E <sub>H</sub> |

| GPT1 Timer 2                                           | T2IR            | T2IE           | T2INT               | 00'0088 <sub>H</sub> | 22 <sub>H</sub> |

| GPT1 Timer 3                                           | T3IR            | T3IE           | T3INT               | 00'008C <sub>H</sub> | 23 <sub>H</sub> |

| GPT1 Timer 4                                           | T4IR            | T4IE           | T4INT               | 00'0090 <sub>H</sub> | 24 <sub>H</sub> |

| GPT2 Timer 5                                           | T5IR            | T5IE           | T5INT               | 00'0094 <sub>H</sub> | 25 <sub>H</sub> |

| GPT2 Timer 6                                           | T6IR            | T6IE           | T6INT               | 00'0098 <sub>H</sub> | 26 <sub>H</sub> |

| GPT2 CAPREL Reg.                                       | CRIR            | CRIE           | CRINT               | 00'009C <sub>H</sub> | 27 <sub>H</sub> |

| A/D Conversion Compl.                                  | ADCIR           | ADCIE          | ADCINT              | 00'00A0 <sub>H</sub> | 28 <sub>H</sub> |

| A/D Overrun Error                                      | ADEIR           | ADEIE          | ADEINT              | 00'00A4 <sub>H</sub> | 29 <sub>H</sub> |

| ASC0 Transmit                                          | S0TIR           | SOTIE          | SOTINT              | 00'00A8 <sub>H</sub> | 2A <sub>H</sub> |

| ASC0 Transmit Buffer                                   | S0TBIR          | SOTBIE         | SOTBINT             | 00'011C <sub>H</sub> | 47 <sub>H</sub> |

| ASC0 Receive                                           | SORIR           | SORIE          | SORINT              | 00'00AC <sub>H</sub> | 2B <sub>H</sub> |

| ASC0 Error                                             | S0EIR           | SOEIE          | SOEINT              | 00'00B0 <sub>H</sub> | 2C <sub>H</sub> |

| SSC Transmit                                           | SCTIR           | SCTIE          | SCTINT              | 00'00B4 <sub>H</sub> | 2D <sub>H</sub> |

| SSC Receive                                            | SCRIR           | SCRIE          | SCRINT              | 00'00B8 <sub>H</sub> | 2E <sub>H</sub> |

| SSC Error                                              | SCEIR           | SCEIE          | SCEINT              | 00'00BC <sub>H</sub> | 2F <sub>H</sub> |

| IIC Data Transfer Event                                | XP0IR           | XP0IE          | XP0INT              | 00'0100 <sub>H</sub> | 40 <sub>H</sub> |

| IIC Protocol Event                                     | XP1IR           | XP1IE          | XP1INT              | 00'0104 <sub>H</sub> | 41 <sub>H</sub> |

| CAN1 (C161CS/JC)                                       | XP2IR           | XP2IE          | XP2INT              | 00'0108 <sub>H</sub> | 42 <sub>H</sub> |

| PLL/OWD and RTC                                        | XP3IR           | XP3IE          | XP3INT              | 00'010C <sub>H</sub> | 43 <sub>H</sub> |

| ASC1 Transmit                                          | XP4IR           | XP4IE          | XP4INT              | 00'0120 <sub>H</sub> | 48 <sub>H</sub> |

| ASC1 Receive                                           | XP5IR           | XP5IE          | XP5INT              | 00'0124 <sub>H</sub> | 49 <sub>H</sub> |

| ASC1 Error                                             | XP6IR           | XP6IE          | XP6INT              | 00'0128 <sub>H</sub> | 4A <sub>H</sub> |

| CAN2 ( <b>C161CS</b> ) or<br>SDLM ( <b>C161JC/JI</b> ) | XP7IR           | XP7IE          | XP7INT              | 00'012C <sub>H</sub> | 4B <sub>H</sub> |

# Serial Channels

Serial communication with other microcontrollers, processors, terminals or external peripheral components is provided by three serial interfaces with different functionality, two Asynchronous/Synchronous Serial Channels (**ASC0/ASC1**) and a High-Speed Synchronous Serial Channel (**SSC**).

**The ASC0** is upward compatible with the serial ports of the Infineon 8-bit microcontroller families and supports full-duplex asynchronous communication at up to 781 kBaud and half-duplex synchronous communication at up to 3.1 MBaud (@ 25 MHz CPU clock).

A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling 4 separate interrupt vectors are provided. In asynchronous mode, 8- or 9-bit data frames are transmitted or received, preceded by a start bit and terminated by one or two stop bits. For multiprocessor communication, a mechanism to distinguish address from data bytes has been included (8-bit data plus wake up bit mode).

In synchronous mode, the ASC0 transmits or receives bytes (8 bits) synchronously to a shift clock which is generated by the ASC0. The ASC0 always shifts the LSB first. A loop back option is available for testing purposes.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. A parity bit can automatically be generated on transmission or be checked on reception. Framing error detection allows to recognize data frames with missing stop bits. An overrun error will be generated, if the last character received has not been read out of the receive buffer register at the time the reception of a new character is complete.

**The ASC1** is function compatible with the ASC0, except that its registers are not bitaddressable (XBUS peripheral) and it provides only three interrupt vectors.

**The SSC** supports full-duplex synchronous communication at up to 6.25 MBaud (@ 25 MHz CPU clock). It may be configured so it interfaces with serially linked peripheral components. A dedicated baud rate generator allows to set up all standard baud rates without oscillator tuning. For transmission, reception and error handling three separate interrupt vectors are provided.

The SSC transmits or receives characters of 2 ... 16 bits length synchronously to a shift clock which can be generated by the SSC (master mode) or by an external master (slave mode). The SSC can start shifting with the LSB or with the MSB and allows the selection of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase the reliability of data transfers. Transmit and receive error supervise the correct handling of the data buffer. Phase and baudrate error detect incorrect serial data.

## Serial Data Link Module (SDLM)

The Serial Data Link Module (SDLM) provides serial communication via a J1850 type multiplexed serial bus via an external J1850 bus transceiver. The module conforms to the SAE Class B J1850 specification for variable pulse width modulation (VPW). The SDLM is integrated as an on-chip peripheral and is connected to the CPU via the XBUS.

## **General SDLM Features:**

- Compliant to the SAE Class B J1850 specification (VPW)

- Class 2 protocol fully supported

- Variable Pulse Width (VPW) operation at 10.4 kBaud

- High Speed 4X operation at 41.6 kBaud

- Programmable Normalization Bit

- Programmable Delay for transceiver interface

- Digital Noise Filter

- Power Down mode with automatic wakeup support upon bus activity

- Single Byte Header and Consolidated Header supported

- CRC generation and checking

- Receive and transmit Block Mode

## **Data Link Operation Features:**

- 11 Byte Transmit Buffer

- Double buffered 11 Byte receive buffer (optional overwrite enable)

- Support for In Frame Response (IFR) types 1, 2 and 3

- Transmit and Receiver Message Buffers configurable for either FIFO or Byte mode

- Advanced Interrupt Handling with 8 separately enabled sources:

Error, format or bus shorted CRC error Lost Arbitration Break received In-Frame-Response request Header received Complete message received Transmit successful

- Automatic IFR transmission (Types 1 and 2) for 3-Byte consolidated headers

- User configurable clock divider

- Bus status flags (IDLE, EOF, EOD, SOF, Tx and Rx in progress)

- Note: When the SDLM is used with the interface lines assigned to Port 4, the interface lines override the segment address lines and the segment address output on Port 4 is therefore limited to 6/4 bits i.e. address lines A21/A19 ... A16. CS lines can be used to increase the total amount of addressable external memory.

## **CAN-Modules**

The integrated CAN-Modules handle the completely autonomous transmission and reception of CAN frames in accordance with the CAN specification V2.0 part B (active), i.e. the on-chip CAN-Modules can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

The modules provide Full CAN functionality on up to 15 message objects each. Message object 15 may be configured for Basic CAN functionality. Both modes provide separate masks for acceptance filtering which allows to accept a number of identifiers in Full CAN mode and also allows to disregard a number of identifiers in Basic CAN mode. All message objects can be updated independent from the other objects and are equipped for the maximum message length of 8 bytes.

The bit timing is derived from the XCLK and is programmable up to a data rate of 1 MBaud. Each CAN-Module uses two pins of Port 4 or Port 8 to interface to an external bus transceiver. The interface pins are assigned via software.

**Module CAN2** (C161CS only) is identical with the first one, except that it uses a separate address area and a separate interrupt node.

The two CAN modules can be internally coupled by assigning their interface pins to the same two port pins, or they can interface to separate CAN buses.

Note: When one or both of the on-chip CAN Modules are used with the interface lines assigned to Port 4, the interface lines override the segment address lines and the segment address output on Port 4 is therefore limited to 6/4 bits i.e. address lines A21/A19 ... A16. CS lines can be used to increase the total amount of addressable external memory.

## IIC Module

The integrated IIC Bus Module handles the transmission and reception of frames over the two-line IIC bus in accordance with the IIC Bus specification. The on-chip IIC Module can receive and transmit data using 7-bit or 10-bit addressing and it can operate in slave mode, in master mode or in multi-master mode.

Several physical interfaces (port pins) can be established under software control. Data can be transferred at speeds up to 400 kbit/sec.

Two interrupt nodes dedicated to the IIC module allow efficient interrupt service and also support operation via PEC transfers.

Note: The port pins associated with the IIC interfaces feature open drain drivers only, as required by the IIC specification.

## **Instruction Set Summary**

Table 6 lists the instructions of the C161CS/JC/JI in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the **"C166 Family Instruction Set Manual"**.

This document also provides a detailled description of each instruction.

| Mnemonic           | Description                                                                                          | Bytes |

|--------------------|------------------------------------------------------------------------------------------------------|-------|

| ADD(B)             | Add word (byte) operands                                                                             | 2/4   |

| ADDC(B)            | Add word (byte) operands with Carry                                                                  | 2/4   |

| SUB(B)             | Subtract word (byte) operands                                                                        | 2/4   |

| SUBC(B)            | Subtract word (byte) operands with Carry                                                             | 2/4   |

| MUL(U)             | (Un)Signed multiply direct GPR by direct GPR (16-16-bit)                                             | 2     |

| DIV(U)             | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                            | 2     |

| DIVL(U)            | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                            | 2     |

| CPL(B)             | Complement direct word (byte) GPR                                                                    | 2     |

| NEG(B)             | Negate direct word (byte) GPR                                                                        | 2     |

| AND(B)             | Bitwise AND, (word/byte operands)                                                                    | 2/4   |

| OR(B)              | Bitwise OR, (word/byte operands)                                                                     | 2/4   |

| XOR(B)             | Bitwise XOR, (word/byte operands)                                                                    | 2/4   |

| BCLR               | Clear direct bit                                                                                     | 2     |

| BSET               | Set direct bit                                                                                       | 2     |

| BMOV(N)            | Move (negated) direct bit to direct bit                                                              | 4     |

| BAND, BOR,<br>BXOR | AND/OR/XOR direct bit with direct bit                                                                | 4     |

| BCMP               | Compare direct bit to direct bit                                                                     | 4     |

| BFLDH/L            | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data        | 4     |

| CMP(B)             | Compare word (byte) operands                                                                         | 2/4   |

| CMPD1/2            | Compare word data to GPR and decrement GPR by 1/2                                                    | 2/4   |

| CMPI1/2            | Compare word data to GPR and increment GPR by 1/2                                                    | 2/4   |

| PRIOR              | Determine number of shift cycles to normalize direct<br>word GPR and store result in direct word GPR | 2     |

| SHL / SHR          | Shift left/right direct word GPR                                                                     | 2     |

| ROL / ROR          | Rotate left/right direct word GPR                                                                    | 2     |

| ASHR               | Arithmetic (sign bit) shift right direct word GPR                                                    | 2     |

#### Table 6Instruction Set Summary

|                        | truction Set Summary (cont'd)                                                       |       |

|------------------------|-------------------------------------------------------------------------------------|-------|

| Mnemonic               | Description                                                                         | Bytes |

| MOV(B)                 | Move word (byte) data                                                               | 2/4   |

| MOVBS                  | Move byte operand to word operand with sign extension                               | 2/4   |

| MOVBZ                  | Move byte operand to word operand. with zero extension                              | 2/4   |

| JMPA, JMPI,<br>JMPR    | Jump absolute/indirect/relative if condition is met                                 | 4     |

| JMPS                   | Jump absolute to a code segment                                                     | 4     |

| J(N)B                  | Jump relative if direct bit is (not) set                                            | 4     |

| JBC                    | Jump relative and clear bit if direct bit is set                                    | 4     |

| JNBS                   | Jump relative and set bit if direct bit is not set                                  | 4     |

| CALLA, CALLI,<br>CALLR | Call absolute/indirect/relative subroutine if condition is met                      | 4     |

| CALLS                  | Call absolute subroutine in any code segment                                        | 4     |

| PCALL                  | Push direct word register onto system stack and call absolute subroutine            | 4     |

| TRAP                   | Call interrupt service routine via immediate trap number                            | 2     |

| PUSH, POP              | Push/pop direct word register onto/from system stack                                | 2     |

| SCXT                   | Push direct word register onto system stack and update register with word operand   | 4     |

| RET                    | Return from intra-segment subroutine                                                | 2     |

| RETS                   | Return from inter-segment subroutine                                                | 2     |

| RETP                   | Return from intra-segment subroutine and pop direct word register from system stack | 2     |

| RETI                   | Return from interrupt service subroutine                                            | 2     |

| SRST                   | Software Reset                                                                      | 4     |

| IDLE                   | Enter Idle Mode                                                                     | 4     |

| PWRDN                  | Enter Power Down Mode (supposes NMI-pin being low)                                  | 4     |

| SRVWDT                 | Service Watchdog Timer                                                              | 4     |

| DISWDT                 | Disable Watchdog Timer                                                              | 4     |

| EINIT                  | Signify End-of-Initialization on RSTOUT-pin                                         | 4     |

| ATOMIC                 | Begin ATOMIC sequence                                                               | 2     |

| EXTR                   | Begin EXTended Register sequence                                                    | 2     |

| EXTP(R)                | Begin EXTended Page (and Register) sequence                                         | 2/4   |

| EXTS(R)                | Begin EXTended Segment (and Register) sequence                                      | 2/4   |

| NOP                    | Null operation                                                                      | 2     |

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C161CS/ JC/JI and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

#### CC (Controller Characteristics):

The logic of the C161CS/JC/JI will provide signals with the respective timing characteristics.

#### SR (System Requirement):

The external system must provide signals with the respective timing characteristics to the C161CS/JC/JI.

#### **DC Characteristics**

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                                  | Symbol           |    | Limit                        | Values                       | Unit | Test Condition                                                   |

|------------------------------------------------------------------------------------------------------------|------------------|----|------------------------------|------------------------------|------|------------------------------------------------------------------|

|                                                                                                            |                  |    | min.                         | max.                         |      |                                                                  |

| Input low voltage (TTL,<br>all except XTAL1, XTAL3, Port 9)                                                | $V_{IL}$         | SR | -0.5                         | 0.2 V <sub>DD</sub><br>- 0.1 | V    | _                                                                |

| Input low voltage<br>XTAL1, XTAL3, Port 9                                                                  | V <sub>IL2</sub> | SR | -0.5                         | 0.3 V <sub>DD</sub>          | V    | _                                                                |

| Input low voltage<br>(Special Threshold)                                                                   | V <sub>ILS</sub> | SR | -0.5                         | 2.0                          | V    | _                                                                |

| Input high voltage (TTL, all<br>except RSTIN, XTAL1, XTAL3,<br>Port 9)                                     | V <sub>IH</sub>  | SR | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> +<br>0.5     | V    | _                                                                |

| Input high voltage RSTIN (when operated as input)                                                          | V <sub>IH1</sub> | SR | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                                                |

| Input high voltage<br>XTAL1, XTAL3, Port 9                                                                 | V <sub>IH2</sub> | SR | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                                                |

| Input high voltage<br>(Special Threshold)                                                                  | V <sub>IHS</sub> | SR | 0.8 V <sub>DD</sub><br>- 0.2 | V <sub>DD</sub> +<br>0.5     | V    | -                                                                |

| Input Hysteresis<br>(Special Threshold)                                                                    | HYS              |    | 400                          | _                            | mV   | Series resistance<br>= $0 \Omega$                                |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, CLKOUT,<br>RSTOUT, RSTIN <sup>2)</sup> ) | V <sub>OL</sub>  | CC | -                            | 0.45                         | V    | $I_{OL} = 2.4 \text{ mA}^{3)}$<br>$I_{OL} = 0.5 \text{ mA}^{4)}$ |

| Output low voltage<br>(Port 9)                                                                             | V <sub>OL9</sub> | CC | _                            | 0.4                          | V    | <i>I</i> <sub>OL</sub> = 3.0 mA                                  |

- <sup>6)</sup> These parameters describe the  $\overline{\text{RSTIN}}$  pullup, which equals a resistance of ca. 50 to 250 k $\Omega$ .

- <sup>7)</sup> The maximum current may be drawn while the respective signal line remains inactive.

- <sup>8)</sup> The minimum current must be drawn in order to drive the respective signal line active.

- <sup>9)</sup> This specification is valid during Reset and during Hold-mode or Adapt-mode. During Hold-mode Port 6 pins are only affected, if they are used (configured) for CS output and the open drain function is not enabled. The READY-pullup is always active, except for Powerdown mode.

- <sup>10)</sup> This specification is valid during Reset and during Adapt-mode.

- <sup>11)</sup> Not 100% tested, guaranteed by design and characterization.

#### Power Consumption C161CS/JC/JI

(Operating Conditions apply)

| Parameter                                                                                          | Symbol                                 | Symbol Limit |                                | Unit | <b>Test Condition</b>                                                                 |

|----------------------------------------------------------------------------------------------------|----------------------------------------|--------------|--------------------------------|------|---------------------------------------------------------------------------------------|

|                                                                                                    |                                        | min.         | max.                           |      |                                                                                       |

| Power supply current (active) with all peripherals active                                          | I <sub>DD</sub>                        | _            | 15 +<br>2.5 × f <sub>CPU</sub> | mA   | $\frac{\text{RSTIN}}{f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}}$                   |

| Idle mode supply current<br>with all peripherals active                                            | I <sub>IDX</sub>                       | -            | 5 +<br>1.5 × f <sub>CPU</sub>  | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$     |

| Idle mode supply curr., Main osc,<br>with all peripherals deactivated,<br>PLL off, SDD factor = 32 | I <sub>IDOM</sub> <sup>2)</sup>        | _            | 500 +<br>50 × f <sub>OSC</sub> | μA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$<br>$f_{\text{OSC}}$ in [MHz] <sup>1)</sup> |

| Idle mode supply curr., Aux. osc,<br>with all peripherals deactivated,<br>PLL off, SDD factor = 32 | I <sub>IDOA</sub> <sup>2)</sup>        | _            | 100                            | μA   | $V_{\text{DD}} = V_{\text{DDmax}}$<br>$f_{\text{OSC}} = 32 \text{ kHz}^{3)}$          |

| Sleep and Power-down mode<br>supply current with RTC running<br>on main oscillator                 | <i>I</i> <sub>PDRM</sub> <sup>2)</sup> | _            | 200 +<br>25 × f <sub>OSC</sub> | μA   | $V_{\text{DD}} = V_{\text{DDmax}}$<br>$f_{\text{OSC}}$ in [MHz] <sup>3)</sup>         |

| Sleep and Power-down mode supply current with RTC disabled                                         | I <sub>PDO</sub>                       | _            | 50                             | μA   | $V_{\rm DD} = V_{\rm DDmax}^{3)}$                                                     |

<sup>1)</sup> The supply current is a function of the operating frequency. This dependency is illustrated in Figure 10. These parameters are tested at V<sub>DDmax</sub> and maximum CPU clock with all outputs disconnected and all inputs at V<sub>IL</sub> or V<sub>IH</sub>.

- <sup>2)</sup> This parameter is determined mainly by the current consumed by the oscillator (see Figure 9). This current, however, is influenced by the external oscillator circuitry (crystal, capacitors). The values given refer to a typical circuitry and may change in case of a not optimized external oscillator circuitry.

- <sup>3)</sup> This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  0.1 V to  $V_{DD}$ , all outputs (including pins configured as outputs) disconnected.

# A/D Converter Characteristics

(Operating Conditions apply)

| Table 13 | A/D Converter Characteristics |

|----------|-------------------------------|

|----------|-------------------------------|

| Parameter                     | Symbol            |    | Limit                 | Values                       | Unit | Test                                    |  |

|-------------------------------|-------------------|----|-----------------------|------------------------------|------|-----------------------------------------|--|

|                               |                   |    | min.                  | max.                         |      | Condition                               |  |

| Analog reference supply       | VAREF             | SR | 4.0                   | V <sub>DD</sub> + 0.1        | V    | 1)                                      |  |

| Analog reference ground       | VAGNE             | SR | V <sub>SS</sub> - 0.1 | $V_{\rm SS}$ + 0.2           | V    |                                         |  |

| Analog input voltage range    | $V_{AIN}$         | SR | V <sub>AGND</sub>     | V <sub>AREF</sub>            | V    | 2)                                      |  |

| Basic clock frequency         | f <sub>BC</sub>   |    | 0.5                   | 6.25                         | MHz  | 3)                                      |  |

| Conversion time               | t <sub>C</sub>    | CC | _                     | 40 <i>t</i> <sub>BC</sub> +  | _    | 4)                                      |  |

|                               |                   |    |                       | $t_{\rm S}$ + $2t_{\rm CPU}$ |      | $t_{\rm CPU} = 1 / f_{\rm CPU}$         |  |

| Calibration time after reset  | t <sub>CAL</sub>  | CC | -                     | 3328 t <sub>BC</sub>         | -    | 5)                                      |  |

| Total unadjusted error        | TUE               | CC | -                     | ±2                           | LSB  | 1)                                      |  |

| Internal resistance of        | R <sub>AREF</sub> | SR | _                     | t <sub>BC</sub> / 60         | kΩ   | t <sub>BC</sub> in [ns] <sup>6)7)</sup> |  |

| reference voltage source      |                   |    |                       | - 0.25                       |      |                                         |  |

| Internal resistance of analog | R <sub>ASRC</sub> | SR | _                     | t <sub>S</sub> / 450         | kΩ   | t <sub>S</sub> in [ns] <sup>7)8)</sup>  |  |

| source                        |                   |    |                       | - 0.25                       |      |                                         |  |

| ADC input capacitance         | $C_{AIN}$         | CC | -                     | 33                           | pF   | 7)                                      |  |

<sup>1)</sup> TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V,  $V_{DD}$  = 4.9 V. It is guaranteed by design for all other voltages within the defined voltage range.

If the analog reference supply voltage exceeds the power supply voltage by up to 0.2 V (i.e.  $V_{AREF} = V_{DD} = +0.2$  V) the maximum TUE is increased to ±3 LSB. This range is not 100% tested. The specified TUE is guaranteed only if the absolute sum of input overload currents on Port 5 pins (see  $I_{OV}$  specification) does not exceed 10 mA.

During the reset calibration sequence the maximum TUE may be  $\pm 4$  LSB.

- <sup>2)</sup> V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- <sup>3)</sup> The limit values for  $f_{BC}$  must not be exceeded when selecting the CPU frequency and the ADCTC setting.

- <sup>4)</sup> This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time to load the result register with the conversion result.

Values for the basic clock t<sub>BC</sub> depend on programming and can be taken from Table 14.

This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

- <sup>5)</sup> During the reset calibration conversions can be executed (with the current accuracy). The time required for these conversions is added to the total reset calibration time.

- <sup>6)</sup> During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference voltage source must allow the capacitance to reach its respective voltage level within each conversion step. The maximum internal resistance results from the programmed conversion timing.

- <sup>7)</sup> Not 100% tested, guaranteed by design and characterization.

# Multiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                 |    |                            | Max. CPU Clock<br>= 25 MHz    |                                      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz                 |    |  |

|----------------------------------------------------------------------------------------|------------------------|----|----------------------------|-------------------------------|--------------------------------------|--------------------------------------------------------------|----|--|

|                                                                                        |                        |    | min.                       | max.                          | min.                                 | max.                                                         |    |  |

| RD, WR low time<br>(no RW-delay)                                                       | <i>t</i> <sub>13</sub> | CC | $50 + t_{\rm C}$           | -                             | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |  |

| RD to valid data in<br>(with RW-delay)                                                 | <i>t</i> <sub>14</sub> | SR | -                          | $20 + t_{\rm C}$              | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |  |

| RD to valid data in (no RW-delay)                                                      | t <sub>15</sub>        | SR | -                          | $40 + t_{\rm C}$              | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |  |

| ALE low to valid data in                                                               | <i>t</i> <sub>16</sub> | SR | -                          | $40 + t_{A} + t_{C}$          | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub> | ns |  |

| Address to valid data in                                                               | t <sub>17</sub>        | SR | -                          | $50 + 2t_A + t_C$             | -                                    | $4TCL - 30 + 2t_A + t_C$                                     | ns |  |

| Data hold after RD rising edge                                                         | t <sub>18</sub>        | SR | 0                          | _                             | 0                                    | -                                                            | ns |  |

| Data float after RD                                                                    | <i>t</i> <sub>19</sub> | SR | _                          | 26 + <i>t</i> <sub>F</sub>    | -                                    | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>                         | ns |  |

| Data valid to WR                                                                       | t <sub>22</sub>        | CC | $20 + t_{\rm C}$           | -                             | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | _                                                            | ns |  |

| Data hold after $\overline{WR}$                                                        | <i>t</i> <sub>23</sub> | CC | 26 + $t_{\rm F}$           | -                             | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |  |

| ALE rising edge after $\overline{RD}$ , $\overline{WR}$                                | t <sub>25</sub>        | CC | 26 + $t_{\rm F}$           | -                             | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |  |

| Address hold after RD,<br>WR                                                           | t <sub>27</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                             | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |  |

| ALE falling edge to $\overline{CS}^{1)}$                                               | t <sub>38</sub>        | CC | -4 - t <sub>A</sub>        | 10 - <i>t</i> <sub>A</sub>    | -4 - <i>t</i> <sub>A</sub>           | 10 - <i>t</i> <sub>A</sub>                                   | ns |  |

| CS low to Valid Data In <sup>1)</sup>                                                  | t <sub>39</sub>        | SR | -                          | 40<br>+ $t_{C}$<br>+ $2t_{A}$ | _                                    | $3TCL - 20 + t_C + 2t_A$                                     | ns |  |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{1)}$ | <i>t</i> <sub>40</sub> | CC | 46 + <i>t</i> <sub>F</sub> | -                             | 3TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |  |

| ALE fall. edge to RdCS,<br>WrCS (with RW delay)                                        | t <sub>42</sub>        | CC | 16 + <i>t</i> <sub>A</sub> | -                             | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | _                                                            | ns |  |

# **AC Characteristics**

## **Demultiplexed Bus**

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                      | Symbol                 |    |                            | Max. CPU Clock<br>= 25 MHz |                                      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz                 |    |  |

|----------------------------------------------------------------|------------------------|----|----------------------------|----------------------------|--------------------------------------|--------------------------------------------------------------|----|--|

|                                                                |                        |    | min.                       | max.                       | min.                                 | max.                                                         |    |  |

| ALE high time                                                  | <i>t</i> <sub>5</sub>  | СС | 10 + <i>t</i> <sub>A</sub> | _                          | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |  |

| Address setup to ALE                                           | <i>t</i> <sub>6</sub>  | CC | $4 + t_A$                  | -                          | TCL - 16<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |  |

| ALE falling edge to $\overline{RD}$ ,<br>WR (with RW-delay)    | <i>t</i> 8             | CC | $10 + t_{A}$               | -                          | TCL - 10<br>+ <i>t</i> <sub>A</sub>  | -                                                            | ns |  |

| ALE falling edge to $\overline{RD}$ ,<br>WR (no RW-delay)      | t <sub>9</sub>         | CC | $-10 + t_{A}$              | -                          | -10<br>+ <i>t</i> <sub>A</sub>       | -                                                            | ns |  |

| RD, WR low time<br>(with RW-delay)                             | <i>t</i> <sub>12</sub> | CC | $30 + t_{\rm C}$           | -                          | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |  |

| RD, WR low time<br>(no RW-delay)                               | <i>t</i> <sub>13</sub> | CC | $50 + t_{\rm C}$           | -                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |  |

| RD to valid data in (with RW-delay)                            | <i>t</i> <sub>14</sub> | SR | -                          | $20 + t_{\rm C}$           | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |  |

| RD to valid data in (no RW-delay)                              | t <sub>15</sub>        | SR | -                          | $40 + t_{\rm C}$           | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |  |

| ALE low to valid data in                                       | <i>t</i> <sub>16</sub> | SR | -                          | $40 + t_A + t_C$           | _                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub> | ns |  |

| Address to valid data in                                       | t <sub>17</sub>        | SR | -                          | $50 + 2t_A + t_C$          | _                                    | $4TCL - 30 + 2t_A + t_C$                                     | ns |  |

| Data hold after RD rising edge                                 | t <sub>18</sub>        | SR | 0                          | -                          | 0                                    | -                                                            | ns |  |

| Data float after RD rising edge (with RW-delay <sup>1)</sup> ) | <i>t</i> <sub>20</sub> | SR | -                          | $26 + 2t_A + t_F^{(1)}$    | _                                    | 2TCL - 14<br>+ $22t_A$<br>+ $t_F^{(1)}$                      | ns |  |

| Data float after RD rising edge (no RW-delay <sup>1)</sup> )   | <i>t</i> <sub>21</sub> | SR | -                          | $10 + 2t_A + t_F^{(1)}$    | -                                    | TCL - 10<br>+ $22t_A$<br>+ $t_F^{(1)}$                       | ns |  |

# Demultiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                            | Symbol                    | Max. CPU Clock<br>= 25 MHz |             | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                  | Unit |

|------------------------------------------------------|---------------------------|----------------------------|-------------|----------------------------------------------|----------------------------------|------|

|                                                      |                           | min.                       | max.        | min.                                         | max.                             |      |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup> | <i>t</i> <sub>68</sub> SR | _                          | $0 + t_{F}$ | -                                            | TCL - 20<br>+ $2t_A + t_F^{(1)}$ | ns   |

| Address hold after<br>RdCS, WrCS                     | <i>t</i> <sub>55</sub> CC | -6 + <i>t</i> <sub>F</sub> | _           | -6 + <i>t</i> <sub>F</sub>                   | -                                | ns   |

| Data hold after WrCS                                 | <i>t</i> <sub>57</sub> CC | $6 + t_{F}$                | _           | TCL - 14 +<br><i>t</i> <sub>F</sub>          | _                                | ns   |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

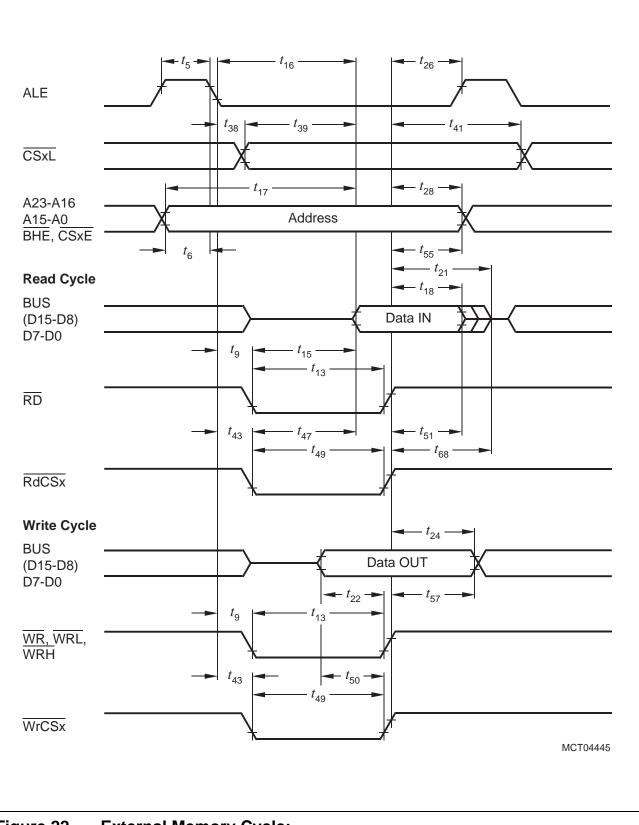

#### Figure 22 External Memory Cycle: Demultiplexed Bus, No Read/Write Delay, Normal ALE

# **AC Characteristics**

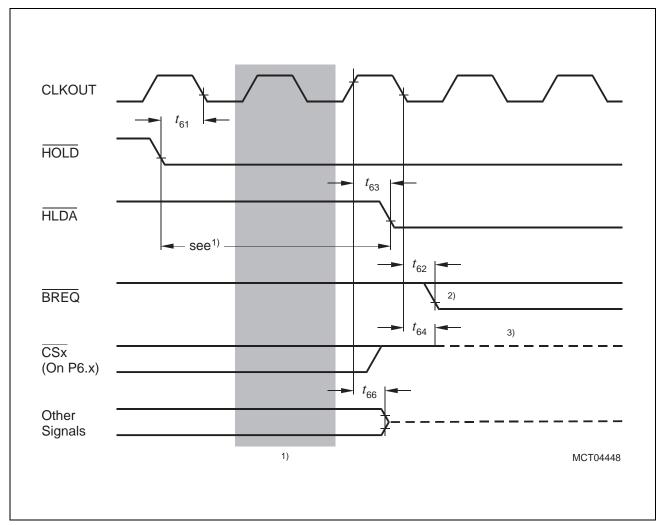

## **External Bus Arbitration**

(Operating Conditions apply)

| Parameter                                | Symbol                    | Max. CPU Clock<br>= 25 MHz |      | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |      | Unit |

|------------------------------------------|---------------------------|----------------------------|------|----------------------------------------------|------|------|

|                                          |                           | min.                       | max. | min.                                         | max. |      |

| HOLD input setup time to CLKOUT          | <i>t</i> <sub>61</sub> SR | 20                         | -    | 20                                           | -    | ns   |

| CLKOUT to HLDA high or BREQ low delay    | <i>t</i> <sub>62</sub> CC | -                          | 20   | -                                            | 20   | ns   |

| CLKOUT to HLDA low<br>or BREQ high delay | <i>t</i> <sub>63</sub> CC | -                          | 20   | -                                            | 20   | ns   |

| CSx release                              | t <sub>64</sub> CC        | -                          | 20   | -                                            | 20   | ns   |

| CSx drive                                | t <sub>65</sub> CC        | -4                         | 24   | -4                                           | 24   | ns   |

| Other signals release                    | t <sub>66</sub> CC        | _                          | 20   | -                                            | 20   | ns   |

| Other signals drive                      | t <sub>67</sub> CC        | - 4                        | 24   | - 4                                          | 24   | ns   |

Figure 25 External Bus Arbitration, Releasing the Bus

- **Notes** <sup>1)</sup> The C161CS/JC/JI will complete the currently running bus cycle before granting bus access.

- <sup>2)</sup> This is the first possibility for BREQ to get active.

- <sup>3)</sup> The  $\overline{CS}$  outputs will be resistive high (pullup) after  $t_{64}$ .

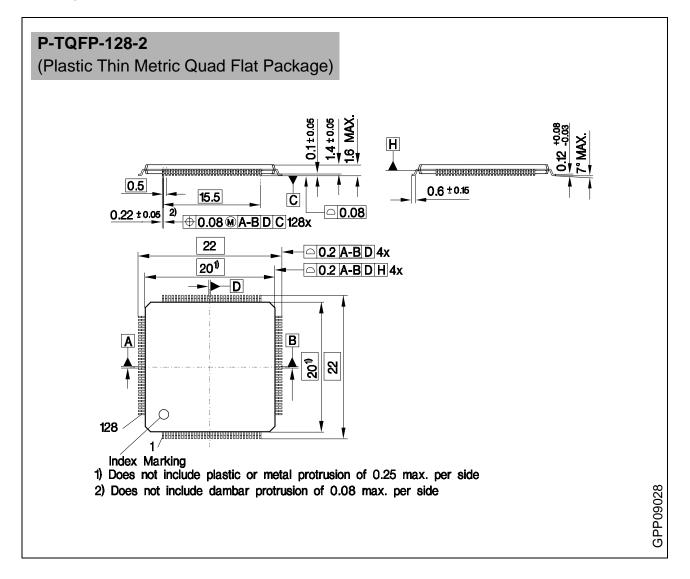

## Package Outline

#### Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device