Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SLDM, SPI, UART/USART                            |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 93                                                                          |

| Program Memory Size        | ·                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 10K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 128-LQFP                                                                    |

| Supplier Device Package    | PG-TQFP-128-2                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-c161ji-lf-ca |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet, V3.0, Jan. 2001

# C161CS-32R/-L C161JC-32R/-L C161JI-32R/-L

16-Bit Single-Chip Microcontroller

## Microcontrollers

Never stop thinking.

| Table 2 | F          | Pin Defini     | tions and F | unctions                                                                                                                                                                         | (cont'd)                              |  |  |  |  |  |  |

|---------|------------|----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|

| Symbol  | Pin<br>No. | Input<br>Outp. | Function    |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5      |            | I              | The pins c  | Port 5 is a 12-bit input-only port with Schmitt-Trigger char.<br>The pins of Port 5 also serve as analog input channels for the<br>A/D converter, or they serve as timer inputs: |                                       |  |  |  |  |  |  |

| P5.0    | 27         | 1              | AN0         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.1    | 28         | 1              | AN1         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.2    | 29         | 1              | AN2         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.3    | 30         | 1              | AN3         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.4    | 31         | 1              | AN4         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.5    | 32         | 1              | AN5         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.6    | 33         | 1              | AN6         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.7    | 34         | 1              | AN7         |                                                                                                                                                                                  |                                       |  |  |  |  |  |  |

| P5.12   | 37         | 1              | AN12,       | T6IN                                                                                                                                                                             | GPT2 Timer T6 Count Inp.              |  |  |  |  |  |  |

| P5.13   | 38         | 1              | AN13,       | T5IN                                                                                                                                                                             | GPT2 Timer T5 Count Inp.              |  |  |  |  |  |  |

| P5.14   | 39         | 1              | AN14,       | T4EUD                                                                                                                                                                            | GPT1 Timer T4 Ext. Up/Down Ctrl. Inp. |  |  |  |  |  |  |

| P5.15   | 40         |                | AN15,       | T2EUD                                                                                                                                                                            | GPT1 Timer T5 Ext. Up/Down Ctrl. Inp. |  |  |  |  |  |  |

Note: When one or both of the on-chip CAN Modules or the SDLM are used with the interface lines assigned to Port 4, the interface lines override the segment address lines and the segment address output on Port 4 is therefore limited to 6/4 bits i.e. address lines A21/A19 ... A16. CS lines can be used to increase the total amount of addressable external memory.

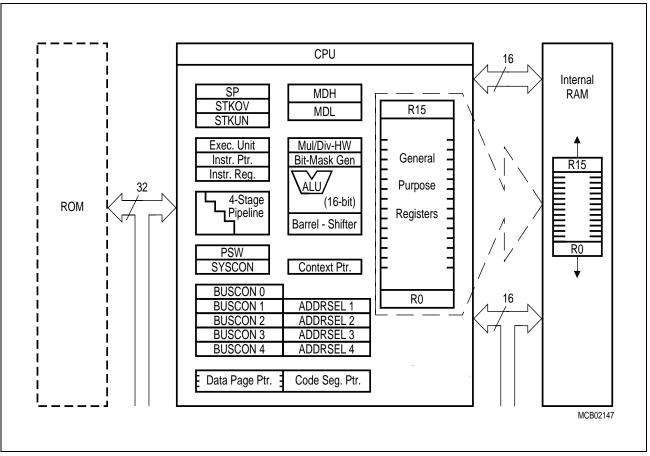

#### **Central Processing Unit (CPU)**

The main core of the CPU consists of a 4-stage instruction pipeline, a 16-bit arithmetic and logic unit (ALU) and dedicated SFRs. Additional hardware has been spent for a separate multiply and divide unit, a bit-mask generator and a barrel shifter.

Based on these hardware provisions, most of the C161CS/JC/JI's instructions can be executed in just one machine cycle which requires 80 ns at 25 MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle independent of the number of bits to be shifted. All multiple-cycle instructions have been optimized so that they can be executed very fast as well: branches in 2 cycles, a  $16 \times 16$  bit multiplication in 5 cycles and a 32-/16-bit division in 10 cycles. Another pipeline optimization, the so-called 'Jump Cache', allows reducing the execution time of repeatedly performed jumps in a loop from 2 cycles to 1 cycle.

Figure 4 CPU Block Diagram

#### Interrupt System

With an interrupt response time within a range from just 5 to 12 CPU clocks (in case of internal program execution), the C161CS/JC/JI is capable of reacting very fast to the occurrence of non-deterministic events.

The architecture of the C161CS/JC/JI supports several mechanisms for fast and flexible response to service requests that can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source or the destination pointer. An individual PEC transfer counter is implicity decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source related vector location. PEC services are very well suited, for example, for supporting the transmission or reception of blocks of data. The C161CS/JC/JI has 8 PEC channels each of which offers such fast interrupt-driven data transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable flag and an interrupt priority bitfield exists for each of the possible interrupt sources. Via its related register, each source can be programmed to one of sixteen interrupt priority levels. Once having been accepted by the CPU, an interrupt service can only be interrupted by a higher prioritized service request. For the standard interrupt processing, each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high precision requirements. These fast interrupt inputs feature programmable edge detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the 'TRAP' instruction in combination with an individual trap (interrupt) number.

**Table 3** shows all of the possible C161CS/JC/JI interrupt sources and the corresponding hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not used by associated peripherals, may be used to generate software controlled interrupt requests by setting the respective interrupt request bit (xIR).

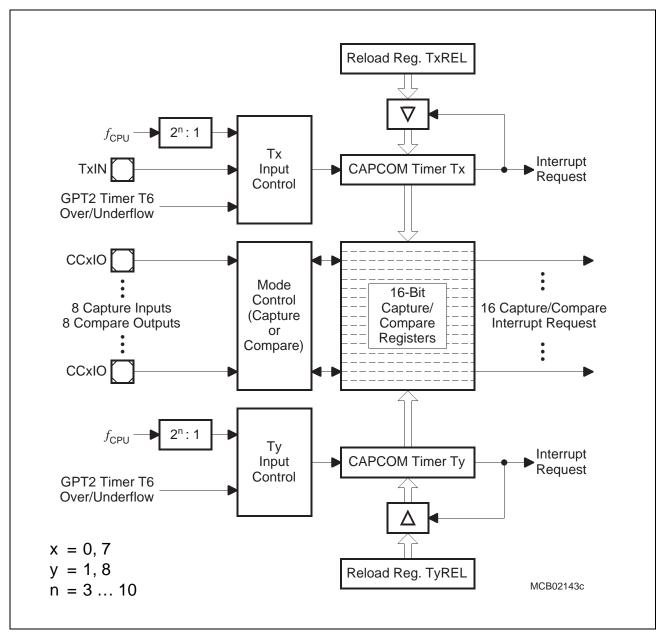

#### Capture/Compare (CAPCOM) Units

The CAPCOM units support generation and control of timing sequences on up to 32 channels with a maximum resolution of 16 TCL. The CAPCOM units are typically used to handle high speed I/O tasks such as pulse and waveform generation, pulse width modulation (PMW), Digital to Analog (D/A) conversion, software timing, or time recording relative to external events.

Four 16-bit timers (T0/T1, T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, external count inputs for CAPCOM timers T0 and T7 allow event scheduling for the capture/ compare registers relative to external events.

Both of the two capture/compare register arrays contain 16 dual purpose capture/ compare registers, each of which may be individually allocated to either CAPCOM timer T0 or T1 (T7 or T8, respectively), and programmed for capture or compare function. Eight registers of each module have one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

| Compare Modes | Function                                                                                                              |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>several compare interrupts per timer period are possible                              |

| Mode 1        | Pin toggles on each compare match;<br>several compare events per timer period are possible                            |

| Mode 2        | Interrupt-only compare mode;<br>only one compare interrupt per timer period is generated                              |

| Mode 3        | Pin set '1' on match; pin reset '0' on compare time overflow;<br>only one compare event per timer period is generated |

Table 5Compare Modes (CAPCOM)

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

Figure 5 CAPCOM Unit Block Diagram

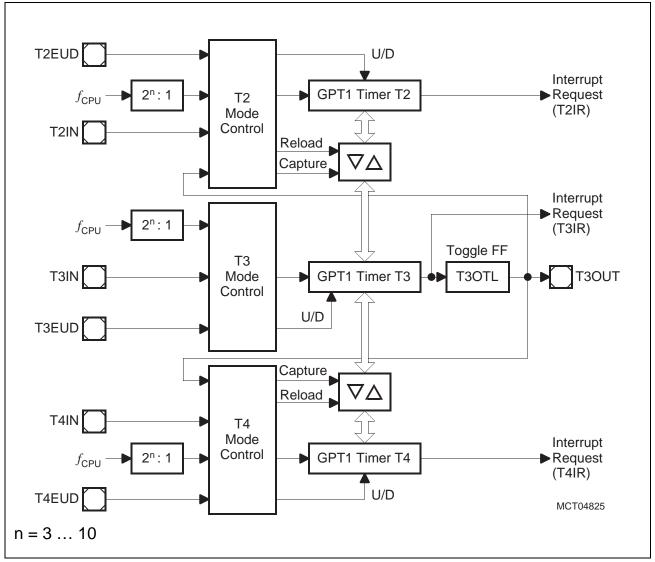

#### Figure 6 Block Diagram of GPT1

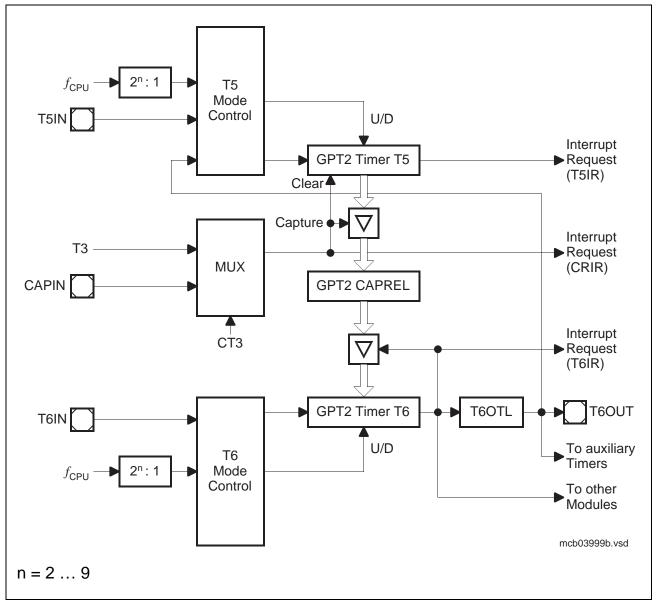

With its maximum resolution of 8 TCL, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The count direction (up/ down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM timers T0 or T1, and to cause a reload from the CAPREL register. The CAPREL register may capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared

after the capture procedure. This allows the C161CS/JC/JI to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer T3's inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

#### Serial Data Link Module (SDLM)

The Serial Data Link Module (SDLM) provides serial communication via a J1850 type multiplexed serial bus via an external J1850 bus transceiver. The module conforms to the SAE Class B J1850 specification for variable pulse width modulation (VPW). The SDLM is integrated as an on-chip peripheral and is connected to the CPU via the XBUS.

#### **General SDLM Features:**

- Compliant to the SAE Class B J1850 specification (VPW)

- Class 2 protocol fully supported

- Variable Pulse Width (VPW) operation at 10.4 kBaud

- High Speed 4X operation at 41.6 kBaud

- Programmable Normalization Bit

- Programmable Delay for transceiver interface

- Digital Noise Filter

- Power Down mode with automatic wakeup support upon bus activity

- Single Byte Header and Consolidated Header supported

- CRC generation and checking

- Receive and transmit Block Mode

#### **Data Link Operation Features:**

- 11 Byte Transmit Buffer

- Double buffered 11 Byte receive buffer (optional overwrite enable)

- Support for In Frame Response (IFR) types 1, 2 and 3

- Transmit and Receiver Message Buffers configurable for either FIFO or Byte mode

- Advanced Interrupt Handling with 8 separately enabled sources:

Error, format or bus shorted CRC error Lost Arbitration Break received In-Frame-Response request Header received Complete message received Transmit successful

- Automatic IFR transmission (Types 1 and 2) for 3-Byte consolidated headers

- User configurable clock divider

- Bus status flags (IDLE, EOF, EOD, SOF, Tx and Rx in progress)

- Note: When the SDLM is used with the interface lines assigned to Port 4, the interface lines override the segment address lines and the segment address output on Port 4 is therefore limited to 6/4 bits i.e. address lines A21/A19 ... A16. CS lines can be used to increase the total amount of addressable external memory.

#### **Instruction Set Summary**

Table 6 lists the instructions of the C161CS/JC/JI in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the **"C166 Family Instruction Set Manual"**.

This document also provides a detailled description of each instruction.

| Mnemonic           | Description                                                                                          | Bytes |

|--------------------|------------------------------------------------------------------------------------------------------|-------|

| ADD(B)             | Add word (byte) operands                                                                             | 2/4   |

| ADDC(B)            | Add word (byte) operands with Carry                                                                  | 2/4   |

| SUB(B)             | Subtract word (byte) operands                                                                        | 2/4   |

| SUBC(B)            | Subtract word (byte) operands with Carry                                                             | 2/4   |

| MUL(U)             | (Un)Signed multiply direct GPR by direct GPR (16-16-bit)                                             | 2     |

| DIV(U)             | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                            | 2     |

| DIVL(U)            | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                            | 2     |

| CPL(B)             | Complement direct word (byte) GPR                                                                    | 2     |

| NEG(B)             | Negate direct word (byte) GPR                                                                        | 2     |

| AND(B)             | Bitwise AND, (word/byte operands)                                                                    | 2/4   |

| OR(B)              | Bitwise OR, (word/byte operands)                                                                     | 2/4   |

| XOR(B)             | Bitwise XOR, (word/byte operands)                                                                    | 2/4   |

| BCLR               | Clear direct bit                                                                                     | 2     |

| BSET               | Set direct bit                                                                                       | 2     |

| BMOV(N)            | Move (negated) direct bit to direct bit                                                              | 4     |

| BAND, BOR,<br>BXOR | AND/OR/XOR direct bit with direct bit                                                                | 4     |

| BCMP               | Compare direct bit to direct bit                                                                     | 4     |

| BFLDH/L            | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data        | 4     |

| CMP(B)             | Compare word (byte) operands                                                                         | 2/4   |

| CMPD1/2            | Compare word data to GPR and decrement GPR by 1/2                                                    | 2/4   |

| CMPI1/2            | Compare word data to GPR and increment GPR by 1/2                                                    | 2/4   |

| PRIOR              | Determine number of shift cycles to normalize direct<br>word GPR and store result in direct word GPR | 2     |

| SHL / SHR          | Shift left/right direct word GPR                                                                     | 2     |

| ROL / ROR          | Rotate left/right direct word GPR                                                                    | 2     |

| ASHR               | Arithmetic (sign bit) shift right direct word GPR                                                    | 2     |

#### Table 6Instruction Set Summary

#### Table 7 C161CS/JC/JI Registers, Ordered by Name (cont'd)

| Name   |   | Physical<br>Address |   | 8-Bit<br>Addr.  | Description                             | Reset<br>Value    |

|--------|---|---------------------|---|-----------------|-----------------------------------------|-------------------|

| IDPROG |   | F078 <sub>H</sub>   | Ε | 3C <sub>H</sub> | Identifier                              | XXXX <sub>H</sub> |

| IFR    |   | EB18 <sub>H</sub>   | Χ |                 | SDLM In-Frame Response Register         | 0000 <sub>H</sub> |

| INTCON |   | EB2C <sub>H</sub>   | Χ |                 | SDLM Interrupt Control Register         | 0000 <sub>H</sub> |

| IPCR   |   | EB04 <sub>H</sub>   | Χ |                 | SDLM Interface Port Connect Register    | 0007 <sub>H</sub> |

| ISNC   |   | F1DE <sub>H</sub>   | Е | EF <sub>H</sub> | Interrupt Subnode Control Register      | 0000 <sub>H</sub> |

| MDC    | b | FF0E <sub>H</sub>   |   | 87 <sub>H</sub> | CPU Multiply Divide Control Register    | 0000 <sub>H</sub> |

| MDH    |   | FE0C <sub>H</sub>   |   | 06 <sub>H</sub> | CPU Multiply Divide Reg. – High Word    | 0000 <sub>H</sub> |

| MDL    |   | FE0E <sub>H</sub>   |   | 07 <sub>H</sub> | CPU Multiply Divide Reg. – Low Word     | 0000 <sub>H</sub> |

| ODP2   | b | F1C2 <sub>H</sub>   | Ε | E1 <sub>H</sub> | Port 2 Open Drain Control Register      | 0000 <sub>H</sub> |

| ODP3   | b | F1C6 <sub>H</sub>   | Ε | E3 <sub>H</sub> | Port 3 Open Drain Control Register      | 0000 <sub>H</sub> |

| ODP4   | b | F1CA <sub>H</sub>   | Ε | E5 <sub>H</sub> | Port 4 Open Drain Control Register      | 00 <sub>H</sub>   |

| ODP6   | b | F1CE <sub>H</sub>   | Е | E7 <sub>H</sub> | Port 6 Open Drain Control Register      | 00 <sub>H</sub>   |

| ODP7   | b | F1D2 <sub>H</sub>   | Ε | E9 <sub>H</sub> | Port 7 Open Drain Control Register      | 00 <sub>H</sub>   |

| ONES   | b | FF1E <sub>H</sub>   |   | 8F <sub>H</sub> | Constant Value 1's Register (read only) | FFFF <sub>H</sub> |

| P0H    | b | FF02 <sub>H</sub>   |   | 81 <sub>H</sub> | Port 0 High Reg. (Upper half of PORT0)  | 00 <sub>H</sub>   |

| P0L    | b | FF00 <sub>H</sub>   |   | 80 <sub>H</sub> | Port 0 Low Reg. (Lower half of PORT0)   | 00 <sub>H</sub>   |

| P1H    | b | FF06 <sub>H</sub>   |   | 83 <sub>H</sub> | Port 1 High Reg. (Upper half of PORT1)  | 00 <sub>H</sub>   |

| P1L    | b | FF04 <sub>H</sub>   |   | 82 <sub>H</sub> | Port 1 Low Reg. (Lower half of PORT1)   | 00 <sub>H</sub>   |

| P2     | b | FFC0 <sub>H</sub>   |   | E0 <sub>H</sub> | Port 2 Register                         | 0000 <sub>H</sub> |

| P3     | b | FFC4 <sub>H</sub>   |   | E2 <sub>H</sub> | Port 3 Register                         | 0000 <sub>H</sub> |

| P4     | b | FFC8 <sub>H</sub>   |   | E4 <sub>H</sub> | Port 4 Register (7 bits)                | 00 <sub>H</sub>   |

| P5     | b | FFA2 <sub>H</sub>   |   | D1 <sub>H</sub> | Port 5 Register (read only)             | XXXX <sub>H</sub> |

| P6     | b | $FFCC_{H}$          |   | E6 <sub>H</sub> | Port 6 Register (8 bits)                | 00 <sub>H</sub>   |

| P7     | b | FFD0 <sub>H</sub>   |   | E8 <sub>H</sub> | Port 7 Register (8 bits)                | 00 <sub>H</sub>   |

| P9     | b | FFD8 <sub>H</sub>   |   | ECH             | Port 9 Register (8 bits)                | 00 <sub>H</sub>   |

| PECC0  |   | FEC0 <sub>H</sub>   |   | 60 <sub>H</sub> | PEC Channel 0 Control Register          | 0000 <sub>H</sub> |

| PECC1  |   | FEC2 <sub>H</sub>   |   | 61 <sub>H</sub> | PEC Channel 1 Control Register          | 0000 <sub>H</sub> |

| PECC2  |   | FEC4 <sub>H</sub>   |   | 62 <sub>H</sub> | PEC Channel 2 Control Register          | 0000 <sub>H</sub> |

| PECC3  |   | FEC6 <sub>H</sub>   |   | 63 <sub>H</sub> | PEC Channel 3 Control Register          | 0000 <sub>H</sub> |

| PECC4  |   | FEC8 <sub>H</sub>   |   | 64 <sub>H</sub> | PEC Channel 4 Control Register          | 0000 <sub>H</sub> |

| PECC5  |   | FECA <sub>H</sub>   |   | 65 <sub>H</sub> | PEC Channel 5 Control Register          | 0000 <sub>H</sub> |

| PECC6  |   | FECC <sub>H</sub>   |   | 66 <sub>H</sub> | PEC Channel 6 Control Register          | 0000 <sub>H</sub> |

#### Table 7 C161CS/JC/JI Registers, Ordered by Name (cont'd)

| Name    |   |                   |   | 8-Bit<br>Addr.  | Description                             | Reset<br>Value                  |

|---------|---|-------------------|---|-----------------|-----------------------------------------|---------------------------------|

| SYSCON  | b | FF12 <sub>H</sub> |   | 89 <sub>H</sub> | CPU System Configuration Register       | <sup>1)</sup> 0XX0 <sub>H</sub> |

| SYSCON1 | b | F1DC <sub>H</sub> | Ε | EEH             | CPU System Configuration Register 1     | 0000 <sub>H</sub>               |

| SYSCON2 | b | F1D0 <sub>H</sub> | Ε | E8 <sub>H</sub> | CPU System Configuration Register 2     | 0000 <sub>H</sub>               |

| SYSCON3 | b | F1D4 <sub>H</sub> | Ε | EA <sub>H</sub> | CPU System Configuration Register 3     | 0X00 <sub>H</sub>               |

| Т0      |   | FE50 <sub>H</sub> |   | 28 <sub>H</sub> | CAPCOM Timer 0 Register                 | 0000 <sub>H</sub>               |

| T01CON  | b | FF50 <sub>H</sub> |   | A8 <sub>H</sub> | CAPCOM Timer 0 and Timer 1 Ctrl. Reg.   | 0000 <sub>H</sub>               |

| TOIC    | b | FF9C <sub>H</sub> |   | CEH             | CAPCOM Timer 0 Interrupt Ctrl. Reg.     | 0000 <sub>H</sub>               |

| TOREL   |   | FE54 <sub>H</sub> |   | 2A <sub>H</sub> | CAPCOM Timer 0 Reload Register          | 0000 <sub>H</sub>               |

| T1      |   | FE52 <sub>H</sub> |   | 29 <sub>H</sub> | CAPCOM Timer 1 Register                 | 0000 <sub>H</sub>               |

| T14     |   | F0D2 <sub>H</sub> | Ε | 69 <sub>H</sub> | RTC Timer 14 Register                   | no                              |

| T14REL  |   | F0D0 <sub>H</sub> | Ε | 68 <sub>H</sub> | RTC Timer 14 Reload Register            | no                              |

| T1IC    | b | FF9E <sub>H</sub> |   | CF <sub>H</sub> | CAPCOM Timer 1 Interrupt Ctrl. Reg.     | 0000 <sub>H</sub>               |

| T1REL   |   | FE56 <sub>H</sub> |   | 2B <sub>H</sub> | CAPCOM Timer 1 Reload Register          | 0000 <sub>H</sub>               |

| T2      |   | FE40 <sub>H</sub> |   | 20 <sub>H</sub> | GPT1 Timer 2 Register                   | 0000 <sub>H</sub>               |

| T2CON   | b | FF40 <sub>H</sub> |   | A0 <sub>H</sub> | GPT1 Timer 2 Control Register           | 0000 <sub>H</sub>               |

| T2IC    | b | FF60 <sub>H</sub> |   | B0 <sub>H</sub> | GPT1 Timer 2 Interrupt Control Register | 0000 <sub>H</sub>               |

| Т3      |   | FE42 <sub>H</sub> |   | 21 <sub>H</sub> | GPT1 Timer 3 Register                   | 0000 <sub>H</sub>               |

| T3CON   | b | FF42 <sub>H</sub> |   | A1 <sub>H</sub> | GPT1 Timer 3 Control Register           | 0000 <sub>H</sub>               |

| T3IC    | b | FF62 <sub>H</sub> |   | B1 <sub>H</sub> | GPT1 Timer 3 Interrupt Control Register | 0000 <sub>H</sub>               |

| T4      |   | FE44 <sub>H</sub> |   | 22 <sub>H</sub> | GPT1 Timer 4 Register                   | 0000 <sub>H</sub>               |

| T4CON   | b | FF44 <sub>H</sub> |   | A2 <sub>H</sub> | GPT1 Timer 4 Control Register           | 0000 <sub>H</sub>               |

| T4IC    | b | FF64 <sub>H</sub> |   | B2 <sub>H</sub> | GPT1 Timer 4 Interrupt Control Register | 0000 <sub>H</sub>               |

| Т5      |   | FE46 <sub>H</sub> |   | 23 <sub>H</sub> | GPT2 Timer 5 Register                   | 0000 <sub>H</sub>               |

| T5CON   | b | FF46 <sub>H</sub> |   | A3 <sub>H</sub> | GPT2 Timer 5 Control Register           | 0000 <sub>H</sub>               |

| T5IC    | b | FF66 <sub>H</sub> |   | B3 <sub>H</sub> | GPT2 Timer 5 Interrupt Control Register | 0000 <sub>H</sub>               |

| Т6      |   | FE48 <sub>H</sub> |   | 24 <sub>H</sub> | GPT2 Timer 6 Register                   | 0000 <sub>H</sub>               |

| T6CON   | b | FF48 <sub>H</sub> |   | A4 <sub>H</sub> | GPT2 Timer 6 Control Register           | 0000 <sub>H</sub>               |

| T6IC    | b | FF68 <sub>H</sub> |   | B4 <sub>H</sub> | GPT2 Timer 6 Interrupt Control Register | 0000 <sub>H</sub>               |

| T7      |   | F050 <sub>H</sub> | Ε | 28 <sub>H</sub> | CAPCOM Timer 7 Register                 | 0000 <sub>H</sub>               |

| T78CON  | b | FF20 <sub>H</sub> |   | 90 <sub>H</sub> | CAPCOM Timer 7 and 8 Ctrl. Reg.         | 0000 <sub>H</sub>               |

| T7IC    | b | F17A <sub>H</sub> | Ε | BD <sub>H</sub> | CAPCOM Timer 7 Interrupt Ctrl. Reg.     | 0000 <sub>H</sub>               |

| T7REL   |   | F054 <sub>H</sub> | Ε | 2A <sub>H</sub> | CAPCOM Timer 7 Reload Register          | 0000 <sub>H</sub>               |

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C161CS/ JC/JI and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

#### CC (Controller Characteristics):

The logic of the C161CS/JC/JI will provide signals with the respective timing characteristics.

#### SR (System Requirement):

The external system must provide signals with the respective timing characteristics to the C161CS/JC/JI.

#### **DC Characteristics**

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                                                                  | Symbol           |    | Limit                        | Values                       | Unit | Test Condition                                                   |

|------------------------------------------------------------------------------------------------------------|------------------|----|------------------------------|------------------------------|------|------------------------------------------------------------------|

|                                                                                                            |                  |    | min.                         | max.                         |      |                                                                  |

| Input low voltage (TTL,<br>all except XTAL1, XTAL3, Port 9)                                                | $V_{IL}$         | SR | -0.5                         | 0.2 V <sub>DD</sub><br>- 0.1 | V    | _                                                                |

| Input low voltage<br>XTAL1, XTAL3, Port 9                                                                  | V <sub>IL2</sub> | SR | -0.5                         | 0.3 V <sub>DD</sub>          | V    | _                                                                |

| Input low voltage<br>(Special Threshold)                                                                   | V <sub>ILS</sub> | SR | -0.5                         | 2.0                          | V    | _                                                                |

| Input high voltage (TTL, all<br>except RSTIN, XTAL1, XTAL3,<br>Port 9)                                     | V <sub>IH</sub>  | SR | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> +<br>0.5     | V    | _                                                                |

| Input high voltage RSTIN (when operated as input)                                                          | V <sub>IH1</sub> | SR | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                                                |

| Input high voltage<br>XTAL1, XTAL3, Port 9                                                                 | V <sub>IH2</sub> | SR | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> +<br>0.5     | V    | _                                                                |

| Input high voltage<br>(Special Threshold)                                                                  | V <sub>IHS</sub> | SR | 0.8 V <sub>DD</sub><br>- 0.2 | V <sub>DD</sub> +<br>0.5     | V    | -                                                                |

| Input Hysteresis<br>(Special Threshold)                                                                    | HYS              |    | 400                          | _                            | mV   | Series resistance<br>= $0 \Omega$                                |

| Output low voltage<br>(PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, CLKOUT,<br>RSTOUT, RSTIN <sup>2)</sup> ) | V <sub>OL</sub>  | CC | -                            | 0.45                         | V    | $I_{OL} = 2.4 \text{ mA}^{3)}$<br>$I_{OL} = 0.5 \text{ mA}^{4)}$ |

| Output low voltage<br>(Port 9)                                                                             | V <sub>OL9</sub> | CC | _                            | 0.4                          | V    | <i>I</i> <sub>OL</sub> = 3.0 mA                                  |

P0.15-13 (P0H.7-5). Register RP0H can be loaded from the upper half of register RSTCON under software control.

**Table 10** associates the combinations of these three bits with the respective clock generation mode.

| CLKCFG<br>(P0H.7-5) | $CPU Frequency f_{CPU} = f_{OSC} \times F$ | External Clock<br>Input Range <sup>1)</sup> | Notes                      |

|---------------------|--------------------------------------------|---------------------------------------------|----------------------------|

| 1 1 1               | $f_{OSC} \times 4$                         | 2.5 to 6.25 MHz                             | Default configuration      |

| 1 1 0               | $f_{OSC} \times 3$                         | 3.33 to 8.33 MHz                            | -                          |

| 1 0 1               | $f_{OSC} \times 2$                         | 5 to 12.5 MHz                               | -                          |

| 1 0 0               | $f_{OSC} \times 5$                         | 2 to 5 MHz                                  | -                          |

| 0 1 1               | $f_{OSC} \times 1$                         | 1 to 25 MHz                                 | Direct drive <sup>2)</sup> |

| 0 1 0               | $f_{OSC} \times 1.5$                       | 6.66 to 16.6 MHz                            | -                          |

| 0 0 1               | f <sub>OSC</sub> / 2                       | 2 to 50 MHz                                 | CPU clock via prescaler    |

| 0 0 0               | $f_{\rm OSC} \times 2.5$                   | 4 to 10 MHz                                 | -                          |

Table 10

C161CS/JC/JI Clock Generation Modes

<sup>1)</sup> The external clock input range refers to a CPU clock range of 10 ... 25 MHz.

<sup>2)</sup> The maximum frequency depends on the duty cycle of the external clock signal.

#### **Prescaler Operation**

When prescaler operation is configured (CLKCFG =  $001_B$ ) the CPU clock is derived from the internal oscillator (input clock signal) by a 2:1 prescaler.

The frequency of  $f_{CPU}$  is half the frequency of  $f_{OSC}$  and the high and low time of  $f_{CPU}$  (i.e. the duration of an individual TCL) is defined by the period of the input clock  $f_{OSC}$ .

The timings listed in the AC Characteristics that refer to TCLs therefore can be calculated using the period of  $f_{OSC}$  for any TCL.

#### Phase Locked Loop

When PLL operation is configured (via CLKCFG) the on-chip phase locked loop is enabled and provides the CPU clock (see table above). The PLL multiplies the input frequency by the factor **F** which is selected via the combination of pins P0.15-13 (i.e.  $f_{CPU} = f_{OSC} \times \mathbf{F}$ ). With every **F**'th transition of  $f_{OSC}$  the PLL circuit synchronizes the CPU clock to the input clock. This synchronization is done smoothly, i.e. the CPU clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{CPU}$  is constantly adjusted so it is locked to  $f_{OSC}$ . The slight variation causes a jitter of  $f_{CPU}$  which also effects the duration of individual TCLs.

#### A/D Converter Characteristics

(Operating Conditions apply)

| Table 13 | A/D Converter Characteristics |

|----------|-------------------------------|

|----------|-------------------------------|

| Parameter                     | Symbol            |    | Limit                 | Values                       | Unit | Test                                    |  |

|-------------------------------|-------------------|----|-----------------------|------------------------------|------|-----------------------------------------|--|

|                               |                   |    | min.                  | max.                         |      | Condition                               |  |

| Analog reference supply       | VAREF             | SR | 4.0                   | V <sub>DD</sub> + 0.1        | V    | 1)                                      |  |

| Analog reference ground       | VAGNE             | SR | V <sub>SS</sub> - 0.1 | $V_{\rm SS}$ + 0.2           | V    |                                         |  |

| Analog input voltage range    | $V_{AIN}$         | SR | V <sub>AGND</sub>     | V <sub>AREF</sub>            | V    | 2)                                      |  |

| Basic clock frequency         | f <sub>BC</sub>   |    | 0.5                   | 6.25                         | MHz  | 3)                                      |  |

| Conversion time               | t <sub>C</sub>    | CC | _                     | 40 <i>t</i> <sub>BC</sub> +  | _    | 4)                                      |  |

|                               |                   |    |                       | $t_{\rm S}$ + $2t_{\rm CPU}$ |      | $t_{\rm CPU} = 1 / f_{\rm CPU}$         |  |

| Calibration time after reset  | t <sub>CAL</sub>  | CC | -                     | 3328 t <sub>BC</sub>         | -    | 5)                                      |  |

| Total unadjusted error        | TUE               | CC | -                     | ±2                           | LSB  | 1)                                      |  |

| Internal resistance of        | R <sub>AREF</sub> | SR | _                     | t <sub>BC</sub> / 60         | kΩ   | t <sub>BC</sub> in [ns] <sup>6)7)</sup> |  |

| reference voltage source      |                   |    |                       | - 0.25                       |      |                                         |  |

| Internal resistance of analog | R <sub>ASRC</sub> | SR | _                     | t <sub>S</sub> / 450         | kΩ   | t <sub>S</sub> in [ns] <sup>7)8)</sup>  |  |

| source                        |                   |    |                       | - 0.25                       |      |                                         |  |

| ADC input capacitance         | $C_{AIN}$         | CC | -                     | 33                           | pF   | 7)                                      |  |

<sup>1)</sup> TUE is tested at  $V_{AREF} = 5.0 \text{ V}$ ,  $V_{AGND} = 0 \text{ V}$ ,  $V_{DD} = 4.9 \text{ V}$ . It is guaranteed by design for all other voltages within the defined voltage range.

If the analog reference supply voltage exceeds the power supply voltage by up to 0.2 V (i.e.  $V_{AREF} = V_{DD} = +0.2$  V) the maximum TUE is increased to ±3 LSB. This range is not 100% tested. The specified TUE is guaranteed only if the absolute sum of input overload currents on Port 5 pins (see  $I_{OV}$  specification) does not exceed 10 mA.

During the reset calibration sequence the maximum TUE may be  $\pm 4$  LSB.

- <sup>2)</sup> V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- <sup>3)</sup> The limit values for  $f_{BC}$  must not be exceeded when selecting the CPU frequency and the ADCTC setting.

- <sup>4)</sup> This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time to load the result register with the conversion result.

Values for the basic clock t<sub>BC</sub> depend on programming and can be taken from Table 14.

This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

- <sup>5)</sup> During the reset calibration conversions can be executed (with the current accuracy). The time required for these conversions is added to the total reset calibration time.

- <sup>6)</sup> During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference voltage source must allow the capacitance to reach its respective voltage level within each conversion step. The maximum internal resistance results from the programmed conversion timing.

- <sup>7)</sup> Not 100% tested, guaranteed by design and characterization.

#### Multiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 6 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (120 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                 |    |                            | PU Clock<br>MHz               | Variable (<br>1 / 2TCL =             | Unit                                                         |    |

|----------------------------------------------------------------------------------------|------------------------|----|----------------------------|-------------------------------|--------------------------------------|--------------------------------------------------------------|----|

|                                                                                        |                        |    | min.                       | max.                          | min.                                 | max.                                                         |    |

| RD, WR low time<br>(no RW-delay)                                                       | <i>t</i> <sub>13</sub> | CC | $50 + t_{\rm C}$           | -                             | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                                            | ns |

| RD to valid data in<br>(with RW-delay)                                                 | <i>t</i> <sub>14</sub> | SR | -                          | $20 + t_{\rm C}$              | -                                    | 2TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| RD to valid data in (no RW-delay)                                                      | t <sub>15</sub>        | SR | -                          | $40 + t_{\rm C}$              | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>C</sub>                         | ns |

| ALE low to valid data in                                                               | <i>t</i> <sub>16</sub> | SR | -                          | $40 + t_{A} + t_{C}$          | -                                    | 3TCL - 20<br>+ <i>t</i> <sub>A</sub> + <i>t</i> <sub>C</sub> | ns |

| Address to valid data in                                                               | t <sub>17</sub>        | SR | -                          | $50 + 2t_A + t_C$             | -                                    | $4TCL - 30 + 2t_A + t_C$                                     | ns |

| Data hold after RD rising edge                                                         | t <sub>18</sub>        | SR | 0                          | _                             | 0                                    | -                                                            | ns |

| Data float after RD                                                                    | <i>t</i> <sub>19</sub> | SR | _                          | 26 + <i>t</i> <sub>F</sub>    | -                                    | 2TCL - 14<br>+ <i>t</i> <sub>F</sub>                         | ns |

| Data valid to WR                                                                       | t <sub>22</sub>        | CC | $20 + t_{\rm C}$           | -                             | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | _                                                            | ns |

| Data hold after $\overline{WR}$                                                        | <i>t</i> <sub>23</sub> | CC | 26 + $t_{\rm F}$           | -                             | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| ALE rising edge after $\overline{RD}$ , $\overline{WR}$                                | t <sub>25</sub>        | CC | 26 + $t_{\rm F}$           | -                             | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| Address hold after RD,<br>WR                                                           | t <sub>27</sub>        | CC | 26 + <i>t</i> <sub>F</sub> | -                             | 2TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| ALE falling edge to $\overline{CS}^{1)}$                                               | t <sub>38</sub>        | CC | -4 - t <sub>A</sub>        | 10 - <i>t</i> <sub>A</sub>    | -4 - <i>t</i> <sub>A</sub>           | 10 - <i>t</i> <sub>A</sub>                                   | ns |

| CS low to Valid Data In <sup>1)</sup>                                                  | t <sub>39</sub>        | SR | -                          | 40<br>+ $t_{C}$<br>+ $2t_{A}$ | _                                    | $3TCL - 20 + t_C + 2t_A$                                     | ns |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{1)}$ | <i>t</i> <sub>40</sub> | CC | 46 + <i>t</i> <sub>F</sub> | -                             | 3TCL - 14<br>+ <i>t</i> <sub>F</sub> | -                                                            | ns |

| ALE fall. edge to RdCS,<br>WrCS (with RW delay)                                        | t <sub>42</sub>        | CC | 16 + <i>t</i> <sub>A</sub> | -                             | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | _                                                            | ns |

#### Demultiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                                                              | Symbol                 |    |                             | PU Clock<br>MHz            | Variable<br>1 / 2TCL =               | Unit                                 |    |

|----------------------------------------------------------------------------------------|------------------------|----|-----------------------------|----------------------------|--------------------------------------|--------------------------------------|----|

|                                                                                        |                        |    | min.                        | max.                       | min.                                 | max.                                 |    |

| Data valid to $\overline{WR}$                                                          | <i>t</i> <sub>22</sub> | CC | $20 + t_{\rm C}$            | -                          | 2TCL - 20<br>+ <i>t</i> <sub>C</sub> | -                                    | ns |

| Data hold after $\overline{WR}$                                                        | t <sub>24</sub>        | CC | 10 + <i>t</i> <sub>F</sub>  | -                          | TCL - 10<br>+ <i>t</i> <sub>F</sub>  | -                                    | ns |

| ALE rising edge after $\overline{RD}$ , $\overline{WR}$                                | t <sub>26</sub>        | CC | -10 + <i>t</i> <sub>F</sub> | -                          | -10 + <i>t</i> <sub>F</sub>          | -                                    | ns |

| Address hold after $\overline{WR}^{2)}$                                                | t <sub>28</sub>        | CC | $0 + t_{F}$                 | -                          | $0 + t_{F}$                          | -                                    | ns |

| ALE falling edge to $\overline{\text{CS}}^{3)}$                                        | t <sub>38</sub>        | CC | -4 - t <sub>A</sub>         | 10 - <i>t</i> <sub>A</sub> | -4 - t <sub>A</sub>                  | 10 - <i>t</i> <sub>A</sub>           | ns |

| $\overline{\text{CS}}$ low to Valid Data $\ln^{3)}$                                    | t <sub>39</sub>        | SR | _                           | $40 + t_{C} + 2t_{A}$      | _                                    | $3TCL - 20 + t_C + 2t_A$             | ns |

| $\overline{\text{CS}}$ hold after $\overline{\text{RD}}$ , $\overline{\text{WR}}^{3)}$ | <i>t</i> <sub>41</sub> | CC | 6 + <i>t</i> <sub>F</sub>   | -                          | TCL - 14<br>+ <i>t</i> <sub>F</sub>  | -                                    | ns |

| ALE falling edge to RdCS,<br>WrCS (with RW-delay)                                      | t <sub>42</sub>        | CC | 16 + <i>t</i> <sub>A</sub>  | -                          | TCL - 4<br>+ <i>t</i> <sub>A</sub>   | -                                    | ns |

| ALE falling edge to RdCS,<br>WrCS (no RW-delay)                                        | <i>t</i> <sub>43</sub> | CC | $-4 + t_{A}$                | -                          | -4<br>+ t <sub>A</sub>               | _                                    | ns |

| RdCS to Valid Data In (with RW-delay)                                                  | <i>t</i> <sub>46</sub> | SR | _                           | 16 + <i>t</i> <sub>C</sub> | _                                    | 2TCL - 24<br>+ <i>t</i> <sub>C</sub> | ns |

| RdCS to Valid Data In (no RW-delay)                                                    | <i>t</i> <sub>47</sub> | SR | -                           | $36 + t_{\rm C}$           | -                                    | 3TCL - 24<br>+ <i>t</i> <sub>C</sub> | ns |

| RdCS, WrCS Low Time<br>(with RW-delay)                                                 | t <sub>48</sub>        | CC | $30 + t_{\rm C}$            | -                          | 2TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                    | ns |

| RdCS, WrCS Low Time<br>(no RW-delay)                                                   | <i>t</i> <sub>49</sub> | CC | $50 + t_{\rm C}$            | -                          | 3TCL - 10<br>+ <i>t</i> <sub>C</sub> | -                                    | ns |

| Data valid to WrCS                                                                     | t <sub>50</sub>        | CC | $26 + t_{\rm C}$            | -                          | 2TCL - 14<br>+ <i>t</i> <sub>C</sub> | -                                    | ns |

| Data hold after RdCS                                                                   | t <sub>51</sub>        | SR | 0                           | -                          | 0                                    | _                                    | ns |

| Data float after RdCS<br>(with RW-delay) <sup>1)</sup>                                 | t <sub>53</sub>        | SR | -                           | 20 + <i>t</i> <sub>F</sub> | -                                    | 2TCL - 20<br>+ $2t_A + t_F^{(1)}$    | ns |

#### Demultiplexed Bus (cont'd)

(Operating Conditions apply)

ALE cycle time = 4 TCL +  $2t_A$  +  $t_C$  +  $t_F$  (80 ns at 25 MHz CPU clock without waitstates)

| Parameter                                            | Symbol                    | Max. CPU Clock<br>= 25 MHz |                           | Variable CPU Clock<br>1 / 2TCL = 1 to 25 MHz |                                  | Unit |

|------------------------------------------------------|---------------------------|----------------------------|---------------------------|----------------------------------------------|----------------------------------|------|

|                                                      |                           | min.                       | max.                      | min.                                         | max.                             |      |

| Data float after RdCS<br>(no RW-delay) <sup>1)</sup> | <i>t</i> <sub>68</sub> SR | _                          | 0 + <i>t</i> <sub>F</sub> | -                                            | TCL - 20<br>+ $2t_A + t_F^{(1)}$ | ns   |

| Address hold after<br>RdCS, WrCS                     | <i>t</i> <sub>55</sub> CC | -6 + <i>t</i> <sub>F</sub> | _                         | -6 + <i>t</i> <sub>F</sub>                   | -                                | ns   |

| Data hold after WrCS                                 | <i>t</i> <sub>57</sub> CC | $6 + t_{F}$                | _                         | TCL - 14 +<br><i>t</i> <sub>F</sub>          | _                                | ns   |

<sup>1)</sup> RW-delay and  $t_A$  refer to the next following bus cycle (including an access to an on-chip X-Peripheral).

<sup>2)</sup> Read data are latched with the same clock edge that triggers the address change and the rising RD edge. Therefore address changes before the end of RD have no impact on read cycles.

<sup>3)</sup> These parameters refer to the latched chip select signals (CSxL). The early chip select signals (CSxE) are specified together with the address and signal BHE (see figures below).

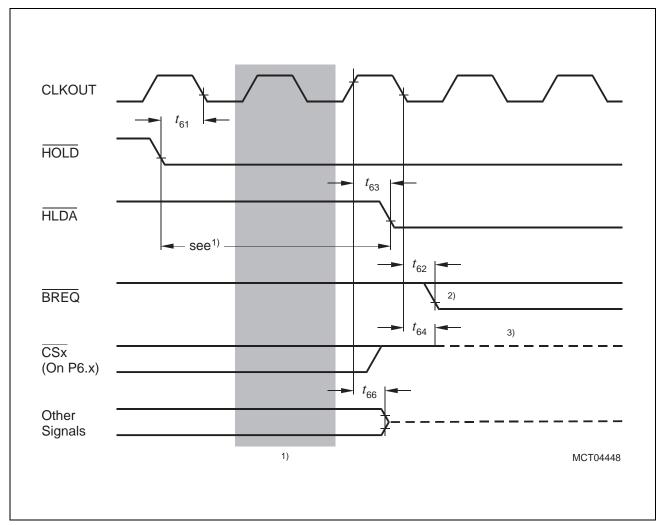

Figure 25 External Bus Arbitration, Releasing the Bus

- **Notes** <sup>1)</sup> The C161CS/JC/JI will complete the currently running bus cycle before granting bus access.

- <sup>2)</sup> This is the first possibility for BREQ to get active.

- <sup>3)</sup> The  $\overline{CS}$  outputs will be resistive high (pullup) after  $t_{64}$ .

### Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com