Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 75                                                                               |

| Program Memory Size        | 576KB (576K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xc2364a-72f80l-aa |

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                                    | Summary of Features         7           Basic Device Types         9           Special Device Types         10           Definition of Feature Variants         11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                                           | General Device Information13Pin Configuration and Definition15Identification Registers39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19 | Functional Description         40           Memory Subsystem and Organization         41           External Bus Controller         44           Central Processing Unit (CPU)         45           Memory Protection Unit (MPU)         47           Memory Checker Module (MCHK)         47           Interrupt System         48           On-Chip Debug Support (OCDS)         49           Capture/Compare Unit (CAPCOM2)         50           Capture/Compare Units CCU6x         53           General Purpose Timer (GPT12E) Unit         55           Real Time Clock         59           A/D Converters         61           Universal Serial Interface Channel Modules (USIC)         62           MultiCAN Module         64           System Timer         65           Watchdog Timer         66           Clock Generation         66           Parallel Ports         67           Instruction Set Summary         68 |

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3                                                                 | Electrical Parameters         71           General Parameters         71           Absolut Maximum Rating Conditions         71           Operating Conditions         72           Pad Timing Definition         74           Parameter Interpretation         74           DC Parameters         75           DC Parameters         77           DC Parameters for Lower Voltage Area         79           Power Consumption         81           Analog/Digital Converter Parameters         86                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.4                                                                                                                                              | System Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### **Summary of Features**

- Two Synchronizable A/D Converters with a total of up to 16 channels, 10-bit resolution, conversion time below 1  $\mu$ s, optional data preprocessing (data reduction, range check), broken wire detection

- Up to 6 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 64 message objects (Full CAN/Basic CAN) on up to 3 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Four programmable chip-select signals

- Single power supply from 3.0 V to 5.5 V

- Programmable watchdog timer and oscillator watchdog

- Up to 76 general purpose I/O lines

- · On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via Device Access Port (DAP) or JTAG interface

- 100-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

### **Summary of Features**

#### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- · the function set of the corresponding product type

- the temperature range:

- SAF-...: -40°C to 85°C

- SAH-...: -40°C to 110°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XC236xA please contact your sales representative or local distributor.

This document describes several derivatives of the XC236xA group:

Basic Device Types are readily available and

Special Device Types are only available on request.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term XC236xA is used for all derivatives throughout this document.

### 1.1 Basic Device Types

Basic device types are available and can be ordered through Infineon's direct and/or distribution channels.

Table 1 Synopsis of XC236xA Basic Device Types

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>       |

|--------------------------|-------------------------------|------------------------------|------------------------|----------------------------|--------------------------------|

| XC2365A-<br>104FxxL      | 832 Kbytes                    | 32 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1         | 11 + 5                     | 3 CAN Nodes,<br>6 Serial Chan. |

| XC2364A-<br>104FxxL      | 832 Kbytes                    | 32 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1         | 11 + 5                     | 2 CAN Nodes,<br>4 Serial Chan. |

| XC2364A-<br>72FxxL       | 576 Kbytes                    | 32/16<br>Kbytes<br>16 Kbytes | CC2<br>CCU60/1         | 11 + 5                     | 2 CAN Nodes,<br>4 Serial Chan. |

<sup>1)</sup> xx is a placeholder for the available speed grade (in MHz).

<sup>2)</sup> Specific information about the on-chip Flash memory in Table 3.

<sup>3)</sup> All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

Specific information about the available channels in Table 5.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

### **Summary of Features**

# 1.2 Special Device Types

Special device types are only available for high-volume applications on request.

Table 2 Synopsis of XC236xA Special Device Types

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.    | ADC <sup>4)</sup> Chan. | Interfaces <sup>4)</sup>       |

|--------------------------|-------------------------------|------------------------------|----------------|-------------------------|--------------------------------|

| XC2365A-<br>72FxxL       | 576 Kbytes                    | 32/16<br>Kbytes<br>16 Kbytes | CC2<br>CCU60/1 | 11 + 5                  | 3 CAN Nodes,<br>6 Serial Chan. |

| XC2365A-<br>56FxxL       | 448 Kbytes                    | 32/16<br>Kbytes<br>16 Kbytes | CC2<br>CCU60/1 | 11 + 5                  | 3 CAN Nodes,<br>6 Serial Chan. |

| XC2364A-<br>56FxxL       | 448 Kbytes                    | 32/16<br>Kbytes<br>16 Kbytes | CC2<br>CCU60/1 | 11 + 5                  | 2 CAN Nodes,<br>4 Serial Chan. |

| XC2363A-<br>72FxxL       | 576 Kbytes                    | 32/16<br>Kbytes<br>16 Kbytes | CC2<br>CCU60/1 | 4 + 4                   | 2 CAN Nodes,<br>2 Serial Chan. |

| XC2363A-<br>56FxxL       | 448 Kbytes                    | 32/16<br>Kbytes<br>16 Kbytes | CC2<br>CCU60/1 | 4 + 4                   | 2 CAN Nodes,<br>2 Serial Chan. |

| XC2361A-<br>72FxxL       | 576 Kbytes                    | 32 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1 | 11 + 5                  | 2 CAN Nodes,<br>6 Serial Chan. |

| XC2361A-<br>56FxxL       | 448 Kbytes                    | 16 Kbytes<br>16 Kbytes       | CC2<br>CCU60/1 | 11 + 5                  | 2 CAN Nodes,<br>6 Serial Chan. |

<sup>1)</sup> xx is a placeholder for the available speed grade (in MHz).

<sup>2)</sup> Specific information about the on-chip Flash memory in Table 3.

<sup>3)</sup> All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

Specific information about the available channels in Table 5.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

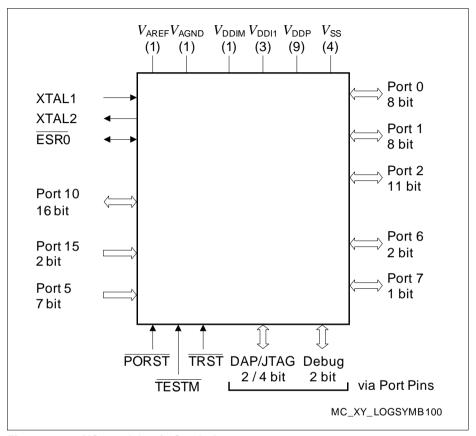

Figure 3 XC236xA Logic Symbol

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 46  | P2.5             | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output  |

|     | U0C0_SCLK<br>OUT | O1     | St/B | USIC0 Channel 0 Shift Clock Output             |

|     | TxDC0            | O2     | St/B | CAN Node 0 Transmit Data Output                |

|     | CC2_CC18         | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.      |

|     | A18              | ОН     | St/B | External Bus Interface Address Line 18         |

|     | U0C0_DX1D        | I      | St/B | USIC0 Channel 0 Shift Clock Input              |

|     | ESR1_10          | I      | St/B | ESR1 Trigger Input 10                          |

| 47  | P4.2             | O0 / I | St/B | Bit 2 of Port 4, General Purpose Input/Output  |

|     | TxDC2            | O2     | St/B | CAN Node 2 Transmit Data Output                |

|     | CC2_CC26         | O3 / I | St/B | CAPCOM2 CC26IO Capture Inp./ Compare Out.      |

|     | CS2              | ОН     | St/B | External Bus Interface Chip Select 2 Output    |

|     | T2INA            | I      | St/B | GPT12E Timer T2 Count/Gate Input               |

| 48  | P2.6             | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output  |

|     | U0C0_SELO<br>0   | O1     | St/B | USIC0 Channel 0 Select/Control 0 Output        |

|     | U0C1_SELO<br>1   | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output        |

|     | CC2_CC19         | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.      |

|     | A19              | ОН     | St/B | External Bus Interface Address Line 19         |

|     | U0C0_DX2D        | I      | St/B | USIC0 Channel 0 Shift Control Input            |

|     | RxDC0D           | I      | St/B | CAN Node 0 Receive Data Input                  |

|     | ESR2_6           | I      | St/B | ESR2 Trigger Input 6                           |

| 49  | P4.3             | O0 / I | St/B | Bit 3 of Port 4, General Purpose Input/Output  |

|     | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

|     | CC2_CC27         | O3 / I | St/B | CAPCOM2 CC27IO Capture Inp./ Compare Out.      |

|     | CS3              | ОН     | St/B | External Bus Interface Chip Select 3 Output    |

|     | RxDC2A           | I      | St/B | CAN Node 2 Receive Data Input                  |

|     | T2EUDA           | I      | St/B | GPT12E Timer T2 External Up/Down Control Input |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.      | Туре | Function                                       |

|-----|-------------------|------------|------|------------------------------------------------|

| 62  | P10.2             | O0 / I     | St/B | Bit 2 of Port 10, General Purpose Input/Output |

|     | U0C0_SCLK<br>OUT  | O1         | St/B | USIC0 Channel 0 Shift Clock Output             |

|     | CCU60_CC6         | O2         | St/B | CCU60 Channel 2 Output                         |

|     | AD2               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 2     |

|     | CCU60_CC6<br>2INA | I          | St/B | CCU60 Channel 2 Input                          |

|     | U0C0_DX1B         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |

| 63  | P0.4              | O0 / I     | St/B | Bit 4 of Port 0, General Purpose Input/Output  |

|     | U1C1_SELO<br>0    | O1         | St/B | USIC1 Channel 1 Select/Control 0 Output        |

|     | U1C0_SELO<br>1    | O2         | St/B | USIC1 Channel 0 Select/Control 1 Output        |

|     | CCU61_COU<br>T61  | О3         | St/B | CCU61 Channel 1 Output                         |

|     | A4                | ОН         | St/B | External Bus Interface Address Line 4          |

|     | U1C1_DX2A         | I          | St/B | USIC1 Channel 1 Shift Control Input            |

|     | RxDC1B            | I          | St/B | CAN Node 1 Receive Data Input                  |

|     | ESR2_8            | I          | St/B | ESR2 Trigger Input 8                           |

| 65  | P2.13             | O0 / I     | St/B | Bit 13 of Port 2, General Purpose Input/Output |

|     | U2C1_SELO<br>2    | O1         | St/B | USIC2 Channel 1 Select/Control 2 Output        |

|     | RxDC2D            | I          | St/B | CAN Node 2 Receive Data Input                  |

| 66  | P2.10             | O0 / I     | St/B | Bit 10 of Port 2, General Purpose Input/Output |

|     | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |

|     | U0C0_SELO<br>3    | O2         | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CC2_CC23          | O3 / I     | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |

|     | A23               | ОН         | St/B | External Bus Interface Address Line 23         |

|     | U0C1_DX0E         | I          | St/B | USIC0 Channel 1 Shift Data Input               |

|     | CAPINA            | I          | St/B | GPT12E Register CAPREL Capture Input           |

Table 6 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.      | Туре | Function                                       |

|-----|------------------|------------|------|------------------------------------------------|

|     | ,                |            |      |                                                |

| 67  | P10.3            | O0 / I     |      | Bit 3 of Port 10, General Purpose Input/Output |

|     | CCU60_COU<br>T60 | O2         | St/B | CCU60 Channel 0 Output                         |

|     | AD3              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 3     |

|     | U0C0_DX2A        | I          | St/B | USIC0 Channel 0 Shift Control Input            |

|     | U0C1_DX2A        | I          | St/B | USIC0 Channel 1 Shift Control Input            |

| 68  | P0.5             | O0 / I     | St/B | Bit 5 of Port 0, General Purpose Input/Output  |

|     | U1C1_SCLK<br>OUT | O1         | St/B | USIC1 Channel 1 Shift Clock Output             |

|     | U1C0_SELO<br>2   | O2         | St/B | USIC1 Channel 0 Select/Control 2 Output        |

|     | CCU61_COU<br>T62 | О3         | St/B | CCU61 Channel 2 Output                         |

|     | A5               | ОН         | St/B | External Bus Interface Address Line 5          |

|     | U1C1_DX1A        | I          | St/B | USIC1 Channel 1 Shift Clock Input              |

|     | U1C0_DX1C        | I          | St/B | USIC1 Channel 0 Shift Clock Input              |

| 69  | P10.4            | O0 / I     | St/B | Bit 4 of Port 10, General Purpose Input/Output |

|     | U0C0_SELO<br>3   | O1         | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CCU60_COU<br>T61 | O2         | St/B | CCU60 Channel 1 Output                         |

|     | AD4              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 4     |

|     | U0C0_DX2B        | I          | St/B | USIC0 Channel 0 Shift Control Input            |

|     | U0C1_DX2B        | I          | St/B | USIC0 Channel 1 Shift Control Input            |

|     | ESR1_9           | I          | St/B | ESR1 Trigger Input 9                           |

Table 6 Pin Definitions and Functions (cont'd)

| Pin              | Symbol     | Ctrl.  | Туре | Function                                                                                                                                                                                                                                              |

|------------------|------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 98               | ESR1       | O0 / I | St/B | External Service Request 1 After power-up, an internal weak pull-up device holds this pin high when nothing is driving it.                                                                                                                            |

|                  | RxDC0E     | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                                                                                         |

|                  | U1C0_DX0F  | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                      |

|                  | U1C0_DX2C  | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                   |

|                  | U1C1_DX0C  | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                      |

|                  | U1C1_DX2B  | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                   |

|                  | U2C1_DX2C  | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                   |

| 99               | ESR0       | O0 / I | St/B | External Service Request 0 After power-up, ESR0 operates as open-drain bidirectional reset with a weak pull-up.                                                                                                                                       |

|                  | U1C0_DX0E  | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                      |

|                  | U1C0_DX2B  | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                   |

| 10               | $V_{DDIM}$ | -      | PS/M | Digital Core Supply Voltage for Domain M Decouple with a ceramic capacitor, see Data Sheet for details.                                                                                                                                               |

| 38,<br>64,<br>88 | $V_{DDI1}$ | -      | PS/1 | Digital Core Supply Voltage for Domain 1 Decouple with a ceramic capacitor, see Data Sheet for details. All V <sub>DDI1</sub> pins must be connected to each other.                                                                                   |

| 14               | $V_{DDPA}$ | -      | PS/A | Digital Pad Supply Voltage for Domain A Connect decoupling capacitors to adjacent $V_{\rm DDP}/V_{\rm SS}$ pin pairs as close as possible to the pins. Note: The A/D_Converters and ports P5, P6 and P15 are fed from supply voltage $V_{\rm DDPA}$ . |

#### **Functional Description**

# 3 Functional Description

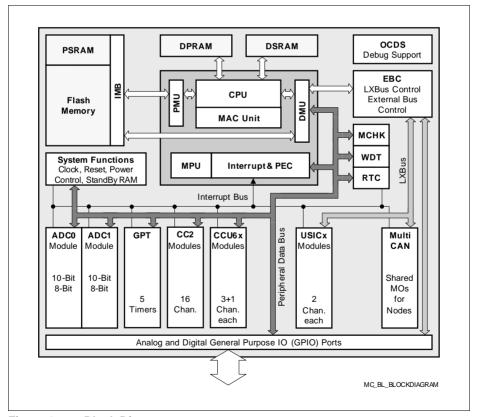

The architecture of the XC236xA combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources (see **Figure 6**). This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC236xA.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC236xA.

Figure 6 Block Diagram

### **Functional Description**

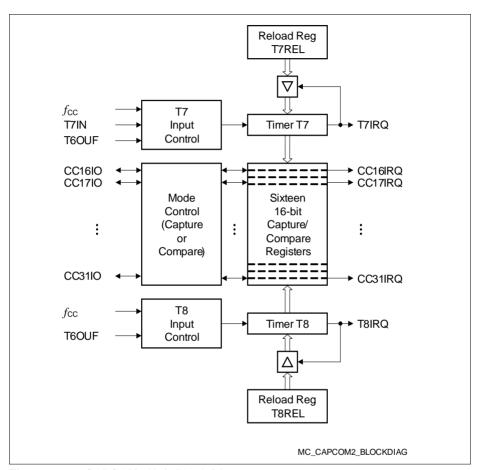

### 3.8 Capture/Compare Unit (CAPCOM2)

The CAPCOM2 unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM2 unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range or variation for the timer period and resolution and allows precise adjustments to the application-specific requirements. In addition, an external count input allows event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

Table 9 Compare Modes

| Compare Modes | Function                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

#### **Functional Description**

Figure 8 CAPCOM2 Unit Block Diagram

**Functional Description**

#### 3.12 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 11 + 5 multiplexed input channels and a sample and hold circuit have been integrated on-chip. 4 inputs can be converted by both A/D converters. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XC236xA support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

### **Functional Description**

Table 11 Instruction Set Summary (cont'd)

| Mnemonic     | Description                         | Bytes |

|--------------|-------------------------------------|-------|

| NOP          | Null operation                      | 2     |

| CoMUL/CoMAC  | Multiply (and accumulate)           | 4     |

| CoADD/CoSUB  | Add/Subtract                        | 4     |

| Co(A)SHR     | (Arithmetic) Shift right            | 4     |

| CoSHL        | Shift left                          | 4     |

| CoLOAD/STORE | Load accumulator/Store MAC register | 4     |

| CoCMP        | Compare                             | 4     |

| CoMAX/MIN    | Maximum/Minimum                     | 4     |

| CoABS/CoRND  | Absolute value/Round accumulator    | 4     |

| CoMOV        | Data move                           | 4     |

| CoNEG/NOP    | Negate accumulator/Null operation   | 4     |

The Enter Power Down Mode instruction is not used in the XC236xA, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

**Electrical Parameters**

### 4 Electrical Parameters

The operating range for the XC236xA is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

#### 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

### 4.1.1 Absolut Maximum Rating Conditions

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability.

During absolute maximum rating overload conditions  $(V_{\rm IN} > V_{\rm DDP} \text{ or } V_{\rm IN} < V_{\rm SS})$  the voltage on  $V_{\rm DDP}$  pins with respect to ground  $(V_{\rm SS})$  must not exceed the values defined by the absolute maximum ratings.

Table 12 Absolute Maximum Rating Parameters

| Parameter                                                 | Symbol                                      |      | Values |                        |    | Note /                     |

|-----------------------------------------------------------|---------------------------------------------|------|--------|------------------------|----|----------------------------|

|                                                           |                                             | Min. | Тур.   | Max.                   |    | Test Condition             |

| Output current on a pin when high value is driven         | $I_{OH}SR$                                  | -30  | _      | _                      | mA |                            |

| Output current on a pin when low value is driven          | $I_{\rm OL}{\rm SR}$                        | -    | _      | 30                     | mA |                            |

| Overload current                                          | $I_{OV}SR$                                  | -10  | _      | 10                     | mA | 1)                         |

| Absolute sum of overload currents                         | $\Sigma  I_{ m OV} $ SR                     | -    | -      | 100                    | mA | 1)                         |

| Junction Temperature                                      | $T_{J}SR$                                   | -40  | _      | 150                    | °C |                            |

| Storage Temperature                                       | $T_{\rm ST}{ m SR}$                         | -65  | _      | 150                    | °C |                            |

| Digital supply voltage for IO pads and voltage regulators | $V_{\rm DDPA}, \\ V_{\rm DDPB} \\ {\rm SR}$ | -0.5 | -      | 6.0                    | V  |                            |

| Voltage on any pin with respect to ground (Vss)           | $V_{IN}SR$                                  | -0.5 | _      | V <sub>DDP</sub> + 0.5 | V  | $V_{IN} \leq V_{DDP(max)}$ |

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

#### **Electrical Parameters**

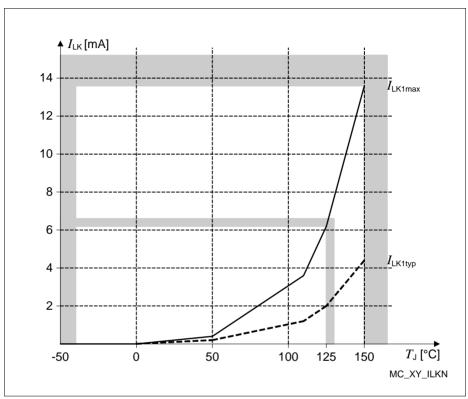

Figure 17 Leakage Supply Current as a Function of Temperature

#### **Electrical Parameters**

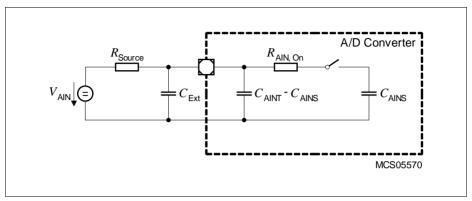

Figure 18 Equivalent Circuitry for Analog Inputs

#### **Electrical Parameters**

Sample time and conversion time of the XC236xA's A/D converters are programmable. The timing above can be calculated using **Table 19**.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

Table 19 A/D Converter Computation Table

| GLOBCTR.5-0<br>(DIVA) | A/D Converter Analog Clock $f_{\mathrm{ADCI}}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup> |

|-----------------------|------------------------------------------------|---------------------|---------------------------|

| 000000 <sub>B</sub>   | $f_{	extsf{SYS}}$                              | 00 <sub>H</sub>     | $t_{ADCI} \times 2$       |

| 000001 <sub>B</sub>   | $f_{\rm SYS}$ / 2                              | 01 <sub>H</sub>     | $t_{ADCI} \times 3$       |

| 000010 <sub>B</sub>   | $f_{\rm SYS}$ / 3                              | 02 <sub>H</sub>     | $t_{ADCI} \times 4$       |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                       | :                   | $t_{ADCI} \times (STC+2)$ |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                          | FE <sub>H</sub>     | $t_{ADCI} \times 256$     |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                          | FF <sub>H</sub>     | $t_{ADCI} \times 257$     |

<sup>1)</sup> The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

### **Converter Timing Example A:**

Assumptions:  $f_{SYS} = 80 \text{ MHz}$  (i.e.  $t_{SYS} = 12.5 \text{ ns}$ ), DIVA =  $03_H$ , STC =  $00_H$

Analog clock  $f_{ADCI} = f_{SYS} / 4 = 20 \text{ MHz}$ , i.e.  $t_{ADCI} = 50 \text{ ns}$

Sample time  $t_S = t_{ADCI} \times 2 = 100 \text{ ns}$

Conversion 10-bit:

$t_{\text{C10}} = 13 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 13 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.675 \text{ }\mu\text{s}$

Conversion 8-bit:

$t_{C8} = 11 \times t_{ADCI} + 2 \times t_{SYS} = 11 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.575 \text{ }\mu\text{s}$

## Converter Timing Example B:

Assumptions:  $f_{SYS} = 40 \text{ MHz}$  (i.e.  $t_{SYS} = 25 \text{ ns}$ ), DIVA =  $02_H$ , STC =  $03_H$

Analog clock  $f_{ADCI} = f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e.  $t_{ADCI} = 75 \text{ ns}$

Sample time  $t_S = t_{ADCI} \times 5 = 375 \text{ ns}$

Conversion 10-bit:

$t_{\text{C10}} = 16 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 16 \times 75 \text{ ns} + 2 \times 25 \text{ ns} = 1.25 \text{ }\mu\text{s}$

Conversion 8-bit:

$t_{\text{C8}} = 14 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 14 \times 75 \text{ ns} + 2 \times 25 \text{ ns} = 1.10 \text{ }\mu\text{s}$

Data Sheet 89 V2.1, 2011-07

#### **Electrical Parameters**

## 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XC236xA into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

Table 20 Various System Parameters

| Parameter                                                             | Symbol                 | Values                               |          |                                             | Unit | Note /                            |

|-----------------------------------------------------------------------|------------------------|--------------------------------------|----------|---------------------------------------------|------|-----------------------------------|

|                                                                       |                        | Min.                                 | Тур.     | Max.                                        |      | Test Condition                    |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC   | -1                                   | -        | 1                                           | %    | <i>∆T</i> <sub>J</sub> ≤ 10 °C    |

| Internal clock source frequency                                       | $f_{INT}CC$            | 4.8                                  | 5.0      | 5.2                                         | MHz  |                                   |

| Wakeup clock source frequency <sup>2)</sup>                           | $f_{WU}$ CC            | 400                                  | _        | 700                                         | kHz  | FREQSEL= 00                       |

|                                                                       |                        | 210                                  | _        | 390                                         | kHz  | FREQSEL= 01                       |

|                                                                       |                        | 140                                  | _        | 260                                         | kHz  | FREQSEL= 10                       |

|                                                                       |                        | 110                                  | _        | 200                                         | kHz  | FREQSEL= 11                       |

| Startup time from power-<br>on with code execution<br>from Flash      | $t_{SPO}$ CC           | 1.8                                  | 2.2      | 2.7                                         | ms   | $f_{\rm WU}$ = 500 kHz            |

| Startup time from stopover mode with code execution from PSRAM        | $t_{\rm SSO}$ CC       | 11 / $f_{\rm WU}^{3)}$               | -        | 12 /<br>$f_{\rm WU}^{3)}$                   | μS   |                                   |

| Core voltage (PVC) supervision level                                  | $V_{PVC}CC$            | V <sub>LV</sub><br>- 0.03            | $V_{LV}$ | <i>V</i> <sub>LV</sub> + 0.07 <sub>4)</sub> | V    | 5)                                |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC | V <sub>LV</sub> - 0.10 <sup>6)</sup> | $V_{LV}$ | <i>V</i> <sub>LV</sub> + 0.15               | V    | Lower voltage range <sup>5)</sup> |

|                                                                       |                        | V <sub>LV</sub> - 0.15               | $V_{LV}$ | V <sub>LV</sub><br>+ 0.15                   | V    | Upper voltage range <sup>5)</sup> |

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

<sup>2)</sup> This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

#### **Electrical Parameters**

Table 30 EBC External Bus Timing for Upper Voltage Range

| Parameter                                                                                     | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                               |                           | Min.   | Тур. | Max. |      | Test Condition |

| Output valid delay for $\overline{\text{RD}}$ , $\overline{\text{WR}}(\overline{\text{L/H}})$ | t <sub>10</sub> CC        | _      | 7    | 13   | ns   |                |

| Output valid delay for BHE, ALE                                                               | <i>t</i> <sub>11</sub> CC | _      | 7    | 14   | ns   |                |

| Address output valid delay for A23 A0                                                         | <i>t</i> <sub>12</sub> CC | _      | 8    | 14   | ns   |                |

| Address output valid delay for AD15 AD0 (MUX mode)                                            | t <sub>13</sub> CC        | -      | 8    | 15   | ns   |                |

| Output valid delay for CS                                                                     | t <sub>14</sub> CC        | -      | 7    | 13   | ns   |                |

| Data output valid delay for AD15 AD0 (write data, MUX mode)                                   | t <sub>15</sub> CC        | _      | 8    | 15   | ns   |                |

| Data output valid delay for D15 D0 (write data, DEMUX mode)                                   | t <sub>16</sub> CC        | _      | 8    | 15   | ns   |                |

| Output hold time for $\overline{\text{RD}}$ , $\overline{\text{WR}}(\overline{\text{L/H}})$   | t <sub>20</sub> CC        | -2     | 6    | 8    | ns   |                |

| Output hold time for BHE, ALE                                                                 | t <sub>21</sub> CC        | -2     | 6    | 10   | ns   |                |

| Address output hold time for AD15 AD0                                                         | t <sub>23</sub> CC        | -3     | 6    | 8    | ns   |                |

| Output hold time for CS                                                                       | t <sub>24</sub> CC        | -3     | 6    | 11   | ns   |                |

| Data output hold time for D15 D0 and AD15 AD0                                                 | t <sub>25</sub> CC        | -3     | 6    | 8    | ns   |                |

| Input setup time for<br>READY, D15 D0, AD15<br>AD0                                            | t <sub>30</sub> SR        | 25     | 15   | _    | ns   |                |

| Input hold time READY,<br>D15 D0, AD15 AD0 <sup>1)</sup>                                      | <i>t</i> <sub>31</sub> SR | 0      | -7   | _    | ns   |                |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge

of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can

change after the rising edge of RD.