Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Betuils                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | C166SV2                                                                           |

| Core Size                  | 16/32-Bit                                                                         |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI              |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                   |

| Number of I/O              | 75                                                                                |

| Program Memory Size        | 832KB (832K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 50K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                         |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-100-8                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2365a104f80laakxuma1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Summary of Features

- Two Synchronizable A/D Converters with a total of up to 16 channels, 10-bit resolution, conversion time below  $1 \,\mu$ s, optional data preprocessing (data reduction, range check), broken wire detection

- Up to 6 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 64 message objects (Full CAN/Basic CAN) on up to 3 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

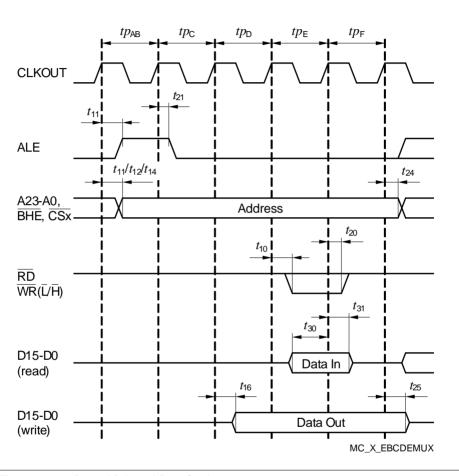

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Four programmable chip-select signals

- Single power supply from 3.0 V to 5.5 V

- Programmable watchdog timer and oscillator watchdog

- Up to 76 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via Device Access Port (DAP) or JTAG interface

- 100-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

| Tabl | Table 6         Pin Definitions and Functions (cont'd) |       |      |                                               |  |  |  |  |

|------|--------------------------------------------------------|-------|------|-----------------------------------------------|--|--|--|--|

| Pin  | Symbol                                                 | Ctrl. | Туре | Function                                      |  |  |  |  |

| 30   | P5.8                                                   | 1     | In/A | Bit 8 of Port 5, General Purpose Input        |  |  |  |  |

|      | ADC0_CH8                                               | I     | In/A | Analog Input Channel 8 for ADC0               |  |  |  |  |

|      | ADC1_CH8                                               | I     | In/A | Analog Input Channel 8 for ADC1               |  |  |  |  |

|      | CCU6x_T12H<br>RC                                       | I     | In/A | External Run Control Input for T12 of CCU60/1 |  |  |  |  |

|      | CCU6x_T13H<br>RC                                       | I     | In/A | External Run Control Input for T13 of CCU60/1 |  |  |  |  |

|      | U2C0_DX0F                                              | 1     | In/A | USIC2 Channel 0 Shift Data Input              |  |  |  |  |

| 31   | P5.9                                                   | 1     | In/A | Bit 9 of Port 5, General Purpose Input        |  |  |  |  |

|      | ADC0_CH9                                               | 1     | In/A | Analog Input Channel 9 for ADC0               |  |  |  |  |

|      | ADC1_CH9                                               | I     | In/A | Analog Input Channel 9 for ADC1               |  |  |  |  |

|      | CC2_T7IN                                               | 1     | In/A | CAPCOM2 Timer T7 Count Input                  |  |  |  |  |

| 32   | P5.10                                                  | 1     | In/A | Bit 10 of Port 5, General Purpose Input       |  |  |  |  |

|      | ADC0_CH10                                              | 1     | In/A | Analog Input Channel 10 for ADC0              |  |  |  |  |

|      | ADC1_CH10                                              | I     | In/A | Analog Input Channel 10 for ADC1              |  |  |  |  |

|      | BRKIN_A                                                | I     | In/A | OCDS Break Signal Input                       |  |  |  |  |

|      | U2C1_DX0F                                              | I     | In/A | USIC2 Channel 1 Shift Data Input              |  |  |  |  |

|      | CCU61_T13<br>HRA                                       | I     | In/A | External Run Control Input for T13 of CCU61   |  |  |  |  |

| 33   | P5.11                                                  | 1     | In/A | Bit 11 of Port 5, General Purpose Input       |  |  |  |  |

|      | ADC0_CH11                                              | I     | In/A | Analog Input Channel 11 for ADC0              |  |  |  |  |

|      | ADC1_CH11                                              | I     | In/A | Analog Input Channel 11 for ADC1              |  |  |  |  |

| 34   | P5.13                                                  | I     | In/A | Bit 13 of Port 5, General Purpose Input       |  |  |  |  |

|      | ADC0_CH13                                              | I     | In/A | Analog Input Channel 13 for ADC0              |  |  |  |  |

| 35   | P5.15                                                  | I     | In/A | Bit 15 of Port 5, General Purpose Input       |  |  |  |  |

|      | ADC0_CH15                                              | I     | In/A | Analog Input Channel 15 for ADC0              |  |  |  |  |

|      | RxDC2F                                                 | 1     | In/A | CAN Node 2 Receive Data Input                 |  |  |  |  |

|      |                                                        | -     |      |                                               |  |  |  |  |

| Pin | Symbol         | Ctrl.      | Туре | Function                                                                                                                                        |

|-----|----------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 36  | P2.12          | O0 / I     | St/B | Bit 12 of Port 2, General Purpose Input/Output                                                                                                  |

|     | U0C0_SELO<br>4 | O1         | St/B | USIC0 Channel 0 Select/Control 4 Output                                                                                                         |

|     | U0C1_SELO<br>3 | O2         | St/B | USIC0 Channel 1 Select/Control 3 Output                                                                                                         |

|     | TXDC2          | O3         | St/B | CAN Node 2 Transmit Data Output                                                                                                                 |

|     | READY          | IH         | St/B | External Bus Interface READY Input                                                                                                              |

| 37  | P2.11          | O0 / I     | St/B | Bit 11 of Port 2, General Purpose Input/Output                                                                                                  |

|     | U0C0_SELO<br>2 | 01         | St/B | USIC0 Channel 0 Select/Control 2 Output                                                                                                         |

|     | U0C1_SELO<br>2 | 02         | St/B | USIC0 Channel 1 Select/Control 2 Output                                                                                                         |

|     | BHE/WRH        | ОН         | St/B | <b>External Bus Interf. High-Byte Control Output</b><br>Can operate either as Byte High Enable (BHE) or<br>as Write strobe for High Byte (WRH). |

| 39  | P2.0           | O0 / I     | St/B | Bit 0 of Port 2, General Purpose Input/Output                                                                                                   |

|     | AD13           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 13                                                                                                     |

|     | RxDC0C         | I          | St/B | CAN Node 0 Receive Data Input                                                                                                                   |

|     | T5INB          | I          | St/B | GPT12E Timer T5 Count/Gate Input                                                                                                                |

| 40  | P2.1           | O0 / I     | St/B | Bit 1 of Port 2, General Purpose Input/Output                                                                                                   |

|     | TxDC0          | 01         | St/B | CAN Node 0 Transmit Data Output                                                                                                                 |

|     | AD14           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 14                                                                                                     |

|     | T5EUDB         | I          | St/B | GPT12E Timer T5 External Up/Down Control<br>Input                                                                                               |

|     | ESR1_5         | I          | St/B | ESR1 Trigger Input 5                                                                                                                            |

| 41  | P2.2           | O0 / I     | St/B | Bit 2 of Port 2, General Purpose Input/Output                                                                                                   |

|     | TxDC1          | 01         | St/B | CAN Node 1 Transmit Data Output                                                                                                                 |

|     | AD15           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15                                                                                                     |

|     | ESR2_5         | I          | St/B | ESR2 Trigger Input 5                                                                                                                            |

| Table | e 6 Pin De        | 1          |      | Functions (cont'd)                             |

|-------|-------------------|------------|------|------------------------------------------------|

| Pin   | Symbol            | Ctrl.      | Туре | Function                                       |

| 62    | P10.2             | O0 / I     | St/B | Bit 2 of Port 10, General Purpose Input/Output |

|       | U0C0_SCLK<br>OUT  | O1         | St/B | USIC0 Channel 0 Shift Clock Output             |

|       | CCU60_CC6<br>2    | O2         | St/B | CCU60 Channel 2 Output                         |

|       | AD2               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 2     |

|       | CCU60_CC6<br>2INA | I          | St/B | CCU60 Channel 2 Input                          |

|       | U0C0_DX1B         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |

| 63    | P0.4              | O0 / I     | St/B | Bit 4 of Port 0, General Purpose Input/Output  |

|       | U1C1_SELO<br>0    | O1         | St/B | USIC1 Channel 1 Select/Control 0 Output        |

|       | U1C0_SELO<br>1    | O2         | St/B | USIC1 Channel 0 Select/Control 1 Output        |

|       | CCU61_COU<br>T61  | O3         | St/B | CCU61 Channel 1 Output                         |

|       | A4                | ОН         | St/B | External Bus Interface Address Line 4          |

|       | U1C1_DX2A         | I          | St/B | USIC1 Channel 1 Shift Control Input            |

|       | RxDC1B            | I          | St/B | CAN Node 1 Receive Data Input                  |

|       | ESR2_8            | I          | St/B | ESR2 Trigger Input 8                           |

| 65    | P2.13             | O0 / I     | St/B | Bit 13 of Port 2, General Purpose Input/Output |

|       | U2C1_SELO<br>2    | O1         | St/B | USIC2 Channel 1 Select/Control 2 Output        |

|       | RxDC2D            | I          | St/B | CAN Node 2 Receive Data Input                  |

| 66    | P2.10             | O0 / I     | St/B | Bit 10 of Port 2, General Purpose Input/Output |

|       | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |

|       | U0C0_SELO<br>3    | O2         | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|       | CC2_CC23          | O3 / I     | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |

|       | A23               | ОН         | St/B | External Bus Interface Address Line 23         |

|       | U0C1_DX0E         | I          | St/B | USIC0 Channel 1 Shift Data Input               |

|       | CAPINA            | 1          | St/B | GPT12E Register CAPREL Capture Input           |

| Table | e 6 Pin De        | finitior   | ns and | Functions (cont'd)                                                                                                                                                                                                                                                                                   |

|-------|-------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   | Symbol            | Ctrl.      | Туре   | Function                                                                                                                                                                                                                                                                                             |

| 79    | P10.8             | O0 / I     | St/B   | Bit 8 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |

|       | U0C0_MCLK<br>OUT  | O1         | St/B   | USIC0 Channel 0 Master Clock Output                                                                                                                                                                                                                                                                  |

|       | U0C1_SELO<br>0    | O2         | St/B   | USIC0 Channel 1 Select/Control 0 Output                                                                                                                                                                                                                                                              |

|       | U2C1_DOUT         | O3         | St/B   | USIC2 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |

|       | AD8               | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 8                                                                                                                                                                                                                                                           |

|       | CCU60_CCP<br>OS1A | I          | St/B   | CCU60 Position Input 1                                                                                                                                                                                                                                                                               |

|       | U0C0_DX1C         | I          | St/B   | USIC0 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                    |

|       | BRKIN_B           | I          | St/B   | OCDS Break Signal Input                                                                                                                                                                                                                                                                              |

|       | T3EUDB            | I          | St/B   | GPT12E Timer T3 External Up/Down Control<br>Input                                                                                                                                                                                                                                                    |

| 80    | P10.9             | O0 / I     | St/B   | Bit 9 of Port 10, General Purpose Input/Output                                                                                                                                                                                                                                                       |

|       | U0C0_SELO<br>4    | O1         | St/B   | USIC0 Channel 0 Select/Control 4 Output                                                                                                                                                                                                                                                              |

|       | U0C1_MCLK<br>OUT  | O2         | St/B   | USIC0 Channel 1 Master Clock Output                                                                                                                                                                                                                                                                  |

|       | AD9               | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 9                                                                                                                                                                                                                                                           |

|       | CCU60_CCP<br>OS2A | I          | St/B   | CCU60 Position Input 2                                                                                                                                                                                                                                                                               |

|       | ТСК_В             | IH         | St/B   | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |

|       | T3INB             | I          | St/B   | GPT12E Timer T3 Count/Gate Input                                                                                                                                                                                                                                                                     |

| Table | 1                | 1          |      | Functions (cont'd)                                                                                                                                                        |  |  |

|-------|------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol           | Ctrl.      | Туре |                                                                                                                                                                           |  |  |

| 81    | P1.1             | 00 / I     | St/B | Bit 1 of Port 1, General Purpose Input/Output                                                                                                                             |  |  |

|       | U1C0_SELO<br>5   | O2         | St/B | USIC1 Channel 0 Select/Control 5 Output                                                                                                                                   |  |  |

|       | U2C1_DOUT        | O3         | St/B | USIC2 Channel 1 Shift Data Output                                                                                                                                         |  |  |

|       | A9               | ОН         | St/B | External Bus Interface Address Line 9                                                                                                                                     |  |  |

|       | ESR2_3           | I          | St/B | ESR2 Trigger Input 3                                                                                                                                                      |  |  |

|       | U2C1_DX0C        | I          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                          |  |  |

| 82    | P10.10           | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                           |  |  |

|       | U0C0_SELO<br>0   | O1         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                                   |  |  |

|       | CCU60_COU<br>T63 | O2         | St/B | CCU60 Channel 3 Output                                                                                                                                                    |  |  |

|       | AD10             | OH /<br>IH | St/B | External Bus Interface Address/Data Line 10                                                                                                                               |  |  |

|       | U0C0_DX2C        | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                                       |  |  |

|       | U0C1_DX1A        | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                         |  |  |

|       | TDI_B            | IH         | St/B | JTAG Test Data Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.                  |  |  |

| 83    | P10.11           | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                           |  |  |

|       | U1C0_SCLK<br>OUT | O1         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                        |  |  |

|       | BRKOUT           | 02         | St/B | OCDS Break Signal Output                                                                                                                                                  |  |  |

|       | AD11             | OH /<br>IH | St/B | External Bus Interface Address/Data Line 11                                                                                                                               |  |  |

|       | U1C0_DX1D        | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                         |  |  |

|       | RxDC2B           | I          | St/B | CAN Node 2 Receive Data Input                                                                                                                                             |  |  |

|       | TMS_B            | IH         | St/B | <b>JTAG Test Mode Selection Input</b><br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it. |  |  |

| Table | e 6 Pin De       | finitior   | ns and | Functions (cont'd)                                                                                                                                                                 |  |  |

|-------|------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol           | Ctrl.      | Туре   | Function                                                                                                                                                                           |  |  |

| 84    | P1.2             | O0 / I     | St/B   | Bit 2 of Port 1, General Purpose Input/Output                                                                                                                                      |  |  |

|       | U1C0_SELO<br>6   | O2         | St/B   | USIC1 Channel 0 Select/Control 6 Output                                                                                                                                            |  |  |

|       | U2C1_SCLK<br>OUT | O3         | St/B   | USIC2 Channel 1 Shift Clock Output                                                                                                                                                 |  |  |

|       | A10              | ОН         | St/B   | External Bus Interface Address Line 10                                                                                                                                             |  |  |

|       | ESR1_4           | I          | St/B   | ESR1 Trigger Input 4                                                                                                                                                               |  |  |

|       | CCU61_T12<br>HRB | I          | St/B   | External Run Control Input for T12 of CCU61                                                                                                                                        |  |  |

|       | U2C1_DX0D        | I          | St/B   | USIC2 Channel 1 Shift Data Input                                                                                                                                                   |  |  |

|       | U2C1_DX1C        | I          | St/B   | USIC2 Channel 1 Shift Clock Input                                                                                                                                                  |  |  |

| 85    | P10.12           | O0 / I     | St/B   | Bit 12 of Port 10, General Purpose Input/Output                                                                                                                                    |  |  |

|       | U1C0_DOUT        | 01         | St/B   | USIC1 Channel 0 Shift Data Output                                                                                                                                                  |  |  |

|       | TxDC2            | 02         | St/B   | CAN Node 2 Transmit Data Output                                                                                                                                                    |  |  |

|       | TDO_B            | OH /<br>IH | St/B   | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it.      |  |  |

|       | AD12             | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 12                                                                                                                                        |  |  |

|       | U1C0_DX0C        | I          | St/B   | USIC1 Channel 0 Shift Data Input                                                                                                                                                   |  |  |

|       | U1C0_DX1E        | I          | St/B   | USIC1 Channel 0 Shift Clock Input                                                                                                                                                  |  |  |

| 86    | P10.13           | O0 / I     | St/B   | Bit 13 of Port 10, General Purpose Input/Output                                                                                                                                    |  |  |

|       | U1C0_DOUT        | 01         | St/B   | USIC1 Channel 0 Shift Data Output                                                                                                                                                  |  |  |

|       | U1C0_SELO<br>3   | O3         | St/B   | USIC1 Channel 0 Select/Control 3 Output                                                                                                                                            |  |  |

|       | WR/WRL           | ОН         | St/B   | <b>External Bus Interface Write Strobe Output</b><br>Active for each external write access, when $\overline{WR}$ , active for ext. writes to the low byte, when $\overline{WRL}$ . |  |  |

|       | U1C0_DX0D        | I          | St/B   | USIC1 Channel 0 Shift Data Input                                                                                                                                                   |  |  |

| Table            | Table 6Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                              |  |  |  |  |

|------------------|-----------------------------------------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin              | Symbol                                        | Ctrl.  | Туре | Function                                                                                                                                                                                                     |  |  |  |  |

| 98               | ESR1                                          | O0 / I | St/B | <b>External Service Request 1</b><br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                                                      |  |  |  |  |

|                  | RxDC0E                                        | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                                                |  |  |  |  |

|                  | U1C0_DX0F                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                             |  |  |  |  |

|                  | U1C0_DX2C                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                          |  |  |  |  |

|                  | U1C1_DX0C                                     | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                             |  |  |  |  |

|                  | U1C1_DX2B                                     | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                          |  |  |  |  |

|                  | U2C1_DX2C                                     | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                          |  |  |  |  |

| 99               | ESR0                                          | O0 / I | St/B | <b>External Service Request 0</b><br>After power-up, ESR0 operates as open-drain<br>bidirectional reset with a weak pull-up.                                                                                 |  |  |  |  |

|                  | U1C0_DX0E                                     | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                             |  |  |  |  |

|                  | U1C0_DX2B                                     | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                          |  |  |  |  |

| 10               |                                               | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                                         |  |  |  |  |

| 38,<br>64,<br>88 | V <sub>DDI1</sub>                             | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All V <sub>DDI1</sub> pins must be connected to each other.                          |  |  |  |  |

| 14               | V <sub>DDPA</sub>                             | -      | PS/A | <b>Digital Pad Supply Voltage for Domain A</b><br>Connect decoupling capacitors to adjacent<br>$V_{DDP}/V_{SS}$ pin pairs as close as possible to the pins.<br>Note: The A/D_Converters and ports P5, P6 and |  |  |  |  |

|                  |                                               |        |      | P15 are fed from supply voltage $V_{DDPA}$ .                                                                                                                                                                 |  |  |  |  |

### **Functional Description**

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 2                  | Interrupt-only compare mode;<br>Only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>Pin toggles on each compare match;<br>Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>Can be used with any compare mode                                                          |

## Table 9 Compare Modes (cont'd)

### **Functional Description**

## 3.9 Capture/Compare Units CCU6x

The XC236xA types feature the CCU60, CCU61 unit(s).

The CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

### **Timer 12 Features**

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

### **Timer 13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

### **Additional Features**

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC drives

- · Output levels can be selected and adapted to the power stage

# 4 Electrical Parameters

The operating range for the XC236xA is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

## 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

## 4.1.1 Absolut Maximum Rating Conditions

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability.

During absolute maximum rating overload conditions ( $V_{\rm IN} > V_{\rm DDP}$  or  $V_{\rm IN} < V_{\rm SS}$ ) the voltage on  $V_{\rm DDP}$  pins with respect to ground ( $V_{\rm SS}$ ) must not exceed the values defined by the absolute maximum ratings.

| Parameter                                                       | Symbol                        |      | Values | 5                         | Unit | Note /                             |

|-----------------------------------------------------------------|-------------------------------|------|--------|---------------------------|------|------------------------------------|

|                                                                 |                               | Min. | Тур.   | Max.                      |      | Test Condition                     |

| Output current on a pin when high value is driven               | I <sub>OH</sub> SR            | -30  | -      | -                         | mA   |                                    |

| Output current on a pin when low value is driven                | I <sub>OL</sub> SR            | -    | -      | 30                        | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$          | -10  | -      | 10                        | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR       | -    | -      | 100                       | mA   | 1)                                 |

| Junction Temperature                                            | $T_{\rm J}{\rm SR}$           | -40  | -      | 150                       | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$           | -65  | -      | 150                       | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{ m DDPA}, V_{ m DDPB}$ SR | -0.5 | -      | 6.0                       | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}$ SR               | -0.5 | -      | V <sub>DDP</sub><br>+ 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

### Table 12 Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

| Parameter                                                       | Symbol                  |      | Values |      | Unit | Note /                            |

|-----------------------------------------------------------------|-------------------------|------|--------|------|------|-----------------------------------|

|                                                                 |                         | Min. | Тур.   | Max. |      | Test Condition                    |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR | -    | -      | 50   | mA   | not subject to<br>production test |

| Digital core supply voltage for domain M <sup>8)</sup>          | V <sub>DDIM</sub><br>CC | -    | 1.5    | -    |      |                                   |

| Digital core supply voltage for domain 1 <sup>8)</sup>          | V <sub>DDI1</sub><br>CC | -    | 1.5    | -    |      |                                   |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$    | 4.5  | -      | 5.5  | V    |                                   |

| Digital ground voltage                                          | $V_{\rm SS}{\rm SR}$    | -    | 0      | -    | V    |                                   |

### Table 13 Operating Conditions (cont'd)

To ensure the stability of the voltage regulators the EVRs must be buffered with ceramic capacitors. Separate buffer capacitors with the recomended values shall be connected as close as possible to each V<sub>DDIM</sub> and V<sub>DDI1</sub> pin to keep the resistance of the board tracks below 2 Ohm. Connect all V<sub>DDI1</sub> pins together. The minimum capacitance value is required for proper operation under all conditions (e.g. temperature). Higher values slightly increase the startup time.

2) Use one Capacitor for each pin.

- This is the reference load. For bigger capacitive loads, use the derating factors listed in the PAD properties section.

- 4) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability (C<sub>L</sub>).

- 5) The operating frequency range may be reduced for specific device types. This is indicated in the device designation (...FxxL). 80 MHz devices are marked ...F80L.

- 6) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range: V<sub>OV</sub> > V<sub>IHmax</sub> (I<sub>OV</sub> > 0) or V<sub>OV</sub> < V<sub>ILmin</sub> ((I<sub>OV</sub> < 0). The absolute sum of input overload currents on all pins may not exceed 50 mA. The supply voltages must remain within the specified limits. Proper operation under overload conditions depends on the application. Overload conditions must not occur on pin XTAL1 (powered by V<sub>DDIM</sub>).

- 7) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pins leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ}| + (|I_{OV}| K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- 8) Value is controlled by on-chip regulator

## 4.2.2 DC Parameters for Lower Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

Table 15 is valid under the following conditions:

$V_{\text{DDP}} \ge 3.0 \text{ V}; V_{\text{DDPtvp}} = 3.3 \text{ V}; V_{\text{DDP}} \le 4.5 \text{ V}$

| Parameter                                                                                            | Symbol                   |                                   | Values | 5                                 | Unit | Note /                                                                                             |

|------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------|--------|-----------------------------------|------|----------------------------------------------------------------------------------------------------|

|                                                                                                      |                          | Min. Typ.                         |        | Max.                              |      | Test Condition                                                                                     |

| Pin capacitance (digital<br>inputs/outputs). To be<br>doubled for double bond<br>pins. <sup>1)</sup> | C <sub>IO</sub> CC       | -                                 | -      | 10                                | pF   | not subject to production test                                                                     |

| Input Hysteresis <sup>2)</sup>                                                                       | HYS CC                   | 0.07 x<br>V <sub>DDP</sub>        | _      | -                                 | V    | $R_{\rm S} = 0$ Ohm                                                                                |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                                 | I <sub>OZ1</sub>  <br>CC | _                                 | 10     | 200                               | nA   | $V_{\rm IN} > V_{\rm SS}; \\ V_{\rm IN} < V_{\rm DDP}$                                             |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double                    | I <sub>0Z2</sub>  <br>CC | -                                 | 0.2    | 2.5                               | μA   | $T_{\rm J} \leq 110 ~^{\rm o}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| bond pins. <sup>3)1)4)</sup>                                                                         |                          | -                                 | 0.2    | 8                                 | μA   | $T_{\rm J} \leq 150 ~^{\circ}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| Pull Level Force Current <sup>5)</sup>                                                               | $ I_{PLF} $ SR           | 150                               | -      | -                                 |      | 6)                                                                                                 |

| Pull Level Keep Current <sup>7)</sup>                                                                | I <sub>PLK</sub>  <br>SR | -                                 | -      | 10                                | μA   | 6)                                                                                                 |

| Input high voltage<br>(all except XTAL1)                                                             | $V_{\rm IH}{ m SR}$      | $0.7 	ext{ x}$<br>$V_{	ext{DDP}}$ | -      | V <sub>DDP</sub><br>+ 0.3         | V    |                                                                                                    |

| Input low voltage<br>(all except XTAL1)                                                              | $V_{\rm IL}{\rm SR}$     | -0.3                              | -      | $0.3 	ext{ x}$<br>$V_{	ext{DDP}}$ | V    |                                                                                                    |

| Output High voltage <sup>8)</sup>                                                                    | V <sub>OH</sub> CC       | V <sub>DDP</sub><br>- 1.0         | _      | -                                 | V    | $I_{\rm OH} \ge I_{\rm OHmax}$                                                                     |

|                                                                                                      |                          | V <sub>DDP</sub><br>- 0.4         | _      | -                                 | V    | $I_{\rm OH} \ge I_{\rm OHnom}^{9)}$                                                                |

### Table 15 DC Characteristics for Lower Voltage Range

2) The pad supply voltage pins (V<sub>DDPB</sub>) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers input stages are switched.

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to 3 + 0.6 x f<sub>SYS</sub>.

3) Please consider the additional conditions described in section "Active Mode Power Supply Current".

### Active Mode Power Supply Current

The actual power supply current in active mode not only depends on the system frequency but also on the configuration of the XC236xA's subsystem.

Besides the power consumed by the device logic the power supply pins also provide the current that flows through the pin output drivers.

A small current is consumed because the drivers' input stages are switched.

The IO power domains can be supplied separately. Power domain A ( $V_{\rm DDPA}$ ) supplies the A/D converters and Port 6. Power domain B ( $V_{\rm DDPB}$ ) supplies the on-chip EVVRs and all other ports.

During operation domain A draws a maximum current of 1.5 mA for each active A/D converter module from  $V_{\rm DDPA}$ .

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to  $(3 + 0.6 \times f_{SYS})$  mA.

## **Direct Drive**

When direct drive operation is selected (SYSCON0.CLKSEL =  $11_B$ ), the system clock is derived directly from the input clock signal CLKIN1:

$f_{SYS} = f_{IN}$ .

The frequency of  $f_{SYS}$  is the same as the frequency of  $f_{IN}$ . In this case the high and low times of  $f_{SYS}$  are determined by the duty cycle of the input clock  $f_{IN}$ .

Selecting Bypass Operation from the XTAL1<sup>1)</sup> input and using a divider factor of 1 results in a similar configuration.

### **Prescaler Operation**

When prescaler operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $1_B$ ), the system clock is derived either from the crystal oscillator (input clock signal XTAL1) or from the internal clock source through the output prescaler K1 (= K1DIV+1):

$f_{\text{SYS}} = f_{\text{OSC}} / \text{K1}.$

If a divider factor of 1 is selected, the frequency of  $f_{\rm SYS}$  equals the frequency of  $f_{\rm OSC}$ . In this case the high and low times of  $f_{\rm SYS}$  are determined by the duty cycle of the input clock  $f_{\rm OSC}$  (external or internal).

The lowest system clock frequency results from selecting the maximum value for the divider factor K1:

$f_{\rm SYS} = f_{\rm OSC} / 1024.$

## 4.6.2.1 Phase Locked Loop (PLL)

When PLL operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $0_B$ ), the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor **F** ( $f_{SYS} = f_{IN} \times F$ ).

**F** is calculated from the input divider P (= PDIV+1), the multiplication factor N (= NDIV+1), and the output divider K2 (= K2DIV+1):

$(F = N / (P \times K2)).$

The input clock can be derived either from an external source at XTAL1 or from the onchip clock source.

The PLL circuit synchronizes the system clock to the input clock. This synchronization is performed smoothly so that the system clock frequency does not change abruptly.

Adjustment to the input clock continuously changes the frequency of  $f_{\text{SYS}}$  so that it is locked to  $f_{\text{IN}}$ . The slight variation causes a jitter of  $f_{\text{SYS}}$  which in turn affects the duration of individual TCSs.

<sup>1)</sup> Voltages on XTAL1 must comply to the core supply voltage  $V_{\text{DDIM}}$ .

### PLL frequency band selection

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| Parameter                                  | Symbol                | Values |      |      | Unit | Note /          |

|--------------------------------------------|-----------------------|--------|------|------|------|-----------------|

|                                            |                       | Min.   | Тур. | Max. |      | Test Condition  |

| VCO output frequency                       | $f_{\rm VCO}{\rm CC}$ | 50     | -    | 110  | MHz  | $VCOSEL = 00_B$ |

| (VCO controlled)                           |                       | 100    | _    | 160  | MHz  | $VCOSEL = 01_B$ |

| VCO output frequency<br>(VCO free-running) | $f_{\rm VCO}{\rm CC}$ | 10     | -    | 40   | MHz  | $VCOSEL = 00_B$ |

|                                            |                       | 20     | -    | 80   | MHz  | $VCOSEL = 01_B$ |

### Table 24 System PLL Parameters

## 4.6.2.2 Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL =  $00_B$ ), the system clock is derived from the low-frequency wakeup clock source:

$f_{SYS} = f_{WU}$ .

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

## 4.6.2.3 Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

Table 26 is valid under the following conditions:

$V_{\text{DDP}} \ge 4.5 \text{ V}; V_{\text{DDPtyp}} = 5 \text{ V}; V_{\text{DDP}} \le 5.5 \text{ V}; C_{\text{L}} \ge 20 \text{ pF}; C_{\text{L}} \le 100 \text{ pF};$

### Table 26 Standard Pad Parameters for Upper Voltage Range

| Parameter                                                    | Symbol                  | Values |      |                                           | Unit | Note /                        |

|--------------------------------------------------------------|-------------------------|--------|------|-------------------------------------------|------|-------------------------------|

|                                                              |                         | Min.   | Тур. | Max.                                      |      | Test Condition                |

| Maximum output driver current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -      | -    | 10                                        | mA   | Strong driver                 |

|                                                              |                         | _      | -    | 4.0                                       | mA   | Medium driver                 |

|                                                              |                         | -      | -    | 0.5                                       | mA   | Weak driver                   |

| Nominal output driver current (absolute value)               | I <sub>Onom</sub><br>CC | -      | -    | 2.5                                       | mA   | Strong driver                 |

|                                                              |                         | _      | -    | 1.0                                       | mA   | Medium driver                 |

|                                                              |                         | -      | -    | 0.1                                       | mA   | Weak driver                   |

| Rise and Fall times (10% -<br>90%)                           | t <sub>RF</sub> CC      | -      | -    | 4.2 +<br>0.14 x<br><i>C</i> <sub>L</sub>  | ns   | Strong driver;<br>Sharp edge  |

|                                                              |                         | -      | -    | 11.6 +<br>0.22 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Medium edge |

|                                                              |                         | -      | -    | 20.6 +<br>0.22 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Slow edge   |

|                                                              |                         | -      | -    | 23 +<br>0.6 x<br><i>C</i> L               | ns   | Medium driver                 |

|                                                              |                         | -      | -    | 212 +<br>1.9 x<br><i>C</i> L              | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

**Electrical Parameters**

### Table 33 USIC SSC Master Mode Timing for Lower Voltage Range (cont'd)

| Parameter                                                   | Symbol            | Values |      |      | Unit | Note /         |

|-------------------------------------------------------------|-------------------|--------|------|------|------|----------------|

|                                                             |                   | Min.   | Тур. | Max. | 1    | Test Condition |

| Receive data input setup<br>time to SCLKOUT receive<br>edge | t <sub>4</sub> SR | 40     | -    | -    | ns   |                |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge    | t <sub>5</sub> SR | -5     | -    | -    | ns   |                |

1)  $t_{SYS} = 1 / f_{SYS}$

### Table 34 USIC SSC Slave Mode Timing for Upper Voltage Range

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                   |                           | Min.   | Тур. | Max. | 1    | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5      | -    | -    | ns   |                |

| Data output DOUT valid time                                                       | <i>t</i> <sub>14</sub> CC | 7      | -    | 33   | ns   |                |

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

| Parameter                                         | Symbol                    | Values           |      |      | Unit | Note /                 |

|---------------------------------------------------|---------------------------|------------------|------|------|------|------------------------|

|                                                   |                           | Min.             | Тур. | Max. |      | Test Condition         |

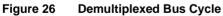

| DAP0 clock period                                 | <i>t</i> <sub>11</sub> SR | 25 <sup>1)</sup> | -    | -    | ns   |                        |

| DAP0 high time                                    | t <sub>12</sub> SR        | 8                | -    | -    | ns   |                        |

| DAP0 low time                                     | t <sub>13</sub> SR        | 8                | -    | -    | ns   |                        |

| DAP0 clock rise time                              | t <sub>14</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP0 clock fall time                              | t <sub>15</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP1 setup to DAP0<br>rising edge                 | <i>t</i> <sub>16</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 hold after DAP0 rising edge                  | <i>t</i> <sub>17</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 valid per DAP0<br>clock period <sup>2)</sup> | <i>t</i> <sub>19</sub> CC | 12               | 17   | -    | ns   | pad_type= stan<br>dard |

### Table 37 DAP Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

2) The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 29 Test Clock Timing (DAP0)