Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                  |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | 2592                                                                      |

| Total RAM Bits                 | 43008                                                                     |

| Number of I/O                  | 171                                                                       |

| Number of Gates                | 80000                                                                     |

| Voltage - Supply               | 3V ~ 3.6V                                                                 |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                           |

| Package / Case                 | 208-BFQFP                                                                 |

| Supplier Device Package        | 208-PQFP (28x28)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/or3t556s208-db |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **System-Level Features**

System-level features reduce glue logic requirements and make a system on a chip possible. These features in the *ORCA* Series 3 include:

- Full PCI local bus compliance.

- Dual-use microprocessor interface (MPI) can be used for configuration, readback, device control, and device status, as well as for a general-purpose interface to the FPGA. Glueless interface to *i960\** and *PowerPC\** processors with user-configurable address space provided.

- Parallel readback of configuration data capability with the built-in microprocessor interface.

- Programmable clock manager (PCM) adjusts clock

phase and duty cycle for input clock rates from 5 MHz to 120 MHz. The PCM may be combined with FPGA logic to create complex functions, such as digital phase-locked loops (DPLL), frequency counters, and frequency synthesizers or clock doublers. Two PCMs are provided per device.

- True, internal, 3-state, bidirectional buses with simple control provided by the SLIC.

- 32 x 4 RAM per PFU, configurable as single- or dualport at >176 MHz. Create large, fast RAM/ROM blocks (128 x 8 in only eight PFUs) using the SLIC decoders as bank drivers.

Table 2. ORCA Series 3 System Performance

| Parameter                                 | # PFUs |       | Spo   | eed  | Unit |       |

|-------------------------------------------|--------|-------|-------|------|------|-------|

| raianietei                                | #1103  | -4    | -5    | -6   | -7   | Oilit |

| 16-bit Loadable Up/Down Counter           | 2      | 78    | 102   | 131  | 168  | MHz   |

| 16-bit Accumulator                        | 2      | 78    | 102   | 131  | 168  | MHz   |

| 8 x 8 Parallel Multiplier:                |        |       |       |      |      |       |

| Multiplier Mode, Unpipelined <sup>1</sup> | 11.5   | 19    | 25    | 30   | 38   | MHz   |

| ROM Mode, Unpipelined <sup>2</sup>        | 8      | 51    | 66    | 80   | 102  | MHz   |

| Multiplier Mode, Pipelined <sup>3</sup>   | 15     | 76    | 104   | 127  | 166  | MHz   |

| 32 x 16 RAM (synchronous):                |        |       |       |      |      |       |

| Single-port, 3-state Bus <sup>4</sup>     | 4      | 97    | 127   | 151  | 192  | MHz   |

| Dual-port <sup>5</sup>                    | 4      | 127   | 166   | 203  | 253  | MHz   |

| 128 x 8 RAM (synchronous):                |        |       |       |      |      |       |

| Single-port, 3-state Bus <sup>4</sup>     | 8      | 88    | 116   | 139  | 176  | MHz   |

| Dual-port <sup>5</sup>                    | 8      | 88    | 116   | 139  | 176  | MHz   |

| 8-bit Address Decode (internal):          |        |       |       |      |      |       |

| Using Softwired LUTs                      | 0.25   | 4.87  | 3.66  | 2.58 | 2.03 | ns    |

| Using SLICs <sup>6</sup>                  | 0      | 2.35  | 1.82  | 1.23 | 0.99 | ns    |

| 32-bit Address Decode (internal):         |        |       |       |      |      |       |

| Using Softwired LUTs                      | 2      | 16.06 | 12.07 | 9.01 | 7.03 | ns    |

| Using SLICs <sup>7</sup>                  | 0      | 6.91  | 5.41  | 4.21 | 3.37 | ns    |

| 36-bit Parity Check (internal)            | 2      | 16.06 | 12.07 | 9.01 | 7.03 | ns    |

<sup>1.</sup> Implemented using 8 x 1 multiplier mode (unpipelined), register-to-register, two 8-bit inputs, one 16-bit output.

<sup>\*</sup> i960 is a registered trademark of Intel Corporation.

<sup>†</sup> PowerPC is a registered trademark of International Business Machines Corporation.

<sup>2.</sup> Implemented using two 32 x 12 ROMs and one 12-bit adder, one 8-bit input, one fixed operand, one 16-bit output.

<sup>3.</sup> Implemented using 8 x 1 multiplier mode (fully pipelined), two 8-bit inputs, one 16-bit output (7 of 15 PFUs contain only pipelining registers).

<sup>4.</sup> Implemented using 32 x 4 RAM mode with read data on 3-state buffer to bidirectional read/write bus.

<sup>5.</sup> Implemented using 32 x 4 dual-port RAM mode.

<sup>6.</sup> Implemented in one partially occupied SLIC with decoded output set up to CE in same PLC.

<sup>7.</sup> Implemented in five partially occupied SLICs.

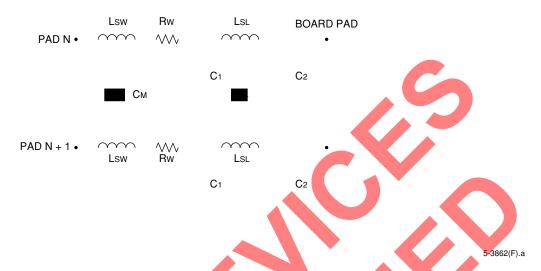

# **Programmable Input/Output Cells**

(continued)

### **Outputs**

The PIC's output drivers have programmable drive capability and slew rates. Three propagation delays (fast, slewlim, sinklim) are available on output drivers. The sinklim mode has the longest propagation delay and is used to minimize system noise and minimize power consumption. The fast and slewlim modes allow critical timing to be met.

The drive current is 12 mA sink/6 mA source for the slewlim and fast output speed selections and 6 mA sink/3 mA source for the sinklim output. Two adjacent outputs can be interconnected to increase the output sink/source current to 24 mA/12 mA.

All outputs that are not speed critical should be configured as sinklim to minimize power and noise. The number of outputs that switch simultaneously in the same direction should be limited to minimize ground bounce. To minimize ground bounce problems, locate heavily loaded output buffers near the ground pads. Ground bounce is generally a function of the driving circuits, traces on the printed-circuit board, and loads and is best determined with a circuit simulation.

At powerup, the output drivers are in slewlim mode, and the input buffers are configured as TTL-level compatible (CMOS for OR3Txxx) with a pull-up. If an output is not to be driven in the selected configuration mode, it is 3-stated.

The output buffer signal can be inverted, and the 3-state control signal can be made active-high, active-low, or always enabled. In addition, this 3-state signal can be registered or nonregistered. Additionally, there is a fast, open-drain output option that directly connects the output signal to the 3-state control, allowing the output buffer to either drive to a logic 0 or 3-state, but never to drive to a logic 1. Because there is no explicit route required to create the open-drain output, its response is very fast. Like the input side of the PIO, there are two output connections from PIC routing to the output side of the PIO, OUT1, and OUT2. These connections provide for flexible routing and can be used in data manipulation in the PIO as described in subsequent paragraphs.

An FF has been added to the output path of the PIO. The register has a local set/reset and clock enable. The LSR has the option to be synchronous or asynchronous and have priority set as clock enable over LSR or LSR over clock enable. Clocking to the output FF can come from either the system clock or the ExpressCLK associated with the PIC. The input to the FF can come from either OUT1 or OUT2, or it can be tied to VDD or GND. Additionally, the input to the FF can be inverted.

#### **Output Multiplexing**

The Series 3 PIO output FF can be combined with the new PIO logic block to perform output data multiplexing with no PLC resources required. The PIO logic block has three multiplexing modes: OUT1OUTREG, OUT2OUTREG, and OUT1OUT2. OUT1OUTREG and OUT2OUTREG are equivalent except that either OUT1 or OUT2 is MUXed with the FF, where the FF data is output on the clock phase after the active edge. The simplest multiplexing mode is OUT1OUT2. In this mode, the signal at OUT1 is output to the pad while the clock is low, and the signal on OUT2 is output to the pad when the clock is high. Figure 25 shows a simple schematic of a PIO in OUT1OUT2 mode and a general timing diagram for multiplexing an address and data signal.

Often an address will be used to generate or read a data sample from memory with the goal of multiplexing the data onto a single line. In this case, the address often precedes the data by one clock cycle.

OUT1OUTREG and OUT2OUTREG modes of the PIO logic can be used to address this situation.

Because OUT1OUTREG mode is equivalent to OUT2OUTREG, only OUT2OUTREG mode is described here. Figure 26 shows a simple PIO schematic in OUT2OUTREG mode and general timing for multiplexing data with a leading address. The address signal on OUT1 is registered in the PIO FF. This delays the address so that it aligns with the data signal. The PIO logic block then sends the OUTREG signal (address) to the pad when the clock is high and the OUT2 signal (data) to the pad when the clock is low, resulting in an aligned, multiplexed signal.

#### **Clock Distribution Network**

The Series 3 FPGAs provide three types of high-speed, low-skew clock distributions: system clock, fast middle clock (fast clock), and ExpressCLK. Because of the great variety of sources and distribution for clock signals in the *ORCA* Series 3, the clock mechanisms will be described here from the inside out. The clock connections to the PFU will be described, followed by clock distribution to the PLC array, clock sources to the PLC array, and finally ending with clock sources and distribution in the PICs. The ExpressCLK inputs are new, dedicated clock inputs in Series 3 FPGAs. They are mentioned in several of the clock network descriptions and are described fully later in this section.

#### **PFU Clock Sources**

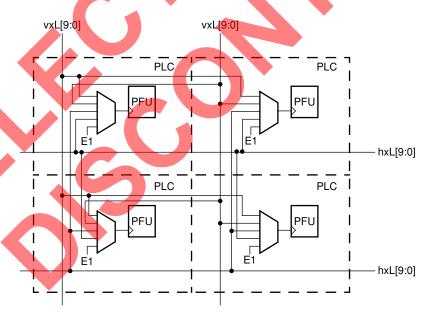

Within a PLC there are five sources for the clock signal of the latches/FFs in the PFU. Two of the signals are generated off of the long lines (xL) within the PLC: one from the set of vertical long lines and one from the set of horizontal long lines. For each of these signals, any one of the ten long lines of each set, vertical or horizontal, can generate the clock signal. Two of the five PFU clock sources come from neighboring PLCs. One clock

is generated from the PLC to the left or right of the current PLC, and one is generated from the PLC above or below the current PLC. The selection decision as to where these signals come from, above/below and left/right, is based on the position of the PLC in the array and has to do with the alternating nature of the source of the system clock spines (discussed later). The last of the five clock sources is also generated within the PLC. The E1 control signal, described in the PLC Routing Resources section, can drive the PFU clock. The E1 signal can come from any xBID routing resource in the PLC. The selection and switching of clock signals in a PLC is performed in the FINS. Figure 31 shows the PFU clock sources for a set of four adjacent PLCs.

### Global Control Signals

The four clock signals in each PLC that are generated from the long lines (xL) in the current PLC or an adjacent PLC can also be used to drive the PFU clock enable (CE), local set/reset (LSR) and add/subtract/write enable (ASWE) signals. The clock signals generated from vertical long lines can drive CE and ASWE, and the clocks generated from horizontal long lines can drive LSR. This allows for low-skew global distribution of two of these three control signals with the clock routing while still allowing a global clock route to occur.

5-6054(F)

Figure 31. PFU Clock Sources

# Programmable Clock Manager (PCM)

(continued)

### Delay-Locked Loop (DLL) Mode

DLL mode is used for implementing a delayed clock (phase adjustment), clock doubling, and duty cycle adjustment. All DLL functions stem from a delay line with 32 taps. The delayed input clock is pulled from various taps and processed to implement the desired result. There is no feedback clock in DLL mode, providing a very stable output and a fast lock time for the output clock.

DLL mode is selected by setting bit 0 in PCM register five to a 0. The settings for the various submodes of DLL mode are described in the following paragraphs. Divider DIV0 may be used with any of the DLL modes to divide the input clock by an integer factor of 1 to 8 prior to implementation of the DLL process.

#### **Delayed Clock**

A delayed version of the input clock can be constructed in DLL mode. The output clock can be delayed by increments of 1/32 of the input clock period. Express CLK and system CLK outputs in delay modes are selected by setting register six, bits [5:4] to 10 or 11 for Express-CLK output, and/or bits [7:6] to 10 for system clock output. The delay value is entered in register four. See register four programming details for more information. Delay values are also shown in the second column of Table 27.

Note that when register six, bits [5:4] are set to 11, the ExpressCLK output is divided by an integer factor from 1 to 8 while the system clock cannot be divided. The ExpressCLK divider is provided so that the I/O clocking provided by the ExpressCLK can operate slower than the internal system clock. This allows for very fast internal processing while maintaining slower interface speeds off-chip for improved noise and power performance or to interoperate with slower devices in the system. The divisor of the ExpressCLK frequency is selected in register two. See the register two programming details for more information.

#### 1x Clock Duty-Cycle Adjustment

A duty-cycle adjusted replica of the input clock can be constructed in DLL mode. The duty cycle can be adjusted in 1/32 (3.125%) increments of the input clock period. DLL 1x clock mode is selected by setting bit 4 of register five to a 1, and output clock source selection is selected by setting register six, bits [5:4] to 01 for ExpressCLK output, and/or bits [7:6] to 01 for system clock output. The duty-cycle percentage value is entered in register four. See register four programming details for more information. Duty cycle values are also shown in the third column of Table 27.

Table 27. DLL Mode Delay/1x Duty Cycle Programming Values

| Register 4 [7:0]<br>7 6 5 4 3 2 1 0 | Delay<br>(CLK_IN/32) | Duty Cycle<br>(% of CLK_IN) |

|-------------------------------------|----------------------|-----------------------------|

| 00XXX000                            | 1                    | 3.125                       |

| 0 0 X X X 0 0 1                     | 2 3                  | 6.250                       |

| 0 0 X X X 0 1 0                     | 3                    | 9.375                       |

| 00XXX011                            | 4                    | 12.500                      |

| 00XXX100                            | 5                    | 15.625                      |

| 00XXX101                            | 6                    | 18.750                      |

| 00XXX110                            | 7                    | 21.875                      |

| 00XXX111                            | 8                    | 25.000                      |

| 01XXX000                            | 9                    | 28.125                      |

| 01XXX001                            | 10                   | 31.250                      |

| 01XXX010                            | 11                   | 34.375                      |

| 01XXX011                            | 12                   | 37.500                      |

| 01XXX100                            | 13                   | 40.625                      |

| 01XXX101                            | 14                   | 43.750                      |

| 01XXX110                            | 15                   | 46.875                      |

| 01111XXX                            | 16                   | 50.000                      |

| 10000XXX                            | 17                   | 53.125                      |

| 10001XXX                            | 18                   | 56.250                      |

| 10010XXX                            | 19                   | 59.375                      |

| 10011XXX                            | 20                   | 62.500                      |

| 10100XXX                            | 21                   | 65.625                      |

| 10101XXX                            | 22                   | 68.750                      |

| 10110XXX                            | 23                   | 71.875                      |

| 10111XXX                            | 24                   | 75.000                      |

| 11000XXX                            | 25                   | 78.125                      |

| 11001XXX                            | 26                   | 81.250                      |

| 11010XXX                            | 27                   | 84.375                      |

| 11011XXX                            | 28                   | 87.500                      |

| 11100XXX                            | 29                   | 90.625                      |

| 11101XXX                            | 30                   | 93.750                      |

| 1 1 1 1 0 X X X                     | 31                   | 96.875                      |

## **Programmable Clock Manager (PCM)**

(continued)

Table 29. PCM Oscillator Frequency Range 3Txxx

**System** Clock Output Frequency Т Register 4 Min Acquisition (MHz) Max 76543210 NOM (MHz) (MHz) (µs) 00XXX010 17.00 58.50 100.00 36.00 00XXX011 52.50 37.00 16.10 89.00 49.00 82.80 38.00 00XXX100 15.17 00XXX101 14.25 45.00 76.50 39.00 00XXX110 13.33 41.50 70.30 40.00 00XXX111 12.40 38.00 64.00 41.00 01XXX000 12.20 36.75 61.30 43.75 01XXX001 12.10 35.00 58.00 46.50 01XXX010 11.90 33.00 54.30 49.25 01XXX011 11.70 31.30 51.00 52.00 01XXX100 30.00 11.10 49.40 54.75 10.50 29.15 47.80 57.50 01XXX101 01XXX110 28.10 46.20 10.00 60.25 01XXX111 9.40 27.00 44.60 63.00 26.25 10000XXX 9.20 43.30 65.40 10001XXX 9.00 25.65 42.30 67.80 10010XXX 8.80 25.00 41.30 70.10 10011XXX 8.60 24.45 40.30 72.50 10100XXX 23.70 8.40 39.00 74.90 10101XXX 8.10 22.90 37.70 77.30 10110XXX 7.90 22.20 36.50 79.60 21.50 10111XXX 7.70 35.20 82.00 11000XXX 7.60 20.80 34.00 84.30 11001XXX 7.45 20.10 32.80 86.50 7.30 11010XXX 19.45 31.60 88.80 11011XXX 7.20 18.85 30.50 91.00 11100XXX 18.30 30.00 93.30 6.60 11101XXX 6.00 17.70 29.40 95.50 11110XXX 5.50 17.10 28.60 97.80 11111XXX 5.00 16.50 28.00 100.00

Note: Use of settings in the first three rows is not recommended. X means don't care.

Table 30. PCM Oscillator Frequency Range 3Cxx

|   |            |       | System          |        |             |

|---|------------|-------|-----------------|--------|-------------|

|   |            |       | System<br>Clock |        |             |

|   |            |       | Output          |        |             |

|   |            |       | Frequency       |        | Т           |

|   | Register 4 | Min   | (MHz)           | Max    | Acquisition |

|   | 76543210   | (MHz) | NOM             | (MHz)  | (µs)        |

|   | 00XXX010   | 10.50 | 73.00           | 135.00 | 36.00       |

|   | 00XXX011   | 10.00 | 68.00           | 126.00 | 37.00       |

|   | 00XXX100   | 9.50  | 63.00           | 117.00 | 38.00       |

|   | 00XXX101   | 9.10  | 58.50           | 108.00 | 39.00       |

|   | 00XXX110   | 8.60  | 53.80           | 99.00  | 40.00       |

|   | 00XXX111   | 8.10  | 49.00           | 90.00  | 41.00       |

| 4 | 01XXX000   | 7.80  | 47.70           | 87.50  | 43.80       |

|   | 01XXX001   | 7.60  | 46.30           | 85.00  | 46.50       |

|   | 01XXX010   | 7.30  | 45.00           | 82.50  | 49.30       |

|   | 01XXX011   | 7.10  | 43.60           | 80.00  | 52.00       |

|   | 01XXX100   | 6.80  | 42.10           | 77.50  | 55.00       |

|   | 01XXX101   | 6.50  | 40.75           | 75.00  | 57.50       |

|   | 01XXX110   | 6.30  | 39.40           | 72.50  | 60.30       |

|   | 01XXX111   | 6.00  | 38.00           | 70.00  | 63.00       |

|   | 10000XXX   | 5.90  | 37.40           | 68.80  | 65.40       |

|   | 10001XXX   | 5.90  | 36.70           | 67.50  | 67.80       |

|   | 10010XXX   | 5.80  | 36.00           | 66.30  | 70.10       |

|   | 10011XXX   | 5.80  | 35.40           | 65.00  | 72.50       |

| ١ | 10100XXX   | 5.70  | 35.00           | 63.80  | 74.90       |

| 7 | 10101XXX   | 5.60  | 34.10           | 62.50  | 77.30       |

|   | 10110XXX   | 5.60  | 33.50           | 61.30  | 79.60       |

|   | 10111XXX   | 5.50  | 32.80           | 60.00  | 82.00       |

|   | 11000XXX   | 5.40  | 32.10           | 58.80  | 84.30       |

|   | 11001XXX   | 5.40  | 31.50           | 57.50  | 86.50       |

|   | 11010XXX   | 5.30  | 30.70           | 56.30  | 88.80       |

|   | 11011XXX   | 5.30  | 30.10           | 55.00  | 91.00       |

|   | 11100XXX   | 5.20  | 29.50           | 53.80  | 93.30       |

|   | 11101XXX   | 5.10  | 28.80           | 52.50  | 95.50       |

|   | 11110XXX   | 5.10  | 28.20           | 51.30  | 97.80       |

|   | 11111XXX   | 5.00  | 27.50           | 50.00  | 100.00      |

Note: Use of settings in the first three rows is not recommended. X means don't care.

# Programmable Clock Manager (PCM) (continued)

# **PCM Detailed Programming**

Descriptions of bit fields and individual control bits in the PCM control registers are provided in Table 31. Refer to Figure 46 for more information on the location of the PCM elements that are discussed. In the following discussion, the duty cycle is in the percentage of the clock period where the clock is high.

**Table 31. PCM Control Registers**

| B              |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit #          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Register 0 Div | rider 0 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bits [3:0]     | <b>4-Bit Divider, DIVO, Value</b> . This value enables the input clock to immediately be divided by a value from 1 to 8. A 0 value (the default) indicates that DIVO is bypassed (no division). Bypass incurs less delay than dividing by 1. Hexadecimal values greater than 8 for bits [3:0] yield their modulo 8 value. For example, if bits [3:0] are 1001 (9 hex), the result is divide by 1 (remainder 9/8 = 1).                              |

| Bits [6:4]     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Bit 7          | <b>DIV 0 Reset Bit.</b> DIV0 may not be reset by GSRN depending on the value of register 7, bit 7. This bit may be set to 1 to reset DIV0 to its default value. Bit 0 must be set to 0 (the default) to remove the reset.                                                                                                                                                                                                                          |

| Register 1 Div | rider 1 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bits [3:0]     | <b>4-Bit Divider, DIV1, Value.</b> This value enables the feedback clock to be divided by a value from 1 to 8. A 0 value (the default) indicates that DIV1 is bypassed (no division). Bypass incurs less delay than dividing by 1. Hexadecimal values greater than 8 for bits [3:0] yield their modulo 8 value. For example, if bits [3:0] are 1001 (9 hex), the result is divide by 1 (remainder 9/8 = 1).                                        |

| Bits [6:4]     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Bit 7          | <b>DIV1 Reset Bit.</b> DIV1 may not be reset by GSRN, depending on the value of register 7, bit 7. This bit may be set to 1 to reset DIV1 to its default value. Bit 0 must be set to 0 (the default) to remove the reset.                                                                                                                                                                                                                          |

|                | rider 2 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bits [3:0]     | <b>4-Bit Divider, DIV2, Value.</b> This value enables the tapped delay line output clock driven onto ExpressCLK to be divided by a value from 1 to 8. A 0 value (the default) indicates that DIV2 is bypassed (no division). Bypass incurs less delay than dividing by 1. Hexadecimal values greater than 8 for bits [3:0] yield their modulo 8 value. For example, if bits [3:0] are 1001 (9 hex), the result is divide by 1 (remainder 9/8 = 1). |

| Bits [6:4]     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Bit 7          | <b>DIV2 Reset Bit.</b> DIV2 may not be reset by GSRN, depending on the value of register 7, bit 7. This bit may be set to 1 to reset DIV2 to its default value. Bit 7 must be set to 0 (the default) to remove the reset.                                                                                                                                                                                                                          |

| Register 3 DL  | L 2x Duty-Cycle Programming                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Bits [2:0]     | Duty-cycle selection for the doubled clock period associated with the input clock high. The duty cycle is (value of bit 6) * 50% + ((value of bits [2:0]) + 1) * 6.25%. See the description for bit 6.                                                                                                                                                                                                                                             |

| Bits [5:3]     | Duty-cycle selection for the doubled clock period associated with the input clock low. The duty cycle is (value of bit 7) * 50% + ((value of bits [2:0]) + 1) * 6.25%. See the description for bit 7.                                                                                                                                                                                                                                              |

| Bit 6          | Master duty-cycle control for the first clock period of the doubled clock: 0 = less than or equal to 50%, 1 = greater than 50%.                                                                                                                                                                                                                                                                                                                    |

| Bit 7          | Master duty-cycle control for the second clock period of the doubled clock: 0 = less than or equal to 50%, 1 = greater than 50%. Example: Both clock periods having a 62.5% duty cycle, bits [7:0] are 11 001 001.                                                                                                                                                                                                                                 |

5-4488(F

### FPGA Configuration Modes (continued)

### **Daisy-Chaining**

Multiple FPGAs can be configured by using a daisy-chain of the FPGAs. Daisy-chaining uses a lead FPGA and one or more FPGAs configured in slave serial mode. The lead FPGA can be configured in any mode except slave parallel mode. (Daisy-chaining is available with the boundary-scan ram\_w instruction discussed later.)

All daisy-chained FPGAs are connected in series. Each FPGA reads and shifts the preamble and length count in on positive CCLK and out on negative CCLK edges.

An upstream FPGA that has received the preamble and length count outputs a high on DOUT until it has received the appropriate number of data frames so that downstream FPGAs do not receive frame start bit pairs. After loading and retransmitting the preamble and length count to a daisy-chain of slave devices, the lead device loads its configuration data frames.

The loading of configuration data continues after the lead device has received its configuration data if its internal frame bit counter has not reached the length count. When the configuration RAM is full and the number of bits received is less than the length count field, the FPGA shifts any additional data out on DOUT.

The configuration data is read into DIN of slave devices on the positive edge of CCLK, and shifted out DOUT on the negative edge of CCLK. Figure 63 shows the connections for loading multiple FPGAs in a daisy-chain configuration.

The generation of CCLK for the daisy-chained devices that are in slave serial mode differs depending on the configuration mode of the lead device. A master parallel mode device uses its internal timing generator to produce an internal CCLK at eight times its memory address rate (RCLK). The asynchronous peripheral mode device outputs eight CCLKs for each write cycle. If the lead device is configured in slave mode, CCLK must be routed to the lead device and to all of the daisy-chained devices.

Figure 63. Daisy-Chain Configuration Schematic

As seen in Figure 63, the INIT pins for all of the FPGAs are connected together. This is required to guarantee that powerup and initialization will work correctly. In general, the DONE pins for all of the FPGAs are also connected together as shown to guarantee that all of the FPGAs enter the start-up state simultaneously. This may not be required, depending upon the start-up sequence desired.

# **Electrical Characteristics**

#### **Table 37. Electrical Characteristics**

OR3Cxx Commercial: VDD =  $5.0 \text{ V} \pm 5\%$ ,  $0 ^{\circ}\text{C} < \text{TA} < 70 ^{\circ}\text{C}$ ; Industrial: VDD =  $5.0 \text{ V} \pm 10\%$ ,  $-40 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ . OR3Txxx Commercial: VDD = 3.0 V to 3.6 V,  $-40 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ .

| Parameter                                              | Sym-       | Test Conditions                                                                                                                                               | OR                    | ЗСхх                  | OR:                             | Тххх                                 | Unit                 |

|--------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|---------------------------------|--------------------------------------|----------------------|

| Parameter                                              | bol        | rest Conditions                                                                                                                                               | Min                   | Max                   | Min                             | Max                                  | Unit                 |

| Input Voltage:<br>High<br>Low                          | VIH<br>VIL | Input configured as CMOS<br>(includes OR3Txxx)                                                                                                                | 50% VDD<br>GND – 0.5  | VDD + 0.5<br>20% VDD  | 50% VDD<br>GND – 0.5            | VDD + 0.5<br>30% VDD                 | <b>&gt;</b> >        |

| Input Voltage:<br>High<br>Low                          | VIH<br>VIL | OR3Txxx 5 V Tolerant                                                                                                                                          | 1                     | <b>J</b> _            | 50% VDD<br>GND - 0.5            | 5.8 V<br>30% VDD                     | V<br>V               |

| Input Voltage:<br>High<br>Low                          | VIH<br>VIL | Input configured as TTL (not valid for OR3Txxx)                                                                                                               | 2.0<br>-0.5           | VDD + 0.3<br>0.8      |                                 | _                                    | V<br>V               |

| Output Voltage:<br>High<br>Low                         | Voh<br>Vol | VDD = min, IOH = 6 mA or 3 mA<br>VDD = min, IOL = 12 mA or 6 mA                                                                                               | 2.4                   |                       | 2.4                             | <br>0.4                              | V<br>V               |

| Input Leakage Current                                  | ΙL         | VDD = max, VIN = Vss or VDD                                                                                                                                   | -10                   | 10                    | -10                             | 10                                   | μΑ                   |

| Standby Current: OR3T20 OR3T30 OR3T55 OR3C/T80 OR3T125 | IDDSB      | OR3Cxx (TA = 25 °C,  VDD = 5.0 V)  OR3Txxx (TA = 25 °C,  VDD = 3.3 V)  internal oscillator running, no output loads, inputs VDD or GND  (after configuration) |                       | <br>4.06<br>4.56<br>  | <br> -<br> -<br> -              | 4.70<br>4.90<br>5.30<br>5.80<br>6.70 | mA<br>mA<br>mA<br>mA |

| Standby Current: OR3T20 OR3T30 OR3T55 OR3C/T80 OR3T125 | IDDSB      | OR3Cxx (TA = 25 °C, VDD = 5.0 V) OR3Txxx (TA = 25 °C, VDD = 3.3 V) internal oscillator stopped, no output loads, inputs VDD or GND (after configuration)      | _<br>_<br>_<br>_<br>_ | <br>3.05<br>3.42<br>  |                                 | 3.52<br>3.68<br>3.98<br>4.35<br>5.02 | mA<br>mA<br>mA<br>mA |

| Powerup Current: OR3T20 OR3T30 OR3T55 OR3C/T80 OR3T125 | lpp        | Power supply current @ approximately 1 V, within a recommended power supply ramp rate of 1 ms—200 ms                                                          | <br>3.2<br>5.4<br>    | _<br>_<br>_<br>_<br>_ | 1.2<br>1.6<br>2.7<br>4.0<br>6.5 | 11111                                | mA<br>mA<br>mA<br>mA |

| Data Retention Voltage                                 | VDR        | TA = 25 °C                                                                                                                                                    | 2.3                   | _                     | 2.3                             | _                                    | V                    |

| Input Capacitance                                      | Cin        | OR3Cxx (TA = 25 °C,<br>VDD = 5.0 V)<br>OR3Txxx (TA = 25 °C,<br>VDD = 3.3 V)<br>Test frequency = 1 MHz                                                         | _                     | 9                     |                                 | 8                                    | pF                   |

| Output Capacitance                                     | Соит       | OR3Cxx (TA = 25 °C,<br>VDD = 5.0 V)<br>OR3Txxx (TA = 25 °C,<br>VDD = 3.3 V)<br>Test frequency = 1 MHz                                                         | _                     | 9                     | _                               | 8                                    | pF                   |

In addition to supply voltage, process variation, and operating temperature, circuit and process improvements of the *ORCA* Series FPGAs over time will result in significant improvement of the actual performance over those listed for a speed grade. Even though lower speed grades may still be available, the distribution of yield to timing parameters may be several speed grades higher than that designated on a product brand. Design practices need to consider best-case timing parameters (e.g., delays = 0), as well as worst-case timing.

The routing delays are a function of fan-out and the capacitance associated with the CIPs and metal interconnect in the path. The number of logic elements that can be driven (fan-out) by PFUs is unlimited, although the delay to reach a valid logic level can exceed timing requirements. It is difficult to make accurate routing delay estimates prior to design compilation based on fan-out. This is because the CAE software may delete redundant logic inserted by the designer to reduce fanout, and/or it may also automatically reduce fanout by net splitting.

The waveform test points are given in the Input/Output Buffer Measurement Conditions section of this data sheet. The timing parameters given in the electrical characteristics tables in this data sheet follow industry practices, and the values they reflect are described below.

Propagation Delay—The time between the specified reference points. The delays provided are the worst case of the tphh and tpll delays for noninverting functions, tplh and tphl for inverting functions, and tphz and tplz for 3-state enable.

**Setup Time**—The interval immediately preceding the transition of a clock or latch enable signal, during which the data must be stable to ensure it is recognized as the intended value.

Hold Time—The interval immediately following the transition of a clock or latch enable signal, during which the data must be held stable to ensure it is recognized as the intended value.

**3-State Enable**—The time from when a 3-state control signal becomes active and the output pad reaches the high-impedance state.

### **PFU Timing**

Table 41. Combinatorial PFU Timing Characteristics

OR3Cxx Commercial: VDD =  $5.0 \text{ V} \pm 5\%$ ,  $0 ^{\circ}\text{C} < \text{TA} < 70 ^{\circ}\text{C}$ ; Industrial: VDD =  $5.0 \text{ V} \pm 10\%$ ,  $-40 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ . OR3Txxx Commercial: VDD = 3.0 V to 3.6 V,  $0 ^{\circ}\text{C} < \text{TA} < 70 ^{\circ}\text{C}$ ; Industrial: VDD = 3.0 V to 3.6 V,  $-40 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ .

|                                                 |            |     |      |     | S    | peed |      |     |      |      |

|-------------------------------------------------|------------|-----|------|-----|------|------|------|-----|------|------|

| Parameter                                       | Symbol     |     | -4   |     | -5   | -    | 6    | -   | 7    | Unit |

|                                                 |            | Min | Max  | Min | Max  | Min  | Max  | Min | Max  |      |

| Combinatorial Delays (TJ = +85 °C, VDD = min);  |            |     |      |     |      |      |      |     |      |      |

| Four-input Variables (Kz[3:0] to F[z])*         | F4_DEL     | _   | 2.34 | _   | 1.80 | _    | 1.32 | _   | 1.05 | ns   |

| Five-input Variables (F5[A:D] to F[0, 2, 4, 6]) | F5_DEL     | _   | 2.11 | _   | 1.57 | _    | 1.23 | _   | 0.99 | ns   |

| Two-level LUT Delay (Kz[3:0] to F w/feedbk)*    | SWL2_DEL   | _   | 4.87 | _   | 3.66 | _    | 2.58 | _   | 2.03 | ns   |

| Two-level LUT Delay (F5[A:D] to F w/feedbk)     | SWL2F5_DEL | _   | 4.69 | _   | 3.51 | _    | 2.48 | _   | 1.94 | ns   |

| Three-level LUT Delay (Kz[3:0] to F w/feedbk)*  | SWL3_DEL   | _   | 6.93 | _   | 5.15 | _    | 3.63 | _   | 2.82 | ns   |

| Three-level LUT Delay (F5[A:D] to F w/feedbk)   | SWL3F5_DEL | _   | 6.89 | _   | 5.08 | _    | 3.54 | _   | 2.75 | ns   |

| CIN to COUT Delay (logic mode)                  | CO_DEL     | _   | 3.47 | _   | 2.65 | _    | 1.79 | _   | 1.43 | ns   |

<sup>\*</sup> Four-input variables' (KZ[3:0)) path delays are valid for LUTs in both F4 (four-input LUT) and F5 (five-input LUT) modes.

#### **Table 42. Sequential PFU Timing Characteristics**

OR3Cxx Commercial: VDD =  $5.0 \text{ V} \pm 5\%$ ,  $0 ^{\circ}\text{C} < \text{TA} < 70 ^{\circ}\text{C}$ ; Industrial: VDD =  $5.0 \text{ V} \pm 10\%$ ,  $-40 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ . OR3Txxx Commercial: VDD = 3.0 V to 3.6 V,  $0 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ .

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |                                                                                      |                      |                                                                                              | Spe                  | eed                                                                                  |                      |                                                                                              |                      |                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------|----------------------|----------------------------------------------|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbol                                                                                        |                                                                                      | -4                   | -                                                                                            | 5                    |                                                                                      | 6                    |                                                                                              | 7                    | Unit                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | Min                                                                                  | Max                  | Min                                                                                          | Max                  | Min                                                                                  | Max                  | Min                                                                                          | Max                  |                                              |

| Input Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                               |                                                                                      |                      |                                                                                              |                      |                                                                                      |                      |                                                                                              |                      |                                              |

| Clock Low Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CLKL_MPW                                                                                      | 3.36                                                                                 | _                    | 2.07                                                                                         |                      | 0.94                                                                                 | _                    | 0.72                                                                                         |                      | ns                                           |

| Clock High Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLKH_MPW                                                                                      | 1.61                                                                                 |                      | 1.06                                                                                         |                      | 0.54                                                                                 | _                    | 0.45                                                                                         |                      | ns                                           |

| Global S/R Pulse Width (GSRN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GSR_MPW                                                                                       | 3.36                                                                                 | 1                    | 2.07                                                                                         |                      | 0.94                                                                                 |                      | 0.72                                                                                         | _                    | ns                                           |

| Local S/R Pulse Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LSR_MPW                                                                                       | 3.36                                                                                 |                      | 2.07                                                                                         | _                    | 0.94                                                                                 | 7                    | 0.72                                                                                         | $\subseteq$          | ns                                           |

| Combinatorial Setup Times (TJ = +85 °C, VDD = min): Four-input Variables to Clock (Kz[3:0] to CLK)* Five-input Variables to Clock (F5[A:D] to CLK) Data In to Clock (DIN[7:0] to CLK) Carry-in to Clock, DIRECT to REGCOUT (CIN to CLK) Clock Enable to Clock (CE to CLK) Clock Enable to Clock (ASWE to CLK) Local Set/Reset to Clock (SYNC) (LSR to CLK) Data Select to Clock (SEL to CLK) Two-level LUT to Clock (Kz[3:0] to CLK w/feedbk)* Two-level LUT to Clock (Kz[3:0] to CLK w/feedbk)* Three-level LUT to Clock (Kz[3:0] to CLK w/feedbk)* | F4_SET F5_SET DIN_SET CINDIR_SET CE1_SET CE2_SET LSR_SET SEL_SET SWL2_SET SWL2F5_SET SWL3_SET | 1.99<br>1.79<br>0.47<br>1.25<br>2.86<br>1.68<br>1.86<br>1.37<br>3.98<br>4.06<br>6.49 |                      | 1.47<br>1.33<br>0.32<br>0.99<br>2.15<br>1.30<br>1.36<br>1.00<br>2.99<br>2.97<br>4.81<br>4.73 |                      | 1.08<br>1.03<br>0.18<br>0.71<br>1.80<br>0.95<br>0.86<br>0.92<br>2.13<br>2.29<br>3.42 |                      | 0.85<br>0.81<br>0.16<br>0.58<br>1.37<br>0.77<br>0.68<br>0.70<br>1.63<br>1.68<br>2.64<br>2.57 |                      | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

| Three-level LUT to Clock (F5[A:D] to CLK w/feedbk)  Combinatorial Hold Times (TJ = all, VDD = all):  Data In (DIN[7:0] from CLK)  Carry-in from Clock, DIRECT to REGCOUT (CIN from CLK)  Clock Enable (CE from CLK)  Clock Enable from Clock (ASWE from CLK)  Local Set/Reset from Clock (sync) (LSR from CLK)  Data Select from Clock (SEL from CLK)  All Others                                                                                                                                                                                    | SWL3F5_SET  DIN_HLD  CINDIR_HLD  CE1_HLD  CE2_HLD  LSR_HLD  SEL_HLD  —                        | 0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00                                 |                      | 0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00                                         | _                    | 0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00                                 |                      | 0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00<br>0.00                                         | _                    | ns ns ns ns ns ns ns ns                      |

| Output Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                               |                                                                                      |                      |                                                                                              |                      |                                                                                      |                      |                                                                                              |                      |                                              |

| Sequential Delays (TJ = +85 °C, VDD = min): Local S/R (async) to PFU Out (LSR to Q[7:0], REG-COUT) Global S/B to PFU Out (GSRN to Q[7:0], REGCOUT) Clock to PFU Out—Register (CLK to Q[7:0], REG-COUT)                                                                                                                                                                                                                                                                                                                                               | LSR_DEL<br>GSR_DEL<br>REG_DEL                                                                 | _<br>_<br>_                                                                          | 7.02<br>5.21<br>2.38 | _<br>_<br>_                                                                                  | 5.29<br>3.90<br>1.75 |                                                                                      | 3.64<br>2.55<br>1.26 |                                                                                              | 2.90<br>2.00<br>0.97 | ns<br>ns<br>ns                               |

| Clock to PFU Out—Latch (CLK to Q[7:0]) Transparent Latch (DIN[7:0] to Q[7:0])                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LTCH_DEL<br>LTCHD_DEL                                                                         | _                                                                                    | 2.51<br>2.73         | _                                                                                            | 1.88<br>2.10         | _                                                                                    | 1.21<br>1.38         | _                                                                                            | 0.96<br>1.12         | ns<br>ns                                     |

<sup>\*</sup> Four-input variables' (Kz[3:0]) setup times are valid for LUTs in both F4 (four-input LUT) and F5 (five-input LUT) modes.

Note: The table shows worst-case delays. ispLEVER reports the delays for individual paths within a group of paths representing the same timing parameter and may accurately report delays that are less than those listed.

104

# **PIO Timing**

### Table 48. Programmable I/O (PIO) Timing Characteristics

OR3Cxx Commercial: VDD =  $5.0 \text{ V} \pm 5\%$ ,  $0 ^{\circ}\text{C} < \text{TA} < 70 ^{\circ}\text{C}$ ; Industrial: VDD =  $5.0 \text{ V} \pm 10\%$ ,  $-40 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ . OR3Txxx Commercial: VDD = 3.0 V to 3.6 V,  $0 ^{\circ}\text{C} < \text{TA} < 70 ^{\circ}\text{C}$ ; Industrial: VDD = 3.0 V to 3.6 V,  $-40 ^{\circ}\text{C} < \text{TA} < +85 ^{\circ}\text{C}$ .

|                                                                                                                                                                                            |                                                    |                              |                              |                              | Sp                           | eed                          |                              | 4                            |                              |                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|----------------------|

| Parameter                                                                                                                                                                                  | Symbol                                             | -                            | 4                            |                              | 5                            |                              | 6                            | -                            | 7                            | Unit                 |

|                                                                                                                                                                                            |                                                    | Min                          | Max                          | Min                          | Max                          | Min                          | Max                          | Min                          | Max                          |                      |

| Input Delays (TJ = 85 °C, VDD = min)                                                                                                                                                       |                                                    |                              |                              |                              |                              |                              |                              |                              |                              |                      |

| Input Rise Time                                                                                                                                                                            | IN_RIS                                             | _                            | 500                          |                              | 500                          |                              | 500                          | _                            | 500                          | ns                   |

| Input Fall Time                                                                                                                                                                            | IN_FAL                                             |                              | 500                          | -                            | 500                          |                              | 500                          | _                            | 500                          | ns                   |

| PIO Direct Delays: Pad to In (pad to CLK IN) Pad to In (pad to IN1, IN2) Pad to In Delayed (pad to IN1, IN2)                                                                               | CKIN_DEL<br>IN_DEL<br>IND_DEL                      |                              | 1.41<br>2.16<br>9.05         | 7                            | 1.26<br>1.87<br>7.83         | _                            | 0.64<br>1.28<br>6.64         | Ê                            | 0.41<br>0.90<br>7.27         | ns<br>ns<br>ns       |

| PIO Transparent Latch Delays: Pad to In (pad to IN1, IN2) Pad to In Delayed (pad to IN1, IN2)                                                                                              | LATCH_DEL<br>LATCHD_DEL                            |                              | 4.11<br>10.58                | _<br>_                       | 3.25<br>9.05                 |                              | 2.52<br>7.67                 |                              | 1.82<br>7.65                 | ns<br>ns             |

| Input Latch/FF Setup Timing: Pad to ExpressCLK (fast-capture latch/FF) Pad Delayed to ExpressCLK (fast-capture latch/FF)                                                                   | INREGE_SET<br>INREGED_SET                          | 5.93<br>12.86                |                              | 4.82<br>11.03                | _                            | 3.63<br>9.18                 | _<br>_                       | 3.23<br>9.68                 | _<br>_                       | ns<br>ns             |

| Pad to Clock (input latch/FF) Pad Delayed to Clock (input latch/FF) Clock Enable to Clock (CE to CLK) Local Set/Reset (sync) to Clock (LSR to CLK)                                         | INREG_SET<br>INREGD_SET<br>INCE_SET<br>INLSR_SET   | 1.62<br>8.57<br>2.03<br>1.79 |                              | 1.42<br>7.36<br>1.64<br>1.45 |                              | 0.71<br>5.91<br>1.29<br>1.14 | _<br>_<br>_<br>_             | 0.50<br>7.06<br>1.00<br>0.89 | _<br>_<br>_<br>_             | ns<br>ns<br>ns       |

| Input FF/Latch Hold Timing: Pad from ExpressCLK (fast-capture latch/FF) Pad Delayed from ExpressCLK (fast-capture latch/FF)                                                                | INREGE_HLD<br>INREGED_HLD                          | 0.00<br>0.00                 |                              | 0.00                         | _<br>_                       | 0.00<br>0.00                 | _                            | 0.00<br>0.00                 | _                            | ns<br>ns             |

| Pad from Clock (input latch/FF) Pad Delayed from Clock (input latch/FF) Clock Enable from Clock (CE from CLK) Local Set/Reset (sync) from Clock (LSR from CLK)                             | INREG_HLD<br>INREGD_HLD<br>INCE_HLD<br>INLSR_HLD   | 0.00<br>0.00<br>0.00<br>0.00 | _<br>_<br>_<br>_             | 0.00<br>0.00<br>0.00<br>0.00 | _<br>_<br>_<br>_             | 0.00<br>0.00<br>0.00<br>0.00 | _<br>_<br>_<br>_             | 0.00<br>0.00<br>0.00<br>0.00 | _<br>_<br>_<br>_             | ns<br>ns<br>ns<br>ns |

| Clock-to-in Delay (FF CLK to IN1, IN2) Clock-to-in Delay (latch CLK to IN1, IN2) Local S/R (async) to IN (LSR to IN1, IN2) Local S/R (async) to IN (LSR to IN1, IN2) LatchFF in Latch Mode | INREG_DEL<br>INLTCH_DEL<br>INLSR_DEL<br>INLSRL_DEL | _<br>_<br>_                  | 4.05<br>4.08<br>6.11<br>5.89 | _<br>_<br>_                  | 3.14<br>3.19<br>4.76<br>4.66 |                              | 2.53<br>2.62<br>3.81<br>3.57 | _<br>_<br>_                  | 2.05<br>2.14<br>3.17<br>2.98 | ns<br>ns<br>ns<br>ns |

| Global S/R to In (GSRN to IN1, IN2)                                                                                                                                                        | INGSR_DEL                                          | _                            | 5.38                         | _                            | 4.22                         | _                            | 3.44                         | _                            | 2.88                         | ns                   |

Note: The delays for all input buffers assume an input rise/fall time of <1 V/ns.

### **Table 51. Boundary-Scan Timing Characteristics**

OR3Cxx Commercial: VDD =  $5.0 \text{ V} \pm 5\%$ , 0 °C < TA < 70 °C; Industrial: VDD =  $5.0 \text{ V} \pm 10\%$ , -40 °C < TA < +85 °C. OR3Txxx Commercial: VDD = 3.0 V to 3.6 V, 0 °C < TA < +85 °C.

| Parameter                  | Symbol | Min  | Max  | Unit |

|----------------------------|--------|------|------|------|

| TDI/TMS to TCK Setup Time  | Ts     | 25.0 | -    | ns   |

| TDI/TMS Hold Time from TCK | Тн     | 0.0  |      | ns   |

| TCK Low Time               | TCL    | 50.0 |      | ns   |

| TCK High Time              | Тсн    | 50.0 |      | ns   |

| TCK to TDO Delay           | TD     | _    | 20.0 | ns   |

| TCK Frequency              | Ттск   |      | 10.0 | MHz  |

Figure 75. Boundary-Scan Timing Diagram

# Pin Information (continued)

Table 67. Pin Descriptions (continued)

| Symbol               | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special-Purp         | ose l | Pins (continued)                                                                                                                                                                                                                                                                                                                                                               |

| M3                   | I     | During powerup and initialization, M3 is used to select the speed of the internal oscillator during configuration with their values latched on the rising edge of INIT. When M3 is low, the oscillator frequency is 10 MHz. When M3 is high, the oscillator is 1.25 MHz. During configuration, a pull-up is enabled.                                                           |

|                      | I/O   | After configuration, this pin is a user-programmable I/O pin (see Note).                                                                                                                                                                                                                                                                                                       |

| TDI, TCK,<br>TMS     | I     | If boundary scan is used, these pins are test data in, test clock, and test mode select inputs. If boundary scan is not selected, all boundary-scan functions are inhibited once configuration is complete. Even if boundary scan is not used, either TCK or TMS must be held at logic 1 during configuration. Each pin has a pull-up enabled during configuration.            |

|                      | I/O   | After configuration, these pins are user-programmable I/O (see Note).                                                                                                                                                                                                                                                                                                          |

| RDY/RCLK/<br>MPI_ALE | 0     | During configuration in peripheral mode, RDY/RCLK indicates another byte can be written to the FPGA. If a read operation is done when the device is selected, the same status is also available on D7 in asynchronous peripheral mode.                                                                                                                                         |

|                      | 0     | During the master parallel configuration mode, RCLK is a read output signal to an external memory. This output is not normally used.                                                                                                                                                                                                                                           |

|                      | ı     | In i960 microprocessor mode, this pin acts as the address latch enable (ALE) input.                                                                                                                                                                                                                                                                                            |

|                      | I/O   | After configuration, if the MPI is not used, this pin is a user-programmable I/O pin (see Note).                                                                                                                                                                                                                                                                               |

| HDC                  | 0     | High During Configuration is output high until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                                                                                                                       |

|                      | I/O   | After configuration, this pin is a user-programmable I/O pin (see Note).                                                                                                                                                                                                                                                                                                       |

| LDC                  | 0     | Low During Configuration is output low until configuration is complete. It is used as a control output, indicating that configuration is not complete.                                                                                                                                                                                                                         |

|                      | I/O   | After configuration, this pin is a user-programmable I/O pin (see Note).                                                                                                                                                                                                                                                                                                       |

| INIT                 | 1/0   | INIT is a bidirectional signal before and during configuration. During configuration, a pull-up is enabled, but an external pull-up resistor is recommended. As an active-low open-drain output, INIT is held low during power stabilization and internal clearing of memory. As an active-low input, INIT holds the FPGA in the wait-state before the start of configuration. |

|                      | I/O   | After configuration, this pin is a user-programmable I/O pin (see Note).                                                                                                                                                                                                                                                                                                       |

Note: The FPGA States of Operation section contains more information on how to control these signals during start-up. The timing of DONE release is controlled by one set of bit stream options, and the timing of the simultaneous release of all other configuration pins (and the activation of all user I/Os) is controlled by a second set of options.

# Pin Information (continued)

### Compatibility with OR2C/TxxA Series

The pinouts shown for the OR3Cxx and OR3Txxx devices are consistent with the OR2C/TxxA Series for all devices offered in the same packages. This includes the following pins: VDD, VSS, VDD5 (OR2TxxA Series only), and all configuration pins.

The following restrictions apply: