Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 20 MIPS                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9×9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc506a-h-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS70204) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

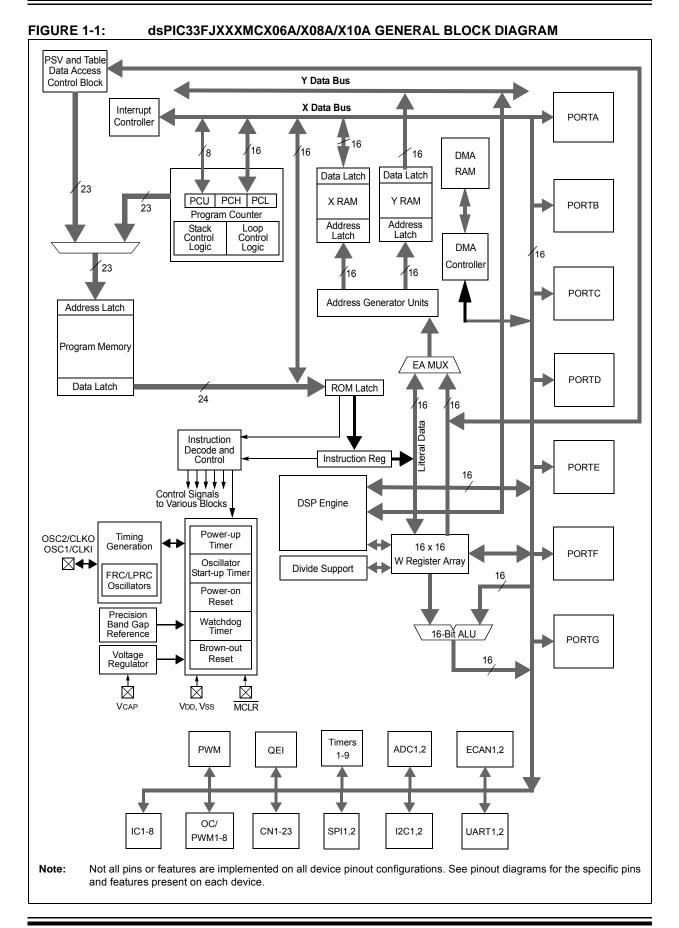

The dsPIC33FJXXXMCX06A/X08A/X10A CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJXXXMCX06A/X08A/X10A devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJXXXMCX06A/X08A/X10A instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum 'C' compiler efficiency. For most instructions, the dsPIC33FJXXXMCX06A/X08A/X10A devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1 and the programmer's model for the dsPIC33FJXXXMCX06A/X08A/X10A is shown in Figure 3-2.

#### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes, and is split into two blocks referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page register (PSVPAG). The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers but may be used as general purpose RAM.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers, and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM memory data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

### TABLE 4-9: 8-OUTPUT PWM REGISTER MAP

| SFR Name  | Addr. | Bit 15  | Bit 14                     | Bit 13                          | Bit 12 | Bit 11 | Bit 10 | Bit 9               | Bit 8               | Bit 7       | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Reset State         |

|-----------|-------|---------|----------------------------|---------------------------------|--------|--------|--------|---------------------|---------------------|-------------|------------|--------|--------|--------|---------|--------|--------|---------------------|

| P1TCON    | 01C0  | PTEN    | —                          | PTSIDL                          | —      | —      | _      | —                   | _                   |             | PTOP       | S<3:0> |        | PTCKP  | 'S<1:0> | PTMO   | D<1:0> | 0000 0000 0000 0000 |

| P1TMR     | 01C2  | PTDIR   |                            |                                 |        |        |        | F                   | WM Time             | r Count Val | ue Registe | er     |        |        |         |        |        | 0000 0000 0000 0000 |

| P1TPER    | 01C4  | _       |                            |                                 |        |        |        | F                   | PWM Time            | Base Perio  | od Registe | r      |        |        |         |        |        | 0000 0000 0000 0000 |

| P1SECMP   | 01C6  | SEVTDIR |                            |                                 |        |        |        | PW                  | M Special           | Event Corr  | pare Regi  | ster   |        |        |         |        |        | 0000 0000 0000 0000 |

| PWM1CON1  | 01C8  |         | _                          | _                               | _      | PMOD4  | PMOD3  | PMOD2               | PMOD1               | PEN4H       | PEN3H      | PEN2H  | PEN1H  | PEN4L  | PEN3L   | PEN2L  | PEN1L  | 0000 0000 1111 1111 |

| PWM1CON2  | 01CA  |         | _                          | _                               | _      |        | SEVOP  | °S<3:0>             |                     | -           | _          | _      | _      | _      | IUE     | OSYNC  | UDIS   | 0000 0000 0000 0000 |

| P1DTCON1  | 01CC  | DTBPS   | 6<1:0>                     | 0> DTB<5:0> DTAPS<1:0> DTA<5:0> |        |        |        | 0000 0000 0000 0000 |                     |             |            |        |        |        |         |        |        |                     |

| P1DTCON2  | 01CE  |         | _                          | _                               | _      | _      | _      | _                   | _                   | DTS4A       | DTS4I      | DTS3A  | DTS3I  | DTS2A  | DTS2I   | DTS1A  | DTS1I  | 0000 0000 0000 0000 |

| P1FLTACON | 01D0  | FAOV4H  | FAOV4L                     | FAOV3H                          | FAOV3L | FAOV2H | FAOV2L | FAOV1H              | FAOV1L              | FLTAM       | _          | _      | _      | FAEN4  | FAEN3   | FAEN2  | FAEN1  | 0000 0000 0000 0000 |

| P1FLTBCON | 01D2  | FBOV4H  | FBOV4L                     | FBOV3H                          | FBOV3L | FBOV2H | FBOV2L | FBOV1H              | FBOV1L              | FLTBM       | _          | _      | _      | FBEN4  | FBEN3   | FBEN2  | FBEN1  | 0000 0000 0000 0000 |

| P10VDCON  | 01D4  | POVD4H  | POVD4L                     | POVD3H                          | POVD3L | POVD2H | POVD2L | POVD1H              | POVD1L              | POUT4H      | POUT4L     | POUT3H | POUT3L | POUT2H | POUT2L  | POUT1H | POUT1L | 1111 1111 0000 0000 |

| P1DC1     | 01D6  |         |                            |                                 |        |        |        | PW                  | /I Duty Cyc         | le #1 Regis | ster       |        |        |        |         |        |        | 0000 0000 0000 0000 |

| P1DC2     | 01D8  |         | PWM Duty Cycle #2 Register |                                 |        |        |        |                     | 0000 0000 0000 0000 |             |            |        |        |        |         |        |        |                     |

| P1DC3     | 01DA  |         |                            |                                 |        |        |        | PW                  | /I Duty Cyc         | le #3 Regi  | ster       |        |        |        |         |        |        | 0000 0000 0000 0000 |

| P1DC4     | 01DC  |         | PWM Duty Cycle #4 Register |                                 |        |        |        | 0000 0000 0000 0000 |                     |             |            |        |        |        |         |        |        |                     |

Legend: u = uninitialized bit, - = unimplemented, read as '0'

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address           | AIVT Address          | Interrupt Source                   |

|------------------|--------------------------------------|-----------------------|-----------------------|------------------------------------|

| 54               | 46                                   | 0x000070              | 0x000170              | DMA4 – DMA Channel 4               |

| 55               | 47                                   | 0x000072              | 0x000172              | T6 – Timer6                        |

| 56               | 48                                   | 0x000074              | 0x000174              | T7 – Timer7                        |

| 57               | 49                                   | 0x000076              | 0x000176              | SI2C2 – I2C2 Slave Events          |

| 58               | 50                                   | 0x000078              | 0x000178              | MI2C2 – I2C2 Master Events         |

| 59               | 51                                   | 0x00007A              | 0x00017A              | T8 – Timer8                        |

| 60               | 52                                   | 0x00007C              | 0x00017C              | T9 – Timer9                        |

| 61               | 53                                   | 0x00007E              | 0x00017E              | INT3 – External Interrupt 3        |

| 62               | 54                                   | 0x000080              | 0x000180              | INT4 – External Interrupt 4        |

| 63               | 55                                   | 0x000082              | 0x000182              | C2RX – ECAN2 Receive Data Ready    |

| 64               | 56                                   | 0x000084              | 0x000184              | C2 – ECAN2 Event                   |

| 65               | 57                                   | 0x000086              | 0x000186              | PWM – PWM Period Match             |

| 66               | 58                                   | 0x000088              | 0x000188              | QEI – Position Counter Compare     |

| 69               | 61                                   | 0x00008E              | 0x00018E              | DMA5 – DMA Channel 5               |

| 70               | 62                                   | 0x000090              | 0x000190              | Reserved                           |

| 71               | 63                                   | 0x000092              | 0x000192              | FLTA – MCPWM Fault A               |

| 72               | 64                                   | 0x000094              | 0x000194              | FLTB – MCPWM Fault B               |

| 73               | 65                                   | 0x000096              | 0x000196              | U1E – UART1 Error                  |

| 74               | 66                                   | 0x000098              | 0x000198              | U2E – UART2 Error                  |

| 75               | 67                                   | 0x00009A              | 0x00019A              | Reserved                           |

| 76               | 68                                   | 0x00009C              | 0x00019C              | DMA6 – DMA Channel 6               |

| 77               | 69                                   | 0x00009E              | 0x00019E              | DMA7 – DMA Channel 7               |

| 78               | 70                                   | 0x0000A0              | 0x0001A0              | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                                   | 0x0000A2              | 0x0001A2              | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 72-117                               | 0x0000A4-<br>0x0000FE | 0x0001A4-<br>0x0001FE | Reserved                           |

### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

#### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

| U-0          | R/W-1                                                                                                                              | R/W-0                 | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| _            |                                                                                                                                    | T8IP<2:0>             |                |                   |                 | MI2C2IP<2:0>    |       |  |  |  |  |  |  |

| bit 15       | ·                                                                                                                                  |                       |                |                   | •               |                 | bit   |  |  |  |  |  |  |

|              |                                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                              | R/W-0                 | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|              |                                                                                                                                    | SI2C2IP<2:0>          |                | —                 |                 | T7IP<2:0>       | 1.11  |  |  |  |  |  |  |

| bit 7        |                                                                                                                                    |                       |                |                   |                 |                 | bit   |  |  |  |  |  |  |

| Legend:      |                                                                                                                                    |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                             | W = Writable b        | oit            | U = Unimple       | mented bit, rea | d as '0'        |       |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                              | '1' = Bit is set      |                | '0' = Bit is cle  | eared           | x = Bit is unkr | iown  |  |  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                          | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |  |  |

| bit 14-12    | -                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | <b>T8IP&lt;2:0&gt;:</b> Timer8 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)               |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                                                                                                      |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 000 = Inter                                                                                                                        | rupt source is disa   | abled          |                   |                 |                 |       |  |  |  |  |  |  |

| bit 11       | Unimpleme                                                                                                                          | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |  |  |

| bit 10-8     | MI2C2IP<2:0>: I2C2 Master Events Interrupt Priority bits                                                                           |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul>                                                     |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 7        |                                                                                                                                    | ented: Read as '0     |                |                   |                 |                 |       |  |  |  |  |  |  |

| bit 6-4      | -                                                                                                                                  |                       |                | unt Priority hite |                 |                 |       |  |  |  |  |  |  |

| DIL 0-4      | <b>SI2C2IP&lt;2:0&gt;:</b> I2C2 Slave Events Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •<br>001 = Inter                                                                                                                   | rupt is priority 1    |                |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                                                                    | rupt source is disa   | abled          |                   |                 |                 |       |  |  |  |  |  |  |

| bit 3        | Unimpleme                                                                                                                          | ented: Read as 'o     | )'             |                   |                 |                 |       |  |  |  |  |  |  |

| bit 2-0      | T7IP<2:0>:                                                                                                                         | Timer7 Interrupt      | Priority bits  |                   |                 |                 |       |  |  |  |  |  |  |

|              | 111 = Inter                                                                                                                        | rupt is priority 7 (h | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                                                                                  |                       |                |                   |                 |                 |       |  |  |  |  |  |  |

|              | 001 = Inter                                                                                                                        | rupt is priority 1    |                |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                                                                    | rupt source is disa   |                |                   |                 |                 |       |  |  |  |  |  |  |

#### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

### 11.6 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 26-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and Vss. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 26.0 "Electrical Characteristics" for additional information.

### 11.7 I/O Resources

Many useful resources related to I/O are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en546066

#### 11.7.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| R/W-0           | U-0                                                         | R/W-0                             | U-0            | U-0               | U-0            | U-0                | U-0 |  |  |  |  |  |

|-----------------|-------------------------------------------------------------|-----------------------------------|----------------|-------------------|----------------|--------------------|-----|--|--|--|--|--|

| TON             | _                                                           | TSIDL                             | —              | —                 | _              | —                  | _   |  |  |  |  |  |

| bit 15          |                                                             | •                                 |                |                   |                |                    | bit |  |  |  |  |  |

|                 |                                                             |                                   |                |                   |                |                    |     |  |  |  |  |  |

| U-0             | R/W-0                                                       | R/W-0                             | R/W-0          | R/W-0             | U-0            | R/W-0              | U-0 |  |  |  |  |  |

| _               | TGATE                                                       | TCKP                              | S<1:0>         | T32               | _              | TCS <sup>(1)</sup> |     |  |  |  |  |  |

| bit 7           |                                                             |                                   |                |                   |                |                    | bit |  |  |  |  |  |

| Legend:         |                                                             |                                   |                |                   |                |                    |     |  |  |  |  |  |

| R = Readable    | bit                                                         | W = Writable                      | bit            | U = Unimplem      | ented bit, rea | d as '0'           |     |  |  |  |  |  |

| -n = Value at F | POR                                                         | '1' = Bit is set                  | t              | '0' = Bit is clea |                | x = Bit is unkno   | own |  |  |  |  |  |

| bit 15          | <b>TON:</b> Timerx<br>When T32 = 2                          | L <u>:</u>                        |                |                   |                |                    |     |  |  |  |  |  |

|                 | 1 = Starts 32-<br>0 = Stops 32-                             |                                   |                |                   |                |                    |     |  |  |  |  |  |

|                 | When T32 = 0<br>1 = Starts 16-<br>0 = Stops 16-             | bit Timerx                        |                |                   |                |                    |     |  |  |  |  |  |

| bit 14          | •                                                           | ted: Read as '                    | 0'             |                   |                |                    |     |  |  |  |  |  |

| bit 13          | TSIDL: Stop i                                               | n Idle Mode bi                    | t              |                   |                |                    |     |  |  |  |  |  |

|                 |                                                             | ue module ope<br>module operat    |                | evice enters Idle | e mode         |                    |     |  |  |  |  |  |

| bit 12-7        | Unimplemen                                                  | ted: Read as '                    | 0'             |                   |                |                    |     |  |  |  |  |  |

| bit 6           | TGATE: Timerx Gated Time Accumulation Enable bit            |                                   |                |                   |                |                    |     |  |  |  |  |  |

|                 | When TCS = 1:                                               |                                   |                |                   |                |                    |     |  |  |  |  |  |

|                 | This bit is ignored.                                        |                                   |                |                   |                |                    |     |  |  |  |  |  |

|                 | <u>When TCS = 0:</u><br>1 = Gated time accumulation enabled |                                   |                |                   |                |                    |     |  |  |  |  |  |

|                 |                                                             | e accumulatio                     |                |                   |                |                    |     |  |  |  |  |  |

| bit 5-4         | TCKPS<1:0>                                                  | : Timerx Input                    | Clock Prescal  | e Select bits     |                |                    |     |  |  |  |  |  |

|                 | 11 <b>= 1:256</b>                                           |                                   |                |                   |                |                    |     |  |  |  |  |  |

|                 | 10 = 1:64                                                   |                                   |                |                   |                |                    |     |  |  |  |  |  |

|                 | 01 = 1:8<br>00 = 1:1                                        |                                   |                |                   |                |                    |     |  |  |  |  |  |

| bit 3           |                                                             | mer Mode Sel                      | ect bit        |                   |                |                    |     |  |  |  |  |  |

|                 | 1 = Timerx ar                                               | nd Timery form<br>nd Timery act a | a single 32-bi |                   |                |                    |     |  |  |  |  |  |

| bit 2           |                                                             | ted: Read as '                    |                |                   |                |                    |     |  |  |  |  |  |

| bit 1           | -                                                           | Clock Source                      |                |                   |                |                    |     |  |  |  |  |  |

|                 |                                                             | clock from TxC                    |                | rising edge)      |                |                    |     |  |  |  |  |  |

|                 |                                                             |                                   |                |                   |                |                    |     |  |  |  |  |  |

### REGISTER 13-1: TxCON (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

#### 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This   | insures               | that  | the        | first | fr | ame |

|-------|--------|-----------------------|-------|------------|-------|----|-----|

|       | transr | nission a             | after | initializa | ation | is | not |

|       | shifte | shifted or corrupted. |       |            |       |    |     |

- 2. In non-framed 3-wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- Note: This will insure that during power-up and initialization the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame sync pulse is active on the SSx pin, which indicates the start of a data frame.

| Note: | Not all third-party devices support Frame |

|-------|-------------------------------------------|

|       | mode timing. Refer to the SPI electrical  |

|       | characteristics for details.              |

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must guarantee enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI shift register and is empty once the data transmission begins.

#### 18.2 SPI Resources

Many useful resources related to SPI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en546066                                                       |

#### 18.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

## 18.3 SPI Control Registers

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0  | U-0    | R/W-0   | U-0 | U-0 | U-0 | U-0    | U-0    |

|--------|--------|---------|-----|-----|-----|--------|--------|

| SPIEN  | —      | SPISIDL | —   |     | —   |        | —      |

| bit 15 |        |         |     |     |     |        | bit 8  |

|        |        |         |     |     |     |        |        |

| U-0    | R/C-0  | U-0     | U-0 | U-0 | U-0 | R-0    | R-0    |

| —      | SPIROV | —       | —   | _   | —   | SPITBF | SPIRBF |

| bit 7  |        |         |     |     |     |        | bit 0  |

| Legend:           | C = Clearable bit |                       |                                    |  |  |  |

|-------------------|-------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 15   | SPIEN: SPIx Enable bit                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module                                                                                                                                                                               |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 13   | SPISIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                |

|          | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                                                                                                                                                         |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 6    | SPIROV: Receive Overflow Flag bit                                                                                                                                                                                                                                                             |

|          | <ul> <li>1 = A new byte/word is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.</li> <li>0 = No overflow has occurred</li> </ul>                                                                                                 |

| bit 5-2  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 1    | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                                                  |

|          | 1 = Transmit not yet started; SPIxTXB is full                                                                                                                                                                                                                                                 |

|          | 0 = Transmit started; SPIxTXB is empty<br>Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB. Automatically<br>cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.                                                                       |

| bit 0    | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                                                   |

|          | <ul> <li>1 = Receive complete; SPIxRXB is full</li> <li>0 = Receive is not complete; SPIxRXB is empty</li> <li>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.</li> </ul> |

#### TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                              |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈<br>{W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                         |  |  |  |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                            |  |  |  |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                    |  |  |  |

| Wnd   | One of 16 destination working registers $\in$ {W0W15}                                                                                                                                                                                                    |  |  |  |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                             |  |  |  |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                 |  |  |  |

| Ws    | Source W register ∈ {Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws]}                                                                                                                                                                                               |  |  |  |

| Wso   | Source W register ∈<br>{Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb]}                                                                                                                                                                            |  |  |  |

| Wx    | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8]+ = 6, [W8]+ = 4, [W8]+ = 2, [W8], [W8]- = 6, [W8]- = 4, [W8]- = 2,<br>[W9]+ = 6, [W9]+ = 4, [W9]+ = 2, [W9], [W9]- = 6, [W9]- = 4, [W9]- = 2,<br>[W9 + W12], none}                |  |  |  |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |  |  |  |

| Wy    | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10]+ = 6, [W10]+ = 4, [W10]+ = 2, [W10], [W10]- = 6, [W10]- = 4, [W10]- = 2,<br>[W11]+ = 6, [W11]+ = 4, [W11]+ = 2, [W11], [W11]- = 6, [W11]- = 4, [W11]- = 2,<br>[W11 + W12], none} |  |  |  |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |  |  |  |

### 25.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 25.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 25.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 25.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

| DC CHARACTERISTICS |                          |     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |       |        |            |         |  |

|--------------------|--------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------------|---------|--|

| Parameter<br>No.   | Typical <sup>(2)</sup>   | Max | Doze Ratio                                                                                                                                                                                                                                                                              | Units |        | Conditions |         |  |

| Doze Current       | : (IDOZE) <sup>(1)</sup> |     |                                                                                                                                                                                                                                                                                         |       |        |            |         |  |

| DC73a              | 11                       | 35  | 1:2                                                                                                                                                                                                                                                                                     | mA    |        |            |         |  |

| DC73f              | 11                       | 30  | 1:64                                                                                                                                                                                                                                                                                    | mA    | -40°C  | 3.3V       | 40 MIPS |  |

| DC73g              | 11                       | 30  | 1:128                                                                                                                                                                                                                                                                                   | mA    |        |            |         |  |

| DC70a              | 42                       | 50  | 1:2                                                                                                                                                                                                                                                                                     | mA    |        |            |         |  |

| DC70f              | 26                       | 30  | 1:64                                                                                                                                                                                                                                                                                    | mA    | +25°C  | 3.3V       | 40 MIPS |  |

| DC70g              | 25                       | 30  | 1:128                                                                                                                                                                                                                                                                                   | mA    |        |            |         |  |

| DC71a              | 41                       | 50  | 1:2                                                                                                                                                                                                                                                                                     | mA    |        |            |         |  |

| DC71f              | 25                       | 30  | 1:64                                                                                                                                                                                                                                                                                    | mA    | +85°C  | 3.3V       | 40 MIPS |  |

| DC71g              | 24                       | 30  | 1:128                                                                                                                                                                                                                                                                                   | mA    | ]      |            |         |  |

| DC72a              | 42                       | 50  | 1:2                                                                                                                                                                                                                                                                                     | mA    |        |            |         |  |

| DC72f              | 26                       | 30  | 1:64                                                                                                                                                                                                                                                                                    | mA    | +125°C | 3.3V       | 40 MIPS |  |

| DC72g              | 25                       | 30  | 1:128                                                                                                                                                                                                                                                                                   | mA    |        |            |         |  |

#### TABLE 26-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail with overshoot/undershoot < 250 mV</li>

- CLKO is configured as an I/O input pin in the Configuration word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU executing while(1) statement

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

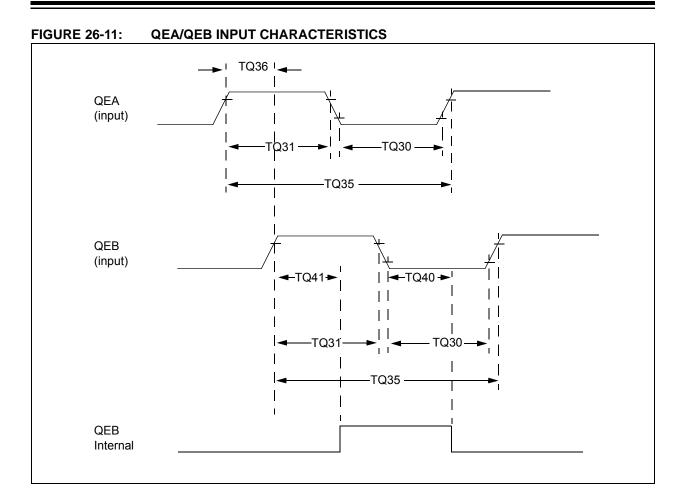

#### TABLE 26-29: QUADRATURE DECODER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |  |                    |     |       |                                                         |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------------|-----|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                       |  | Тур <sup>(2)</sup> | Мах | Units | Conditions                                              |

| TQ30               | TQUL   | Quadrature Input Low Time                                                                                                                                                                                                                                                           |  | 6 Tcy              | _   | ns    | —                                                       |

| TQ31               | ΤουΗ   | Quadrature Input High Time                                                                                                                                                                                                                                                          |  | 6 Tcy              |     | ns    | —                                                       |

| TQ35               | TQUIN  | Quadrature Input Period                                                                                                                                                                                                                                                             |  | 12 TCY             | _   | ns    | —                                                       |

| TQ36               | TQUP   | Quadrature Phase Period                                                                                                                                                                                                                                                             |  | 3 TCY              | —   | ns    | —                                                       |

| TQ40               | TQUFL  | Filter Time to Recognize Low with Digital Filter                                                                                                                                                                                                                                    |  | 3 * N * Tcy        | —   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 3)</b> |

| TQ41               | TQUFH  | Filter Time to Recognize High with Digital Filter                                                                                                                                                                                                                                   |  | 3 * N * Tcy        | —   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 3)</b> |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** N = Index Channel Digital Filter Clock Divide Select bits. Refer to **Section 15. "Quadrature Encoder Interface (QEI)"** (DS70208) in the "*dsPIC33F/PIC24H Family Reference Manual*".

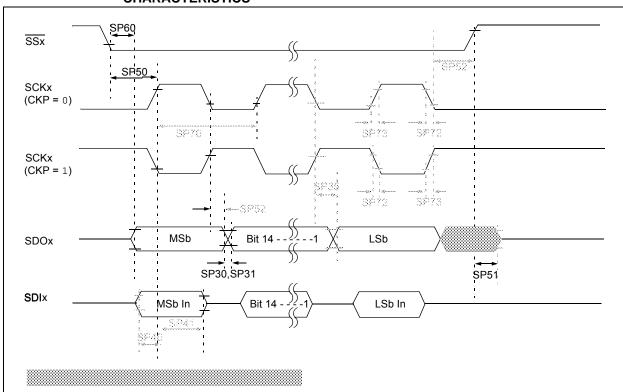

## FIGURE 26-19: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

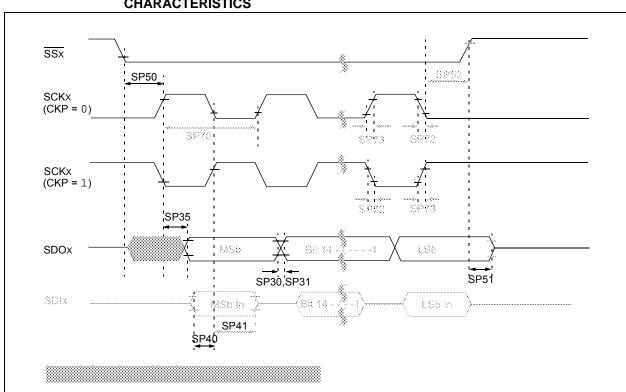

## FIGURE 26-20: SPIX SLAVE MODE (FULL-DUPLEX CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |           |                        |           |         |                                                  |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|-----------|---------|--------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                              | Min.      | Тур                    | Max.      | Units   | Conditions                                       |

|                    |        | ADC Accuracy (12-Bit Mo                                                                                                                                                                                     | de) – Mea | asureme                | nts with  | Externa | al Vref+/Vref-                                   |

| AD20a              | Nr     | Resolution                                                                                                                                                                                                  | 1:        | 2 data bi              | ts        | bits    | —                                                |

| AD21a              | INL    | Integral Nonlinearity                                                                                                                                                                                       | -2        | _                      | +2        | LSb     | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| AD22a              | DNL    | Differential Nonlinearity                                                                                                                                                                                   | >-1       | —                      | <1        | LSb     | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| AD23a              | Gerr   | Gain Error                                                                                                                                                                                                  | -         | 3.4                    | 10        | LSb     | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD24a              | EOFF   | Offset Error                                                                                                                                                                                                | Q         | 0.9                    | 5         | LSb     | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| AD25a              | _      | Monotonicity                                                                                                                                                                                                | _         |                        |           | _       | Guaranteed                                       |

|                    |        | ADC Accuracy (12-Bit Mo                                                                                                                                                                                     | de) – Mea | asureme                | ents with | Interna | I VREF+/VREF-                                    |

| AD20b              | Nr     | Resolution                                                                                                                                                                                                  | 1:        | 2 data bi <sup>.</sup> | ts        | bits    | —                                                |

| AD21b              | INL    | Integral Nonlinearity                                                                                                                                                                                       | -2        |                        | +2        | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD22b              | DNL    | Differential Nonlinearity                                                                                                                                                                                   | >-1       |                        | <1        | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD23b              | Gerr   | Gain Error                                                                                                                                                                                                  | —         | 10.5                   | 20        | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD24b              | EOFF   | Offset Error                                                                                                                                                                                                |           | 3.8                    | 10        | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |

| AD25b              | —      | Monotonicity                                                                                                                                                                                                |           |                        |           |         | Guaranteed                                       |

|                    |        | Dynamie                                                                                                                                                                                                     | c Perforn | nance (1               | 2-Bit Mo  | de)     |                                                  |

| AD30a              | THD    | Total Harmonic Distortion                                                                                                                                                                                   | —         |                        | -75       | dB      | —                                                |

| AD31a              | SINAD  | Signal to Noise and Distortion                                                                                                                                                                              | 68.5      | 69.5                   | _         | dB      | _                                                |

| AD32a              | SFDR   | Spurious Free Dynamic<br>Range                                                                                                                                                                              | 80        | —                      |           | dB      | _                                                |

| AD33a              | Fnyq   | Input Signal Bandwidth                                                                                                                                                                                      | _         |                        | 250       | kHz     | —                                                |

| AD34a              | ENOB   | Effective Number of Bits                                                                                                                                                                                    | 11.09     | 11.3                   |           | bits    | _                                                |

## TABLE 26-44: ADC MODULE SPECIFICATIONS (12-BIT MODE)<sup>(1)</sup>

**Note 1:** Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

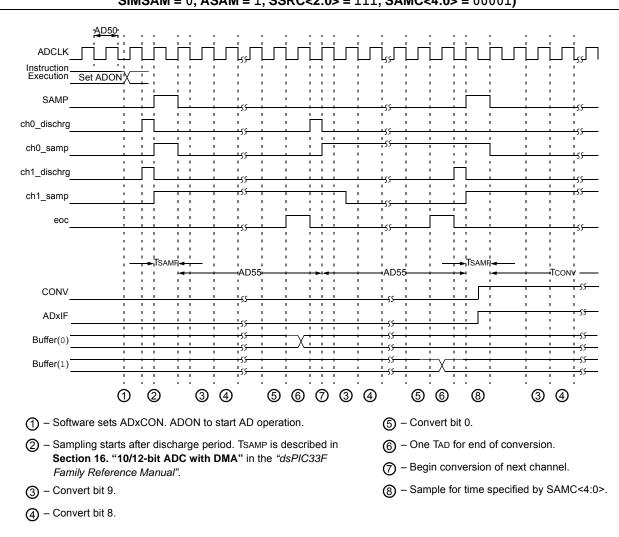

## FIGURE 26-29:ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01,<br/>SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

### 29.1 Package Marking Information (Continued)

100-Lead TQFP (12x12x1 mm)

100-Lead TQFP (14x14x1mm)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3) | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn) |

|--------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | *                                     | This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.                                                                                                                                      |

|        | be carrie                             | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>for customer-specific information.                                                                       |

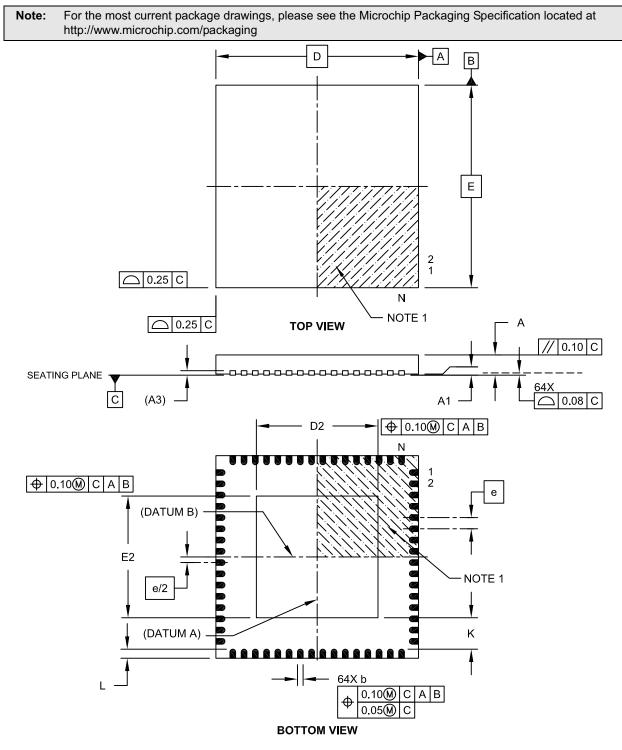

### 29.2 Package Details

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

| Section Name                                               | Update Description                                                                                                                                          |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 26.0 "Electrical Characteristics"                  | Removed Note 4 from the DC Temperature and Voltage Specifications (see Table 26-4).                                                                         |