Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc506a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

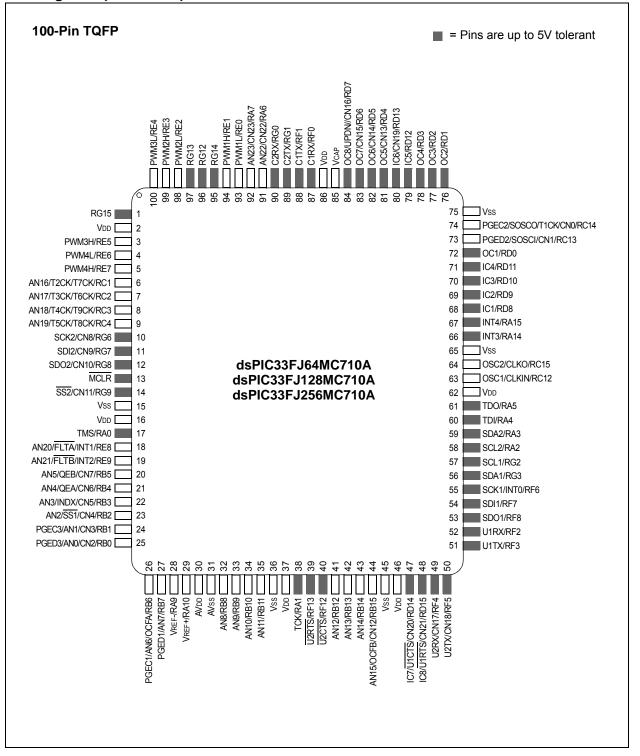

### **Pin Diagrams (Continued)**

### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXMCX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's *Reference Manual*" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXMCX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed sign operation in several MCU multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXMCX06A/X08A/X10A devices are a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF)

- 2. Signed or unsigned DSP multiply (US)

- 3. Conventional or convergent rounding (RND)

- 4. Automatic saturation on/off for AccA (SATA)

- 5. Automatic saturation on/off for AccB (SATB)

- 6. Automatic saturation on/off for writes to data memory (SATDW)

- 7. Accumulator Saturation mode selection (ACCSAT)

Table 2-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

| SUMMARY     |                         |                   |  |  |  |  |  |  |  |

|-------------|-------------------------|-------------------|--|--|--|--|--|--|--|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |  |  |  |  |  |  |  |

| CLR         | A = 0                   | Yes               |  |  |  |  |  |  |  |

| ED          | $A = (x - y)^2$         | No                |  |  |  |  |  |  |  |

| EDAC        | $A = A + (x - y)^2$     | No                |  |  |  |  |  |  |  |

| MAC         | $A = A + (x \bullet y)$ | Yes               |  |  |  |  |  |  |  |

| MAC         | $A = A + x^2$           | No                |  |  |  |  |  |  |  |

| MOVSAC      | No change in A          | Yes               |  |  |  |  |  |  |  |

| MPY         | $A = x \bullet y$       | No                |  |  |  |  |  |  |  |

| MPY         | $A = x^2$               | No                |  |  |  |  |  |  |  |

| MPY.N       | $A = -x \bullet y$      | No                |  |  |  |  |  |  |  |

| MSC         | $A = A - x \bullet y$   | Yes               |  |  |  |  |  |  |  |

#### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier/scaler is a 33-bit value which is sign-extended to 40 bits. Integer data is inherently represented as a signed two's complement value, where the MSb is defined as a sign bit. Generally speaking, the range of an N-bit two's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ . For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including 0. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518 x 10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product which has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions which include integer 16-bit signed, unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

### 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter prior to accumulation.

### 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true, or complement data into the other input. In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented); whereas in the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented. The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described above and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS register bits have been provided to support saturation and overflow; they are:

- 1. OA: AccA overflowed into guard bits

- OB: AccB overflowed into guard bits

- 3. SA:

AccA saturated (bit 31 overflow and saturation) or

AccA overflowed into guard bits and saturated (bit 39 overflow and saturation)

- 4. SB:

- AccB saturated (bit 31 overflow and saturation) or

AccB overflowed into guard bits and saturated (bit 39 overflow and saturation)

5. OAB:

Logical OR of OA and OB

6. SAB:

Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when they and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register (refer to **Section 7.0 "Interrupt Controller"**) are set. This allows the user to take immediate action, for example, to correct system gain.

### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is as follows:

- 1. Read eight rows of program memory (512 instructions) and store it in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5 using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMC | ON for block erase operation         |                                         |

|---------------|--------------------------------------|-----------------------------------------|

| MOV           | #0x4042, W0                          | ;                                       |

| MOV           | W0, NVMCON                           | ; Initialize NVMCON                     |

| ; Init pointe | r to row to be ERASED                |                                         |

| MOV           | <pre>#tblpage(PROG_ADDR), W0</pre>   | ;                                       |

| MOV           | W0, TBLPAG                           | ; Initialize PM Page Boundary SFR       |

| MOV           | <pre>#tbloffset(PROG_ADDR), W0</pre> | ; Initialize in-page EA[15:0] pointer   |

| TBLWT         | L WO, [WO]                           | ; Set base address of erase block       |

| DISI          | #5                                   | ; Block all interrupts with priority <7 |

|               |                                      | ; for next 5 instructions               |

| MOV           | #0x55, W0                            |                                         |

| MOV           | W0, NVMKEY                           | ; Write the 55 key                      |

| MOV           | #0xAA, W1                            | ;                                       |

| MOV           | W1, NVMKEY                           | ; Write the AA key                      |

| BSET          | NVMCON, #WR                          | ; Start the erase sequence              |

| NOP           |                                      | ; Insert two NOPs after the erase       |

| NOP           |                                      | ; command is asserted                   |

|               |                                      |                                         |

#### R/W-0 U-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 FLTAIE DMA5IE \_\_\_\_ QEIIE **PWMIE** C2IE \_\_\_\_ \_\_\_\_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 C2RXIE INT4IE INT3IE T9IE T8IE MI2C2IE SI2C2IE T7IE bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLTAIE: PWM Fault A Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 14 Unimplemented: Read as '0' bit 13 DMA5IE: DMA Channel 5 Data Transfer Complete Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 12-11 Unimplemented: Read as '0' bit 10 **QEIIE:** QEI Event Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 9 **PWMIE:** PWM Error Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 8 C2IE: ECAN2 Event Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 7 C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 6 INT4IE: External Interrupt 4 Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 5 INT3IE: External Interrupt 3 Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 4 **T9IE:** Timer9 Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 3 **T8IE:** Timer8 Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled bit 2 MI2C2IE: I2C2 Master Events Interrupt Enable bit 1 = Interrupt request enabled 0 = Interrupt request not enabled

### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| U-0          | R/W-1                                                                                                                             | R/W-0                                                   | R/W-0          | U-0              | U-0             | U-0             | U-0   |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| _            |                                                                                                                                   | CNIP<2:0>                                               |                | —                |                 | —               |       |  |  |  |

| bit 15       |                                                                                                                                   |                                                         |                |                  |                 |                 | bit 8 |  |  |  |

|              |                                                                                                                                   |                                                         |                |                  |                 |                 |       |  |  |  |

| U-0          | R/W-1                                                                                                                             | R/W-0                                                   | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |

|              |                                                                                                                                   | MI2C1IP<2:0>                                            |                |                  |                 | SI2C1IP<2:0>    |       |  |  |  |

| bit 7        |                                                                                                                                   |                                                         |                |                  |                 |                 | bit ( |  |  |  |

| Legend:      |                                                                                                                                   |                                                         |                |                  |                 |                 |       |  |  |  |

| R = Readab   | le bit                                                                                                                            | W = Writable                                            | bit            | U = Unimplei     | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value a | t POR                                                                                                                             | '1' = Bit is set                                        |                | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |

|              |                                                                                                                                   |                                                         |                |                  |                 |                 |       |  |  |  |

| bit 15       | -                                                                                                                                 | nented: Read as 'o                                      |                |                  |                 |                 |       |  |  |  |

| bit 14-12    | <b>CNIP&lt;2:0&gt;:</b> Change Notification Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                         |                |                  |                 |                 |       |  |  |  |

|              | 111 = Inte                                                                                                                        | errupt is priority 7 (I                                 | highest priori | ty interrupt)    |                 |                 |       |  |  |  |

|              |                                                                                                                                   |                                                         |                |                  |                 |                 |       |  |  |  |

|              | •                                                                                                                                 |                                                         |                |                  |                 |                 |       |  |  |  |

|              |                                                                                                                                   | errupt is priority 1                                    |                |                  |                 |                 |       |  |  |  |

|              | 000 = Inte                                                                                                                        | errupt source is dis                                    | abled          |                  |                 |                 |       |  |  |  |

| bit 11-7     | Unimplem                                                                                                                          | nented: Read as 'o                                      | כ'             |                  |                 |                 |       |  |  |  |

| bit 6-4      | MI2C1IP<2:0>: I2C1 Master Events Interrupt Priority bits                                                                          |                                                         |                |                  |                 |                 |       |  |  |  |

|              | 111 = Inte                                                                                                                        | errupt is priority 7 (I                                 | highest priori | ty interrupt)    |                 |                 |       |  |  |  |

|              | •                                                                                                                                 |                                                         |                |                  |                 |                 |       |  |  |  |

|              | •                                                                                                                                 |                                                         |                |                  |                 |                 |       |  |  |  |

|              | 001 = Inte                                                                                                                        | errupt is priority 1                                    |                |                  |                 |                 |       |  |  |  |

|              |                                                                                                                                   | errupt source is dis                                    | abled          |                  |                 |                 |       |  |  |  |

| bit 3        | Unimplem                                                                                                                          | Unimplemented: Read as '0'                              |                |                  |                 |                 |       |  |  |  |

| bit 2-0      | SI2C1IP<                                                                                                                          | SI2C1IP<2:0>: I2C1 Slave Events Interrupt Priority bits |                |                  |                 |                 |       |  |  |  |

|              | 111 = Inte                                                                                                                        | errupt is priority 7 (I                                 | highest priori | ty interrupt)    |                 |                 |       |  |  |  |

|              | •                                                                                                                                 |                                                         |                |                  |                 |                 |       |  |  |  |

|              | •                                                                                                                                 |                                                         |                |                  |                 |                 |       |  |  |  |

|              | -<br>001 - Inte                                                                                                                   |                                                         |                |                  |                 |                 |       |  |  |  |

|              |                                                                                                                                   | errupt is priority 1                                    |                |                  |                 |                 |       |  |  |  |

### REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0          | U-0                                                        | U-0                                                                                                                        | U-0   | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|------------------|-----------------|-----------------|-------|--|--|--|--|

| _            |                                                            | _                                                                                                                          | _     | _                |                 | U2EIP<2:0>      |       |  |  |  |  |

| bit 15       |                                                            |                                                                                                                            |       |                  | •               |                 | bit   |  |  |  |  |

|              |                                                            |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                                                                                                      | R/W-0 | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

| —            |                                                            | U1EIP<2:0>                                                                                                                 |       | —                |                 | FLTBIP<2:0>     |       |  |  |  |  |

| bit 7        |                                                            |                                                                                                                            |       |                  |                 |                 | bit   |  |  |  |  |

| Legend:      |                                                            |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                     | W = Writable                                                                                                               | bit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set                                                                                                           |       | '0' = Bit is cle | eared           | x = Bit is unkn | own   |  |  |  |  |

|              |                                                            |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

| bit 15-11    | -                                                          | nted: Read as '                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

| bit 10-8     |                                                            | <b>U2EIP&lt;2:0&gt;:</b> UART2 Error Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |       |                  |                 |                 |       |  |  |  |  |

|              | 111 = Interru                                              | <ul> <li>Interrupt is priority / (nignest priority interrupt)</li> </ul>                                                   |       |                  |                 |                 |       |  |  |  |  |

|              |                                                            |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                          |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              |                                                            | pt is priority 1<br>pt source is dis                                                                                       | abled |                  |                 |                 |       |  |  |  |  |

| bit 7        | Unimplemer                                                 | nted: Read as '                                                                                                            | )'    |                  |                 |                 |       |  |  |  |  |

| bit 6-4      | U1EIP<2:0>: UART1 Error Interrupt Priority bits            |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                          |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                          |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                         |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              |                                                            | pt source is dis                                                                                                           | abled |                  |                 |                 |       |  |  |  |  |

| bit 3        | Unimplemer                                                 | Unimplemented: Read as '0'                                                                                                 |       |                  |                 |                 |       |  |  |  |  |

| bit 2-0      | FLTBIP<2:0>                                                | FLTBIP<2:0>: PWM Fault B Interrupt Priority bits                                                                           |       |                  |                 |                 |       |  |  |  |  |

|              | 111 = Interru                                              | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                 |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                          |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                          |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | •                                                          |                                                                                                                            |       |                  |                 |                 |       |  |  |  |  |

|              | 001 = Interru                                              | pt is priority 1                                                                                                           |       |                  |                 |                 |       |  |  |  |  |

### REGISTER 7-31: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

### REGISTER 8-8: DMACS1: DMA CONTROLLER STATUS REGISTER 1

| U-0                     | U-0                                                                                                                                                                  | U-0                                                                                                                                                                                                         | U-0                                                                                                   | R-1                                    | R-1              | R-1             | R-1   |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|-----------------|-------|--|--|--|--|--|

| _                       | —                                                                                                                                                                    | —                                                                                                                                                                                                           | -                                                                                                     |                                        | LSTCI            | 1<3:0>          |       |  |  |  |  |  |

| bit 15                  |                                                                                                                                                                      |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 | bit 8 |  |  |  |  |  |

|                         |                                                                                                                                                                      |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

| R-0                     | R-0                                                                                                                                                                  | R-0                                                                                                                                                                                                         | R-0                                                                                                   | R-0                                    | R-0              | R-0             | R-0   |  |  |  |  |  |

| PPST7                   | PPST6                                                                                                                                                                | PPST5                                                                                                                                                                                                       | PPST4                                                                                                 | PPST3                                  | PPST2            | PPST1           | PPST0 |  |  |  |  |  |

| bit 7                   |                                                                                                                                                                      |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 | bit 0 |  |  |  |  |  |

| Logondi                 |                                                                                                                                                                      |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

| Legend:<br>R = Readable | a hit                                                                                                                                                                | W = Writable                                                                                                                                                                                                | bit                                                                                                   |                                        | onted hit read   |                 |       |  |  |  |  |  |

| -n = Value at           |                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                            |                                                                                                       | '0' = Bit is clea                      | nented bit, read | x = Bit is unkr |       |  |  |  |  |  |

|                         | FUK                                                                                                                                                                  | I - DILIS SEL                                                                                                                                                                                               |                                                                                                       |                                        | areu             | X - DILISUIKI   | IOWII |  |  |  |  |  |

| bit 15-12               | Unimplemen                                                                                                                                                           | ted: Read as '                                                                                                                                                                                              | ı'                                                                                                    |                                        |                  |                 |       |  |  |  |  |  |

| bit 11-8                | -                                                                                                                                                                    | : Last DMA Ch                                                                                                                                                                                               |                                                                                                       | nits                                   |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | MA transfer has                                                                                                                                                                                             |                                                                                                       |                                        | et               |                 |       |  |  |  |  |  |

|                         | 1110-1000 =                                                                                                                                                          | Reserved                                                                                                                                                                                                    |                                                                                                       | -                                      |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | data transfer wa                                                                                                                                                                                            |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | 0110 = Last data transfer was by DMA Channel 6                                                                                                                                                              |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         | 0101 = Last data transfer was by DMA Channel 5<br>0100 = Last data transfer was by DMA Channel 4                                                                     |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         | 0011 = Last data transfer was by DMA Channel 3                                                                                                                       |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         | 0010 = Last data transfer was by DMA Channel 2<br>0001 = Last data transfer was by DMA Channel 1                                                                     |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

| bit 7                   | 0000 = Last data transfer was by DMA Channel 0<br>PPST7: Channel 7 Ping-Pong Mode Status Flag bit                                                                    |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | B register selec                                                                                                                                                                                            | -                                                                                                     | o 1 10g 210                            |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | A register selec                                                                                                                                                                                            |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

| bit 6                   | PPST6: Char                                                                                                                                                          | nnel 6 Ping-Por                                                                                                                                                                                             | ig Mode Statu                                                                                         | s Flag bit                             |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | B register selec<br>A register selec                                                                                                                                                                        |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

| bit 5                   | PPST5: Char                                                                                                                                                          | nnel 5 Ping-Por                                                                                                                                                                                             | ig Mode Statu                                                                                         | s Flag bit                             |                  |                 |       |  |  |  |  |  |

|                         | 1 = DMA5STB register selected                                                                                                                                        |                                                                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | A register selec                                                                                                                                                                                            |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

| bit 4                   |                                                                                                                                                                      | PPST4: Channel 4 Ping-Pong Mode Status Flag bit                                                                                                                                                             |                                                                                                       |                                        |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | -                                                                                                                                                                                                           | -                                                                                                     | s Flag bit                             |                  |                 |       |  |  |  |  |  |

|                         |                                                                                                                                                                      | B register select<br>A register select                                                                                                                                                                      | ted                                                                                                   | s Flag bit                             |                  |                 |       |  |  |  |  |  |

| bit 3                   | 0 = DMA4ST                                                                                                                                                           | B register selec                                                                                                                                                                                            | ted                                                                                                   | -                                      |                  |                 |       |  |  |  |  |  |

| bit 3                   | 0 = DMA4ST<br><b>PPST3:</b> Char<br>1 = DMA3ST                                                                                                                       | B register select<br>A register select                                                                                                                                                                      | eted<br>ted<br>ig Mode Statu<br>ited                                                                  | -                                      |                  |                 |       |  |  |  |  |  |

| bit 3<br>bit 2          | 0 = DMA4ST,<br><b>PPST3:</b> Char<br>1 = DMA3ST<br>0 = DMA3ST,                                                                                                       | B register select<br>A register select<br>nnel 3 Ping-Por<br>B register select<br>A register select                                                                                                         | ted<br>ted<br>g Mode Statu<br>ted<br>ted                                                              | s Flag bit                             |                  |                 |       |  |  |  |  |  |

|                         | 0 = DMA4ST<br><b>PPST3:</b> Char<br>1 = DMA3ST<br>0 = DMA3ST<br><b>PPST2:</b> Char<br>1 = DMA2ST                                                                     | B register select<br>A register select<br>annel 3 Ping-Por<br>B register select<br>A register select<br>annel 2 Ping-Por<br>B register select                                                               | ited<br>ted<br>g Mode Statu<br>ted<br>ted<br>g Mode Statu                                             | s Flag bit                             |                  |                 |       |  |  |  |  |  |

| bit 2                   | 0 = DMA4ST,<br><b>PPST3:</b> Char<br>1 = DMA3ST<br>0 = DMA3ST,<br><b>PPST2:</b> Char<br>1 = DMA2ST<br>0 = DMA2ST,                                                    | B register select<br>A register select<br>anel 3 Ping-Por<br>B register select<br>A register select<br>anel 2 Ping-Por<br>B register select<br>A register select                                            | ited<br>ted<br>g Mode Statu<br>ited<br>ted<br>g Mode Statu<br>ited<br>ted                             | s Flag bit<br>s Flag bit               |                  |                 |       |  |  |  |  |  |

|                         | 0 = DMA4ST<br><b>PPST3:</b> Char<br>1 = DMA3ST<br>0 = DMA3ST<br><b>PPST2:</b> Char<br>1 = DMA2ST<br>0 = DMA2ST<br><b>PPST1:</b> Char                                 | B register select<br>A register select<br>annel 3 Ping-Por<br>B register select<br>A register select<br>annel 2 Ping-Por<br>B register select<br>A register select<br>annel 1 Ping-Por                      | eted<br>ted<br>og Mode Statu<br>ted<br>og Mode Statu<br>ted<br>ted<br>og Mode Statu                   | s Flag bit<br>s Flag bit               |                  |                 |       |  |  |  |  |  |

| bit 2                   | 0 = DMA4ST<br><b>PPST3:</b> Char<br>1 = DMA3ST<br>0 = DMA3ST<br><b>PPST2:</b> Char<br>1 = DMA2ST<br>0 = DMA2ST<br><b>PPST1:</b> Char<br>1 = DMA1ST                   | B register select<br>A register select<br>anel 3 Ping-Por<br>B register select<br>A register select<br>anel 2 Ping-Por<br>B register select<br>A register select                                            | eted<br>ted<br>og Mode Statu<br>ted<br>og Mode Statu<br>ted<br>ted<br>og Mode Statu                   | s Flag bit<br>s Flag bit               |                  |                 |       |  |  |  |  |  |

| bit 2                   | 0 = DMA4ST,<br><b>PPST3:</b> Char<br>1 = DMA3ST<br>0 = DMA3ST,<br><b>PPST2:</b> Char<br>1 = DMA2ST<br>0 = DMA2ST,<br><b>PPST1:</b> Char<br>1 = DMA1ST<br>0 = DMA1ST, | B register select<br>A register select<br>annel 3 Ping-Por<br>B register select<br>A register select<br>annel 2 Ping-Por<br>B register select<br>A register select<br>annel 1 Ping-Por<br>B register select | eted<br>ted<br>og Mode Statu<br>ted<br>ted<br>ted<br>ted<br>ted<br>og Mode Statu<br>ted<br>ted<br>ted | s Flag bit<br>s Flag bit<br>s Flag bit |                  |                 |       |  |  |  |  |  |

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit                                                        |

|-------|----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Output Compare 4 module is disabled</li><li>0 = Output Compare 4 module is enabled</li></ul> |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul> |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul> |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                        |

|       | 1 = Output Compare 1 module is disabled                                                                  |

|       | 0 = Output Compare 1 module is enabled                                                                   |

|       |                                                                                                          |

NOTES:

| R/W-0         | R/W-0               | R/W-0                                          | R/W-0           | R/W-0                              | R/W-0                | R/W-0                | R/W-0                |  |  |

|---------------|---------------------|------------------------------------------------|-----------------|------------------------------------|----------------------|----------------------|----------------------|--|--|

| FBOV4H        | FBOV4L              | FBOV3H                                         | FBOV3L          | FBOV2H                             | FBOV2L               | FBOV1H               | FBOV1L               |  |  |

| bit 15        |                     |                                                |                 |                                    |                      |                      | bit 8                |  |  |

|               |                     |                                                |                 |                                    |                      |                      |                      |  |  |

| R/W-0         | U-0                 | U-0                                            | U-0             | R/W-0                              | R/W-0                | R/W-0                | R/W-0                |  |  |

| FLTBM         | —                   | —                                              | —               | FBEN4 <sup>(1)</sup>               | FBEN3 <sup>(1)</sup> | FBEN2 <sup>(1)</sup> | FBEN1 <sup>(1)</sup> |  |  |

| bit 7         |                     |                                                |                 |                                    |                      |                      | bit (                |  |  |

| Legend:       |                     |                                                |                 |                                    |                      |                      |                      |  |  |

| R = Readable  | bit                 | W = Writable                                   | hit             |                                    | nented bit, read     | l as '0'             |                      |  |  |

| -n = Value at |                     | '1' = Bit is set                               |                 | '0' = Bit is clea                  |                      | x = Bit is unkr      | own                  |  |  |

|               |                     |                                                |                 |                                    | arcu                 |                      | lowin                |  |  |

| bit 15-8      | FBOVxH<4:1          | >:FBOVxI <4:                                   | 1>: Fault Inpu  | t B PWM Over                       | ride Value bits      |                      |                      |  |  |

|               |                     |                                                | •               |                                    | ault input even      | t                    |                      |  |  |

|               |                     |                                                |                 |                                    | Fault input eve      |                      |                      |  |  |

| bit 7         | FLTBM: Faul         | t B Mode bit                                   |                 |                                    |                      |                      |                      |  |  |

|               |                     |                                                |                 | Cycle-by-Cycle                     |                      |                      |                      |  |  |

|               |                     | • •                                            |                 | ol pins to the sta                 | ates programm        | ed in FLTBCON        | V<15:8>              |  |  |

| bit 6-4       | •                   | ted: Read as '                                 |                 |                                    |                      |                      |                      |  |  |

| bit 3         |                     | t Input B Enabl                                |                 | . –                                | _                    |                      |                      |  |  |

|               |                     |                                                |                 | by Fault Input<br>lled by Fault In |                      |                      |                      |  |  |

| bit 2         |                     | t Input B Enabl                                |                 |                                    | put D                |                      |                      |  |  |

|               |                     |                                                |                 | by Fault Input                     | B                    |                      |                      |  |  |

|               |                     |                                                |                 | lled by Fault In                   |                      |                      |                      |  |  |

| bit 1         | FBEN2: Fault        | FBEN2: Fault Input B Enable bit <sup>(1)</sup> |                 |                                    |                      |                      |                      |  |  |

|               |                     |                                                |                 | by Fault Input                     |                      |                      |                      |  |  |

|               |                     |                                                |                 | lled by Fault In                   | put B                |                      |                      |  |  |

| bit 0         |                     | t Input B Enabl                                |                 |                                    |                      |                      |                      |  |  |

|               |                     |                                                |                 | by Fault Input<br>lled by Fault In |                      |                      |                      |  |  |

|               | $\alpha = PWW11H/P$ | 21/1/1/11 nin noi                              | r in not contro |                                    |                      |                      |                      |  |  |

### REGISTER 16-10: PxFLTBCON: PWMx FAULT B CONTROL REGISTER

**Note 1:** Fault A pin has priority over Fault B pin, if enabled.

### REGISTER 17-2: DFLTxCON: DIGITAL FILTER x CONTROL REGISTER

|                | U-0                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                       | U-0                                                                                                                                                     | U-0                                                                                                    | R/W-0                                                                 | R/W-0            | R/W-0         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------|---------------|

| —              | —                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                       | —                                                                                                      | IMV<                                                                  | 2:0>             | CEID          |

| bit 15         |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                  | bit 8         |

|                |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                         |                                                                                                        |                                                                       |                  |               |

| R/W-0          |                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                         | U-0                                                                                                    | U-0                                                                   | U-0              | U-0           |

| QEOUT          |                                                                                                                                                                                                                                                                                                   | QECK<2:0>                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                         | —                                                                                                      | —                                                                     | —                | —             |