Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

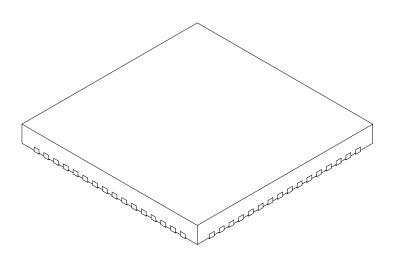

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc510a-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

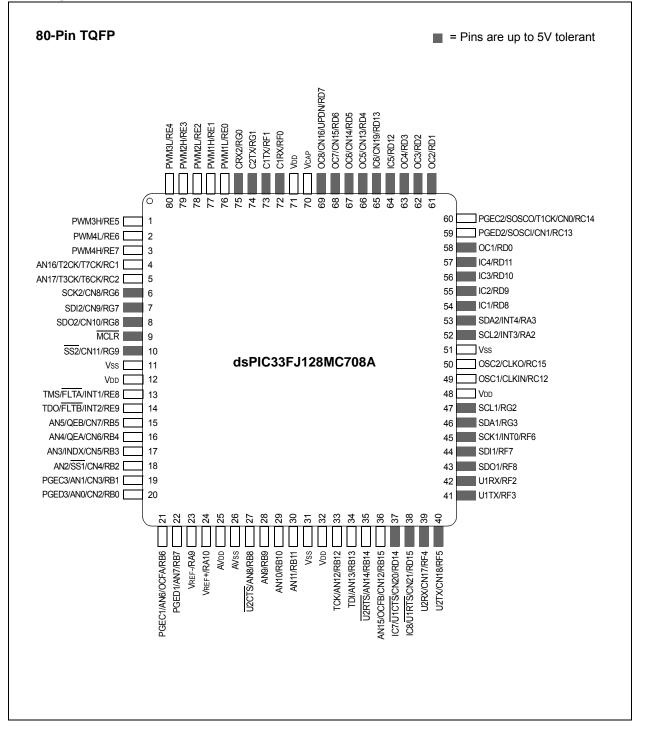

#### **Pin Diagrams (Continued)**

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Pin Name                                                                                                                                                                                    | Pin<br>Type                                                                               | Buffer<br>Type                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RA0-RA7                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RA9-RA10                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RA12-RA15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RB0-RB15                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RC1-RC4                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RC12-RC15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RD0-RD15                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RE0-RE9                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RF0-RF8                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RF12-RF13                                                                                                                                                                                   |                                                                                           |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RG0-RG3                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RG6-RG9                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RG12-RG15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SCK1                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SDI1                                                                                                                                                                                        | 1                                                                                         | ST                                                                                     | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| SDO1                                                                                                                                                                                        | Ō                                                                                         | _                                                                                      | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SS1                                                                                                                                                                                         | I/O                                                                                       | ST                                                                                     | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SCK2                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SDI2                                                                                                                                                                                        | I                                                                                         | ST                                                                                     | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| SDO2                                                                                                                                                                                        | 0                                                                                         | —                                                                                      | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SS2                                                                                                                                                                                         | I/O                                                                                       | ST                                                                                     | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SCL1                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SDA1                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SCL2                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SDA2                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SOSCI                                                                                                                                                                                       | I                                                                                         | ST/CMOS                                                                                | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SOSCO                                                                                                                                                                                       | 0                                                                                         | _                                                                                      | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TMC                                                                                                                                                                                         | I                                                                                         | ST                                                                                     | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                                             |                                                                                           | ST                                                                                     | JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TMS<br>TCK                                                                                                                                                                                  | I                                                                                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TCK<br>TDI                                                                                                                                                                                  | I                                                                                         | ST                                                                                     | JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| TCK<br>TDI                                                                                                                                                                                  | <br> <br>0                                                                                | ST<br>—                                                                                | JTAG test data input pin.<br>JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| TCK<br>TDI<br>TDO                                                                                                                                                                           | <br> <br>0<br>                                                                            | ST<br>—<br>ST                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                                                                                                                                                                                             |                                                                                           | —<br>ST<br>ST                                                                          | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK                                                                                                                                                                   |                                                                                           | ST                                                                                     | JTAG test data output pin.<br>Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK                                                                                                                                           |                                                                                           | —<br>ST<br>ST<br>ST<br>ST                                                              | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                                   |                                                                                           | —<br>ST<br>ST<br>ST<br>ST<br>ST                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK                                                                                                                   |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST                                                     | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK                                                                                                           |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK                                                                                                   |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK                                                                                                   |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS                                                                                  |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.                                                                                                                                                                                             |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS                                                                                 |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.                                                                                                                                                                     |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>J1CTS</u><br>J1RTS<br>J1RTS<br>J1RX                                                 | <br> <br> <br> <br> <br> <br> <br> <br> <br>                                              |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.                                                                                                                                                   |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX                                                |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.                                                                                                                                                  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS                                               | <br>                                    |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.                                                                                                                                |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS                              | <br>                     |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.                                                                                |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RTS<br>U2RX                     | <br>                          |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.                                |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RX<br>U1RX<br>U1RX<br>U1RX<br>U1RX<br>U1RX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                                                                       |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RX<br>U2TX<br>VDD       | <br> |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.<br>Positive supply for peripheral logic and I/O pins. |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1RX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX                       |                                                                                           | <br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br><br>ST<br><br>ST<br><br>ST<br> | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                     |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

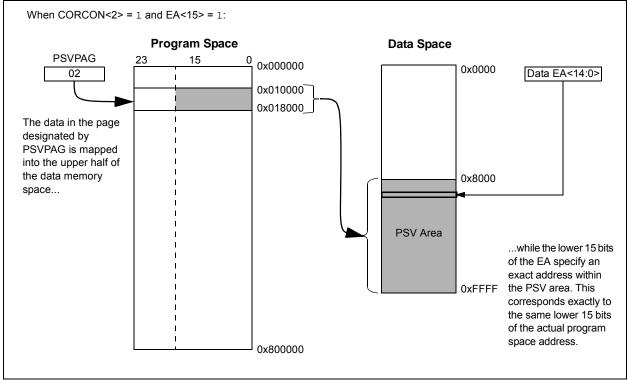

#### 4.6.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-11), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

### Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV and are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data using PSV to execute in a single cycle.

#### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION

© 2009-2012 Microchip Technology Inc.

#### SR: CPU STATUS REGISTER<sup>(1)</sup> **REGISTER 7-1:**

| R-0    | R-0 | R/C-0 | R/C-0 | R-0 | R/C-0 | R-0 | R/W-0 |

|--------|-----|-------|-------|-----|-------|-----|-------|

| OA     | OB  | SA    | SB    | OAB | SAB   | DA  | DC    |

| bit 15 |     |       |       |     |       |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:           |                      |                                    |  |

|-------------------|----------------------|------------------------------------|--|

| C = Clearable bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Settable bit  | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set  | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5

IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU interrupt priority level is 7 (15), user interrupts disabled 110 = CPU interrupt priority level is 6 (14)

101 = CPU interrupt priority level is 5 (13)

100 = CPU interrupt priority level is 4 (12)

- 011 = CPU interrupt priority level is 3 (11)

- 010 = CPU interrupt priority level is 2 (10)

- 001 = CPU interrupt priority level is 1 (9)

- 000 = CPU interrupt priority level is 0 (8)

#### Note 1: For complete register details, see Register 3-1: "SR: CPU STATUS Register".

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### CORCON: CORE CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-2:**

| U-0               | U-0   | U-0             | R/W-0  | R/W-0               | R-0             | R-0              | R-0   |

|-------------------|-------|-----------------|--------|---------------------|-----------------|------------------|-------|

| —                 | —     | —               | US     | EDT                 |                 | DL<2:0>          |       |

| bit 15            |       |                 |        |                     |                 |                  | bit 8 |

|                   |       |                 |        |                     |                 |                  |       |

| R/W-0             | R/W-0 | R/W-1           | R/W-0  | R/C-0               | R/W-0           | R/W-0            | R/W-0 |

| SATA              | SATB  | SATDW           | ACCSAT | IPL3 <sup>(2)</sup> | PSV             | RND              | IF    |

| bit 7             |       |                 |        |                     |                 |                  | bit 0 |

|                   |       |                 |        |                     |                 |                  |       |

| Legend:           |       | C = Clearable   | e bit  |                     |                 |                  |       |

| R = Readable      | bit   | W = Writable    | bit    | -n = Value at       | POR             | '1' = Bit is set |       |

| 0' = Bit is clear | ed    | 'x = Bit is unk | nown   | U = Unimpler        | mented bit, rea | d as '0'         |       |

| -                 |       |                 |        |                     |                 |                  |       |

bit 3

IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU interrupt priority level is greater than 7

0 = CPU interrupt priority level is 7 or less

Note 1: For complete register details, see Register 3-2: "CORCON: CORE Control Register".

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

| R/W-0         | R/W-0                      | R/W-0                                 | R/W-0   | R/W-0            | R/W-0            | R/W-0           | U-0                  |

|---------------|----------------------------|---------------------------------------|---------|------------------|------------------|-----------------|----------------------|

| T5MD          | T4MD                       | T3MD                                  | T2MD    | T1MD             | QEI1MD           | PWMMD           | —                    |

| bit 15        |                            | •                                     | I       |                  |                  |                 | bit 8                |

|               |                            |                                       |         |                  |                  |                 |                      |

| R/W-0         | R/W-0                      | R/W-0                                 | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0                |

| I2C1MD        | U2MD                       | U1MD                                  | SPI2MD  | SPI1MD           | C2MD             | C1MD            | AD1MD <sup>(1)</sup> |

| bit 7         |                            |                                       |         |                  |                  |                 | bit C                |

|               |                            |                                       |         |                  |                  |                 |                      |

| Legend:       |                            |                                       |         |                  |                  |                 |                      |

| R = Readabl   |                            | W = Writable                          | bit     |                  | nented bit, read |                 |                      |

| -n = Value at | POR                        | '1' = Bit is set                      |         | '0' = Bit is cle | ared             | x = Bit is unkr | lown                 |

| L:4 / F       |                            | - Madula Diach                        | I- 1-14 |                  |                  |                 |                      |

| bit 15        |                            | 5 Module Disat<br>odule is disable    |         |                  |                  |                 |                      |

|               |                            | odule is enable                       |         |                  |                  |                 |                      |

| bit 14        |                            | 4 Module Disab                        |         |                  |                  |                 |                      |

|               | 1 = Timer4 m               | odule is disable                      | ed      |                  |                  |                 |                      |

|               | 0 = Timer4 m               | odule is enable                       | d       |                  |                  |                 |                      |

| bit 13        |                            | 3 Module Disab                        |         |                  |                  |                 |                      |

|               |                            | odule is disable                      |         |                  |                  |                 |                      |

| bit 10        |                            | odule is enable<br>2 Module Disat     |         |                  |                  |                 |                      |

| bit 12        | -                          | odule is disable                      |         |                  |                  |                 |                      |

|               | -                          | odule is enable                       |         |                  |                  |                 |                      |

| bit 11        | T1MD: Timer                | 1 Module Disab                        | ole bit |                  |                  |                 |                      |

|               | 1 = Timer1 m               | odule is disable                      | ed      |                  |                  |                 |                      |

|               | 0 = Timer1 m               | odule is enable                       | d       |                  |                  |                 |                      |

| bit 10        |                            | 11 Module Disa                        | ble bit |                  |                  |                 |                      |

|               |                            | dule is disabled<br>dule is enabled   |         |                  |                  |                 |                      |

| bit 9         |                            | /M Module Disa                        | hle hit |                  |                  |                 |                      |

| bit 5         |                            | dule is disabled                      |         |                  |                  |                 |                      |

|               |                            | dule is enabled                       |         |                  |                  |                 |                      |

| bit 8         | Unimplemen                 | ted: Read as '                        | )'      |                  |                  |                 |                      |

| bit 7         | 12C1MD: 12C                | 1 Module Disab                        | ole bit |                  |                  |                 |                      |

|               |                            | lule is disabled                      |         |                  |                  |                 |                      |

|               |                            | lule is enabled                       |         |                  |                  |                 |                      |

| bit 6         |                            | 2 Module Disa                         |         |                  |                  |                 |                      |

|               |                            | nodule is disable<br>nodule is enable |         |                  |                  |                 |                      |

| bit 5         |                            | 1 Module Disa                         |         |                  |                  |                 |                      |

|               | 1 = UART1 m                | nodule is disable                     | ed      |                  |                  |                 |                      |

|               | 0 = UART1 m                | nodule is enable                      | ed      |                  |                  |                 |                      |

| bit 4         | SPI2MD: SPI                | 2 Module Disat                        | ole bit |                  |                  |                 |                      |

|               |                            | lule is disabled                      |         |                  |                  |                 |                      |

|               | $0 = SPI2 \mod 10^{\circ}$ | dule is enabled                       |         |                  |                  |                 |                      |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** The PCFGx bits have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

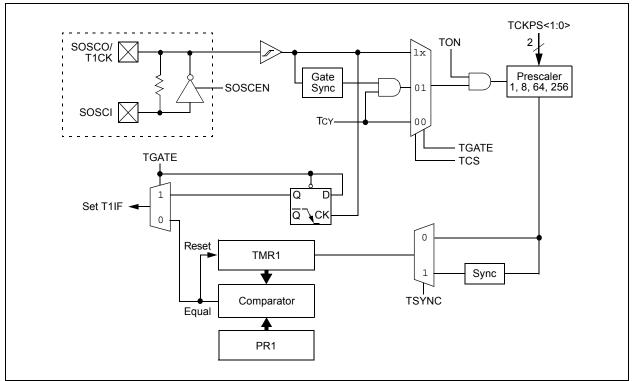

#### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 11. "Timers"** (DS70205) in the *"dsPIC33F/PIC24H Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports the following features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation, do the following:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### REGISTER 21-9: CiCFG1: ECAN™ BAUD RATE CONFIGURATION REGISTER 1

| U-0           | U-0                      | U-0                                                        | U-0        | U-0              | U-0              | U-0             | U-0   |

|---------------|--------------------------|------------------------------------------------------------|------------|------------------|------------------|-----------------|-------|

|               | —                        | _                                                          | —          | —                | —                | —               | —     |

| bit 15        |                          |                                                            |            |                  |                  |                 | bit 8 |

|               |                          |                                                            |            |                  |                  |                 |       |

| R/W-0         | R/W-0                    | R/W-0                                                      | R/W-0      | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| SJV           | V<1:0>                   |                                                            |            | BRF              | P<5:0>           |                 |       |

| bit 7         |                          |                                                            |            |                  |                  |                 | bit 0 |

|               |                          |                                                            |            |                  |                  |                 |       |

| Legend:       |                          |                                                            |            |                  |                  |                 |       |

| R = Readable  | e bit                    | W = Writable                                               | bit        | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at | POR                      | '1' = Bit is set                                           |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               |                          |                                                            |            |                  |                  |                 |       |

| bit 15-8      | Unimplemen               | ted: Read as '                                             | 0'         |                  |                  |                 |       |

| bit 7-6       | <b>SJW&lt;1:0&gt;:</b> S | Synchronization                                            | Jump Width | bits             |                  |                 |       |

|               | 11 = Length i            |                                                            |            |                  |                  |                 |       |

|               | 10 = Length i            |                                                            |            |                  |                  |                 |       |

|               | 01 = Length i            |                                                            |            |                  |                  |                 |       |

|               | 00 = Length i            |                                                            |            |                  |                  |                 |       |

| bit 5-0       |                          | Baud Rate Pres                                             |            |                  |                  |                 |       |

|               |                          | `q = 2 x 64 x 1/l                                          | -CAN       |                  |                  |                 |       |

|               | •                        |                                                            |            |                  |                  |                 |       |

|               | •                        |                                                            |            |                  |                  |                 |       |

|               | •                        | ·                                                          |            |                  |                  |                 |       |

|               |                          | iq = 2 x 3 x 1/F<br>iq = 2 x 2 x 1/F                       |            |                  |                  |                 |       |

|               |                          | $Q = 2 \times 2 \times 1/F$<br>$Q = 2 \times 1 \times 1/F$ |            |                  |                  |                 |       |

|               | 00 0000 - I              |                                                            |            |                  |                  |                 |       |

#### REGISTER 21-10: CiCFG2: ECAN™ BAUD RATE CONFIGURATION REGISTER 2

| U-0             | R/W-x                        | U-0               | U-0               | U-0             | R/W-x           | R/W-x             | R/W-x |

|-----------------|------------------------------|-------------------|-------------------|-----------------|-----------------|-------------------|-------|

|                 | WAKFIL                       | —                 | _                 |                 |                 | SEG2PH<2:0>       |       |

| bit 15          |                              | I                 | ł                 |                 | l               |                   | bit 8 |

|                 |                              |                   |                   |                 |                 |                   |       |

| R/W-x           | R/W-x                        | R/W-x             | R/W-x             | R/W-x           | R/W-x           | R/W-x             | R/W-x |

| SEG2PHTS        | SAM                          |                   | SEG1PH<2:0        | >               |                 | PRSEG<2:0>        |       |

| bit 7           |                              |                   |                   |                 |                 |                   | bit ( |

| Legend:         |                              |                   |                   |                 |                 |                   |       |

| R = Readable    | h:t                          |                   | , bit             |                 | monted bit rea  | ad aa '0'         |       |

| -n = Value at F |                              | W = Writable      |                   | 0 = Onimpler    | mented bit, rea | x = Bit is unkn   | 0.110 |

|                 | UR                           |                   | :L                |                 | areu            |                   | IOWI  |

| bit 15          | Unimplemen                   | ted: Read as      | <b>'</b> 0'       |                 |                 |                   |       |

| bit 14          | -                            |                   | Line Filter for \ | Nake-up bit     |                 |                   |       |

|                 |                              | bus line filter   |                   | ·               |                 |                   |       |

|                 | 0 = CAN bus                  | line filter is no | t used for wak    | e-up            |                 |                   |       |

| bit 13-11       | Unimplemen                   | ted: Read as      | ʻ0'               |                 |                 |                   |       |

| bit 10-8        | SEG2PH<2:0                   | )>: Phase Bu      | ffer Segment 2    | bits            |                 |                   |       |

|                 | 111 = Length                 |                   |                   |                 |                 |                   |       |

|                 | 000 = Length                 |                   |                   |                 |                 |                   |       |

| bit 7           |                              | 0                 | ent 2 Time Sel    | ect bit         |                 |                   |       |

|                 | 1 = Freely pro               |                   | oits or Informat  | tion Processing | ı Time (IPT), v | /hichever is grea | ter   |

| bit 6           |                              | le of the CAN     |                   |                 |                 | 0                 |       |

|                 | •                            |                   | ee times at the   | sample point    |                 |                   |       |