Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 24x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

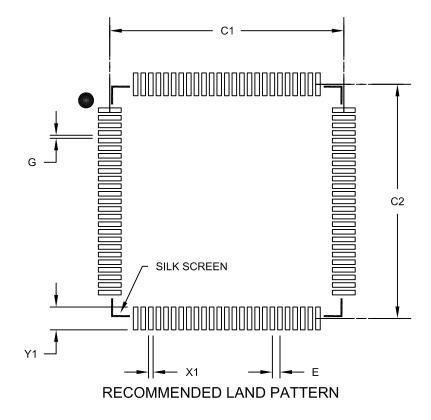

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc510a-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address           | AIVT Address          | Interrupt Source                   |  |  |

|------------------|--------------------------------------|-----------------------|-----------------------|------------------------------------|--|--|

| 54               | 46                                   | 0x000070              | 0x000170              | DMA4 – DMA Channel 4               |  |  |

| 55               | 47                                   | 0x000072              | 0x000172              | T6 – Timer6                        |  |  |

| 56               | 48                                   | 0x000074              | 0x000174              | T7 – Timer7                        |  |  |

| 57               | 49                                   | 0x000076              | 0x000176              | SI2C2 – I2C2 Slave Events          |  |  |

| 58               | 50                                   | 0x000078              | 0x000178              | MI2C2 – I2C2 Master Events         |  |  |

| 59               | 51                                   | 0x00007A              | 0x00017A              | T8 – Timer8                        |  |  |

| 60               | 52                                   | 0x00007C              | 0x00017C              | T9 – Timer9                        |  |  |

| 61               | 53                                   | 0x00007E              | 0x00017E              | INT3 – External Interrupt 3        |  |  |

| 62               | 54                                   | 0x000080              | 0x000180              | INT4 – External Interrupt 4        |  |  |

| 63               | 55                                   | 0x000082              | 0x000182              | C2RX – ECAN2 Receive Data Ready    |  |  |

| 64               | 56                                   | 0x000084              | 0x000184              | C2 – ECAN2 Event                   |  |  |

| 65               | 57                                   | 0x000086              | 0x000186              | PWM – PWM Period Match             |  |  |

| 66               | 58                                   | 0x000088              | 0x000188              | QEI – Position Counter Compare     |  |  |

| 69               | 61                                   | 0x00008E              | 0x00018E              | DMA5 – DMA Channel 5               |  |  |

| 70               | 62                                   | 0x000090              | 0x000190              | Reserved                           |  |  |

| 71               | 63                                   | 0x000092              | 0x000192              | FLTA – MCPWM Fault A               |  |  |

| 72               | 64                                   | 0x000094              | 0x000194              | FLTB – MCPWM Fault B               |  |  |

| 73               | 65                                   | 0x000096              | 0x000196              | U1E – UART1 Error                  |  |  |

| 74               | 66                                   | 0x000098              | 0x000198              | U2E – UART2 Error                  |  |  |

| 75               | 67                                   | 0x00009A              | 0x00019A              | Reserved                           |  |  |

| 76               | 68                                   | 0x00009C              | 0x00019C              | DMA6 – DMA Channel 6               |  |  |

| 77               | 69                                   | 0x00009E              | 0x00019E              | DMA7 – DMA Channel 7               |  |  |

| 78               | 70                                   | 0x0000A0              | 0x0001A0              | C1TX – ECAN1 Transmit Data Request |  |  |

| 79               | 71                                   | 0x0000A2              | 0x0001A2              | C2TX – ECAN2 Transmit Data Request |  |  |

| 80-125           | 72-117                               | 0x0000A4-<br>0x0000FE | 0x0001A4-<br>0x0001FE | Reserved                           |  |  |

### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

#### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x000006    | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x00000C    | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0               | U-0             | U-0                                                                                          | U-0            | U-0              | U-0             | U-0             | U-0    |  |  |  |

|-------------------|-----------------|----------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|--------|--|--|--|

| —                 | —               | _                                                                                            | —              | —                | —               | —               | _      |  |  |  |

| bit 15            |                 |                                                                                              | •              | •                |                 |                 | bit 8  |  |  |  |

|                   |                 |                                                                                              |                |                  |                 |                 |        |  |  |  |

| R/W-0             | R/W-0           | R/W-0                                                                                        | R/W-0          | U-0              | R/W-0           | R/W-0           | R/W-0  |  |  |  |

| C2TXIE            | C1TXIE          | DMA7IE                                                                                       | DMA6IE         | —                | U2EIE           | U1EIE           | FLTBIE |  |  |  |

| bit 7             |                 |                                                                                              |                |                  |                 |                 | bit (  |  |  |  |

| Legend:           |                 |                                                                                              |                |                  |                 |                 |        |  |  |  |

| R = Readab        | le bit          | W = Writable                                                                                 | bit            | U = Unimpler     | mented bit, rea | d as '0'        |        |  |  |  |

| -n = Value a      | t POR           | '1' = Bit is set                                                                             |                | '0' = Bit is cle | ared            | x = Bit is unki | nown   |  |  |  |

| bit 15-8<br>bit 7 | •               | ted: Read as '                                                                               |                | nterrunt Enabl   | e hit           |                 |        |  |  |  |

| bit 7             | C2TXIE: ECA     | N2 Transmit D                                                                                | ata Request li | nterrupt Enable  | e bit           |                 |        |  |  |  |

|                   |                 | request enable<br>request not ena                                                            |                |                  |                 |                 |        |  |  |  |

| bit 6             | C1TXIE: ECA     | N1 Transmit D                                                                                | ata Request I  | nterrupt Enable  | e bit           |                 |        |  |  |  |

|                   |                 | request enable<br>request not ena                                                            |                |                  |                 |                 |        |  |  |  |

| bit 5             | DMA7IE: DM      | A Channel 7 D                                                                                | ata Transfer C | complete Enab    | le Status bit   |                 |        |  |  |  |

|                   |                 | request enable<br>request not ena                                                            |                |                  |                 |                 |        |  |  |  |

| bit 4             | DMA6IE: DM      | DMA6IE: DMA Channel 6 Data Transfer Complete Enable Status bit                               |                |                  |                 |                 |        |  |  |  |

|                   |                 | request enable<br>request not ena                                                            |                |                  |                 |                 |        |  |  |  |

| bit 3             | Unimplemen      | ted: Read as '                                                                               | 0'             |                  |                 |                 |        |  |  |  |

| bit 2             | U2EIE: UART     | Γ2 Error Interru                                                                             | pt Enable bit  |                  |                 |                 |        |  |  |  |

|                   |                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                |                  |                 |                 |        |  |  |  |

| bit 1             | •               | U1EIE: UART1 Error Interrupt Enable bit                                                      |                |                  |                 |                 |        |  |  |  |

|                   | 1 = Interrupt ı | request enable<br>request not ena                                                            | d              |                  |                 |                 |        |  |  |  |

| bit 0             | •               | V Fault B Interr                                                                             |                |                  |                 |                 |        |  |  |  |

| -                 | ו = Interrupt ו | request enable<br>request not ena                                                            | d              |                  |                 |                 |        |  |  |  |

NOTES:

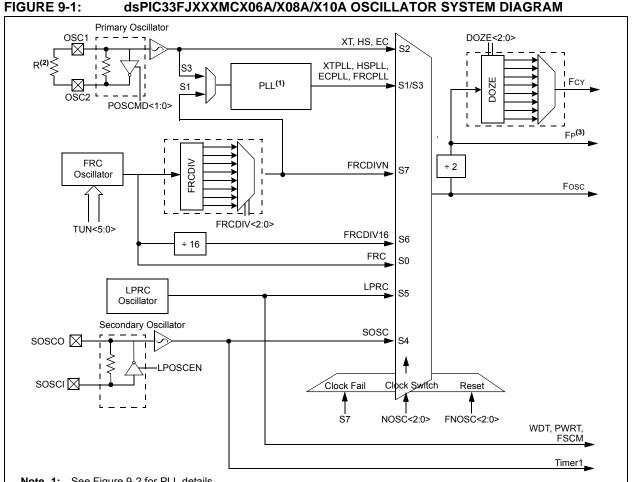

#### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A oscillator system provides the following:

- · Various external and internal oscillator options as clock sources

- · An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- · The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- · Programmable clock postscaler for system power savings

- · A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- A Clock Control register (OSCCON)

- · Nonvolatile Configuration bits for main oscillator selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

Note 1: See Figure 9-2 for PLL details.

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 MΩ must be connected.

- 3: The term, FP refers to the clock source for all the peripherals, while Fcy refers to the clock source for the CPU. Throughout this document FP and FCY are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used in any ratio other than 1:1, which is the default.

## 13.0 TIMER2/3, TIMER4/5, TIMER6/7 AND TIMER8/9

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3, Timer4/5, Timer6/7 and Timer8/9 modules are 32-bit timers that can also be configured as four independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3, Timer4/5, Timer6/7 and Timer8/9 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support the following features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

- ADC2 Event Trigger (Timer4/5 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON, T5CON, T6CON, T7CON, T8CON and T9CON registers. T2CON, T4CON, T6CON and T8CON are shown in generic form in Register 13-1. T3CON, T5CON, T7CON and T9CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2, Timer4, Timer6 or Timer8 is the least significant word; Timer3, Timer5, Timer7 or Timer9 is the most significant word of the 32-bit timers. Note: For 32-bit operation, T3CON, T5CON, T7CON and T9CON control bits are ignored. Only T2CON, T4CON, T6CON and T8CON control bits are used for setup and control. Timer2, Timer4, Timer6 and Timer8 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3, Timer5, Ttimer7 and Timer9 interrupt flags.

To configure Timer2/3, Timer4/5, Timer6/7 or Timer8/9 for 32-bit operation, do the following:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2, Timer4, Timer6 or Timer8 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3, PR5, PR7 or PR9 contains the most significant word of the value, while PR2, PR4, PR6 or PR8 contains the least significant word.

- If interrupts are required, set the interrupt enable bit, T3IE, T5IE, T7IE or T9IE. Use the priority bits, T3IP<2:0>, T5IP<2:0>, T7IP<2:0> or T9IP<2:0>, to set the interrupt priority. While Timer2, Timer4, Timer6 or Timer8 control the timer, the interrupt appears as a Timer3, Timer5, Timer7 or Timer9 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2, TMR5:TMR4, TMR7:TMR6 or TMR9:TMR8. TMR3, TMR5, TMR7 or TMR9 always contain the most significant word of the count, while TMR2, TMR4, TMR6 or TMR8 contain the least significant word.

To configure any of the timers for individual 16-bit operation, do the following:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

A block diagram for a 32-bit timer pair (Timer4/5) example is shown in Figure 13-1, and a timer (Timer4) operating in 16-bit mode example is shown in Figure 13-2.

Note: Only Timer2 and Timer3 can trigger a DMA data transfer.

### REGISTER 17-1: QEIXCON: QEIX CONTROL REGISTER (CONTINUED)

| bit 4-3 | <b>TQCKPS&lt;1:0&gt;:</b> Timer Input Clock Prescale Select bits<br>11 = 1:256 prescale value<br>10 = 1:64 prescale value<br>01 = 1:8 prescale value<br>00 = 1:1 prescale value<br>(Prescaler utilized for 16-Bit Timer mode only.)    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2   | POSRES: Position Counter Reset Enable bit<br>1 = Index pulse resets position counter<br>0 = Index pulse does not reset position counter<br>(Bit only applies when QEIM<2:0> = 100 or 110.)                                             |

| bit 1   | <b>TQCS:</b> Timer Clock Source Select bit<br>1 = External clock from QEA pin (on the rising edge)<br>0 = Internal clock (Tcy)                                                                                                         |

| bit 0   | <pre>UPDN_SRC: Position Counter Direction Selection Control bit<sup>(1)</sup> 1 = QEB pin state defines position counter direction 0 = Control/status bit, UPDN (QEICON&lt;11&gt;), defines Position Counter (POSxCNT) direction</pre> |

Note 1: When configured for QEI mode, the control bit is a 'don't care'.

| R/W-0                        | R/W-0                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                         | U-0                                                                                                                                                                       | U-0                          | U-0              | U-0                | U-0   |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|--------------------|-------|

| FRMEN                        | SPIFSD                                                                                                                                                                                   | FRMPOL                                                                                                                                                                                                                        |                                                                                                                                                                           | _                            |                  |                    | _     |

| bit 15                       |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    | bit 8 |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| U-0                          | U-0                                                                                                                                                                                      | U-0                                                                                                                                                                                                                           | U-0                                                                                                                                                                       | U-0                          | U-0              | R/W-0              | U-0   |

|                              | —                                                                                                                                                                                        | —                                                                                                                                                                                                                             |                                                                                                                                                                           | —                            |                  | FRMDLY             | —     |

| bit 7                        |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    | bit C |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| Legend:                      |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| R = Readable                 | e bit                                                                                                                                                                                    | W = Writable                                                                                                                                                                                                                  | bit                                                                                                                                                                       | U = Unimplen                 | nented bit, read | l as '0'           |       |

| -n = Value at I              | POR                                                                                                                                                                                      | '1' = Bit is set                                                                                                                                                                                                              |                                                                                                                                                                           | '0' = Bit is clea            | ared             | x = Bit is unknown |       |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

|                              |                                                                                                                                                                                          |                                                                                                                                                                                                                               |                                                                                                                                                                           |                              |                  |                    |       |

| bit 15                       |                                                                                                                                                                                          | ned SPIx Supp                                                                                                                                                                                                                 |                                                                                                                                                                           |                              |                  |                    |       |

| bit 15                       | 1 = Framed S                                                                                                                                                                             | Plx support en                                                                                                                                                                                                                | abled (SSx p                                                                                                                                                              | in used as fram              | e Sync pulse ir  | nput/output)       |       |

|                              | 1 = Framed S<br>0 = Framed S                                                                                                                                                             | Plx support en<br>Plx support dis                                                                                                                                                                                             | abled ( <del>SSx</del> p<br>sabled                                                                                                                                        |                              | e Sync pulse ir  | nput/output)       |       |

| bit 15<br>bit 14             | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar                                                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse                                                                                                                                                                            | abled ( <del>SSx</del> p<br>sabled<br>Direction Cor                                                                                                                       |                              | e Sync pulse ir  | nput/output)       |       |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar<br>1 = Frame Sy                                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input                                                                                                                                                          | abled ( <del>SSx</del> p<br>sabled<br>Direction Cor<br>(slave)                                                                                                            |                              | e Sync pulse ir  | nput/output)       |       |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Frar<br>1 = Frame Sy<br>0 = Frame Sy                                                                                                      | Plx support en<br>Plx support dis<br>ne Sync Pulse                                                                                                                                                                            | abled (SSx p<br>sabled<br>Direction Coi<br>(slave)<br>tt (master)                                                                                                         |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra                                                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu                                                                                                                                        | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit                                                                                       |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy                                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls                                                                                                                       | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high                                                                           |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy                                                              | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act                                                                                                    | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low                                                                |                              | e Sync pulse ir  | nput/output)       |       |

| bit 14<br>bit 13             | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen                                                | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act                                                                                 | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>it (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'                                                          | ntrol bit                    | e Sync pulse ir  | nput/output)       |       |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>0 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy                                | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br>ted: Read as '<br>me Sync Pulse<br>nc pulse coinci                           | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first                      | trol bit<br>bit<br>bit clock | e Sync pulse ir  | nput/output)       |       |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame Sy<br>0 = Frame Sy<br>FRMPOL: Fra<br>1 = Frame Sy<br>0 = Frame Sy<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame Sy<br>0 = Frame Sy | Plx support en<br>Plx support dis<br>ne Sync Pulse<br>nc pulse input<br>nc pulse outpu<br>ame Sync Puls<br>nc pulse is act<br>nc pulse is act<br><b>ted:</b> Read as 'u<br>me Sync Pulse<br>nc pulse coinci<br>nc pulse prece | abled (SSx p<br>sabled<br>Direction Cor<br>(slave)<br>It (master)<br>e Polarity bit<br>ive-high<br>ive-low<br>0'<br>e Edge Select<br>ides with first<br>cdes first bit cl | trol bit<br>bit<br>bit clock |                  | nput/output)       |       |

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

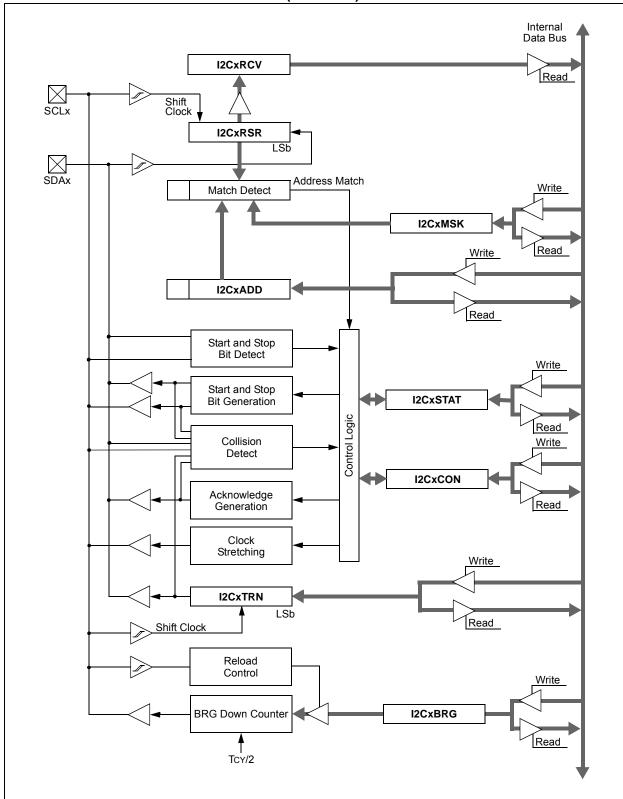

FIGURE 19-1:  $I^2C^{TM}$  BLOCK DIAGRAM (X = 1 OR 2)

## 22.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices have up to 32 ADC input channels. These devices also have up to 2 ADC modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 22.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported.

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device.

A block diagram of the ADC is shown in Figure 22-1.

## 22.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>)

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>)

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>)

- g) Turn on ADC module (ADxCON1<15>)

- 2. Configure ADC interrupt (if required):

- a) Clear the ADxIF bit

- b) Select ADC interrupt priority

### 22.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM Buffer Pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

| R/W-0           | U-0                                                                                                                                                | R/W-0                                                                                         | R/W-0                                                  | U-0                                                                | R/W-0                                                | R/W-0           | R/W-0            |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|-----------------|------------------|--|--|

| ADON            | —                                                                                                                                                  | ADSIDL                                                                                        | ADDMABM                                                | —                                                                  | AD12B                                                | FORM            | <1:0>            |  |  |

| bit 15          |                                                                                                                                                    |                                                                                               |                                                        |                                                                    |                                                      |                 | bit 8            |  |  |

| <b>D</b> 11/ A  | 5444                                                                                                                                               | <b>D</b> # 44 A                                                                               |                                                        |                                                                    | 5444.0                                               |                 |                  |  |  |

| R/W-0           | R/W-0                                                                                                                                              | R/W-0                                                                                         | U-0                                                    | R/W-0                                                              | R/W-0                                                | R/W-0,<br>HC,HS | R/C-0,<br>HC, HS |  |  |

|                 | SSRC<2:0>                                                                                                                                          |                                                                                               | —                                                      | SIMSAM                                                             | ASAM                                                 | SAMP            | DONE             |  |  |

| bit 7           |                                                                                                                                                    |                                                                                               |                                                        |                                                                    |                                                      |                 | bit C            |  |  |

| Legend:         |                                                                                                                                                    | HC = Hardware                                                                                 | Clearable bit                                          | HS = Hardwa                                                        | are Settable bit                                     | C= Clea         | rable bit        |  |  |

| R = Readable    | bit                                                                                                                                                | W = Writable b                                                                                |                                                        |                                                                    | mented bit, read                                     |                 |                  |  |  |

| -n = Value at l |                                                                                                                                                    | '1' = Bit is set                                                                              |                                                        | '0' = Bit is cle                                                   |                                                      | x = Bit is unk  | nown             |  |  |

|                 |                                                                                                                                                    |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

| bit 15          | ADON: ADC                                                                                                                                          | Operating Mode                                                                                | e bit                                                  |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    | dule is operating                                                                             | )                                                      |                                                                    |                                                      |                 |                  |  |  |

|                 | 0 = ADC is o                                                                                                                                       |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

| bit 14          | -                                                                                                                                                  | ted: Read as '0                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

| bit 13          |                                                                                                                                                    | o in Idle Mode b                                                                              |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    | •                                                                                             | ration when dev<br>on in Idle mode                     |                                                                    | mode                                                 |                 |                  |  |  |

| bit 12          |                                                                                                                                                    | •                                                                                             |                                                        |                                                                    |                                                      |                 |                  |  |  |

| SIT 12          | <b>ADDMABM:</b> DMA Buffer Build Mode bit<br>1 = DMA buffers are written in the order of conversion. The module will provide an address to the DMA |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    |                                                                                               | as the address                                         |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    |                                                                                               | n Scatter/Gathe                                        |                                                                    |                                                      |                 |                  |  |  |

| bit 11          |                                                                                                                                                    |                                                                                               | ed on the index                                        | of the analog                                                      | input and the s                                      |                 | Duffer           |  |  |

| bit 10          | -                                                                                                                                                  | ted: Read as '0                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    | it or 12-Bit Ope<br>channel ADC o                                                             |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    | channel ADC o                                                                                 |                                                        |                                                                    |                                                      |                 |                  |  |  |

| bit 9-8         |                                                                                                                                                    | Data Output Fo                                                                                |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 | For 10-Bit Op                                                                                                                                      | -                                                                                             |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    |                                                                                               | = sddd dddd                                            |                                                                    | where s = .NO                                        | ſ.d<9>)         |                  |  |  |

|                 | 10 = Fractional (Dout = dddd  dddd  dd00  0000)<br>01 = Signed integer (Dout = ssss  sssd  dddd  dddd, where s = .NOT.d<9>)                        |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    |                                                                                               |                                                        |                                                                    |                                                      | ,               |                  |  |  |

|                 | 00 = Integer (Dout = 0000_00dd_dddd_dddd)<br>For 12-Bit Operation:                                                                                 |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 | 11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)                                                                          |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 | 10 = Fractional (Dout = dddd  dddd  dddd  0000)<br>01 = Signed Integer (Dout = ssss  sddd  dddd  dddd, where s = .NOT.d<11>)                       |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

|                 |                                                                                                                                                    |                                                                                               | lddd dddd dd                                           |                                                                    |                                                      | (11)            |                  |  |  |

|                 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                         |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

| bit 7-5         | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                          |                                                                                               |                                                        |                                                                    |                                                      |                 |                  |  |  |

| bit 7-5         |                                                                                                                                                    |                                                                                               | sampling and st                                        | arts conversion                                                    |                                                      | )               |                  |  |  |

| bit 7-5         | 110 = Reserv                                                                                                                                       | ved                                                                                           | sampling and st                                        | arts conversio                                                     |                                                      | )               |                  |  |  |

| bit 7-5         | 110 = Reserv<br>101 = Reserv                                                                                                                       | ved<br>ved                                                                                    |                                                        |                                                                    | -                                                    |                 | conversion       |  |  |

| bit 7-5         | 110 = Reserv<br>101 = Reserv<br>100 = GP tim<br>011 = MPWM                                                                                         | ved<br>ved<br>ner (Timer5 for A<br>A interval ends s                                          | ADC1, Timer3 fo<br>sampling and sta                    | r ADC2) comp<br>arts conversior                                    | are ends samp                                        | ling and starts |                  |  |  |

| bit 7-5         | 110 = Reserv<br>101 = Reserv<br>100 = GP tim<br>011 = MPWM<br>010 = GP tim                                                                         | ved<br>ved<br>her (Timer5 for A<br>A interval ends s<br>her (Timer3 for A                     | ADC1, Timer3 fo<br>sampling and sta<br>ADC1, Timer5 fo | r ADC2) comp<br>arts conversior<br>r ADC2) comp                    | are ends samp<br>n<br>are ends samp                  | ling and starts |                  |  |  |

| bit 7-5         | 110 = Reserv<br>101 = Reserv<br>100 = GP tim<br>011 = MPWM<br>010 = GP tim<br>001 = Active                                                         | ved<br>ved<br>her (Timer5 for A<br>A interval ends s<br>her (Timer3 for A<br>transition on IN | ADC1, Timer3 fo<br>sampling and sta                    | r ADC2) comp<br>arts conversior<br>r ADC2) comp<br>npling and star | are ends samp<br>n<br>are ends samp<br>ts conversion | ling and starts |                  |  |  |

### **REGISTER 22-1:** ADxCON1: ADCx CONTROL REGISTER 1 (where x = 1 or 2)

#### **REGISTER 22-2:** ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED) (where x = 1 or 2)

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses channel input selects for Sample A on first sample and Sample B on next sample

- 0 = Always uses channel input selects for Sample A

#### TABLE 24-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Wm*Wm                                                                                                                                                                                                                                                                            | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                             |  |  |

| Wm*Wn                                                                                                                                                                                                                                                                            | Multiplicand and Multiplier working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                            |  |  |

| Wn                                                                                                                                                                                                                                                                               | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                     |  |  |

| Wnd                                                                                                                                                                                                                                                                              | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                         |  |  |

| Wns                                                                                                                                                                                                                                                                              | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                              |  |  |

| WREG                                                                                                                                                                                                                                                                             | W0 (working register used in file register instructions)                                                                                                                                                                                  |  |  |

| Ws                                                                                                                                                                                                                                                                               | Source W register ∈ {Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws]}                                                                                                                                                                                |  |  |

| Wso Source W register ∈<br>{Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb]}                                                                                                                                                                                                |                                                                                                                                                                                                                                           |  |  |

| Wx                                                                                                                                                                                                                                                                               | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8]+ = 6, [W8]+ = 4, [W8]+ = 2, [W8], [W8]- = 6, [W8]- = 4, [W8]- = 2,<br>[W9]+ = 6, [W9]+ = 4, [W9]+ = 2, [W9], [W9]- = 6, [W9]- = 4, [W9]- = 2,<br>[W9 + W12], none} |  |  |

| Wxd                                                                                                                                                                                                                                                                              | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                  |  |  |

| Wy         Y Data Space Prefetch Address register for DSP instructions           € {[W10]+ = 6, [W10]+ = 4, [W10]+ = 2, [W10], [W10]- = 6, [W10]- = 4, [W10]-           [W11]+ = 6, [W11]+ = 4, [W11]+ = 2, [W11], [W11]- = 6, [W11]- = 4, [W11]- =           [W11 + W12], none} |                                                                                                                                                                                                                                           |  |  |

| Wyd                                                                                                                                                                                                                                                                              | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                  |  |  |

| DC CHARACTERISTICS |                       |                                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                |

|--------------------|-----------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|----------------|

| Param<br>No.       | Symbol Characteristic |                                                                             | Min                                                                                                                                                                                                                                                                                 | Тур <sup>(1)</sup> | Max | Units | Conditions     |

| Operati            | ng Voltage            | 9                                                                           |                                                                                                                                                                                                                                                                                     |                    |     |       |                |

| DC10               | Supply V              | oltage                                                                      |                                                                                                                                                                                                                                                                                     |                    |     |       |                |

|                    | Vdd                   | —                                                                           | 3.0                                                                                                                                                                                                                                                                                 |                    | 3.6 | V     | —              |

| DC12               | Vdr                   | RAM Data Retention Voltage <sup>(2)</sup>                                   | 1.8                                                                                                                                                                                                                                                                                 | _                  | _   | V     | —              |

| DC16               | VPOR                  | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal            |                                                                                                                                                                                                                                                                                     | _                  | Vss | V     | _              |

| DC17               | SVDD                  | <b>V</b> DD <b>Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.03                                                                                                                                                                                                                                                                                | _                  | _   | V/ms  | 0-3.0V in 0.1s |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: This is the limit to which VDD can be lowered without losing RAM data.

| AC CHARACTERISTICS |               |                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |                 |                   |                           |  |

|--------------------|---------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------|-------------------|---------------------------|--|