Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                              |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 40 MIPs                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                 |

| Number of I/O              | 85                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 8K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 24x10/12b                                                                      |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TQFP                                                                           |

| Supplier Device Package    | 100-TQFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc510at-i-pf |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

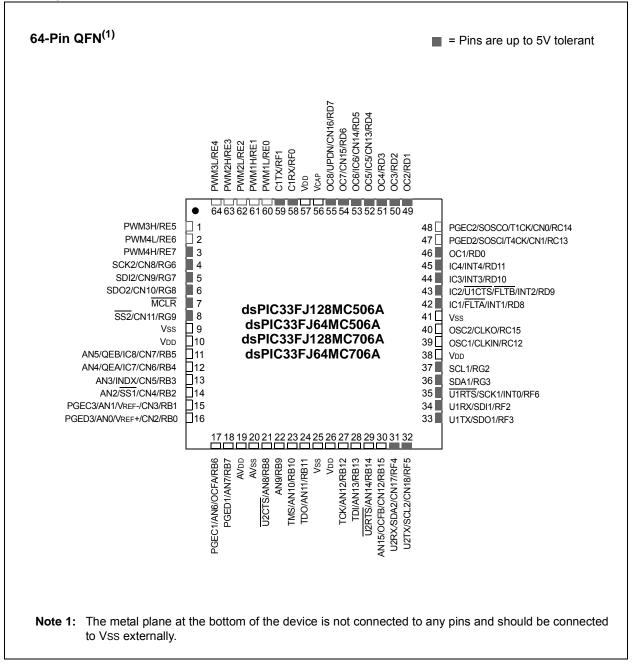

#### Pin Diagrams

| Pin Name                                                                                                                                                                                | Pin<br>Type                                                                               | Buffer<br>Type                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0-RA7                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RA9-RA10                                                                                                                                                                                | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RA12-RA15                                                                                                                                                                               | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RB0-RB15                                                                                                                                                                                | I/O                                                                                       | ST                                                                                     | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RC1-RC4                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RC12-RC15                                                                                                                                                                               | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RD0-RD15                                                                                                                                                                                | I/O                                                                                       | ST                                                                                     | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RE0-RE9                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RF0-RF8                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RF12-RF13                                                                                                                                                                               |                                                                                           |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RG0-RG3                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RG6-RG9                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RG12-RG15                                                                                                                                                                               | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCK1                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDI1                                                                                                                                                                                    | 1                                                                                         | ST                                                                                     | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SDO1                                                                                                                                                                                    | Ō                                                                                         | _                                                                                      | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SS1                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCK2                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDI2                                                                                                                                                                                    | I                                                                                         | ST                                                                                     | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SDO2                                                                                                                                                                                    | 0                                                                                         | —                                                                                      | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SS2                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCL1                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDA1                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCL2                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDA2                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOSCI                                                                                                                                                                                   | I                                                                                         | ST/CMOS                                                                                | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOSCO                                                                                                                                                                                   | 0                                                                                         | _                                                                                      | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TMC                                                                                                                                                                                     | I                                                                                         | ST                                                                                     | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                         |                                                                                           | ST                                                                                     | JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMS<br>TCK                                                                                                                                                                              | I                                                                                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TCK<br>TDI                                                                                                                                                                              | I                                                                                         | ST                                                                                     | JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TCK<br>TDI                                                                                                                                                                              | <br> <br>0                                                                                | ST<br>—                                                                                | JTAG test data input pin.<br>JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TCK<br>TDI<br>TDO                                                                                                                                                                       | <br> <br>0<br>                                                                            | ST<br>—<br>ST                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                         |                                                                                           | —<br>ST<br>ST                                                                          | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK                                                                                                                                                               |                                                                                           | ST                                                                                     | JTAG test data output pin.<br>Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK                                                                                                                                       |                                                                                           | —<br>ST<br>ST<br>ST<br>ST                                                              | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                               |                                                                                           | —<br>ST<br>ST<br>ST<br>ST<br>ST                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK                                                                                                               |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST                                                     | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK                                                                                                       |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK                                                                                               |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK                                                                                       |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS                                                                              |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.                                                                                                                                                                                             |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS                                                                             |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>J1CTS</u><br>J1RTS<br>J1RTS<br>J1RX                                             | <br> <br> <br> <br> <br> <br> <br> <br> <br>                                              |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.                                                                                                                                                   |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX                                            |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.                                                                                                                                                  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS                                           | <br>                                    |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.                                                                                                                                |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS                          | <br>                     |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.                                                                                |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RTS<br>U2RX                 | <br>                          |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.                                |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RX<br>U1RX<br>U1RX<br>U1TX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX             |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                                                                       |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX | <br> |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.<br>Positive supply for peripheral logic and I/O pins. |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RTS<br>U1RX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX          |                                                                                           | <br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br><br>ST<br><br>ST<br><br>ST<br> | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                     |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

## 4.0 MEMORY ORGANIZATION

Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/ X08A/X10A family of devices. However, it is not intended to be a comprereference source. hensive То complement the information in this data sheet, refer to Section 3. Data Memory (DS70202) and Section 4. Program Memory (DS70203) in the □□□□,□which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXMCX06A/X08A/X10A architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 Program Address Space

The program address memory space of the dsPIC33FJXXXMCX06A/X08A/X10A devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 Interfacing Program and Data Memory Spaces.

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFEFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space. Memory usage for the dsPIC33FJXXXMCX06A/X08A/X10A family of devices is shown in Figure 4-1.

| <b>≜</b>                   | dsPIC33FJ64MCXXXA<br>GOTOInstruction<br>Reset Address | dsPIC33FJ128MCXXXA<br>GOTOInstruction<br>Reset Address | dsPIC33FJ256MCXXXA<br>GOTOInstruction<br>Reset Address | 0x000000<br>- 0x000002<br>- 0x000004 |

|----------------------------|-------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------|

|                            | Interrupt Vector Table                                | Interrupt Vector Table                                 | Interrupt Vector Table                                 | 0x000004<br>0x0000FE                 |

|                            | Reserved                                              | Reserved                                               | Reserved                                               | 0x000100                             |

|                            | Alternate Vector Table                                | Alternate Vector Table                                 | Alternate Vector Table                                 | 0x000104<br>0x0001FE                 |

| User Memory Space          | User Program<br>Flash Memory<br>(22K instructions)    | User Program<br>Flash Memory                           | User Program                                           | 0x000200                             |

| ory                        |                                                       | (44K instructions)                                     | (88K instructions)                                     | 0,000,0000                           |

| Mem                        |                                                       |                                                        |                                                        | 0x0157FE                             |

| ser h                      | Unimplemented                                         |                                                        |                                                        | 0x015800                             |

| ٦                          | (Read 'O's)                                           | Unimplemented                                          |                                                        | 0x02ABFE                             |

|                            |                                                       | Unimplemented<br>(Read 'O's)                           | Unimplemented<br>(Read '0's)                           | 0x02AC00                             |

| -                          |                                                       |                                                        |                                                        | 0x7FFFFE<br>0x800000                 |

| σ                          | Reserved                                              | Reserved                                               | Reserved                                               | 0xF7FFE                              |

| Spac                       | Device Configuration<br>Registers                     | Device Configuration<br>Registers                      | Device Configuration<br>Registers                      | 0xF80000                             |

| Configuration Memory Space | Reserved                                              | Reserved                                               | Reserved                                               | 0xF80017<br>0xF80010                 |

| Confiç                     | DEVID (2)                                             | DEVID (2)                                              | DEVID (2)                                              | 0xFEFFFE<br>0xFF0000                 |

FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES

## 5.2 RTSP Operation

The dsPIC33FJXXXMCX06A/X08A/X10A Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory at a time, which consists of eight rows (512 instructions), and to program one row or one word at a time. Table 26-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundaries.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

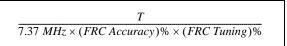

The programming time depends on the FRC accuracy (see Table 26-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the row write time, page erase time and word write cycle time parameters (see Table 26-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `bl11111, the minimum row write time is equal to Equation 5-2.

## EQUATION 5-2: MINIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 1.435 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM ROW WRITE TIME

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.05) \times (1 - 0.00375)} = 1.586 ms$$

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

## 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

- **3:** For dsPIC33FJ256MCX06A/X08A/X10A devices, this bit is unimplemented and reads back a programmed value.

| R/W-0         | R/W-0                                                                                                  | U-0                                                       | R/W-0          | R/W-0                | R/W-0            | R/W-0          | R/W-0                              |  |  |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|----------------------|------------------|----------------|------------------------------------|--|--|--|--|--|--|--|--|--|

| T6IF          | DMA4IF                                                                                                 | _                                                         | OC8IF          | OC7IF                | OC6IF            | OC5IF          | IC6IF                              |  |  |  |  |  |  |  |  |  |

| bit 15        |                                                                                                        |                                                           |                |                      |                  |                | bit 8                              |  |  |  |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                  | R/W-0                                                     | R/W-0          | R/W-0                | R/W-0            | R/W-0          | R/W-0                              |  |  |  |  |  |  |  |  |  |

| IC5IF         | IC4IF                                                                                                  | IC3IF                                                     | DMA3IF         | C1IF                 | C1RXIF           | SPI2IF         | SPI2EIF                            |  |  |  |  |  |  |  |  |  |

| bit 7         |                                                                                                        |                                                           |                |                      | I                |                | bit (                              |  |  |  |  |  |  |  |  |  |

| Legend:       |                                                                                                        |                                                           |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                  | W = Writable                                              | bit            | U = Unimple          | mented bit, read | l as '0'       |                                    |  |  |  |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                    | '1' = Bit is set                                          |                | '0' = Bit is cle     | eared            | x = Bit is unk | nown                               |  |  |  |  |  |  |  |  |  |

| bit 15        | T6IF: Timer6                                                                                           | Interrupt Flag                                            | Status bit     |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                          |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 14        | •                                                                                                      | •                                                         |                | Complete Interi      | rupt Flag Status | bit            |                                    |  |  |  |  |  |  |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                          |                | ·                    |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 13        |                                                                                                        | ted: Read as '                                            |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 12        | OC8IF: Outpu                                                                                           | ut Compare Ch                                             | annel 8 Interr | upt Flag Status      | s bit            |                |                                    |  |  |  |  |  |  |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                          |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 11        | OC7IF: Outpu                                                                                           | ut Compare Ch                                             | annel 7 Interr | upt Flag Status      | s bit            |                |                                    |  |  |  |  |  |  |  |  |  |

|               |                                                                                                        | 1 = Interrupt request has occurred                        |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               | •                                                                                                      | request has no                                            |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 10        | OC6IF: Output Compare Channel 6 Interrupt Flag Status bit                                              |                                                           |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               |                                                                                                        | request has oc<br>request has no                          |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 9         | -                                                                                                      | OC5IF: Output Compare Channel 5 Interrupt Flag Status bit |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                                           |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 8         | •                                                                                                      | Capture Chann                                             |                | -lag Status hit      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit o         | 1 = Interrupt                                                                                          | request has oc<br>request has no                          | curred         | lag Status bit       |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 7         | •                                                                                                      | Capture Chann                                             |                | -lao Status bit      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               | •                                                                                                      | request has oc                                            | •              |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               | 0 = Interrupt request has not occurred                                                                 |                                                           |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 6         | IC4IF: Input Capture Channel 4 Interrupt Flag Status bit                                               |                                                           |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                                           |                |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 5         | -                                                                                                      | Capture Chann                                             |                | -<br>Elaa Status hit |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 5         | 1 = Interrupt                                                                                          | request has oc<br>request has no                          | curred         | ay status bit        |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| bit 4         | •                                                                                                      | •                                                         |                | omnlete Inter        | rupt Flag Status | hit            |                                    |  |  |  |  |  |  |  |  |  |

|               | 1 = Interrupt                                                                                          | request has oc<br>request has no                          | curred         |                      | apting Status    | JA             |                                    |  |  |  |  |  |  |  |  |  |

| bit 3         | -                                                                                                      | l Event Interrup                                          |                | bit                  |                  |                |                                    |  |  |  |  |  |  |  |  |  |

| Sit U         |                                                                                                        | -                                                         | -              |                      |                  |                |                                    |  |  |  |  |  |  |  |  |  |

|               |                                                                                                        | request has no                                            |                |                      |                  |                | 1 = Interrupt request has occurred |  |  |  |  |  |  |  |  |  |

## REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

## REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IE:</b> Input Capture Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled  |

| bit 0 | INTOIE: External Interrupt 0 Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                     |

| REGISTER 7-12: | IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 |

|----------------|-------------------------------------------|

|----------------|-------------------------------------------|

| R/W-0         | R/W-0           | U-0                                                                                          | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|

| T6IE          | DMA4IE          |                                                                                              | OC8IE            | OC7IE            | OC6IE            | OC5IE           | IC6IE   |  |  |  |

| bit 15        |                 | ·                                                                                            |                  |                  |                  |                 | bit 8   |  |  |  |

| R/W-0         | R/W-0           | R/W-0                                                                                        | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| IC5IE         | IC4IE           | IC3IE                                                                                        | DMA3IE           | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |  |  |  |

| bit 7         | 1               |                                                                                              |                  |                  |                  |                 | bit 0   |  |  |  |

| Legend:       |                 |                                                                                              |                  |                  |                  |                 |         |  |  |  |

| R = Readable  | e bit           | W = Writable                                                                                 | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |

| -n = Value at | POR             | '1' = Bit is set                                                                             |                  | '0' = Bit is cle | eared            | x = Bit is unki | nown    |  |  |  |

| bit 15        | T6IF: Timer6    | Interrupt Enabl                                                                              | e bit            |                  |                  |                 |         |  |  |  |

|               |                 | request enabled                                                                              |                  |                  |                  |                 |         |  |  |  |

|               |                 | equest not ena                                                                               |                  |                  |                  |                 |         |  |  |  |

| bit 14        |                 | A Channel 4 D                                                                                |                  | Complete Interi  | rupt Enable bit  |                 |         |  |  |  |

|               |                 | request enableo<br>request not ena                                                           |                  |                  |                  |                 |         |  |  |  |

| bit 13        |                 | ted: Read as '                                                                               |                  |                  |                  |                 |         |  |  |  |

| bit 12        | -               |                                                                                              |                  | unt Enable bit   |                  |                 |         |  |  |  |

| 51(12         | •               | <b>OC8IE:</b> Output Compare Channel 8 Interrupt Enable bit<br>1 = Interrupt request enabled |                  |                  |                  |                 |         |  |  |  |

|               |                 | equest not ena                                                                               |                  |                  |                  |                 |         |  |  |  |

| bit 11        | •               | ut Compare Ch                                                                                |                  | upt Enable bit   |                  |                 |         |  |  |  |

|               |                 | request enabled<br>request not ena                                                           |                  |                  |                  |                 |         |  |  |  |

| bit 10        | •               | ut Compare Ch                                                                                |                  | upt Enable bit   |                  |                 |         |  |  |  |

|               | 1 = Interrupt r | request enabled                                                                              | b                |                  |                  |                 |         |  |  |  |

|               | •               | request not ena                                                                              |                  |                  |                  |                 |         |  |  |  |

| bit 9         | 1 = Interrupt r | ut Compare Ch<br>request enableo<br>request not ena                                          | b                | upt Enable bit   |                  |                 |         |  |  |  |

| bit 8         |                 | Capture Channe                                                                               |                  | Enable bit       |                  |                 |         |  |  |  |