Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

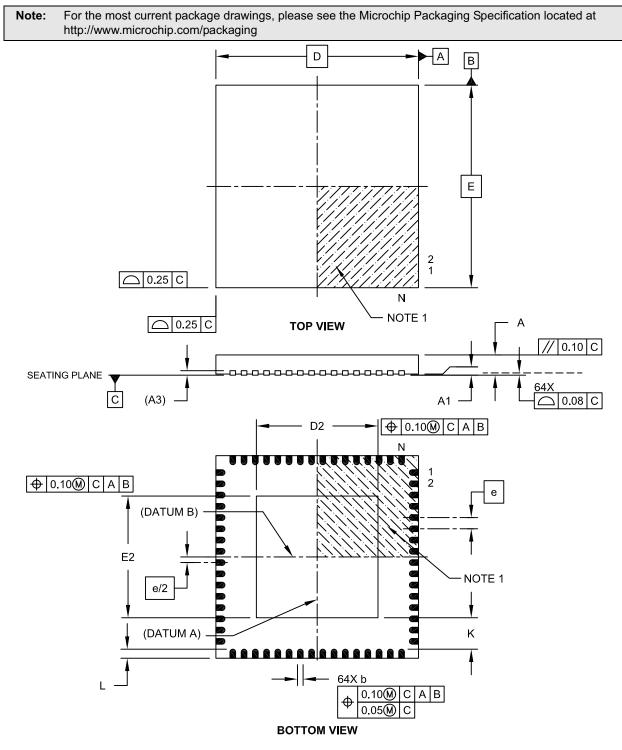

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc706a-e-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

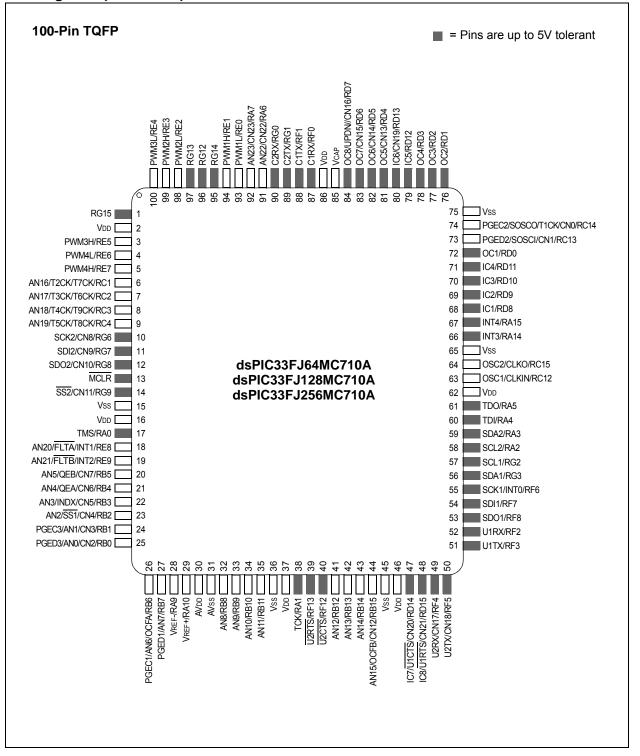

#### **Pin Diagrams (Continued)**

|                                                                                                                                                                                             | PINOUT I/O DESCRIPTIONS (CONTINUED)                                                       |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin Name                                                                                                                                                                                    | Pin<br>Type                                                                               | Buffer<br>Type                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| RA0-RA7                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RA9-RA10                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| RA12-RA15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| RB0-RB15                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RC1-RC4                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RC12-RC15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| RD0-RD15                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RE0-RE9                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RF0-RF8                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RF12-RF13                                                                                                                                                                                   |                                                                                           |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| RG0-RG3                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RG6-RG9                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| RG12-RG15                                                                                                                                                                                   | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| SCK1                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| SDI1                                                                                                                                                                                        | 1                                                                                         | ST                                                                                     | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| SDO1                                                                                                                                                                                        | Ō                                                                                         | _                                                                                      | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| SS1                                                                                                                                                                                         | I/O                                                                                       | ST                                                                                     | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| SCK2                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| SDI2                                                                                                                                                                                        | I                                                                                         | ST                                                                                     | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| SDO2                                                                                                                                                                                        | 0                                                                                         | —                                                                                      | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| SS2                                                                                                                                                                                         | I/O                                                                                       | ST                                                                                     | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| SCL1                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| SDA1                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| SCL2                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| SDA2                                                                                                                                                                                        | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| SOSCI                                                                                                                                                                                       | I                                                                                         | ST/CMOS                                                                                | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| SOSCO                                                                                                                                                                                       | 0                                                                                         | _                                                                                      | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| TMC                                                                                                                                                                                         | I                                                                                         | ST                                                                                     | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                                                                                                                                                                                             |                                                                                           | ST                                                                                     | JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TMS<br>TCK                                                                                                                                                                                  | I                                                                                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| TCK<br>TDI                                                                                                                                                                                  | I                                                                                         | ST                                                                                     | JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| TCK<br>TDI                                                                                                                                                                                  | <br> <br>0                                                                                | ST<br>—                                                                                | JTAG test data input pin.<br>JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO                                                                                                                                                                           | <br> <br>0<br>                                                                            | ST<br>—<br>ST                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                                                                                                                                                                             |                                                                                           | —<br>ST<br>ST                                                                          | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK                                                                                                                                                                   |                                                                                           | ST                                                                                     | JTAG test data output pin.<br>Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK                                                                                                                                           |                                                                                           | —<br>ST<br>ST<br>ST<br>ST                                                              | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                                   |                                                                                           | —<br>ST<br>ST<br>ST<br>ST<br>ST                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK                                                                                                                   |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST                                                     | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK                                                                                                           |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK                                                                                                   |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK                                                                                           |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS                                                                                  |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.                                                                                                                                                                                             |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS                                                                                 |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.                                                                                                                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>J1CTS</u><br>J1RTS<br>J1RTS<br>J1RX                                                 | <br> <br> <br> <br> <br> <br> <br> <br> <br>                                              |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.                                                                                                                                                   |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX                                                |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.                                                                                                                                                  |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS                                       | <br>                                    |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.                                                                                                                                |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS                              | <br>                     |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.                                                                                |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RTS<br>U2RX                     | <br>                          |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.                                |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RX<br>U1RX<br>U1RX<br>U1RX<br>U1RX<br>U1RX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                                                     |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX     | <br> |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.<br>Positive supply for peripheral logic and I/O pins. |  |  |  |  |  |  |  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RTS<br>U1RX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX              |                                                                                           | <br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br><br>ST<br><br>ST<br><br>ST<br> | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                     |  |  |  |  |  |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

NOTES:

# TABLE 4-10: QEI REGISTER MAP

| SFR<br>Name    | Addr | Bit 15 | Bit 14                 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5     | Bit 4 | Bit 3    | Bit 2  | Bit 1 | Bit 0    |        | Reset State | e      |

|----------------|------|--------|------------------------|---------|--------|--------|--------|---------|-------|-------|--------|-----------|-------|----------|--------|-------|----------|--------|-------------|--------|

| <b>QEI1CON</b> | 01E0 | CNTERR | —                      | QEISIDL | INDX   | UPDN   | Q      | EIM<2:0 | )>    | SWPAB | PCDOUT | TQGATE    | TQCKP | S<1:0>   | POSRES | TQCS  | UPDN_SRC | 0000   | 0000 000    | 0 0000 |

| DFLT1CON       | 01E2 | _      | —                      | _       | _      | _      | IMV<   | :1:0>   | CEID  | QEOUT |        | QECK<2:0> |       |          | _      |       | _        | 0000   | 0000 000    | 0 0000 |

| POS1CNT        | 01E4 |        | Position Counter<15:0> |         |        |        |        |         |       |       |        |           | 0000  | 0000 000 | 0 0000 |       |          |        |             |        |

| MAX1CNT        | 01E6 |        | Maximum Count<15:0>    |         |        |        |        |         |       |       |        |           |       |          |        | 1111  | 1111 111 | 1 1111 |             |        |

Legend: u = uninitialized bit, — = unimplemented, read as '0'

#### TABLE 4-11: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                      | Bit 7                 | Bit 6 | Bit 5    | Bit 4      | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|----------------------------|-----------------------|-------|----------|------------|--------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       |        | _       |        |        | _      |        |                            |                       |       |          | I2C1 Recei | ive Register |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | _                          |                       |       |          | I2C1 Trans | mit Register |       |       |       | OOFF          |

| I2C1BRG  | 0204        | —       | _      | _       | -      |        | —      | —      |                            |                       |       | Baud Rat | e Generato | r Register   |       |       |       | 0000          |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                       | GCEN                  | STREN | ACKDT    | ACKEN      | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                      | IWCOL                 | I2COV | D_A      | Р          | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |                            | I2C1 Address Register |       |          |            |              |       | 0000  |       |               |

| I2C1MSK  | 020C        | —       | _      | _       | _      | _      | —      |        | I2C1 Address Mask Register |                       |       |          |            |              |       | 0000  |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                      | Bit 7                  | Bit 6 | Bit 5    | Bit 4      | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|----------------------------|------------------------|-------|----------|------------|------------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        | —       | -      | —       | —      | —      | —      | —      | —                          | I2C2 Receive Register  |       |          |            |            |       |       | 0000  |               |

| I2C2TRN  | 0212        | _       | _      | _       | _      | _      | _      | _      | _                          | I2C2 Transmit Register |       |          |            |            |       |       | OOFF  |               |

| I2C2BRG  | 0214        | _       | _      | _       | _      | _      | _      | _      |                            |                        |       | Baud Rat | e Generato | r Register |       |       |       | 0000          |

| I2C2CON  | 0216        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                       | GCEN                   | STREN | ACKDT    | ACKEN      | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                      | IWCOL                  | I2COV | D_A      | Р          | S          | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        | _       | _      | _       | _      | _      | _      |        |                            | I2C2 Address Register  |       |          |            |            |       |       | 0000  |               |

| I2C2MSK  | 021C        | —       |        |         | —      | -      |        |        | I2C2 Address Mask Register |                        |       |          |            |            |       |       | 0000  |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, <u>one or more of the following conditions</u> is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

## 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

| U-0          | R/W-1                                                                                                                               | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| _            |                                                                                                                                     | T8IP<2:0>                                |                |                   |                 | MI2C2IP<2:0>    |       |  |  |  |  |  |

| bit 15       | ·                                                                                                                                   |                                          |                |                   | •               |                 | bit   |  |  |  |  |  |

|              |                                                                                                                                     |                                          |                |                   |                 |                 |       |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                               | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|              |                                                                                                                                     | SI2C2IP<2:0>                             |                | —                 |                 | T7IP<2:0>       | 1.11  |  |  |  |  |  |

| bit 7        |                                                                                                                                     |                                          |                |                   |                 |                 | bit   |  |  |  |  |  |

| Legend:      |                                                                                                                                     |                                          |                |                   |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                              | W = Writable b                           | oit            | U = Unimple       | mented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                               | '1' = Bit is set                         |                | '0' = Bit is cle  | eared           | x = Bit is unkr | iown  |  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                           | ented: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |  |

| bit 14-12    | -                                                                                                                                   | Timer8 Interrupt                         |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                     | rupt is priority 7 (h                    | -              | ty interrupt)     |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              | 001 = Inter                                                                                                                         | rupt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |  |

|              | 000 = Inter                                                                                                                         | rupt source is disa                      | abled          |                   |                 |                 |       |  |  |  |  |  |

| bit 11       | Unimpleme                                                                                                                           | ented: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |  |

| bit 10-8     | <b>MI2C2IP&lt;2:0&gt;:</b> I2C2 Master Events Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              | 111 = Inter                                                                                                                         | rupt is priority 7 (h                    | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                     | rupt is priority 1                       | ablad          |                   |                 |                 |       |  |  |  |  |  |

| bit 7        |                                                                                                                                     | rupt source is disa<br>ented: Read as '0 |                |                   |                 |                 |       |  |  |  |  |  |

| bit 6-4      | -                                                                                                                                   | :0>: I2C2 Slave E                        |                | unt Priority hite |                 |                 |       |  |  |  |  |  |

| DIL 0-4      |                                                                                                                                     | rupt is priority 7 (h                    |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          | ignoot phon    | ty monapty        |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              | •<br>001 = Inter                                                                                                                    | rupt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                     | rupt source is disa                      | abled          |                   |                 |                 |       |  |  |  |  |  |

| bit 3        | Unimpleme                                                                                                                           | ented: Read as 'o                        | )'             |                   |                 |                 |       |  |  |  |  |  |

| bit 2-0      | T7IP<2:0>:                                                                                                                          | Timer7 Interrupt                         | Priority bits  |                   |                 |                 |       |  |  |  |  |  |

|              | 111 = Inter                                                                                                                         | rupt is priority 7 (h                    | nighest priori | ty interrupt)     |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                                   |                                          |                |                   |                 |                 |       |  |  |  |  |  |

|              | 001 = Inter                                                                                                                         | rupt is priority 1                       |                |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                                     | rupt source is disa                      |                |                   |                 |                 |       |  |  |  |  |  |

## REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

# 9.1 CPU Clocking System

There are seven system clock options provided by the dsPIC33FJXXXMCX06A/X08A/X10A:

- FRC Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- LPRC Oscillator

- FRC Oscillator with Postscaler

## 9.1.1 SYSTEM CLOCK SOURCES

The FRC (Fast RC) internal oscillator runs at a nominal frequency of 7.37 MHz. The user software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> bits (CLKDIV<10:8>).

The primary oscillator can use one of the following as its clock source:

- 1. XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 2. HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 3. EC (External Clock): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC (Low-Power RC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 26-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 23.1 "Configuration Bits**" for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose between twelve different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected), Fosc, is divided by 2 to generate the device instruction clock (FcY) and the peripheral clock time base (FP). FcY defines the operating speed of the device and speeds up to 40 MHz are supported by the dsPIC33FJXXXMCX06A/X08A/X10A architecture.

Instruction execution speed or device operating frequency, FCY, is given by the following equation:

## EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

## 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides a significant amount of flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected to be in the range of 0.8 MHz to 8 MHz. Since the minimum prescale factor is 2, this implies that FIN must be chosen to be in the range of 1.6 MHz to 16 MHz. The prescale factor, 'N1', is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL feedback divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor, 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor, 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

For a primary oscillator or FRC oscillator output, 'FIN', the PLL output, 'FOSC', is given by the following equation:

#### EQUATION 9-2: Fosc CALCULATION

$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$

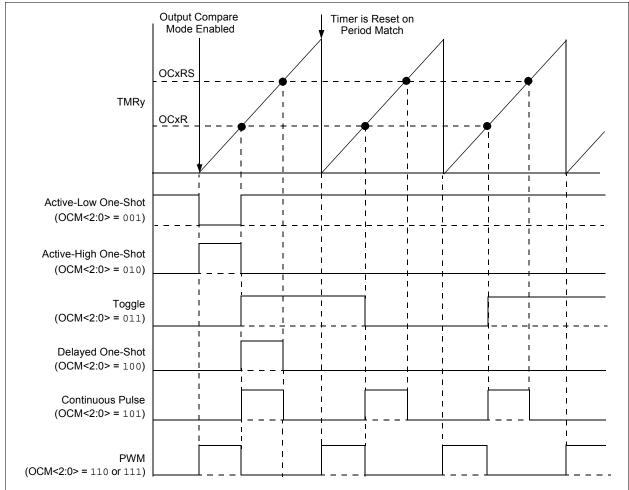

## 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode bits (OCM<2:0>) in the Output Compare Control register (OCxCON<2:0>). Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

| Note: | See Section 13. "Output Compare"      |

|-------|---------------------------------------|

|       | (DS70209) in the "dsPIC33F/PIC24H     |

|       | Family Reference Manual" for OCxR and |

|       | OCxRS register restrictions.          |

| OCM<2:0> | Mode                         | OCx Pin Initial State                                                  | OCx Interrupt Generation         |

|----------|------------------------------|------------------------------------------------------------------------|----------------------------------|

| 000      | Module Disabled              | Controlled by GPIO register                                            | _                                |

| 001      | Active-Low One-Shot          | 0                                                                      | OCx rising edge                  |

| 010      | Active-High One-Shot         | 1                                                                      | OCx falling edge                 |

| 011      | Toggle                       | Current output is maintained                                           | OCx rising and falling edge      |

| 100      | Delayed One-Shot             | 0                                                                      | OCx falling edge                 |