Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc706a-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                                                                                                                | Pin<br>Type                                                                               | Buffer<br>Type                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0-RA7                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RA9-RA10                                                                                                                                                                                | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RA12-RA15                                                                                                                                                                               | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RB0-RB15                                                                                                                                                                                | I/O                                                                                       | ST                                                                                     | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RC1-RC4                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RC12-RC15                                                                                                                                                                               | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RD0-RD15                                                                                                                                                                                | I/O                                                                                       | ST                                                                                     | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RE0-RE9                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RF0-RF8                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RF12-RF13                                                                                                                                                                               |                                                                                           |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RG0-RG3                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RG6-RG9                                                                                                                                                                                 | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RG12-RG15                                                                                                                                                                               | I/O                                                                                       | ST                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCK1                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDI1                                                                                                                                                                                    | 1                                                                                         | ST                                                                                     | SPI1 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SDO1                                                                                                                                                                                    | Ō                                                                                         | _                                                                                      | SPI1 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SS1                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCK2                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for SPI2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDI2                                                                                                                                                                                    | I                                                                                         | ST                                                                                     | SPI2 data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SDO2                                                                                                                                                                                    | 0                                                                                         | —                                                                                      | SPI2 data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SS2                                                                                                                                                                                     | I/O                                                                                       | ST                                                                                     | SPI2 slave synchronization or frame pulse I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCL1                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDA1                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCL2                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial clock input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SDA2                                                                                                                                                                                    | I/O                                                                                       | ST                                                                                     | Synchronous serial data input/output for I2C2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOSCI                                                                                                                                                                                   | I                                                                                         | ST/CMOS                                                                                | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SOSCO                                                                                                                                                                                   | 0                                                                                         | _                                                                                      | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TMC                                                                                                                                                                                     | I                                                                                         | ST                                                                                     | JTAG Test mode select pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                         |                                                                                           | ST                                                                                     | JTAG test clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TMS<br>TCK                                                                                                                                                                              | I                                                                                         |                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TCK<br>TDI                                                                                                                                                                              | I                                                                                         | ST                                                                                     | JTAG test data input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TCK<br>TDI                                                                                                                                                                              | <br> <br>0                                                                                | ST<br>—                                                                                | JTAG test data input pin.<br>JTAG test data output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TCK<br>TDI<br>TDO                                                                                                                                                                       | <br> <br>0<br>                                                                            | ST<br>—<br>ST                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                         |                                                                                           | —<br>ST<br>ST                                                                          | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK                                                                                                                                                               |                                                                                           | ST                                                                                     | JTAG test data output pin.<br>Timer1 external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK                                                                                                                                       |                                                                                           | —<br>ST<br>ST<br>ST<br>ST                                                              | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK                                                                                                                               |                                                                                           | —<br>ST<br>ST<br>ST<br>ST<br>ST                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.                                                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK                                                                                                               |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST                                                     | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.                                                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK                                                                                                       |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK                                                                                               |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK                                                                                       |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.                                                                                                                                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS                                                                              |                                                                                           | U ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST                                               | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.                                                                                                                                                                                             |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS                                                                             |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.                                                                                                                                                                     |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br><u>J1CTS</u><br>J1RTS<br>J1RTS<br>J1RX                                             | <br> <br> <br> <br> <br> <br> <br> <br> <br>                                              |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.                                                                                                                                                   |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX                                            |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 transmit.                                                                                                                                                  |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS                                           | <br>                                    |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.                                                                                                                                |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS                          | <br>                     |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.                                                                                |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RTS<br>U2RX                 | <br>                          |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 ready to send.<br>UART2 ready to send.<br>UART2 receive.                                      |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RX<br>U1RX<br>U1RX<br>U1TX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX             |                                                                                           |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                                                                       |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RTS<br>U1RX<br>U1TX<br>U2CTS<br>U2RTS<br>U2RX<br>U2TX | <br> |                                                                                        | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.<br>Positive supply for peripheral logic and I/O pins. |

| TCK<br>TDI<br>TDO<br>T1CK<br>T2CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK<br>T6CK<br>T7CK<br>T8CK<br>T9CK<br>U1CTS<br>U1RTS<br>U1RTS<br>U1RTS<br>U1RX<br>U2CTS<br>U2RX<br>U2RX<br>U2TX          |                                                                                           | <br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST<br><br>ST<br><br>ST<br><br>ST<br><br>ST<br> | JTAG test data output pin.<br>Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.<br>Timer4 external clock input.<br>Timer5 external clock input.<br>Timer6 external clock input.<br>Timer7 external clock input.<br>Timer8 external clock input.<br>Timer9 external clock input.<br>UART1 clear to send.<br>UART1 receive.<br>UART1 receive.<br>UART1 transmit.<br>UART2 clear to send.<br>UART2 receive.<br>UART2 receive.<br>UART2 receive.<br>UART2 transmit.                                     |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

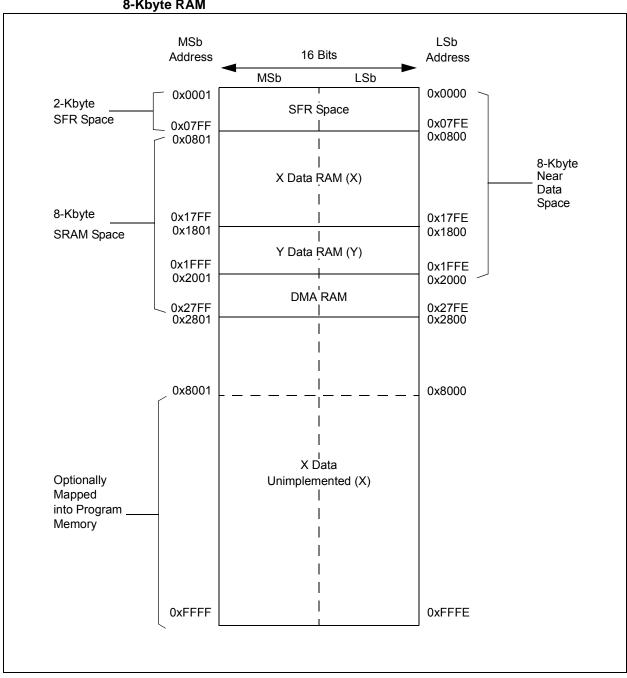

### FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXMCX06A/X08A/X10A DEVICES WITH 8-Kbyte RAM

#### SR: CPU STATUS REGISTER<sup>(1)</sup> **REGISTER 7-1:**

| R-0    | R-0 | R/C-0 | R/C-0 | R-0 | R/C-0 | R-0 | R/W-0 |

|--------|-----|-------|-------|-----|-------|-----|-------|

| OA     | OB  | SA    | SB    | OAB | SAB   | DA  | DC    |

| bit 15 |     |       |       |     |       |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:           |                      |                                    |  |

|-------------------|----------------------|------------------------------------|--|

| C = Clearable bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Settable bit  | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set  | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5

IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU interrupt priority level is 7 (15), user interrupts disabled 110 = CPU interrupt priority level is 6 (14)

101 = CPU interrupt priority level is 5 (13)

100 = CPU interrupt priority level is 4 (12)

- 011 = CPU interrupt priority level is 3 (11)

- 010 = CPU interrupt priority level is 2 (10)

- 001 = CPU interrupt priority level is 1 (9)

- 000 = CPU interrupt priority level is 0 (8)

#### Note 1: For complete register details, see Register 3-1: "SR: CPU STATUS Register".

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU interrupt priority level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### CORCON: CORE CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-2:**

| U-0                               | U-0   | U-0             | R/W-0             | R/W-0                              | R-0   | R-0     | R-0   |

|-----------------------------------|-------|-----------------|-------------------|------------------------------------|-------|---------|-------|

| —                                 | —     | —               | US                | EDT                                |       | DL<2:0> |       |

| bit 15                            |       |                 |                   |                                    |       |         | bit 8 |

|                                   |       |                 |                   |                                    |       |         |       |

| R/W-0                             | R/W-0 | R/W-1           | R/W-0             | R/C-0                              | R/W-0 | R/W-0   | R/W-0 |

| SATA                              | SATB  | SATDW           | ACCSAT            | IPL3 <sup>(2)</sup>                | PSV   | RND     | IF    |

| bit 7                             |       |                 |                   |                                    |       |         | bit 0 |

|                                   |       |                 |                   |                                    |       |         |       |

| Legend:                           |       | C = Clearable   | e bit             |                                    |       |         |       |

| R = Readable bit W = Writable bit |       | bit             | -n = Value at POR |                                    |       |         |       |

| 0' = Bit is clear                 | ed    | 'x = Bit is unk | nown              | U = Unimplemented bit, read as '0' |       |         |       |

| -                                 |       |                 |                   |                                    |       |         |       |

bit 3

IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU interrupt priority level is greater than 7

0 = CPU interrupt priority level is 7 or less

Note 1: For complete register details, see Register 3-2: "CORCON: CORE Control Register".

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

| R/W-0         | R-0           | U-0                                  | U-0           | U-0              | U-0              | U-0             | U-0    |

|---------------|---------------|--------------------------------------|---------------|------------------|------------------|-----------------|--------|

| ALTIVT        | DISI          | —                                    | _             | —                | —                |                 | —      |

| bit 15        |               |                                      |               |                  |                  |                 | bit 8  |

|               |               |                                      |               |                  |                  |                 |        |

| U-0           | U-0           | U-0                                  | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —             | —             | —                                    | INT4EP        | INT3EP           | INT2EP           | INT1EP          | INT0EP |

| bit 7         |               |                                      |               |                  |                  |                 | bit 0  |

|               |               |                                      |               |                  |                  |                 |        |

| Legend:       |               |                                      |               |                  |                  |                 |        |

| R = Readable  |               | W = Writable                         |               | -                | nented bit, read |                 |        |

| -n = Value at | POR           | '1' = Bit is set                     |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|               |               |                                      |               |                  |                  |                 |        |

| bit 15        |               | ole Alternate In                     | •             | lable bit        |                  |                 |        |

|               |               | nate Interrupt \<br>lard (default) v |               |                  |                  |                 |        |

| bit 14        |               | struction Statu                      |               |                  |                  |                 |        |

|               |               | ruction is activ                     |               |                  |                  |                 |        |

|               | 0 = DISI inst | ruction is not a                     | ictive        |                  |                  |                 |        |

| bit 13-5      | Unimplemen    | ted: Read as '                       | 0'            |                  |                  |                 |        |

| bit 4         | INT4EP: Exte  | ernal Interrupt 4                    | Edge Detect   | Polarity Select  | bit              |                 |        |

|               |               | on negative ed                       |               |                  |                  |                 |        |

|               | -             | on positive edg                      |               |                  |                  |                 |        |

| bit 3         |               | •                                    | •             | Polarity Select  | bit              |                 |        |

|               |               | on negative ed<br>on positive edg    |               |                  |                  |                 |        |

| bit 2         | -             |                                      |               | Polarity Select  | bit              |                 |        |

| SIT Z         |               | on negative ed                       | •             |                  | . Dit            |                 |        |

|               |               | on positive edg                      |               |                  |                  |                 |        |

| bit 1         | INT1EP: Exte  | ernal Interrupt                      | I Edge Detect | Polarity Select  | bit              |                 |        |

|               |               | on negative ed                       | 0             |                  |                  |                 |        |

|               | •             | on positive edg                      |               |                  |                  |                 |        |

| bit 0         |               |                                      |               | Polarity Select  | bit              |                 |        |

|               |               | on negative ed                       |               |                  |                  |                 |        |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

#### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0               | U-0             | U-0                               | U-0            | U-0              | U-0             | U-0             | U-0    |

|-------------------|-----------------|-----------------------------------|----------------|------------------|-----------------|-----------------|--------|

| _                 | —               | _                                 | —              | —                | —               | —               | _      |

| bit 15            |                 |                                   | •              | •                |                 |                 | bit 8  |

|                   |                 |                                   |                |                  |                 |                 |        |

| R/W-0             | R/W-0           | R/W-0                             | R/W-0          | U-0              | R/W-0           | R/W-0           | R/W-0  |

| C2TXIE            | C1TXIE          | DMA7IE                            | DMA6IE         | —                | U2EIE           | U1EIE           | FLTBIE |

| bit 7             |                 |                                   |                |                  |                 |                 | bit (  |

| Legend:           |                 |                                   |                |                  |                 |                 |        |

| R = Readab        | le bit          | W = Writable                      | bit            | U = Unimpler     | mented bit, rea | d as '0'        |        |

| -n = Value a      | t POR           | '1' = Bit is set                  |                | '0' = Bit is cle | ared            | x = Bit is unki | nown   |

| bit 15-8<br>bit 7 | •               | ted: Read as '                    |                | nterrunt Enabl   | e hit           |                 |        |

| bit 7             | C2TXIE: ECA     | N2 Transmit D                     | ata Request li | nterrupt Enable  | e bit           |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 6             | C1TXIE: ECA     | N1 Transmit D                     | ata Request I  | nterrupt Enable  | e bit           |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 5             | DMA7IE: DM      | A Channel 7 D                     | ata Transfer C | complete Enab    | le Status bit   |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 4             | DMA6IE: DM      | A Channel 6 D                     | ata Transfer C | complete Enab    | le Status bit   |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 3             | Unimplemen      | ted: Read as '                    | 0'             |                  |                 |                 |        |

| bit 2             | U2EIE: UART     | Γ2 Error Interru                  | pt Enable bit  |                  |                 |                 |        |

|                   |                 | request enable<br>request not ena |                |                  |                 |                 |        |

| bit 1             | •               | T1 Error Interru                  |                |                  |                 |                 |        |

|                   | 1 = Interrupt ı | request enable<br>request not ena | d              |                  |                 |                 |        |

| bit 0             | •               | V Fault B Interr                  |                |                  |                 |                 |        |

| -                 | ו = Interrupt ו | request enable<br>request not ena | d              |                  |                 |                 |        |

### 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 22. "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., the UART Receive register and Input Capture 1 buffer) and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers, and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJXXXMCX06A/X08A/X10A peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

#### TABLE 8-1: PERIPHERALS WITH DMA SUPPORT

| Peripheral         | IRQ Number |

|--------------------|------------|

| INTO               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels. Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data, either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- · Word or byte-sized data transfers.

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral.

- Indirect Addressing of DMA RAM locations with or without automatic post-increment.

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral.

- One-Shot Block Transfers Terminating DMA transfer after one block transfer.

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete.

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately.

- · Automatic or manual initiation of block transfers.

- Each channel can select from 20 possible sources of data sources or destinations.

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0      | R/W-0                  | U-0        | U-0                    | R/W-0      | R/W-0      |

|-------|------------------------|------------|------------------------|------------|------------------------|------------|------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5(2) | IRQSEL4 <sup>(2)</sup> | IRQSEL3(2) | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2) | IRQSEL0(2) |

| bit 7 |                        |            |                        |            |                        |            | bit 0      |

| Legend:                                                              |                  |                      |                    |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: See Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

### 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/ X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit (I<sup>2</sup>C™)" (DS70195) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit  $(I^2C)$  module, with its 16-bit interface, provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard.

The dsPIC33FJXXXMCX06A/X08A/X10A devices have up to two  $I^2$ C interface modules, denoted as I2C1 and I2C2. Each  $I^2$ C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supports both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; it detects bus collision and will arbitrate accordingly

### 19.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $I^2C$  module can operate either as a slave or a master on an  $I^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please refer to the "*dsPIC33F/PIC24H Family Reference Manual*".

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 4 | P: Stop bit                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Stop bit has been detected last                                                                                       |

|       | 0 = Stop bit was not detected last                                                                                                         |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                         |

| bit 3 | S: Start bit                                                                                                                               |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                         |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | 1 = Read – indicates data transfer is output from slave                                                                                    |

|       | 0 = Write – indicates data transfer is input to slave<br>Hardware set or clear after reception of I <sup>2</sup> C device address byte.    |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive complete; I2CxRCV is full                                                                                                      |

|       | 0 = Receive not complete; I2CxRCV is empty                                                                                                 |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.                                       |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty                                                       |

|       | Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.                                              |

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                      |

- Note 1: Refer to Section 17. "UART" (DS70188) in the "dsPIC33F/PIC24H Family Reference Manual" for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on the UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on the UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters</li> </ul> |