Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 20 MIPS                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, QEI, WDT                |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128mc706a-h-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/ X10A family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJXXXMCX06A/X08A/X10A family of 16-bit Digital Signal Controllers (DSC) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The       | AVdd    | and         | AVss    | pins | mu  | st be |

|-------|-----------|---------|-------------|---------|------|-----|-------|

|       | connected |         | independent |         | of   | the | ADC   |

|       | volta     | ge refe | rence       | source. |      |     |       |

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

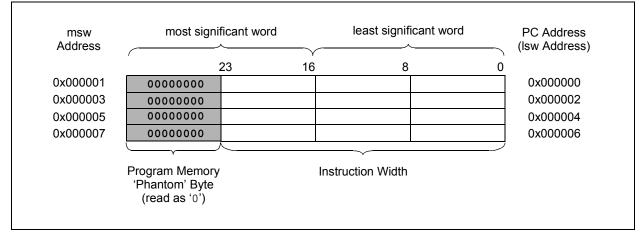

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXMCX06A/X08A/X10A devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXMCX06A/X08A/X10A devices also have two interrupt vector tables located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJXXXMCX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJXXXMCX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJXXXMCX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and

three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data by blocks (or 'rows') of 64 instructions (192 bytes) at a time or by single program memory word; the user can erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

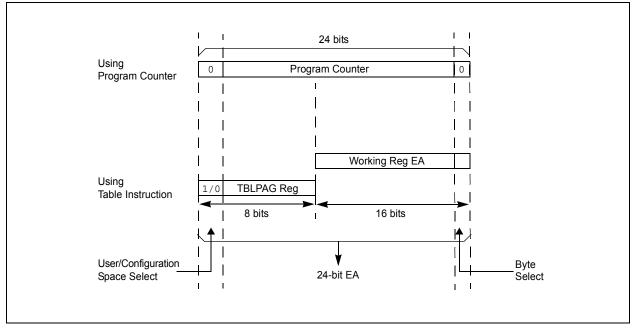

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; Set up NVMCO | N for row programming operations | 3     |                                       |

|----------------|----------------------------------|-------|---------------------------------------|

| MOV            | #0x4001, W0                      | ;     |                                       |

| MOV            | W0, NVMCON                       | ;     | Initialize NVMCON                     |

| ; Set up a poi | nter to the first program memory | / loc | ation to be written                   |

| ; program memo | ry selected, and writes enabled  |       |                                       |

| MOV            | #0x0000, W0                      | ;     |                                       |

| MOV            | W0, TBLPAG                       | ;     | Initialize PM Page Boundary SFR       |

| MOV            | #0x6000, W0                      | ;     | An example program memory address     |

| ; Perform the  | TBLWT instructions to write the  | latc  | hes                                   |

| ; Oth_program_ | word                             |       |                                       |

| MOV            | #LOW_WORD_0, W2                  | ;     |                                       |

| MOV            | #HIGH_BYTE_0, W3                 | ;     |                                       |

| TBLWTL         | W2, [W0]                         | ;     | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; 1st_program_ | word                             |       |                                       |

| MOV            | #LOW_WORD_1, W2                  | ;     |                                       |

| MOV            | #HIGH_BYTE_1, W3                 | ;     |                                       |

| TBLWTL         | W2, [W0]                         | ;     | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; 2nd_program  | _word                            |       |                                       |

|                | #LOW_WORD_2, W2                  | ;     |                                       |

|                | <pre>#HIGH_BYTE_2, W3</pre>      | ;     |                                       |

|                | W2, [W0]                         |       | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| •              |                                  |       |                                       |

| •              |                                  |       |                                       |

| •              |                                  |       |                                       |

| ; 63rd_program | —                                |       |                                       |

| MOV            | #LOW_WORD_31, W2                 | ;     |                                       |

| MOV            | #HIGH_BYTE_31, W3                | ;     |                                       |

|                | W2, [W0]                         |       | Write PM low word into program latch  |

| TBLWTH         | W3, [W0++]                       | ;     | Write PM high byte into program latch |

|                |                                  |       |                                       |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI | #5          | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | ;                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ; Insert two NOPs after the             |

| NOP  |             | ; erase command is asserted             |

|      |             |                                         |

# dsPIC33FJXXXMCX06A/X08A/X10A

| GURE 7-1:                         |                             |                      | NTERRUPT VECTOR TABLE                                  |

|-----------------------------------|-----------------------------|----------------------|--------------------------------------------------------|

| 1                                 | Reset – GOTO Instruction    | 0x000000             |                                                        |

|                                   | Reset – GOTO Address        | 0x000002             |                                                        |

|                                   | Reserved                    | 0x000002             |                                                        |

|                                   |                             | 0X000004             |                                                        |

|                                   | Oscillator Fail Trap Vector | -                    |                                                        |

|                                   | Address Error Trap Vector   |                      |                                                        |

|                                   | Stack Error Trap Vector     |                      |                                                        |

|                                   | Math Error Trap Vector      |                      |                                                        |

|                                   | DMA Error Trap Vector       |                      |                                                        |

|                                   | Reserved                    |                      |                                                        |

|                                   | Reserved                    |                      |                                                        |

|                                   | Interrupt Vector 0          | 0x000014 —           |                                                        |

|                                   | Interrupt Vector 1          |                      |                                                        |

|                                   | ~                           |                      |                                                        |

|                                   | ~                           |                      |                                                        |

|                                   | ~                           |                      |                                                        |

|                                   | Interrupt Vector 52         | 0x00007C             | <b>—</b> • • • • • • • • • • • • • • • • • • •         |

|                                   | Interrupt Vector 53         | 0x00007E             | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| Ę                                 | Interrupt Vector 54         | 0x000080             |                                                        |

| ori                               | ~                           | 0,000000             |                                                        |

| Pri                               | ~                           |                      |                                                        |

| er                                | ~                           | _                    |                                                        |

| Drd                               | Interrupt Venter 116        | 0,0000000            |                                                        |

|                                   | Interrupt Vector 116        | 0x0000FC<br>0x0000FE |                                                        |

| nıs                               | Interrupt Vector 117        |                      |                                                        |

| Vat                               | Reserved                    | 0x000100             |                                                        |

| <u>г</u>                          | Reserved                    | 0x000102             |                                                        |

| sin                               | Reserved                    |                      |                                                        |

| ea                                | Oscillator Fail Trap Vector |                      |                                                        |

| Decreasing Natural Order Priority | Address Error Trap Vector   |                      |                                                        |

| ă                                 | Stack Error Trap Vector     |                      |                                                        |

|                                   | Math Error Trap Vector      |                      |                                                        |

|                                   | DMA Error Trap Vector       |                      |                                                        |

|                                   | Reserved                    |                      |                                                        |

|                                   | Reserved                    |                      |                                                        |

|                                   | Interrupt Vector 0          | 0x000114             |                                                        |

|                                   | Interrupt Vector 1          |                      |                                                        |

|                                   | ~                           |                      |                                                        |

|                                   | ~                           |                      |                                                        |

|                                   | ~                           | -                    | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52         | 0x00017C             | Alternate interrupt veotor rable (Alt I)               |

|                                   | Interrupt Vector 53         | 0x00017E             |                                                        |

|                                   | Interrupt Vector 54         | 0x000180             |                                                        |

|                                   | ~                           | 0,000,100            |                                                        |

|                                   |                             | _                    |                                                        |

|                                   | ~                           | -                    |                                                        |

|                                   |                             | -                    |                                                        |

|                                   | Interrupt Vector 116        |                      |                                                        |

| ↓                                 | Interrupt Vector 117        | 0x0001FE -           | l                                                      |

| v                                 | Start of Code               | 0x000200             |                                                        |

|                                   |                             |                      |                                                        |

|                                   |                             |                      |                                                        |

|                                   |                             |                      |                                                        |

|                                   |                             | ented interrupt v    |                                                        |

| R/W-0         | R-0                                                                                                   | U-0                                                          | U-0         | U-0              | U-0              | U-0             | U-0    |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------|------------------|------------------|-----------------|--------|--|--|--|--|

| ALTIVT        | DISI                                                                                                  | —                                                            | _           | —                | —                |                 | —      |  |  |  |  |

| bit 15        |                                                                                                       |                                                              |             |                  |                  |                 | bit 8  |  |  |  |  |

|               |                                                                                                       |                                                              |             |                  |                  |                 |        |  |  |  |  |

| U-0           | U-0                                                                                                   | U-0                                                          | R/W-0       | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

| —             | —                                                                                                     | —                                                            | INT4EP      | INT3EP           | INT2EP           | INT1EP          | INT0EP |  |  |  |  |

| bit 7         |                                                                                                       |                                                              |             |                  |                  |                 | bit 0  |  |  |  |  |

|               |                                                                                                       |                                                              |             |                  |                  |                 |        |  |  |  |  |

| Legend:       |                                                                                                       |                                                              |             |                  |                  |                 |        |  |  |  |  |

| R = Readable  |                                                                                                       | W = Writable                                                 |             | -                | nented bit, read |                 |        |  |  |  |  |

| -n = Value at | POR                                                                                                   | '1' = Bit is set                                             |             | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |  |

|               |                                                                                                       |                                                              |             |                  |                  |                 |        |  |  |  |  |

| bit 15        |                                                                                                       | ole Alternate In                                             | •           | lable bit        |                  |                 |        |  |  |  |  |

|               |                                                                                                       | nate Interrupt \<br>lard (default) v                         |             |                  |                  |                 |        |  |  |  |  |

| bit 14        |                                                                                                       | struction Statu                                              |             |                  |                  |                 |        |  |  |  |  |

|               |                                                                                                       | ruction is activ                                             |             |                  |                  |                 |        |  |  |  |  |

|               | 0 = DISI inst                                                                                         | ruction is not a                                             | ictive      |                  |                  |                 |        |  |  |  |  |

| bit 13-5      | Unimplemen                                                                                            | ted: Read as '                                               | 0'          |                  |                  |                 |        |  |  |  |  |

| bit 4         | INT4EP: Exte                                                                                          | ernal Interrupt 4                                            | Edge Detect | Polarity Select  | bit              |                 |        |  |  |  |  |

|               |                                                                                                       | on negative ed                                               |             |                  |                  |                 |        |  |  |  |  |

|               | -                                                                                                     | on positive edg                                              |             |                  |                  |                 |        |  |  |  |  |

| bit 3         |                                                                                                       | INT3EP: External Interrupt 3 Edge Detect Polarity Select bit |             |                  |                  |                 |        |  |  |  |  |

|               | <ul> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul>            |                                                              |             |                  |                  |                 |        |  |  |  |  |

| bit 2         | -                                                                                                     |                                                              |             | Polarity Select  | bit              |                 |        |  |  |  |  |

| SIT Z         | <b>INT2EP:</b> External Interrupt 2 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge |                                                              |             |                  |                  |                 |        |  |  |  |  |

|               | 0 = Interrupt on positive edge                                                                        |                                                              |             |                  |                  |                 |        |  |  |  |  |

| bit 1         | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit                                          |                                                              |             |                  |                  |                 |        |  |  |  |  |

|               |                                                                                                       | on negative ed                                               | 0           |                  |                  |                 |        |  |  |  |  |

|               | •                                                                                                     | on positive edg                                              |             |                  |                  |                 |        |  |  |  |  |

| bit 0         |                                                                                                       |                                                              |             | Polarity Select  | bit              |                 |        |  |  |  |  |

|               |                                                                                                       | on negative ed                                               |             |                  |                  |                 |        |  |  |  |  |

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| REGISTER 7-11: IEC | 1: INTERRUPT ENABLE CONTROL REGISTER 1 |

|--------------------|----------------------------------------|

|--------------------|----------------------------------------|

| R/W-0           | R/W-0                                                                                                              | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0            |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|------------------|------------------|-----------------|------------------|--|--|--|--|

| U2TXIE          | U2RXIE                                                                                                             | INT2IE                            | T5IE            | T4IE             | OC4IE            | OC3IE           | DMA2IE           |  |  |  |  |

| bit 15          | •                                                                                                                  | ·                                 | •               |                  | •                | •               | bit 8            |  |  |  |  |

|                 |                                                                                                                    |                                   | DAMO            | DAMO             |                  |                 |                  |  |  |  |  |

| R/W-0<br>IC8IE  | R/W-0                                                                                                              | R/W-0<br>AD2IE                    | R/W-0<br>INT1IE | R/W-0            | U-0              | R/W-0           | R/W-0<br>SI2C1IE |  |  |  |  |

| bit 7           | IC7IE                                                                                                              | ADZIE                             |                 | CNIE             | —                | MI2C1IE         | bit 0            |  |  |  |  |

|                 |                                                                                                                    |                                   |                 |                  |                  |                 |                  |  |  |  |  |

| Legend:         |                                                                                                                    |                                   |                 |                  |                  |                 |                  |  |  |  |  |

| R = Readable    |                                                                                                                    | W = Writable                      |                 | -                | mented bit, read |                 |                  |  |  |  |  |

| -n = Value at F | POR                                                                                                                | '1' = Bit is set                  |                 | '0' = Bit is cle | ared             | x = Bit is unkr | IOWN             |  |  |  |  |

| bit 15          | U2TXIE: UAR                                                                                                        | RT2 Transmitter                   | r Interrupt Ena | able bit         |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request enable                    |                 |                  |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request not ena                   |                 |                  |                  |                 |                  |  |  |  |  |

| bit 14          | U2RXIE: UAF                                                                                                        | RT2 Receiver Ir                   | nterrupt Enabl  | le bit           |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request enable                    |                 |                  |                  |                 |                  |  |  |  |  |

| bit 13          |                                                                                                                    | request not ena                   |                 |                  |                  |                 |                  |  |  |  |  |

| DIL 13          | INT2IE: External Interrupt 2 Enable bit<br>1 = Interrupt request enabled                                           |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request not ena                   |                 |                  |                  |                 |                  |  |  |  |  |

| bit 12          | T5IE: Timer5 Interrupt Enable bit                                                                                  |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 | 1 = Interrupt request enabled                                                                                      |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 | -                                                                                                                  | 0 = Interrupt request not enabled |                 |                  |                  |                 |                  |  |  |  |  |

| bit 11          | <b>T4IE:</b> Timer4 Interrupt Enable bit<br>1 = Interrupt request enabled                                          |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request enable                    |                 |                  |                  |                 |                  |  |  |  |  |

| bit 10          | <b>OC4IE:</b> Output Compare Channel 4 Interrupt Enable bit                                                        |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request enable<br>request not ena |                 |                  |                  |                 |                  |  |  |  |  |

| bit 9           | •                                                                                                                  | •                                 |                 | unt Enable bit   |                  |                 |                  |  |  |  |  |

| bit 5           | <b>OC3IE:</b> Output Compare Channel 3 Interrupt Enable bit<br>1 = Interrupt request enabled                       |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request not ena                   |                 |                  |                  |                 |                  |  |  |  |  |

| bit 8           | DMA2IE: DM                                                                                                         | A Channel 2 D                     | ata Transfer (  | Complete Interi  | rupt Enable bit  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request enable                    |                 |                  |                  |                 |                  |  |  |  |  |

| bit 7           | <ul> <li>0 = Interrupt request not enabled</li> <li>IC8IE: Input Capture Channel 8 Interrupt Enable bit</li> </ul> |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 | 1 = Interrupt request enabled                                                                                      |                                   |                 |                  |                  |                 |                  |  |  |  |  |

|                 | 0 = Interrupt request not enabled                                                                                  |                                   |                 |                  |                  |                 |                  |  |  |  |  |

| bit 6           | -                                                                                                                  | Capture Chann                     | -               | Enable bit       |                  |                 |                  |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul>                       |                                   |                 |                  |                  |                 |                  |  |  |  |  |

| bit 5           |                                                                                                                    | 2 Conversion C                    |                 | runt Enable bit  |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request enable                    | •               | ישףי בוומטופ טונ |                  |                 |                  |  |  |  |  |

|                 | •                                                                                                                  | request not ena                   |                 |                  |                  |                 |                  |  |  |  |  |

| bit 4           | INT1IE: Exter                                                                                                      | nal Interrupt 1                   | Enable bit      |                  |                  |                 |                  |  |  |  |  |

|                 |                                                                                                                    | request enable                    |                 |                  |                  |                 |                  |  |  |  |  |

|                 | 0 = Interrupt r                                                                                                    | request not ena                   | abled           |                  |                  |                 |                  |  |  |  |  |

| REGISTER 7-26: IPC11: INTERRUPT PRIC | ORITY CONTROL REGISTER 11 |

|--------------------------------------|---------------------------|

|--------------------------------------|---------------------------|

| U-0          | R/W-1                                                                     | R/W-0              | R/W-0        | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

|--------------|---------------------------------------------------------------------------|--------------------|--------------|------------------|------------------|-----------------|-------|--|--|--|--|

|              |                                                                           | T6IP<2:0>          |              |                  |                  | DMA4IP<2:0>     |       |  |  |  |  |

| bit 15       |                                                                           |                    |              |                  |                  |                 | bit 8 |  |  |  |  |

| U-0          | U-0                                                                       | U-0                | U-0          | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

| _            |                                                                           | _                  | _            | _                |                  | OC8IP<2:0>      |       |  |  |  |  |

| bit 7        |                                                                           |                    |              |                  | I                |                 | bit   |  |  |  |  |

|              |                                                                           |                    |              |                  |                  |                 |       |  |  |  |  |

| Legend:      |                                                                           |                    |              |                  |                  |                 |       |  |  |  |  |

| R = Readab   |                                                                           | W = Writable I     | oit          | -                | mented bit, read |                 |       |  |  |  |  |

| -n = Value a | t POR                                                                     | '1' = Bit is set   |              | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

|              |                                                                           |                    |              |                  |                  |                 |       |  |  |  |  |

| bit 15       | -                                                                         | ented: Read as 'o  |              |                  |                  |                 |       |  |  |  |  |

| bit 14-12    | T6IP<2:0>: Timer6 Interrupt Priority bits                                 |                    |              |                  |                  |                 |       |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>     |                    |              |                  |                  |                 |       |  |  |  |  |

|              | •                                                                         |                    |              |                  |                  |                 |       |  |  |  |  |

|              | •                                                                         |                    |              |                  |                  |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1                                             |                    |              |                  |                  |                 |       |  |  |  |  |

|              |                                                                           | upt source is disa |              |                  |                  |                 |       |  |  |  |  |

| bit 11       | Unimplemented: Read as '0'                                                |                    |              |                  |                  |                 |       |  |  |  |  |

| bit 10-8     | DMA4IP<2:0>: DMA Channel 4 Data Transfer Complete Interrupt Priority bits |                    |              |                  |                  |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                |                    |              |                  |                  |                 |       |  |  |  |  |

|              |                                                                           |                    |              |                  |                  |                 |       |  |  |  |  |

|              | •                                                                         |                    |              |                  |                  |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1                                             |                    |              |                  |                  |                 |       |  |  |  |  |

|              | 000 = Interrupt source is disabled                                        |                    |              |                  |                  |                 |       |  |  |  |  |

| bit 7-3      | Unimpleme                                                                 | ented: Read as '0  | )'           |                  |                  |                 |       |  |  |  |  |

| bit 2-0      | OC8IP<2:0                                                                 | : Output Compa     | re Channel 8 | Interrupt Prior  | ity bits         |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)                |                    |              |                  |                  |                 |       |  |  |  |  |

|              | •                                                                         |                    |              |                  |                  |                 |       |  |  |  |  |

|              | •                                                                         |                    |              |                  |                  |                 |       |  |  |  |  |

|              | •                                                                         |                    |              |                  |                  |                 |       |  |  |  |  |

|              | •<br>001 = Interr                                                         | upt is priority 1  |              |                  |                  |                 |       |  |  |  |  |

# dsPIC33FJXXXMCX06A/X08A/X10A

NOTES:

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0                               | U-0   | U-0   | U-0   | U-0          | U-0              | R/W-0  | R/W-0 |

|-----------------------------------|-------|-------|-------|--------------|------------------|--------|-------|

| —                                 | —     | —     | _     |              | —                | AMSK9  | AMSK8 |

| bit 15                            |       |       |       |              |                  |        | bit 8 |

|                                   |       |       |       |              |                  |        |       |

| R/W-0                             | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

| AMSK7                             | AMSK6 | AMSK5 | AMSK4 | AMSK3        | AMSK2            | AMSK1  | AMSK0 |

| bit 7                             |       |       |       |              |                  | •      | bit 0 |

|                                   |       |       |       |              |                  |        |       |

| Legend:                           |       |       |       |              |                  |        |       |

| R = Readable bit W = Writable bit |       |       |       | U = Unimpler | mented bit, read | as '0' |       |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSKx: Mask for Address bit x Select bits

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

### REGISTER 21-12: CiBUFPNT1: ECAN™ FILTER 0-3 BUFFER POINTER REGISTER

|                 | R/W-0         | R/W-0                                | R/W-0           | R/W-0             | R/W-0         | R/W-0           | R/W-0 |

|-----------------|---------------|--------------------------------------|-----------------|-------------------|---------------|-----------------|-------|

|                 | F3BP          | <3:0>                                |                 |                   | F2BI          | D<3:0>          |       |

| bit 15          |               |                                      |                 |                   |               |                 | bit 8 |

|                 |               |                                      |                 |                   |               |                 |       |

| R/W-0           | R/W-0         | R/W-0                                | R/W-0           | R/W-0             | R/W-0         | R/W-0           | R/W-0 |

|                 | F1BP          | <3:0>                                |                 |                   | F0B           | P<3:0>          |       |

| bit 7           |               |                                      |                 |                   |               |                 | bit 0 |

| Legend:         |               |                                      |                 |                   |               |                 |       |

| R = Readable    | hit           | W = Writable                         | hit             | U = Unimplem      | ented hit rea | d as '0'        |       |

| -n = Value at F |               | '1' = Bit is set                     |                 | '0' = Bit is clea |               | x = Bit is unki | nown  |

|                 |               | 2.1.0 000                            |                 | 0 2000 0000       |               |                 |       |

| bit 15-12       | F3BP<3:0>:    | RX Buffer Writt                      | en when Filte   | er 3 Hits bits    |               |                 |       |

|                 |               | hits received in                     |                 | -                 |               |                 |       |

|                 |               | hits received in                     | NRX Buffer 1    | 4                 |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | 0001 = Filter | hits received ir                     | n RX Buffer 1   |                   |               |                 |       |

|                 | 0000 = Filter | hits received in                     | n RX Buffer 0   |                   |               |                 |       |

| bit 11-8        |               | RX Buffer Writt                      |                 |                   |               |                 |       |

|                 |               | hits received in<br>hits received in |                 | -                 |               |                 |       |

|                 | •             |                                      | li o C Ballor I |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 |               | hits received in hits received in    |                 |                   |               |                 |       |

| bit 7-4         |               | RX Buffer Writt                      |                 |                   |               |                 |       |

|                 |               | hits received in<br>hits received in |                 | -                 |               |                 |       |

|                 | •             |                                      | THAT Durier 1   | -                 |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 |               | hits received in hits received in    |                 |                   |               |                 |       |

| bit 3-0         | F0BP<3:0>:    | RX Buffer Writt                      | en when Filte   | er 0 Hits bits    |               |                 |       |

|                 |               | hits received in                     |                 |                   |               |                 |       |

|                 | 1110 = Filter | hits received ir                     | n RX Buffer 1   | 4                 |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | •             |                                      |                 |                   |               |                 |       |

|                 | 0001 = Filter | hits received in                     |                 |                   |               |                 |       |

|                 |               | TIILS IECEIVEU II                    |                 |                   |               |                 |       |

#### REGISTER 21-20: CIRXMnSID: ECAN™ ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER

| R/W-x                             | R/W-x             | R/W-x                                                        | R/W-x                              | R/W-x            | R/W-x              | R/W-x           | R/W-x              |  |

|-----------------------------------|-------------------|--------------------------------------------------------------|------------------------------------|------------------|--------------------|-----------------|--------------------|--|

|                                   |                   |                                                              | SID                                | <10:3>           |                    |                 |                    |  |

| bit 15                            |                   |                                                              |                                    |                  |                    |                 | bit 8              |  |

| R/W-x                             |                   |                                                              |                                    |                  |                    |                 |                    |  |

| R/W-X                             | R/W-x<br>SID<2:0> | R/W-x                                                        | U-0                                | R/W-x<br>MIDE    | U-0                | R/W-x           | R/W-x              |  |

| h:+ <b>7</b>                      | SID<2:0>          |                                                              | _                                  | MIDE             |                    | EID<            | -                  |  |

| bit 7                             |                   |                                                              |                                    |                  |                    |                 | bit 0              |  |

| Legend:                           |                   |                                                              |                                    |                  |                    |                 |                    |  |

| R = Readable bit W = Writable bit |                   |                                                              | U = Unimplemented bit, read as '0' |                  |                    |                 |                    |  |

| -n = Value at POR '1' = Bit is    |                   |                                                              |                                    | '0' = Bit is cle | ared               | x = Bit is unkr | nown               |  |

|                                   |                   |                                                              |                                    |                  |                    |                 |                    |  |

| bit 15-5                          | SID<10:0>:        | Standard Identif                                             | ier bits                           |                  |                    |                 |                    |  |

|                                   |                   | bit, SIDx, in filter<br>x, is a don't care i                 | •                                  | parison          |                    |                 |                    |  |

| bit 4                             | Unimpleme         | ented: Read as '0                                            | )'                                 |                  |                    |                 |                    |  |

| bit 3                             | MIDE: Iden        | tifier Receive Mo                                            | de bit                             |                  |                    |                 |                    |  |

|                                   | 0 = Match e       | only message type<br>either standard or<br>Filter SID) = (Me | extended a                         | ddress messag    | e if filters match | n i             | (IDE bit in filter |  |

| bit 2                             | Unimpleme         | ented: Read as '0                                            | )'                                 |                  |                    |                 |                    |  |

| bit 1-0                           | EID<17:16>        | Extended Ident                                               | ifier bits                         |                  |                    |                 |                    |  |

|                                   |                   | bit, EIDx, in filter<br>x, is a don't care                   |                                    |                  |                    |                 |                    |  |

### REGISTER 21-21: CIRXMnEID: ECAN™ ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

|                 |       |                  | EID   | <15:8>           |                  |                 |       |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|                 |       |                  | EID   | <7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                  |                 |       |

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Include bit, EIDx, in filter comparison

0 = Bit, EIDx, is a don't care in filter comparison

#### **REGISTER 22-2:** ADxCON2: ADCx CONTROL REGISTER 2 (where x = 1 or 2)

|                  | R/W-0                                                                      | R/W-0                                                                                                                                                     | U-0                                                                                           | U-0                                              | R/W-0                                                  | R/W-0                                                  | R/W-0                                                |

|------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------|

|                  | VCFG<2:0>                                                                  |                                                                                                                                                           | _                                                                                             | _                                                | CSCNA                                                  | CHPS                                                   | S<1:0>                                               |

| bit 15           |                                                                            |                                                                                                                                                           |                                                                                               |                                                  |                                                        |                                                        | bit 8                                                |

| R-0              | U-0                                                                        | R/W-0                                                                                                                                                     | R/W-0                                                                                         | R/W-0                                            | R/W-0                                                  | R/W-0                                                  | R/W-0                                                |

| BUFS             | _                                                                          |                                                                                                                                                           | SMPI<                                                                                         | :3:0>                                            |                                                        | BUFM                                                   | ALTS                                                 |

| bit 7            | I                                                                          |                                                                                                                                                           |                                                                                               |                                                  |                                                        |                                                        | bit (                                                |

| Legend:          |                                                                            |                                                                                                                                                           |                                                                                               |                                                  |                                                        |                                                        |                                                      |

| R = Readable     | e bit                                                                      | W = Writab                                                                                                                                                | le bit                                                                                        | U = Unimpler                                     | mented bit, read                                       | l as '0'                                               |                                                      |

| -n = Value at    | POR                                                                        | '1' = Bit is s                                                                                                                                            | et                                                                                            | '0' = Bit is cle                                 | ared                                                   | x = Bit is unkr                                        | nown                                                 |

|                  |                                                                            | 0                                                                                                                                                         | the see Defense of a                                                                          | De la filmantia a                                | h:t-                                                   |                                                        |                                                      |

| bit 15-13        |                                                                            |                                                                                                                                                           | bltage Reference (                                                                            | Configuration                                    | DITS                                                   |                                                        |                                                      |

|                  |                                                                            | VREF+                                                                                                                                                     | VREF-                                                                                         | 4                                                |                                                        |                                                        |                                                      |

|                  | 000                                                                        | AVDD                                                                                                                                                      | Avss                                                                                          | _                                                |                                                        |                                                        |                                                      |

|                  |                                                                            | ernal VREF+                                                                                                                                               | Avss                                                                                          | -                                                |                                                        |                                                        |                                                      |

|                  | 010<br>011 Exte                                                            | AVDD<br>ernal VREF+                                                                                                                                       | External VREF-<br>External VREF-                                                              | -                                                |                                                        |                                                        |                                                      |

|                  | 1xx                                                                        |                                                                                                                                                           | Avss                                                                                          | -                                                |                                                        |                                                        |                                                      |

| hit 10 11        |                                                                            |                                                                                                                                                           |                                                                                               | J                                                |                                                        |                                                        |                                                      |

| bit 12-11        |                                                                            |                                                                                                                                                           |                                                                                               | ring Comple                                      | A bit                                                  |                                                        |                                                      |

| bit 10           | 1 = Scan inp                                                               | •                                                                                                                                                         | ctions for CH0+ du                                                                            | ning Sample                                      | A DIL                                                  |                                                        |                                                      |